## E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 25MHz                                                                          |

| Connectivity               | SCI, SmartCard                                                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 86                                                                             |

| Program Memory Size        | 256КВ (256К х 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 128-BFQFP                                                                      |

| Supplier Device Package    | 128-QFP (14x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2328bvf25wv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# 16

## H8S/2329 Group

## Hardware Manual

## Renesas 16-Bit Single-Chip

## Microcomputer H8S Family/H8S/2300 Series

| H8S/2329  | HD64F2329B | H8S/2324S | HD6412324S |

|-----------|------------|-----------|------------|

| 1100/2020 |            | /         |            |

|           | HD64F2329E | H8S/2323  | HD6432323  |

| H8S/2328  | HD6432328  | H8S/2322R | HD6412322R |

|           | HD64F2328B | H8S/2321  | HD6412321  |

| H8S/2327  | HD6432327  | H8S/2320  | HD6412320  |

| H8S/2326  | HD64F2326  |           |            |

Renesas Electronics

Rev.6.00 2007.09

|       | 17.2.3  | Module Stop Control Register (MSTPCR)               | 728 |

|-------|---------|-----------------------------------------------------|-----|

| 17.3  |         | on                                                  |     |

|       | 1       |                                                     |     |

| Secti | on 18   | RAM                                                 | 731 |

| 18.1  | Overvie | PW                                                  | 731 |

|       | 18.1.1  | Block Diagram                                       | 731 |

|       | 18.1.2  | Register Configuration                              | 732 |

| 18.2  |         | r Descriptions                                      |     |

|       |         | System Control Register (SYSCR)                     |     |

| 18.3  |         | on                                                  |     |

| 18.4  | -       | Note                                                |     |

|       | U       |                                                     |     |

| Secti | on 19   | ROM                                                 | 735 |

| 19.1  | Overvie | ew                                                  | 735 |

|       | 19.1.1  | Block Diagram                                       | 735 |

|       | 19.1.2  | Register Configuration                              | 736 |

| 19.2  | Registe | r Descriptions                                      | 736 |

|       | 19.2.1  | Mode Control Register (MDCR)                        | 736 |

|       | 19.2.2  | Bus Control Register L (BCRL)                       | 737 |

| 19.3  | Operati | on                                                  | 737 |

| 19.4  | Overvie | ew of Flash Memory (H8S/2329B F-ZTAT)               | 740 |

|       | 19.4.1  | Features                                            | 740 |

|       | 19.4.2  | Overview                                            | 741 |

|       | 19.4.3  | Flash Memory Operating Modes                        | 742 |

|       |         | On-Board Programming Modes                          |     |

|       | 19.4.5  | Flash Memory Emulation in RAM                       | 745 |

|       |         | Differences between Boot Mode and User Program Mode |     |

|       | 19.4.7  | Block Configuration                                 | 747 |

|       | 19.4.8  | Pin Configuration                                   | 748 |

|       | 19.4.9  | Register Configuration                              | 749 |

| 19.5  | Registe | r Descriptions                                      | 750 |

|       | 19.5.1  | Flash Memory Control Register 1 (FLMCR1)            | 750 |

|       | 19.5.2  | Flash Memory Control Register 2 (FLMCR2)            | 753 |

|       | 19.5.3  | Erase Block Register 1 (EBR1)                       | 754 |

|       | 19.5.4  | Erase Block Registers 2 (EBR2)                      | 754 |

|       | 19.5.5  | System Control Register 2 (SYSCR2)                  | 755 |

|       | 19.5.6  | RAM Emulation Register (RAMER)                      | 756 |

| 19.6  |         | ard Programming Modes                               |     |

|       | 19.6.1  | Boot Mode                                           | 759 |

|       | 19.6.2  | User Program Mode                                   | 763 |

#### 6.2.8 Refresh Timer Counter (RTCNT)

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|            |       |     |     |     |     |     |     |     |     |

| Initial va | lue : | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W        | :     | R/W |

RTCNT is an 8-bit readable/writable up-counter.

RTCNT counts up using the internal clock selected by bits CKS2 to CKS0 in DRAMCR.

When RTCNT matches RTCOR (compare match), the CMF flag in DRAMCR is set to 1 and RTCNT is cleared to H'00. If the RFSHE bit in DRAMCR is set to 1 at this time, a refresh cycle is started. Also, if the CMIE bit in DRAMCR is set to 1, a compare match interrupt (CMI) is generated.

RTCNT is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in software standby mode.

Note: In the H8S/2321 this register is reserved and must not be accessed.

#### 6.2.9 Refresh Time Constant Register (RTCOR)

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|            |       |     |     |     |     |     |     |     |     |

| Initial va | lue : | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W        | :     | R/W |

RTCOR is an 8-bit readable/writable register that sets the period for compare match operations with RTCNT.

The values of RTCOR and RTCNT are constantly compared, and if they match, the CMF flag in DRAMCR is set to 1 and RTCNT is cleared to H'00.

RTCOR is initialized to H'FF by a reset and in hardware standby mode. It is not initialized in software standby mode.

Note: In the H8S/2321 this register is reserved and must not be accessed.

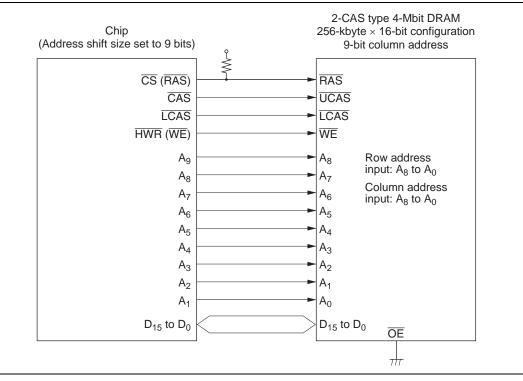

Figure 6.19 Example of 2-CAS DRAM Connection

#### 7.3.3 Execute Transfer Count Register (ETCR)

ETCR is a 16-bit readable/writable register that specifies the number of transfers. The function of this register is different in normal mode and in block transfer mode.

ETCR is not initialized by a reset or in standby mode.

#### Normal Mode

#### ETCRA

| Transfer Counter |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |       |

|------------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-------|

| Bit              | :     | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1    | 0     |

|                  |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |      |       |

| Initial va       | lue : | *   | *   | *   | *   | *   | *   | *   | *   | *   | *   | *   | *   | *   | *   | *    | *     |

| R/W              | :     | R/W  | R/W   |

|                  |       |     |     |     |     |     |     |     |     |     |     |     |     |     | *:  | Unde | fined |

In normal mode, ETCRA functions as a 16-bit transfer counter. ETCRA is decremented by 1 each time a transfer is performed, and transfer ends when the count reaches H'0000. ETCRB is not used at this time.

#### ETCRB

ETCRB is not used in normal mode.

#### 7.3.4 DMA Control Register (DMACR)

DMACR is a 16-bit readable/writable register that controls the operation of each DMAC channel. In full address mode, DMACRA and DMACRB have different functions.

DMACR is initialized to H'0000 by a reset, and in hardware standby mode.

#### DMACRA

| Bit        | :     | 15   | 14   | 13    | 12     | 11   | 10  | 9   | 8   |

|------------|-------|------|------|-------|--------|------|-----|-----|-----|

|            |       | DTSZ | SAID | SAIDE | BLKDIR | BLKE | —   | _   | —   |

| Initial va | lue : | 0    | 0    | 0     | 0      | 0    | 0   | 0   | 0   |

| R/W        | :     | R/W  | R/W  | R/W   | R/W    | R/W  | R/W | R/W | R/W |

#### DMACRB

| Bit        | :     | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|------------|-------|-----|------|-------|-----|------|------|------|------|

|            |       | _   | DAID | DAIDE | _   | DTF3 | DTF2 | DTF1 | DTF0 |

| Initial va | lue : | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W        | :     | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

#### Bit 15—Data Transfer Size (DTSZ): Selects the size of data to be transferred at one time.

| Bit 15 |                    |                 |

|--------|--------------------|-----------------|

| DTSZ   | Description        |                 |

| 0      | Byte-size transfer | (Initial value) |

| 1      | Word-size transfer |                 |

#### 9.13.3 **Pin Functions**

Port F pins also function as bus control signal input/output pins ( $\overline{AS}$ ,  $\overline{RD}$ ,  $\overline{HWR}$ ,  $\overline{LWR}$ ,  $\overline{LCAS}^*$ ,  $\overline{WAIT}$ ,  $\overline{BREQO}$ ,  $\overline{BREQ}$ , and  $\overline{BACK}$ ) and the system clock ( $\phi$ ) output pin. The pin functions differ between modes 4 to 6, and mode 7. Port F pin functions are shown in table 9.25.

Note: \* The  $\overline{\text{LCAS}}$  is not supported in the H8S/2321.

#### Table 9.25Port F Pin Functions

| Pin<br>PF <sub>7</sub> / $\phi$ |                                                         | Selection Method and Pin Functions<br>The pin function is switched as shown below according to bit PF7DDR.      |                              |                            |                            |                               |  |  |  |  |  |

|---------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------|----------------------------|-------------------------------|--|--|--|--|--|

| <b>ΓΓ</b> //Ψ                   | PF7DDR                                                  |                                                                                                                 | 0                            |                            | 1                          |                               |  |  |  |  |  |

|                                 | Pin function                                            | PF <sub>7</sub> input pin                                                                                       |                              |                            |                            | nin                           |  |  |  |  |  |

|                                 | Pin function                                            | PF                                                                                                              | 7 input pin                  |                            | <pre></pre>                | pin                           |  |  |  |  |  |

| PF <sub>6</sub> /AS             |                                                         | The pin function is switched as shown below according to the operating mode, bit PF6DDR, and bit ASOD in PFCR2. |                              |                            |                            |                               |  |  |  |  |  |

|                                 | Operating<br>Mode                                       |                                                                                                                 | Modes 4 to 6                 | Mo                         | de 7                       |                               |  |  |  |  |  |

|                                 | ASOD                                                    | 0                                                                                                               |                              | 1                          | -                          | _                             |  |  |  |  |  |

|                                 | PF6DDR                                                  | _                                                                                                               | 0                            | 1                          | 0                          | 1                             |  |  |  |  |  |

|                                 | Pin function                                            | AS output pin                                                                                                   | PF <sub>6</sub> input<br>pin | PF <sub>6</sub> output pin | PF <sub>6</sub> input pin  | PF <sub>6</sub> output<br>pin |  |  |  |  |  |

|                                 | The pin functior<br>and bit PF5DDF<br>Operating<br>Mode |                                                                                                                 |                              | Mode 7                     |                            |                               |  |  |  |  |  |

|                                 | PF5DDR                                                  |                                                                                                                 |                              | 0                          | 1                          |                               |  |  |  |  |  |

|                                 | Pin function                                            | RD outpu                                                                                                        | ut pin                       | PF <sub>5</sub> input pin  | PF <sub>5</sub>            | output pin                    |  |  |  |  |  |

| PF <sub>4</sub> /HWR            | The pin functior<br>and bit PF4DDF                      |                                                                                                                 | as shown be                  | low according              | g to the oper              | ating mode                    |  |  |  |  |  |

|                                 | Operating<br>Mode                                       | Modes 4                                                                                                         | to 6                         |                            | Mode 7                     |                               |  |  |  |  |  |

|                                 | PF4DDR                                                  | _                                                                                                               |                              | 0                          |                            | 1                             |  |  |  |  |  |

|                                 | Pin function                                            | HWR outp                                                                                                        | unt min                      | PF <sub>4</sub> input pin  | PF <sub>4</sub> output pin |                               |  |  |  |  |  |

**Bits 5 and 4—Group 2 Compare Match Select 1 and 0 (G2CMS1, G2CMS0):** These bits select the compare match that triggers pulse output group 2 (pins PO11 to PO8).

|                 |                 | Description                             |                 |  |  |  |  |  |

|-----------------|-----------------|-----------------------------------------|-----------------|--|--|--|--|--|

| Bit 5<br>G2CMS1 | Bit 4<br>G2CMS0 | Output Trigger for Pulse Output Group 2 |                 |  |  |  |  |  |

| 0               | 0               | Compare match in TPU channel 0          |                 |  |  |  |  |  |

|                 | 1               | Compare match in TPU channel 1          |                 |  |  |  |  |  |

| 1               | 0               | Compare match in TPU channel 2          |                 |  |  |  |  |  |

|                 | 1               | Compare match in TPU channel 3          | (Initial value) |  |  |  |  |  |

**Bits 3 and 2—Group 1 Compare Match Select 1 and 0 (G1CMS1, G1CMS0):** These bits select the compare match that triggers pulse output group 1 (pins PO7 to PO4).

|                 |                 | Description                             |                 |  |  |  |  |  |

|-----------------|-----------------|-----------------------------------------|-----------------|--|--|--|--|--|

| Bit 3<br>G1CMS1 | Bit 2<br>G1CMS0 | Output Trigger for Pulse Output Group 1 |                 |  |  |  |  |  |

| 0               | 0               | Compare match in TPU channel 0          |                 |  |  |  |  |  |

|                 | 1               | Compare match in TPU channel 1          |                 |  |  |  |  |  |

| 1               | 0               | Compare match in TPU channel 2          |                 |  |  |  |  |  |

|                 | 1               | Compare match in TPU channel 3          | (Initial value) |  |  |  |  |  |

**Bits 1 and 0—Group 0 Compare Match Select 1 and 0 (G0CMS1, G0CMS0):** These bits select the compare match that triggers pulse output group 0 (pins PO3 to PO0).

|                 |                 | Description                             |                 |

|-----------------|-----------------|-----------------------------------------|-----------------|

| Bit 1<br>G0CMS1 | Bit 0<br>G0CMS0 | Output Trigger for Pulse Output Group 0 |                 |

| 0               | 0               | Compare match in TPU channel 0          |                 |

|                 | 1               | Compare match in TPU channel 1          |                 |

| 1               | 0               | Compare match in TPU channel 2          |                 |

|                 | 1               | Compare match in TPU channel 3          | (Initial value) |

| Section 16 | A/D Converter | (8 Analog Inpu | t Channel Version) |

|------------|---------------|----------------|--------------------|

|------------|---------------|----------------|--------------------|

| Group<br>Selection | <b>Channel Selection</b> |     | Description            |                      |  |  |  |

|--------------------|--------------------------|-----|------------------------|----------------------|--|--|--|

| CH2                | CH1                      | CH0 | Single Mode (SCAN = 0) | Scan Mode (SCAN = 1) |  |  |  |

| 0                  | 0                        | 0   | AN0 (Initial value)    | AN0                  |  |  |  |

|                    |                          | 1   | AN1                    | AN0, AN1             |  |  |  |

|                    | 1                        | 0   | AN2                    | AN0 to AN2           |  |  |  |

|                    |                          | 1   | AN3                    | AN0 to AN3           |  |  |  |

| 1                  | 0                        | 0   | AN4                    | AN4                  |  |  |  |

|                    |                          | 1   | AN5                    | AN4, AN5             |  |  |  |

|                    | 1                        | 0   | AN6                    | AN4 to AN6           |  |  |  |

|                    |                          | 1   | AN7                    | AN4 to AN7           |  |  |  |

#### 16.2.3 A/D Control Register (ADCR)

| Bit        | :     | 7     | 6     | 5 | 4 | 3    | 2   | 1 | 0 |

|------------|-------|-------|-------|---|---|------|-----|---|---|

|            |       | TRGS1 | TRGS0 | _ | _ | CKS1 | CH3 |   |   |

| Initial va | lue : | 0     | 0     | 1 | 1 | 1    | 1   | 1 | 1 |

| R/W        | :     | R/W   | R/W   | — | — | R/W  | R/W | — | — |

ADCR is an 8-bit readable/writable register that enables or disables external triggering of A/D conversion operations.

ADCR is initialized to H'3F by a reset, and in standby mode or module stop mode.

**Bits 7 and 6—Timer Trigger Select 1 and 0 (TRGS1, TRGS0):** These bits select enabling or disabling of the start of A/D conversion by a trigger signal. Only set bits TRGS1 and TRGS0 while conversion is stopped (ADST = 0).

| Bit 7<br>TRGS1 | Bit 6<br>TRGS0 | Description                                                                         |

|----------------|----------------|-------------------------------------------------------------------------------------|

| 0              | 0              | A/D conversion start by external trigger is disabled (Initial value                 |

|                | 1              | A/D conversion start by external trigger (TPU) is enabled                           |

| 1              | 0              | A/D conversion start by external trigger (8-bit timer) is enabled                   |

|                | 1              | A/D conversion start by external trigger pin $(\overline{\text{ADTRG}})$ is enabled |

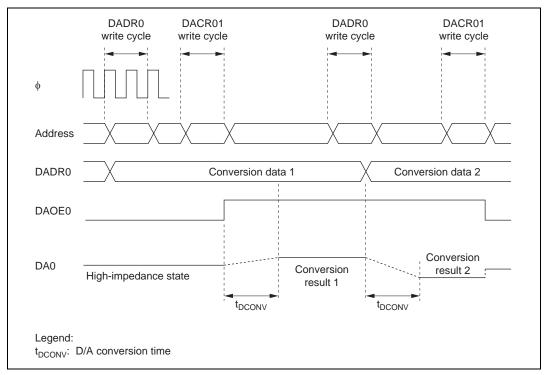

[2] Set the DAOE0 bit in DACR01 to 1. D/A conversion is started and the DA0 pin becomes an output pin. The conversion result is output after the conversion time has elapsed. The output value is expressed by the following formula:

$\frac{\text{DADR contents}}{256} \times V_{ref}$

The conversion results are output continuously until DADR0 is written to again or the DAOE0 bit is cleared to 0.

- [3] If DADR0 is written to again, the new data is immediately converted. The new conversion result is output after the conversion time has elapsed.

- [4] If the DAOE0 bit is cleared to 0, the DA0 pin becomes an input pin.

Figure 17.2 Example of D/A Converter Operation

#### Renesas

| Block (Size)     | Address              |

|------------------|----------------------|

| EB0 (4 kbytes)   | H'000000 to H'000FFF |

| EB1 (4 kbytes)   | H'001000 to H'001FFF |

| EB2 (4 kbytes)   | H'002000 to H'002FFF |

| EB3 (4 kbytes)   | H'003000 to H'003FFF |

| EB4 (4 kbytes)   | H'004000 to H'004FFF |

| EB5 (4 kbytes)   | H'005000 to H'005FFF |

| EB6 (4 kbytes)   | H'006000 to H'006FFF |

| EB7 (4 kbytes)   | H'007000 to H'007FFF |

| EB8 (32 kbytes)  | H'008000 to H'00FFFF |

| EB9 (64 kbytes)  | H'010000 to H'01FFFF |

| EB10 (64 kbytes) | H'020000 to H'02FFFF |

| EB11 (64 kbytes) | H'030000 to H'03FFFF |

| EB12 (64 kbytes) | H'040000 to H'04FFFF |

| EB13 (64 kbytes) | H'050000 to H'05FFFF |

Table 19.7

Flash Memory Erase Blocks

#### 19.5.5 System Control Register 2 (SYSCR2)

| Bit        | :      | 7 | 6 | 5 | 4 | 3     | 2 | 1 | 0   |

|------------|--------|---|---|---|---|-------|---|---|-----|

|            |        |   |   | _ | _ | FLSHE | _ | _ | —   |

| Initial va | alue : | 0 | 0 | 0 | 0 | 0     | 0 | 0 | 0   |

| R/W        | :      | _ | _ | _ | _ | R/W   | _ | _ | R/W |

SYSCR2 is an 8-bit readable/writable register that performs on-chip flash memory control.

SYSCR2 is initialized to H'00 by a reset and in hardware standby mode.

SYSCR2 can only be used in the F-ZTAT version. In the mask ROM version this register will return an undefined value if read, and cannot be modified.

Bits 7 to 4—Reserved: These bits cannot be modified and are always read as 0.

#### Renesas

#### 19.13.3 Flash Memory Operating Modes

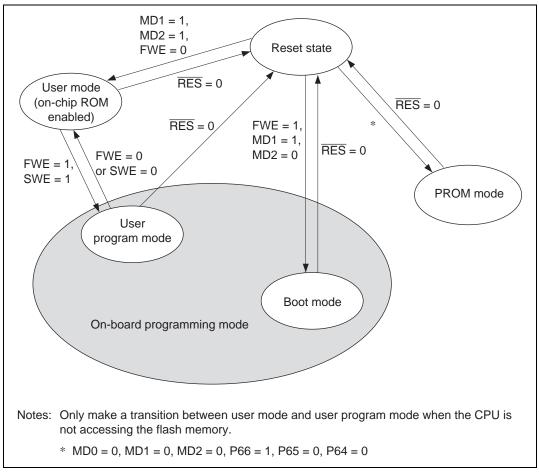

**Mode Transitions:** When the mode pins and the FWE pin are set in the reset state and a resetstart is executed, the chip enters one of the operating modes shown in figure 19.30. In user mode, flash memory can be read but not programmed or erased.

Flash memory can be programmed and erased in boot mode, user program mode, and PROM mode.

Figure 19.30 Flash Memory Mode Transitions

**Bit 3—RAM Select (RAMS):** Specifies selection or non-selection of flash memory emulation in RAM. When RAMS = 1, all flash memory blocks are program/erase-protected.

| Bit 3<br>RAMS | Description                                                     |                 |

|---------------|-----------------------------------------------------------------|-----------------|

| 0             | Emulation not selected                                          | (Initial value) |

|               | Program/erase-protection of all flash memory blocks is disabled |                 |

| 1             | Emulation selected                                              |                 |

|               | Program/erase-protection of all flash memory blocks is enabled  |                 |

**Bits 2 to 0—Flash Memory Area Selection (RAM2 to RAM0):** These bits are used together with bit 3 to select the flash memory area to be overlapped with RAM (see table 19.29).

#### Table 19.29 Flash Memory Area Divisions

| RAM Area             | Block Name         | RAMS | RAM2 | RAM1 | RAM0        |

|----------------------|--------------------|------|------|------|-------------|

| H'FFDC00 to H'FFEBFF | RAM area, 4 kbytes | 0    | *    | *    | *           |

| H'000000 to H'000FFF | EB0 (4 kbytes)     | 1    | 0    | 0    | 0           |

| H'001000 to H'001FFF | EB1 (4 kbytes)     | 1    | 0    | 0    | 1           |

| H'002000 to H'002FFF | EB2 (4 kbytes)     | 1    | 0    | 1    | 0           |

| H'003000 to H'003FFF | EB3 (4 kbytes)     | 1    | 0    | 1    | 1           |

| H'004000 to H'004FFF | EB4 (4 kbytes)     | 1    | 1    | 0    | 0           |

| H'005000 to H'005FFF | EB5 (4 kbytes)     | 1    | 1    | 0    | 1           |

| H'006000 to H'006FFF | EB6 (4 kbytes)     | 1    | 1    | 1    | 0           |

| H'007000 to H'007FFF | EB7 (4 kbytes)     | 1    | 1    | 1    | 1           |

|                      |                    |      |      |      | *. Dan't an |

\*: Don't care

|                   |                    | Cor                          |     |      |                 |

|-------------------|--------------------|------------------------------|-----|------|-----------------|

| Item              | Symbol             | Min                          | Max | Unit | Test Conditions |

| CAS setup time    | t <sub>CSR</sub>   | $0.5\times t_{\text{cyc}}-8$ | _   | ns   | Figure 22.10    |

| WAIT setup time   | t <sub>WTS</sub>   | 25                           | _   | ns   | Figure 22.8     |

| WAIT hold time    | t <sub>WTH</sub>   | 5                            | _   | ns   |                 |

| BREQ setup time   | t <sub>BRQS</sub>  | 30                           | _   | ns   | Figure 22.14    |

| BACK delay time   | t <sub>BACD</sub>  | _                            | 15  | ns   |                 |

| Bus floating time | t <sub>BZD</sub>   | _                            | 40  | ns   |                 |

| BREQO delay time  | t <sub>BRQOD</sub> | _                            | 25  | ns   | Figure 22.15    |

|                   |                    |                              |     |      |                 |

#### (4) DMAC Timing

#### Table 22.18 DMAC Timing

$\begin{array}{ll} \mbox{Condition B:} & V_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V}, \mbox{ AV}_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V}, \mbox{ V}_{ref} = 2.7 \mbox{ V to } AV_{CC}, \mbox{ V}_{SS} = AV_{SS} = 0 \mbox{ V}, \mbox{ } \phi = 2 \mbox{ MHz to } 25 \mbox{ MHz}, \mbox{ } T_a = -20^{\circ}\mbox{C to } 75^{\circ}\mbox{C} \mbox{ (regular specifications)}, \\ & T_a = -40^{\circ}\mbox{C to } 85^{\circ}\mbox{C} \mbox{ (wide-range specifications)} \end{array}$

|                   |                    | Co  | ndition B |      |                         |

|-------------------|--------------------|-----|-----------|------|-------------------------|

| Item              | Symbol             | Min | Max       | Unit | Test Conditions         |

| DREQ setup time   | t <sub>DRQS</sub>  | 25  | _         | ns   | Figure 22.19            |

| DREQ hold time    | t <sub>DRQH</sub>  | 10  | _         |      |                         |

| TEND delay time   | t <sub>TED</sub>   | _   | 18        |      | Figure 22.18            |

| DACK delay time 1 | t <sub>DACD1</sub> | _   | 18        | ns   | Figures 22.16 and 22.17 |

| DACK delay time 2 | t <sub>DACD2</sub> | _   | 18        |      |                         |

#### TIOR4—Timer I/O Control Register 4

#### H'FE92

**TPU4**

| Initial value : 0 0 0 0 0 0 0 0              | Bit        | :      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------------------------------------------|------------|--------|------|------|------|------|------|------|------|------|

|                                              |            |        | IOB3 | IOB2 | IOB1 | IOB0 | IOA3 | IOA2 | IOA1 | IOA0 |

| Read/Write · R/W R/W R/W R/W R/W R/W R/W R/W | Initial va | lue :  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|                                              | Read/W     | rite : | R/W  |

#### TGR4A I/O Control

|  |  | 0 | 0 | 0   | 0 | TGR4A<br>is output<br>compare | Output disabled                                                     |                                                                        |  |  |  |  |

|--|--|---|---|-----|---|-------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|

|  |  |   |   |     | 1 |                               | Initial output is 0                                                 | 0 output at compare match                                              |  |  |  |  |

|  |  |   |   | 1   | 0 | register                      | output 1 outpu                                                      | 1 output at compare match                                              |  |  |  |  |

|  |  |   |   |     | 1 | -                             |                                                                     | Toggle output at compare match                                         |  |  |  |  |

|  |  |   | 1 | 0   | 0 |                               | Output disabled                                                     |                                                                        |  |  |  |  |

|  |  |   |   |     | 1 |                               | Initial output is 1                                                 | 0 output at compare match                                              |  |  |  |  |

|  |  |   |   | 1 0 |   | output                        | 1 output at compare match                                           |                                                                        |  |  |  |  |

|  |  |   |   |     | 1 |                               |                                                                     | Toggle output at compare match                                         |  |  |  |  |

|  |  | 1 | 0 | 0   | 0 | TGR4A                         | Capture input                                                       | Input capture at rising edge                                           |  |  |  |  |

|  |  |   |   |     | 1 | is input capture              | source is<br>TIOCA₄ pin                                             | Input capture at falling edge                                          |  |  |  |  |

|  |  |   |   | 1   | * | register                      |                                                                     | Input capture at both edges                                            |  |  |  |  |

|  |  |   | 1 | *   | * |                               | Capture input<br>source is TGR3A<br>compare match/<br>input capture | Input capture at generation of<br>TGR3A compare match/input<br>capture |  |  |  |  |

\* : Don't care

#### TGR4B I/O Control

| 0 | 0                 | 0 | 0               | TGR4B                     | Output disabled                                                     |                                                                        |  |  |  |  |

|---|-------------------|---|-----------------|---------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|

|   |                   |   | 1               | is output<br>compare      | Initial output is 0 output                                          | 0 output at compare match                                              |  |  |  |  |

|   |                   | 1 | 0               | register                  | ouipui                                                              | 1 output at compare match                                              |  |  |  |  |

|   |                   |   | 1               |                           |                                                                     | Toggle output at compare match                                         |  |  |  |  |

|   | 1 0 0<br>1<br>1 0 |   | Output disabled |                           |                                                                     |                                                                        |  |  |  |  |

|   |                   |   | 1               |                           | Initial output is 1                                                 | 0 output at compare match                                              |  |  |  |  |

|   |                   |   | output          | 1 output at compare match |                                                                     |                                                                        |  |  |  |  |

|   |                   |   | 1               |                           |                                                                     | Toggle output at compare match                                         |  |  |  |  |

| 1 | 1 0               | 0 | 0               | TGR4B                     | Capture input                                                       | Input capture at rising edge                                           |  |  |  |  |

|   |                   |   | 1               | is input<br>capture       | source is<br>TIOCB <sub>4</sub> pin                                 | Input capture at falling edge                                          |  |  |  |  |

|   |                   | 1 | *               | register                  |                                                                     | Input capture at both edges                                            |  |  |  |  |

|   | 1                 | * | *               |                           | Capture input<br>source is TGR3C<br>compare match/<br>input capture | Input capture at generation of<br>TGR3C compare match/input<br>capture |  |  |  |  |

#### WCRL—Wait Control Register L

H'FED3

**Bus Controller**

| Bit           | : | 7   | 6    |     | 5         | 4                           |       | 3         | 2     |                                 | 1                              | 0   |  |  |  |

|---------------|---|-----|------|-----|-----------|-----------------------------|-------|-----------|-------|---------------------------------|--------------------------------|-----|--|--|--|

|               |   | W31 | W30  |     | W21       | W20                         |       | W11       | W1    | o                               | W01 W0                         |     |  |  |  |

| Initial value | : | 1   | 1    |     | 1         | 1                           |       | 1         | 1     |                                 | 1                              | 1   |  |  |  |

| Read/Write    | : | R/W | R/W  |     | R/W       | R/W                         |       | R/W       | R/V   | / R/W                           |                                | R/W |  |  |  |

|               |   |     |      |     |           |                             |       |           |       |                                 |                                |     |  |  |  |

|               |   |     |      |     |           |                             |       |           |       |                                 |                                |     |  |  |  |

|               |   |     |      |     |           |                             |       |           | Are   | Area 0 Wait Control             |                                |     |  |  |  |

|               |   |     |      |     |           |                             |       |           | 0     | 0 Program wait not inserted     |                                |     |  |  |  |

|               |   |     |      |     |           |                             |       |           |       | 1 1 program wait state inserted |                                |     |  |  |  |

|               |   |     |      |     |           |                             |       |           | 1     | 0                               | 2 program wait states inserted |     |  |  |  |

|               |   |     |      |     |           |                             |       |           | 1     | 3 program wait states inserted  |                                |     |  |  |  |

|               |   |     |      |     |           | Area 1 Wait Control         |       |           |       |                                 |                                |     |  |  |  |

|               |   |     |      |     |           | 0 0 Program wait not inse   |       |           |       |                                 |                                |     |  |  |  |

|               |   |     |      |     |           |                             | 1     | 1 progr   |       |                                 |                                |     |  |  |  |

|               |   |     |      |     |           | 1                           | 0     | 2 progr   | am wa | ait sta                         | ted                            |     |  |  |  |

|               |   |     |      |     |           |                             | 1     | 3 progr   | am wa | wait states inserted            |                                |     |  |  |  |

|               |   |     | Area | 2 W | ait Conti | rol                         |       | 1         |       |                                 |                                |     |  |  |  |

|               |   |     | 0    | 0   |           | -                           | not i | earted    |       |                                 |                                |     |  |  |  |

|               |   |     |      | -   | -         | rogram wait not inserted    |       |           |       |                                 |                                |     |  |  |  |

|               |   |     |      | 1   |           |                             |       |           |       |                                 |                                |     |  |  |  |

|               |   |     | 1    | 0   | 2 progr   | rogram wait states inserted |       |           |       |                                 |                                |     |  |  |  |

|               |   |     |      | 1   | 3 prog    | ram wai                     | t sta | tes inser | ted   |                                 |                                |     |  |  |  |

Area 3 Wait Control

| 0 | 0 | Program wait not inserted      |

|---|---|--------------------------------|

|   | 1 | 1 program wait state inserted  |

| 1 | 0 | 2 program wait states inserted |

|   | 1 | 3 program wait states inserted |

| ETCR0A—Tra<br>(Not                             | nsfer<br>t supj        |                  |        | ~      |        | H      | ['FE]  | E6  |       |     |     |       | ]     | DMAC  |      |       |

|------------------------------------------------|------------------------|------------------|--------|--------|--------|--------|--------|-----|-------|-----|-----|-------|-------|-------|------|-------|

| Bit :                                          | 15                     | 14               | 13     | 12     | 11     | 10     | 9      | 8   | 7     | 6   | 5   | 4     | 3     | 2     | 1    | 0     |

| ETCR0A :                                       |                        |                  |        |        |        |        |        |     |       |     |     |       |       |       |      |       |

| Initial value :                                | *                      | *                | *      | *      | *      | *      | *      | *   | *     | *   | *   | *     | *     | *     | *    | *     |

| Read/Write :                                   | R/W                    | R/W              | R/W    | R/W    | R/W    | R/W    | R/W    | R/W | R/W   | R/W | R/W | R/W   | R/W   | R/W   | R/W  | R/W   |

| Sequential<br>mode<br>Idle mode<br>Normal mode |                        | Transfer counter |        |        |        |        |        |     |       |     |     |       |       |       |      |       |

| Repeat mode                                    | Tra                    | insfe            | r num  | nber s | storaç | ge reç | gister |     |       |     | Tr  | ansf  | er co | unter |      |       |

| Block transfer mode                            |                        | Blocl            | k size | stor   | age r  | egiste | ər     |     |       |     | Blo | ock s | ize c | ounte | r    |       |

|                                                |                        |                  |        |        |        |        |        |     |       |     |     |       |       | *:    | Unde | fined |

| MAR0BH—Me                                      | •                      |                  |        | 0      | ·      |        | [      | H   | ['FE] | E8  |     |       |       |       | ]    | DMAC  |

| MAR0BL—Me                                      | t sup<br>mory<br>t sup | y Ado            | lress  | Reg    | ister  | OBL    |        | H   | ['FE] | EA  |     |       |       |       | ]    | DMAC  |

| Bit :                                          | 31                     | 30               | 29     | 28     | 27     | 26     | 25     | 24  | 23    | 22  | 21  | 20    | 19    | 18    | 17   | 16    |

| MAR0BH :                                       | _                      | _                | _      | _      | _      | _      | _      | _   |       |     |     |       |       |       |      |       |

| Initial value :                                | 0                      | 0                | 0      | 0      | 0      | 0      | 0      | 0   | *     | *   | *   | *     | *     | *     | *    | *     |

| Read/Write :                                   | _                      | _                | _      | _      | _      | _      | _      | _   | R/W   | R/W | R/W | R/W   | R/W   | R/W   | R/W  | R/W   |

| Bit :                                          | 15                     | 14               | 13     | 12     | 11     | 10     | 9      | 8   | 7     | 6   | 5   | 4     | 3     | 2     | 1    | 0     |

| MAR0BL :                                       |                        |                  |        |        |        |        |        |     |       |     |     |       |       |       |      |       |

| Initial value :                                | *                      | *                | *      | *      | *      | *      | *      | *   | *     | *   | *   | *     | *     | *     | *    | *     |

| Read/Write :                                   | R/W                    | R/W              | R/W    | R/W    | R/W    | R/W    | R/W    | R/W | R/W   | R/W | R/W | R/W   | R/W   |       | R/W  |       |

In short address mode: Specifies transfer source/transfer destination address In full address mode: Specifies transfer destination address

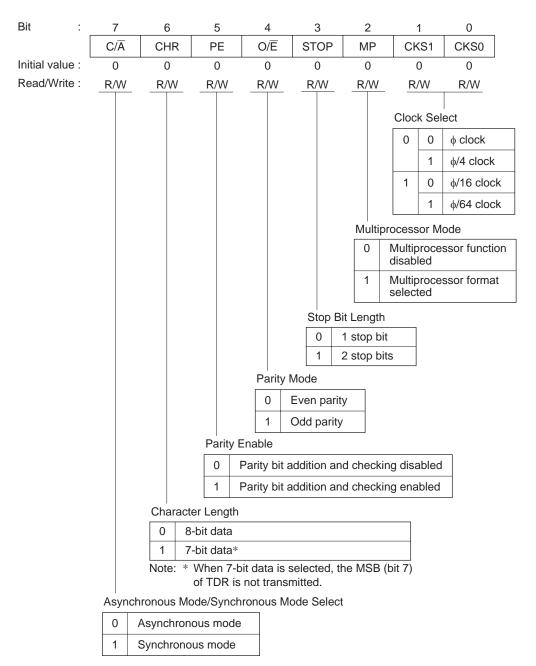

#### SMR0—Serial Mode Register 0

H'FF78

SCI0

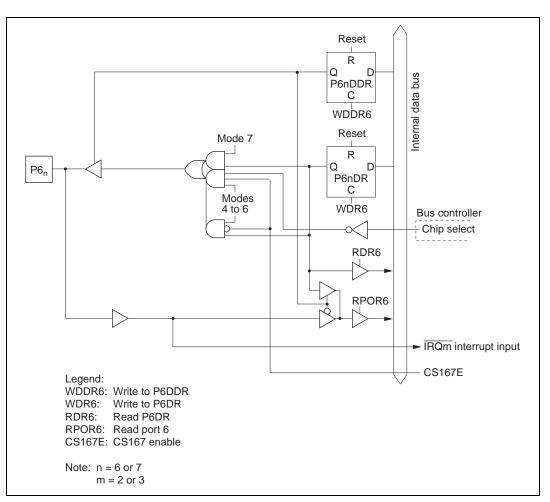

Figure C.6 (f) Port 6 Block Diagram (Pins P6<sub>6</sub> and P6<sub>7</sub>)