Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 25MHz                                                                          |

| Connectivity               | SCI, SmartCard                                                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 86                                                                             |

| Program Memory Size        | 384KB (384K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                    |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 120-TQFP                                                                       |

| Supplier Device Package    | 120-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2329evte25v |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 17.2.3  | Module Stop Control Register (MSTPCR)               | 728 |

|-------|---------|-----------------------------------------------------|-----|

| 17.3  |         | on                                                  |     |

|       | 1       |                                                     |     |

| Secti | on 18   | RAM                                                 | 731 |

| 18.1  | Overvie | PW                                                  | 731 |

|       | 18.1.1  | Block Diagram                                       | 731 |

|       | 18.1.2  | Register Configuration                              | 732 |

| 18.2  |         | r Descriptions                                      |     |

|       |         | System Control Register (SYSCR)                     |     |

| 18.3  |         | on                                                  |     |

| 18.4  | -       | Note                                                |     |

|       | U       |                                                     |     |

| Secti | on 19   | ROM                                                 | 735 |

| 19.1  | Overvie | ew                                                  | 735 |

|       | 19.1.1  | Block Diagram                                       | 735 |

|       | 19.1.2  | Register Configuration                              | 736 |

| 19.2  | Registe | r Descriptions                                      | 736 |

|       | 19.2.1  | Mode Control Register (MDCR)                        | 736 |

|       | 19.2.2  | Bus Control Register L (BCRL)                       | 737 |

| 19.3  | Operati | on                                                  | 737 |

| 19.4  | Overvie | ew of Flash Memory (H8S/2329B F-ZTAT)               | 740 |

|       | 19.4.1  | Features                                            | 740 |

|       | 19.4.2  | Overview                                            | 741 |

|       | 19.4.3  | Flash Memory Operating Modes                        | 742 |

|       |         | On-Board Programming Modes                          |     |

|       | 19.4.5  | Flash Memory Emulation in RAM                       | 745 |

|       |         | Differences between Boot Mode and User Program Mode |     |

|       | 19.4.7  | Block Configuration                                 | 747 |

|       | 19.4.8  | Pin Configuration                                   | 748 |

|       | 19.4.9  | Register Configuration                              | 749 |

| 19.5  | Registe | r Descriptions                                      | 750 |

|       | 19.5.1  | Flash Memory Control Register 1 (FLMCR1)            | 750 |

|       | 19.5.2  | Flash Memory Control Register 2 (FLMCR2)            | 753 |

|       | 19.5.3  | Erase Block Register 1 (EBR1)                       | 754 |

|       | 19.5.4  | Erase Block Registers 2 (EBR2)                      | 754 |

|       | 19.5.5  | System Control Register 2 (SYSCR2)                  | 755 |

|       | 19.5.6  | RAM Emulation Register (RAMER)                      | 756 |

| 19.6  |         | ard Programming Modes                               |     |

|       | 19.6.1  | Boot Mode                                           | 759 |

|       | 19.6.2  | User Program Mode                                   | 763 |

Section 2 CPU

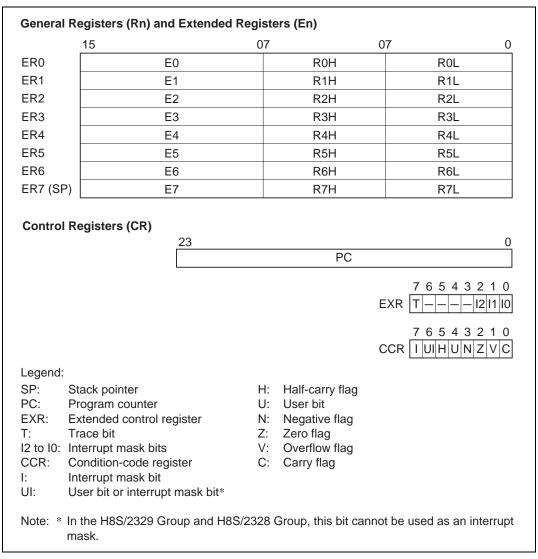

# 2.4 Register Configuration

### 2.4.1 Overview

The CPU has the internal registers shown in figure 2.4. There are two types of registers: general registers and control registers.

### Figure 2.4 CPU Registers

The CPU's architecture allows for 4 Gbytes of address space, but the H8S/2328B F-ZTAT and H8S/2326 F-ZTAT actually accesses a maximum of 16 Mbytes.

Modes 4 to 6 are externally expanded modes that allow access to external memory and peripheral devices.

The external expansion modes allow switching between 8-bit and 16-bit bus modes. After program execution starts, an 8-bit or 16-bit address space can be set for each area, depending on the bus controller setting. If 16-bit access is selected for any one area, 16-bit bus mode is set; if 8-bit access is selected for all areas, 8-bit bus mode is set. Note that the functions of each pin depend on the operating mode.

Modes 10, 11, 14, and 15 are boot modes and user program modes in which the flash memory can be programmed and erased. For details, see section 19, ROM.

The H8S/2328B F-ZTAT and H8S/2326 F-ZTAT can only be used in modes 4 to 7, 10, 11, 14, and 15. This means that the flash write enable pin and mode pins must be set to select one of these modes.

Do not change the inputs at the mode pins during operation.

### 3.1.2 Operating Mode Selection (Mask ROM and ROMless Versions, H8S/2329B F-ZTAT)

The ROMless and mask ROM versions have four operating modes (modes 4 to 7). H8S/2329B F-ZTAT has six operating modes (modes 2 to 7). The operating mode is determined by the mode pins (MD<sub>2</sub> to MD<sub>0</sub>). The CPU operating mode, enabling or disabling of on-chip ROM, and the initial bus width setting can be selected as shown in table 3.2.

Table 3.2 lists the MCU operating modes.

### 3.2.2 System Control Register (SYSCR)

| Bit         | :     | 7   | 6 | 5     | 4     | 3     | 2     | 1      | 0    |

|-------------|-------|-----|---|-------|-------|-------|-------|--------|------|

|             |       |     |   | INTM1 | INTM0 | NMIEG | LWROD | IRQPAS | RAME |

| Initial val | lue : | 0   | 0 | 0     | 0     | 0     | 0     | 0      | 1    |

| R/W         | :     | R/W | — | R/W   | R/W   | R/W   | R/W   | R/W    | R/W  |

Bit 7—Reserved: Only 0 should be written to this bit.

Bit 6—Reserved: This bit is always read as 0, and cannot be modified.

**Bits 5 and 4—Interrupt Control Mode 1 and 0 (INTM1, INTM0):** These bits select the control mode of the interrupt controller. For details of the interrupt control modes, see section 5.4.1, Interrupt Control Modes and Interrupt Operation.

| Bit 5<br>INTM1 | Bit 4<br>INTM0 | Interrupt Control<br>Mode | Description                            |                 |

|----------------|----------------|---------------------------|----------------------------------------|-----------------|

| 0              | 0              | 0                         | Control of interrupts by I bit         | (Initial value) |

|                | 1              | —                         | Setting prohibited                     |                 |

| 1              | 0              | 2                         | Control of interrupts by I2 to I0 bits | s and IPR       |

|                | 1              | —                         | Setting prohibited                     |                 |

Bit 3-NMI Edge Select (NMIEG): Selects the valid edge of the NMI interrupt input.

| Bit 3<br>NMIEG | Description                                                |                 |

|----------------|------------------------------------------------------------|-----------------|

| 0              | An interrupt is requested at the falling edge of NMI input | (Initial value) |

| 1              | An interrupt is requested at the rising edge of NMI input  |                 |

### Bit 2—LWR Output Disable (LWROD): Enables or disables LWR output.

| Bit 2<br>LWROD | Description                                                                            |                 |

|----------------|----------------------------------------------------------------------------------------|-----------------|

| 0              | $PF_3$ is designated as $\overline{LWR}$ output pin                                    | (Initial value) |

| 1              | $PF_3$ is designated as I/O port, and does not function as $\overline{LWR}$ output pin |                 |

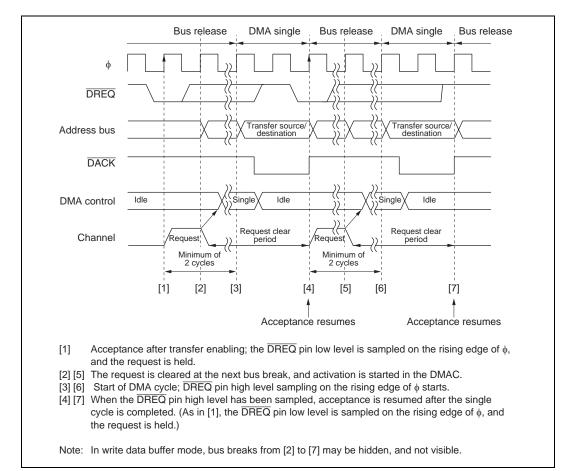

**DREQ Pin Falling Edge Activation Timing:** Set the DTA bit for the channel for which the DREQ pin is selected to 1.

Figure 7.31 shows an example of  $\overline{\text{DREQ}}$  pin falling edge activated single address mode transfer.

# Figure 7.31 Example of DREQ Pin Falling Edge Activated Single Address Mode Transfer

$\overline{\text{DREQ}}$  pin sampling is performed every cycle, with the rising edge of the next  $\phi$  cycle after the end of the DMABCR write cycle for setting the transfer enabled state as the starting point.

When the  $\overline{\text{DREQ}}$  pin low level is sampled while acceptance by means of the  $\overline{\text{DREQ}}$  pin is possible, the request is held in the DMAC. Then, when activation is initiated in the DMAC, the request is cleared, and  $\overline{\text{DREQ}}$  pin high level sampling for edge detection is started. If  $\overline{\text{DREQ}}$  pin high level sampling has been completed by the time the DMA single cycle ends, acceptance

# Renesas

### Port A Data Register (PADR)

| Bit         | :     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|             |       | PA7DR | PA6DR | PA5DR | PA4DR | PA3DR | PA2DR | PA1DR | PA0DR |

| Initial val | lue : | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W         | :     | R/W   |

PADR is an 8-bit readable/writable register that stores output data for the port A pins ( $PA_7$  to  $PA_0$ ).

PADR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

### **Port A Register (PORTA)**

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|            | ſ     | PA7 | PA6 | PA5 | PA4 | PA3 | PA2 | PA1 | PA0 |

| Initial va | lue : | *   | *   | *   | *   | *   | *   | *   | *   |

| R/W        | :     | R   | R   | R   | R   | R   | R   | R   | R   |

Note: \* Determined by state of pins PA7 to PA0.

PORTA is an 8-bit read-only register that shows the pin states. It cannot be written to. Writing of output data for the port A pins ( $PA_7$  to  $PA_0$ ) must always be performed on PADR.

If a port A read is performed while PADDR bits are set to 1, the PADR values are read. If a port A read is performed while PADDR bits are cleared to 0, the pin states are read.

After a reset and in hardware standby mode, PORTA contents are determined by the pin states, as PADDR and PADR are initialized. PORTA retains its prior state in software standby mode.

### 14.2.3 Transmit Shift Register (TSR)

TSR is a register used to transmit serial data.

To perform serial data transmission, the SCI first transfers transmit data from TDR to TSR, then sends the data to the TxD pin starting with the LSB (bit 0).

When transmission of one byte is completed, the next transmit data is transferred from TDR to TSR, and transmission started, automatically. However, data transfer from TDR to TSR is not performed if the TDRE bit in SSR is set to 1.

TSR cannot be directly read or written to by the CPU.

### 14.2.4 Transmit Data Register (TDR)

| Bit        | :      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|            |        |     |     |     |     |     |     |     |     |

| Initial va | alue : | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W        | :      | R/W |

TDR is an 8-bit register that stores data for serial transmission.

When the SCI detects that TSR is empty, it transfers the transmit data written in TDR to TSR and starts serial transmission. Continuous serial transmission can be carried out by writing the next transmit data to TDR during serial transmission of the data in TSR.

TDR can be read or written to by the CPU at all times.

TDR is initialized to H'FF by a reset, and in standby mode or module stop mode.

### Renesas

### **15.3.4** Register Settings

Table 15.3 shows a bit map of the registers used by the smart card interface.

Bits indicated as 0 or 1 must be set to the value shown. The setting of other bits is described below.

|          | Bit   |       |       |       |       |       |       |       |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| SMR      | GM    | BLK   | 1     | O/E   | BCP1  | BCP0  | CKS1  | CKS0  |

| BRR      | BRR7  | BRR6  | BRR5  | BRR4  | BRR3  | BRR2  | BRR1  | BRR0  |

| SCR      | TIE   | RIE   | TE    | RE    | 0     | 0     | CKE1* | CKE0  |

| TDR      | TDR7  | TDR6  | TDR5  | TDR4  | TDR3  | TDR2  | TDR1  | TDR0  |

| SSR      | TDRE  | RDRF  | ORER  | ERS   | PER   | TEND  | 0     | 0     |

| RDR      | RDR7  | RDR6  | RDR5  | RDR4  | RDR3  | RDR2  | RDR1  | RDR0  |

| SCMR     | _     | _     | _     | _     | SDIR  | SINV  | _     | SMIF  |

Table 15.3

Smart Card Interface Register Settings

Notes: —: Unused bit.

\* The CKE1 bit must be cleared to 0 when the GM bit in SMR is cleared to 0.

**SMR Settings:** The GM bit is cleared to 0 in normal smart card interface mode, and set to 1 in GSM mode. The  $O/\overline{E}$  bit is cleared to 0 if the IC card is of the direct convention type, and set to 1 if of the inverse convention type.

Bits CKS1 and CKS0 select the clock source of the built-in baud rate generator, and bits BCP1 and BCP0 select the number of base clock cycles during transfer of one bit. For details, see section 15.3.5, Clock.

The BLK bit is cleared to 0 when using the normal smart card interface mode, and set to 1 when using block transfer mode.

**BRR Setting:** BRR is used to set the bit rate. See section 15.3.5, Clock, for the method of calculating the value to be set.

**SCR Settings:** The function of the TIE, RIE, TE, and RE bits is the same as for the normal SCI. For details, see section 14, Serial Communication Interface (SCI).

Bits CKE1 and CKE0 specify the clock output. When the GM bit in SMR is cleared to 0, set these bits to B'00 if a clock is not to be output, or to B'01 if a clock is to be output. When the GM bit in SMR is set to 1, clock output is performed. The clock output can also be fixed high or low.

| H                                           | 3S/2329B F-ZTAT                                |                                    | Socket Adapter      | HN27C4096                                 | 6HG (40 Pins)                        |

|---------------------------------------------|------------------------------------------------|------------------------------------|---------------------|-------------------------------------------|--------------------------------------|

| TFP-120                                     | FP-128B                                        | Pin Name                           | (40-Pin Conversion) | Pin No.                                   | Pin Name                             |

| 2                                           | 6                                              | A <sub>0</sub>                     |                     | 21                                        | A <sub>0</sub>                       |

| 3                                           | 7                                              | A <sub>1</sub>                     |                     | 22                                        | A <sub>1</sub>                       |

| 4                                           | 8                                              | A <sub>2</sub>                     |                     | 23                                        | A <sub>2</sub>                       |

| 5                                           | 9                                              | A3                                 |                     | 24                                        | A <sub>3</sub>                       |

| 7                                           | 11                                             | A <sub>4</sub>                     |                     | 25                                        | A <sub>4</sub>                       |

| 8                                           | 12                                             | A <sub>5</sub>                     |                     | 26                                        | A <sub>5</sub>                       |

| 9                                           | 13                                             | A <sub>6</sub>                     |                     | 27                                        | A <sub>6</sub>                       |

| 10                                          | 14                                             | A <sub>7</sub>                     |                     | 28                                        | A <sub>7</sub>                       |

| 11                                          | 15                                             | A <sub>8</sub>                     |                     | 29                                        | A <sub>8</sub>                       |

| 12                                          | 16                                             | A <sub>9</sub>                     |                     | 31                                        | A <sub>9</sub>                       |

| 13                                          | 17                                             | A <sub>10</sub>                    |                     | 32                                        | A <sub>10</sub>                      |

| 14                                          | 18                                             | A <sub>11</sub>                    |                     | 33                                        | A <sub>11</sub>                      |

| 16                                          | 20                                             | A <sub>12</sub>                    |                     | 34                                        | A <sub>12</sub>                      |

| 17                                          | 20                                             | A <sub>12</sub>                    |                     | 35                                        | A <sub>13</sub>                      |

| 18                                          | 22                                             | A <sub>13</sub><br>A <sub>14</sub> |                     |                                           | A <sub>14</sub>                      |

| 19                                          | 23                                             | A <sub>14</sub>                    |                     | 37                                        | A <sub>15</sub>                      |

| 20                                          | 23                                             | A <sub>15</sub>                    |                     | 38                                        | A <sub>16</sub>                      |

| 20                                          | 25                                             |                                    |                     | 39                                        | A <sub>17</sub>                      |

| 22                                          | 26                                             | A <sub>17</sub><br>A <sub>18</sub> |                     | 10                                        | A <sub>18</sub>                      |

| 43                                          | 49                                             | D <sub>8</sub>                     |                     | 19                                        | I/O <sub>0</sub>                     |

| 44                                          | 50                                             | D <sub>8</sub>                     |                     | 18                                        | I/O <sub>1</sub>                     |

| 45                                          | 51                                             | D <sub>9</sub><br>D <sub>10</sub>  |                     | 17                                        | I/O <sub>2</sub>                     |

| 45                                          | 52                                             |                                    |                     | 16                                        | 1/O <sub>2</sub>                     |

| 48                                          | 54                                             | D <sub>11</sub>                    |                     | 10                                        | 1/O <sub>3</sub>                     |

| 48                                          | 55                                             | D <sub>12</sub>                    |                     | - 14                                      | 1/O <sub>4</sub>                     |

|                                             |                                                | D <sub>13</sub>                    |                     | 14                                        |                                      |

| 50<br>51                                    | 56<br>57                                       | D <sub>14</sub>                    |                     | 13                                        | I/O <sub>6</sub><br>I/O <sub>7</sub> |

|                                             | 76                                             | D <sub>15</sub>                    |                     | 2                                         |                                      |

| 68                                          | _                                              |                                    |                     | 2                                         | <u> </u>                             |

| 69                                          | 77                                             | OE                                 |                     | 3                                         | WE                                   |

| 67                                          | 75                                             | WE                                 |                     |                                           | FWE                                  |

| 72                                          | 80                                             | EMLE*3                             |                     | - 4 - 1, 40                               | V <sub>CC</sub>                      |

| 1, 30, 33, 52, 55,74,<br>75, 76, 81, 93, 94 | 5, 34, 39, 58, 61, 82,<br>83, 84, 89, 103, 104 | V <sub>cc</sub>                    |                     | 1, 40                                     |                                      |

| -, -, - ,, -                                |                                                |                                    |                     | 5, 6, 7                                   | V <sub>SS</sub><br>NC                |

| 6, 15, 24, 31, 32, 38,                      | 3, 10, 19, 28, 35, 36,                         |                                    |                     | 5, 6, 7                                   |                                      |

| 47, 59, 66, 79, 103,<br>104, 113, 114, 115  | 37, 38, 44, 53, 65,<br>67, 68, 74, 87, 99,     | V <sub>SS</sub>                    |                     | 9                                         | A <sub>20</sub>                      |

| 104, 113, 114, 115                          | 100, 113, 114, 123,                            | 00                                 |                     |                                           | A <sub>19</sub>                      |

|                                             | 124, 125                                       |                                    | *1                  | Legend:<br>EMLE: En                       | nulation enable                      |

| 73                                          | 81                                             | RES                                | Reset circuit       | I/O <sub>7</sub> to I/O <sub>0</sub> : Da |                                      |

| 77                                          | 85                                             | XTAL                               | *2                  |                                           | dress input                          |

| 78                                          | 86                                             | EXTAL                              | Oscillation circuit | CE: Ch                                    | ip enable                            |

| Othe                                        | rpins                                          | NC (OPEN)                          |                     | OE: Ou                                    | Itput enable                         |

Notes: 1. A reset oscillation stabilization time ( $t_{osc1}$ ) of at least 10 ms is required.

2. A 12 MHz crystal resonator should be used.

3. As the FWE pin becomes VCC in the H8S/2329B F-ZTAT, the EMLE pin is ignored in PROM mode.

This figure shows pin assignments, and does not show the entire socket adapter circuit.

### Figure 19.20 H8S/2329B F-ZTAT Socket Adapter Pin Assignments

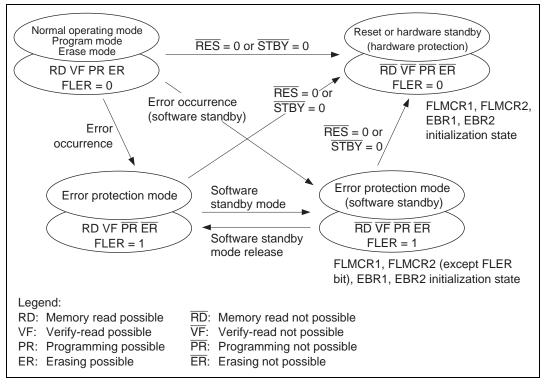

Error protection is released only by a reset and in hardware standby mode.

Figure 19.43 shows the flash memory state transition diagram.

Figure 19.43 Flash Memory State Transitions

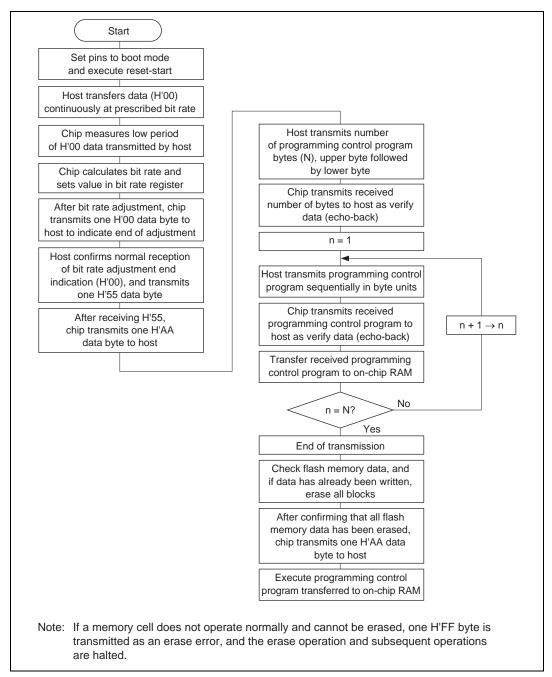

Figure 19.67 Boot Mode Execution Procedure

### 19.27.2 RAM Overlap

|          |                             | This area can be accessed<br>from both the RAM area<br>and flash memory area |

|----------|-----------------------------|------------------------------------------------------------------------------|

| H'000000 | EB0                         |                                                                              |

| H'001000 | EB1                         |                                                                              |

| H'002000 | EB2                         |                                                                              |

| H'030000 | EB3                         |                                                                              |

| H'004000 | EB4                         |                                                                              |

| H'005000 | EB5                         |                                                                              |

| H'006000 | EB6                         |                                                                              |

| H'007000 | EB7                         |                                                                              |

| H'008000 |                             |                                                                              |

|          | Flash memory<br>EB8 to EB15 | H'FFDC00<br>H'FFEBFF                                                         |

|          |                             | On-chip RAM                                                                  |

| H'07FFFF |                             | H'FFFBFF                                                                     |

An example in which flash memory block area EB1 is overlapped is shown below.

### Figure 19.75 Example of RAM Overlap Operation

#### Example in which Flash Memory Block Area EB1 is Overlapped

- 1. Set bits RAMS, RAM2, RAM1, and RAM0 in RAMER to 1, 0, 0, 1, to overlap part of RAM onto the area (EB1) for which real-time programming is required.

- 2. Real-time programming is performed using the overlapping RAM.

- 3. After the program data has been confirmed, the RAMS bit is cleared, releasing RAM overlap.

- 4. The data written in the overlapping RAM is written into the flash memory space (EB1).

- Notes: 1. When the RAMS bit is set to 1, program/erase protection is enabled for all blocks regardless of the value of RAM2, RAM1, and RAM0 (emulation protection). In this state, setting the P1 or E1 bit in flash memory control register 1 (FLMCR1), or setting

### 20.1.2 Register Configuration

The clock pulse generator is controlled by SCKCR. Table 20.1 shows the register configuration.

#### Table 20.1 Clock Pulse Generator Register

| Name                             | Abbreviation | R/W | Initial Value | Address* |

|----------------------------------|--------------|-----|---------------|----------|

| System clock control register    | SCKCR        | R/W | H'00          | H'FF3A   |

| Noto: *1 ower 16 bits of the odd | r000         |     |               |          |

Note: \* Lower 16 bits of the address.

### 20.2 Register Descriptions

#### 20.2.1 System Clock Control Register (SCKCR)

| Bit        | :      | 7     | 6   | 5   | 4 | 3 | 2    | 1    | 0    |

|------------|--------|-------|-----|-----|---|---|------|------|------|

|            |        | PSTOP | _   | DIV |   | _ | SCK2 | SCK1 | SCK0 |

| Initial va | alue : | 0     | 0   | 0   | 0 | 0 | 0    | 0    | 0    |

| R/W        | :      | R/W   | R/W | R/W | — | — | R/W  | R/W  | R/W  |

SCKCR is an 8-bit readable/writable register that controls  $\phi$  clock output, the medium-speed mode in which the bus master runs on a medium-speed clock and the other supporting modules run on the high-speed clock, and a function that allows the medium-speed mode to be disabled and the clock division ratio to be changed for the entire chip.

SCKCR is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in software standby mode.

|                |                               | Des         | cription                 |                          |

|----------------|-------------------------------|-------------|--------------------------|--------------------------|

| Bit 7<br>PSTOP | Normal Operation              | Sleep Mode  | Software<br>Standby Mode | Hardware<br>Standby Mode |

| 0              | $\phi$ output (Initial value) | <pre></pre> | Fixed high               | High impedance           |

| 1              | Fixed high                    | Fixed high  | Fixed high               | High impedance           |

Bit 6—Reserved: This bit can be read or written to, but only 0 should be written.

#### Table 22.3 DC Characteristics (H8S/2324S, H8S/2322R, H8S/2321, H8S/2320)

Conditions:  $V_{CC} = 2.7 \text{ V}$  to 3.6 V,  $AV_{CC} = 2.7 \text{ V}$  to 3.6 V,  $V_{ref} = 2.7 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}^{*1}$ ,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (widerange specifications)

| Item                                             |                                                                                                                                         | Symbol                                | Min                         | Тур | Мах                        | Unit | Test<br>Conditions                                                        |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|-----|----------------------------|------|---------------------------------------------------------------------------|

| Schmitt                                          | Ports 1, 2,                                                                                                                             | V <sub>T</sub> <sup>-</sup>           | $V_{CC} \times 0.2$         | _   | _                          | V    |                                                                           |

| trigger input voltage                            | P64 to P67                                                                                                                              | V <sub>T</sub> <sup>+</sup>           | _                           | _   | $V_{\text{CC}} \times 0.7$ | V    |                                                                           |

| vollage                                          | PA <sub>4</sub> to PA <sub>7</sub>                                                                                                      | $\overline{V_T}^+ - \overline{V_T}^-$ | $V_{\text{CC}} \times 0.06$ | _   | _                          | V    | _                                                                         |

|                                                  | Port 5 (when using IRQ)                                                                                                                 |                                       |                             |     |                            |      |                                                                           |

| Input high<br>voltage                            | $\begin{tabular}{l} \hline RES, \end{tabular} \overline{STBY}, \end{tabular} NMI, \\ MD_2 \mbox{ to } MD_0 \end{tabular}$               | VIH                                   | $V_{CC} \times 0.9$         | —   | V <sub>CC</sub> + 0.3      | V    |                                                                           |

|                                                  | EXTAL                                                                                                                                   | _                                     | $V_{CC} \times 0.7$         | _   | V <sub>CC</sub> + 0.3      | V    |                                                                           |

|                                                  | Ports 3, 5,<br>B to G, $P6_0$ to $P6_3$ ,<br>$PA_0$ to $PA_3$                                                                           | _                                     | 2.2                         | _   | V <sub>CC</sub> + 0.3      | V    | _                                                                         |

|                                                  | Port 4                                                                                                                                  | -                                     | 2.2                         | _   | $AV_{CC} + 0.3$            | 3V   |                                                                           |

| Input low<br>voltage                             | $\overline{\text{RES}}, \overline{\text{STBY}}, \\ \text{MD}_2 \text{ to } \text{MD}_0$                                                 | VIL                                   | -0.3                        |     | $V_{CC} \times 0.1$        | V    |                                                                           |

|                                                  | $\label{eq:NMI} \begin{array}{l} NMI, EXTAL, \\ Ports \ 3 \ to \ 5, \\ B \ to \ G, \ P6_0 \ to \ P6_3, \\ PA_0 \ to \ PA_3 \end{array}$ | _                                     | -0.3                        | _   | $V_{CC} 	imes 0.2$         | V    | _                                                                         |

| Output high                                      | All output pins                                                                                                                         | V <sub>OH</sub>                       | $V_{CC}-0.5$                | _   | _                          | V    | I <sub>OH</sub> = -200 μA                                                 |

| voltage                                          |                                                                                                                                         |                                       | $V_{CC} - 1.0$              | —   | _                          | V    | $I_{OH} = -1 \text{ mA}$                                                  |

| Output low voltage                               | All output pins                                                                                                                         | V <sub>OL</sub>                       | —                           | —   | 0.4                        | V    | I <sub>OL</sub> = 1.6 mA                                                  |

| Input                                            | RES                                                                                                                                     | I <sub>in</sub>                       | _                           | _   | 10.0                       | μA   | $V_{in} = 0.5 V to$                                                       |

| leakage<br>current                               | STBY, NMI,<br>MD <sub>2</sub> to MD <sub>0</sub>                                                                                        | _                                     | _                           | —   | 1.0                        | μΑ   | <sup></sup> V <sub>CC</sub> 0.5 V                                         |

|                                                  | Port 4                                                                                                                                  | _                                     |                             |     | 1.0 μA                     |      | $\begin{array}{l} V_{in} = 0.5 \ V \ to \\ AV_{CC} - 0.5 \ V \end{array}$ |

| Three-state<br>leakage<br>current<br>(off state) | Ports 1, 2, 3, 5, 6, <i>A</i> to G                                                                                                      | A  I <sub>TSI</sub>                   |                             |     | 1.0                        | μA   | $V_{in} = 0.5 \text{ V to}$ $V_{CC} - 0.5 \text{ V}$                      |

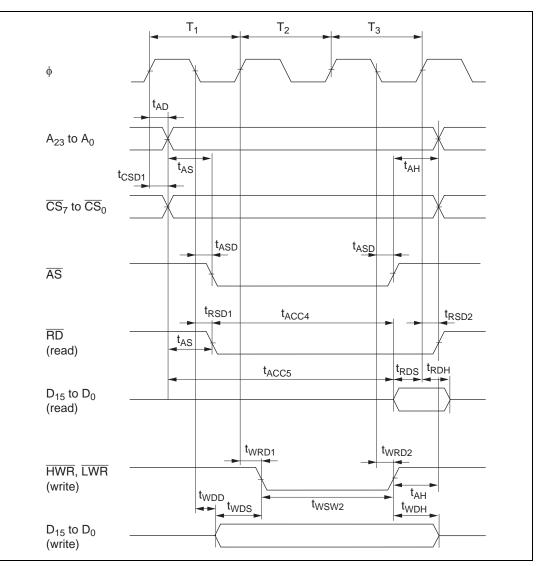

Figure 22.7 Basic Bus Timing (3-State Access)

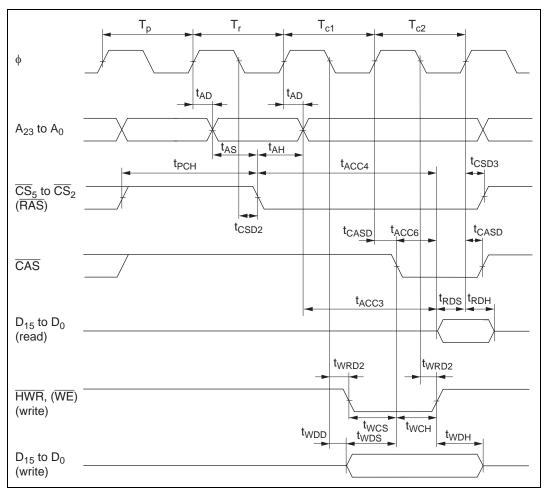

Figure 22.9 DRAM Bus Timing (Not Supported in the H8S/2321)

#### 22.2.6 Flash Memory Characteristics

#### **Table 22.22 Flash Memory Characteristics**

Conditions:  $V_{CC} = 3.0 \text{ V}$  to 3.6 V,  $AV_{CC} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $T_a = 0^{\circ}$ C to  $+75^{\circ}$ C (program/erase operating temperature range: regular specifications),  $T_a = 0^{\circ}$ C to  $+85^{\circ}$ C (program/erase operating temperature range: wide-range specifications)

| Item                       |                                                | Sym              | nbol | Min               | Тур     | Мах    | Unit               | Test<br>Conditions                     |

|----------------------------|------------------------------------------------|------------------|------|-------------------|---------|--------|--------------------|----------------------------------------|

| Programming                |                                                | t₽               |      | —                 | 10      | 200    | ms/<br>128 bytes   |                                        |

| Erase time <sup>*1 *</sup> | 3 *6                                           | t <sub>E</sub>   |      | _                 | 50      | 1000   | ms/block           |                                        |

| Rewrite times              |                                                | $N_{\text{WE}}$  | с    | 100 <sup>*7</sup> | 10000*8 | _      | Times              |                                        |

| Data hold time             |                                                | t <sub>DRP</sub> | *9   | 10                | _       | _      | year               |                                        |

| Programming                | Wait time after SWE bit setting <sup>*1</sup>  | х                |      | 1                 | —       | _      | μS                 |                                        |

|                            | Wait time after PSU bit setting <sup>*1</sup>  | у                |      | 50                | —       | _      | μS                 |                                        |

|                            | Wait time after P bit setting <sup>*1 *4</sup> | Z                | (z1) | —                 | _       | 30     | μS                 | $1 \le n \le 6$                        |

|                            |                                                |                  | (z2) | _                 | —       | 200    | μS                 | $7 \le n \le 1000$                     |

|                            |                                                |                  | (z3) | —                 | _       | 10     | μS                 | Wait time for<br>additional<br>writing |

|                            | Wait time after P bit clearing <sup>*1</sup>   | α                |      | 5                 | —       | _      | μS                 |                                        |

|                            | Wait time after PSU bit clearing <sup>*1</sup> | β                |      | 5                 | _       | —      | μS                 |                                        |

|                            | Wait time after PV bit setting <sup>*1</sup>   | γ                |      | 4                 | —       | _      | μS                 |                                        |

|                            | Wait time after H'FF dummy write <sup>*1</sup> | з                |      | 2                 | —       | —      | μS                 |                                        |

|                            | Wait time after PV bit clearing <sup>*1</sup>  |                  |      | 2                 | _       | _      | μS                 |                                        |

|                            | Wait time after SWE bit clearing <sup>*1</sup> |                  |      | 100               | —       | —      | μS                 |                                        |

|                            | Maximum number of writes *1 *4                 | Ν                |      | —                 | —       | 1000*5 | <sup>3</sup> Times |                                        |

| Erasing                    | Wait time after SWE bit setting $^{*1}$        | х                |      | 1                 | —       | _      | μS                 |                                        |

|                            | Wait time after ESU bit setting <sup>*1</sup>  | у                |      | 100               | —       | —      | μS                 |                                        |

|                            | Wait time after E bit setting <sup>*1 *6</sup> | z                |      | —                 | _       | 10     | ms                 | Wait time for erase time               |

|                            | Wait time after E bit clearing <sup>*1</sup>   | α                |      | 10                | —       | _      | μS                 |                                        |

|                            | Wait time after ESU bit clearing <sup>*1</sup> | β                |      | 10                | _       | _      | μS                 |                                        |

|                            | Wait time after EV bit setting <sup>*1</sup>   | γ                |      | 20                | —       | _      | μS                 |                                        |

|                            | Wait time after H'FF dummy write <sup>*1</sup> | 3                |      | 2                 | _       | —      | μS                 |                                        |

|                            | Wait time after EV bit clearing <sup>*1</sup>  | η                |      | 4                 | _       | —      | μS                 |                                        |

|                            | Wait time after SWE bit clearing <sup>*1</sup> | θ                |      | 100               | _       | _      | μS                 |                                        |

|                            | Maximum number of erases <sup>*1 *6</sup>      | Ν                |      | _                 | _       | 100    | Times              |                                        |

| Instruc- | Macmonic           | 6    |          |     |          |     |          |     |       |          | Inst     | ructior | Instruction Format |          |          |          |           |

|----------|--------------------|------|----------|-----|----------|-----|----------|-----|-------|----------|----------|---------|--------------------|----------|----------|----------|-----------|

| tion     |                    | Size | 1st byte | yte | 2nd byte | yte | 3rd byte | yte | 4th   | 4th byte | 5th byte | yte     | 6th byte           | 7th byte | 8th byte | 9th byte | 10th byte |

| BIST     | BIST #xx:3,Rd      | ш    | 9        | 7   | 1 IMM    | гq  |          |     |       |          |          |         |                    |          |          |          |           |

|          | BIST #xx:3,@ERd    | В    | 7        | D   | 0 erd    | 0   | 9        | 7   | 1 IMM | 0        |          |         |                    |          |          |          |           |

|          | BIST #xx:3,@aa:8   | ш    | 7        | ш   | abs      | s   | 9        | 7   | 1 IMM | 0        |          |         |                    |          |          |          |           |

|          | BIST #xx:3,@aa:16  | ш    | 9        | A   | -        | 8   |          | a   | abs   |          | 9        | 7       | 1 IMM 0            |          |          |          |           |

|          | BIST #xx:3,@aa:32  | ۵    | 9        | A   | e        | 8   |          |     |       | abs      | SC       |         |                    | 6 7      | 1 IMM 0  |          |           |

| BIXOR    | BIXOR #xx:3,Rd     | В    | 7        | 5   | 1 IMM    | rd  |          |     |       |          |          |         |                    |          |          |          |           |

|          | BIXOR #xx:3,@ERd   | m    | 7        | ပ   | 0 erd    | 0   | 7        | 5   | 1 IMM | 0        |          |         |                    |          |          |          |           |

|          | BIXOR #xx:3,@aa:8  | В    | 7        | ш   | abs      | s   | 7        | 5   | 1 IMM | 0        |          |         |                    |          |          |          |           |

|          | BIXOR #xx:3,@aa:16 | ۵    | 9        | A   | -        | 0   |          | a   | abs   |          | ~        | 5       | 1 IMM 0            |          |          |          |           |

|          | BIXOR #xx:3,@aa:32 | ш    | 9        | A   | ę        | 0   |          |     |       | abs      | s        |         |                    | 7 5      | 1 IMM 0  |          |           |

| BLD      | BLD #xx:3,Rd       | ш    | ~        | 7   | 0 IMM    | rd  |          |     |       |          |          |         |                    |          |          |          |           |

|          | BLD #xx:3,@ERd     | В    | 7        | c   | 0 erd    | 0   | 7        | 7   | 0 IMM | 0        |          |         |                    |          |          |          |           |

|          | BLD #xx:3,@aa:8    | в    | 7        | ш   | abs      | s   | 7        | 7   | 0 IMM | 0        |          |         |                    |          |          |          |           |

|          | BLD #xx:3,@aa:16   | В    | 9        | А   | +        | 0   |          | a   | abs   |          | 7        | 7 0     | 0 IMM 0            |          |          |          |           |

|          | BLD #xx:3,@aa:32   | В    | 9        | А   | 3        | 0   |          |     |       | abs      | S        |         |                    | 7 7      | 0 MMM 0  |          |           |

| BNOT     | BNOT #xx:3,Rd      | в    | 7        | -   | 0 IMM    | rd  |          |     |       |          |          |         |                    |          |          |          |           |

|          | BNOT #xx:3,@ERd    | В    | 7        | D   | 0 erd    | 0   | 7        | -   | 0 IMM | 0        |          |         |                    |          |          |          |           |

|          | BNOT #xx:3,@aa:8   | В    | 7        | ш   | abs      | s   | 7        | -   | 0 IMM | 0        |          |         |                    |          |          |          |           |

|          | BNOT #xx:3,@aa:16  | В    | 9        | A   | -        | 8   |          | a   | abs   |          | 7        | 1       | 0 IMM 0            |          |          |          |           |

|          | BNOT #xx:3,@aa:32  | ш    | 9        | A   | e        | 8   |          |     |       | abs      | S        |         |                    | 7 1      | 0 IMM 0  |          |           |

|          | BNOT Rn,Rd         | в    | 9        | -   | E        | p   |          |     |       |          |          |         |                    |          |          |          |           |

|          | BNOT Rn, @ERd      | В    | 7        | D   | 0 erd    | 0   | 9        | ٢   | E     | 0        |          |         |                    |          |          |          |           |

|          | BNOT Rn, @aa:8     | ш    | 7        | ш   | abs      | s   | 9        | ~   | E     | 0        |          |         |                    |          |          |          |           |

|          | BNOT Rn, @aa:16    | В    | 9        | А   | +        | 8   |          | a   | abs   |          | 9        | -       | rn 0               |          |          |          |           |

|          | BNOT Rn, @aa:32    | ш    | 9        | A   | ε        | 8   |          |     |       | abs      | S        |         |                    | 6 1      | 0<br>E   |          |           |

### **PFDDR—Port F Data Direction Register**

| Bit           | : | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|---|--------|--------|--------|--------|--------|--------|--------|--------|

|               |   | PF7DDR | PF6DDR | PF5DDR | PF4DDR | PF3DDR | PF2DDR | PF1DDR | PF0DDR |

| Modes 4 to 6  |   |        |        |        |        |        |        |        |        |

| Initial value | : | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | : | W      | W      | W      | W      | W      | W      | W      | W      |

| Mode 7        |   |        |        |        |        |        |        |        |        |

| Initial value | : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | : | W      | W      | W      | W      | W      | W      | W      | W      |

|               |   |        |        |        |        |        |        |        |        |

Specify input or output for individual port F pins

**H'FEBE**

| PGDDR—Por     | t G | a Data Dir | ection Re | egister   | H      | FEBF   |        |        | Port G |

|---------------|-----|------------|-----------|-----------|--------|--------|--------|--------|--------|

| Bit           | :   | 7          | 6         | 5         | 4      | 3      | 2      | 1      | 0      |

|               |     | _          | _         | _         | PG4DDR | PG3DDR | PG2DDR | PG1DDR | PG0DDR |

| Modes 4 and   | 5   |            |           | 1         |        | 1      | I      | 1      |        |

| Initial value | :   | Undefined  | Undefined | Undefined | 1      | 0      | 0      | 0      | 0      |

| Read/Write    | :   |            | _         | _         | W      | W      | W      | W      | W      |

| Modes 6 and   | 7   |            |           |           |        |        |        |        |        |

| Initial value | :   | Undefined  | Undefined | Undefined | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | :   | —          | _         | _         | W      | W      | W      | W      | W      |

|               |     |            |           |           |        |        |        |        |        |

|               |     |            |           |           |        |        |        |        |        |

Specify input or output for individual port G pins

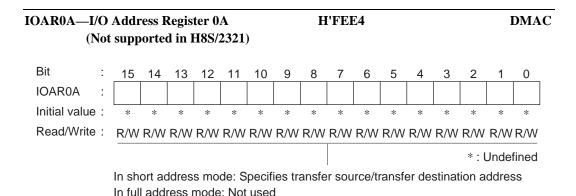

| MAR0AH—M        |                           |      |       | -   |       |     | I   | ł   | I'FE | EO  |     |     |     |     |      | DMAC   |

|-----------------|---------------------------|------|-------|-----|-------|-----|-----|-----|------|-----|-----|-----|-----|-----|------|--------|

| MAR0AL—Mo       | ot suj<br>emory<br>ot suj | y Ad | dress | Reg | ister | 0AL | ı   | I   | I'FE | E2  |     |     |     |     |      | DMAC   |

| Bit :           | 31                        | 30   | 29    | 28  | 27    | 26  | 25  | 24  | 23   | 22  | 21  | 20  | 19  | 18  | 17   | 16     |

| MAR0AH :        | _                         | _    | _     | _   | _     | —   | _   | _   |      |     |     |     |     |     |      |        |

| Initial value : | 0                         | 0    | 0     | 0   | 0     | 0   | 0   | 0   | *    | *   | *   | *   | *   | *   | *    | *      |

| Read/Write :    | —                         | —    | —     | —   | —     | _   | —   | —   | R/W  | R/W | R/W | R/W | R/W | R/W | R/W  | R/W    |

| Bit :           | 15                        | 14   | 13    | 12  | 11    | 10  | 9   | 8   | 7    | 6   | 5   | 4   | 3   | 2   | 1    | 0      |

| MAR0AL :        |                           |      |       |     |       |     |     |     |      |     |     |     |     |     |      |        |

| Initial value : | *                         | *    | *     | *   | *     | *   | *   | *   | *    | *   | *   | *   | *   | *   | *    | *      |

| Read/Write :    | R/W                       | R/W  | R/W   | R/W | R/W   | R/W | R/W | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W  | R/W    |

|                 |                           |      |       |     |       |     |     |     |      |     |     |     |     | *:  | Unde | efined |

In short address mode: Specifies transfer source/transfer destination address In full address mode: Specifies transfer source address