Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | Н8/300Н                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 4MHz                                                                          |

| Connectivity               | I²C, IrDA, SCI, SSU                                                           |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 13                                                                            |

| Program Memory Size        | 16KB (16K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 6x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 32-VFQFN                                                                      |

| Supplier Device Package    | 32-VQFN (5x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38602rft4v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

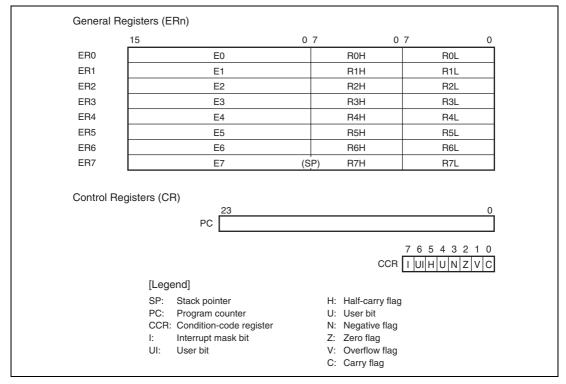

## 2.2 Register Configuration

The H8/300H CPU has the internal registers shown in figure 2.2. There are two types of registers; general registers and control registers. The control registers are a 24-bit program counter (PC), and an 8-bit condition-code register (CCR).

Figure 2.2 CPU Registers

#### 2.3.2 Memory Data Formats

Figure 2.6 shows the data formats in memory. The H8/300H CPU can access word data and longword data in memory, however word or longword data must begin at an even address. If an attempt is made to access word or longword data at an odd address, an address error does not occur, however the least significant bit of the address is regarded as 0, so access begins the preceding address. This also applies to instruction fetches.

When ER7 (SP) is used as an address register to access the stack area, the operand size should be word or longword.

| Data Type     | Address                                                    | Da    | ata Forma | t   |  |

|---------------|------------------------------------------------------------|-------|-----------|-----|--|

|               | ĺ                                                          | 7     |           | 0   |  |

| 1-bit data    | Address L                                                  | 7 6 5 | 4 3 2     | 1 0 |  |

| Byte data     | Address L                                                  | ISB   |           | LSB |  |

| Word data     | Address 2M<br>Address 2M+1                                 | ISB   |           | LSB |  |

| Longword data | Address 2N<br>Address 2N+1<br>Address 2N+2<br>Address 2N+3 | ISB   |           | LSB |  |

|               |                                                            |       |           |     |  |

Figure 2.6 Memory Data Formats

| Source Origin                 | Exception Sources                   | Vector<br>Number | Vector Address   | Priority   |

|-------------------------------|-------------------------------------|------------------|------------------|------------|

| WDT                           | WDT overflow (interval timer)       | 31               | H'003E to H'003F | High       |

| Asynchronous<br>event counter | Asynchronous event counter overflow | 32               | H'0040 to H'0041 | _ <b>≜</b> |

| Timer B1                      | Overflow                            | 33               | H'0042 to H'0043 | -          |

| Synchronous serial            | Overrun error (SSU)                 | 34               | H'0044 to H'0045 | -          |

| communication unit            | Transmit data empty (SSU)           |                  |                  |            |

| (SSU)/                        | Transmit end (SSU)                  |                  |                  |            |

|                               | Receive data full (SSU)             |                  |                  |            |

|                               | Conflict error (SSU)/               |                  |                  |            |

| IIC2*                         | Transmit data empty (IIC2)          |                  |                  |            |

|                               | Transmit end (IIC2)                 |                  |                  |            |

|                               | Receive data full (IIC2)            |                  |                  |            |

|                               | NACK detection (IIC2)               |                  |                  |            |

|                               | Arbitration (IIC2)                  |                  |                  |            |

|                               | Overrun error (IIC2)                |                  |                  |            |

| Timer W                       | Input capture A/compare match A     | 35               | H'0046 to H'0047 | -          |

|                               | Input capture B/compare match B     |                  |                  |            |

|                               | Input capture C/compare match C     |                  |                  |            |

|                               | Input capture D/compare match D     |                  |                  |            |

|                               | Overflow                            |                  |                  |            |

|                               | Reserved for system use             | 36               | H'0048 to H'0049 | -          |

| SCI3                          | Transmit end                        | 37               | H'004A to H'004B | -          |

|                               | Transmit data empty                 |                  |                  |            |

|                               | Receive data full                   |                  |                  |            |

|                               | Overrun error                       |                  |                  |            |

|                               | Framing error                       |                  |                  |            |

|                               | Parity error                        |                  |                  |            |

| A/D converter                 | A/D conversion end                  | 38               | H'004C to H'004D | - 🖌        |

|                               | Reserved for system use             | 39               | H'004E to H'004F | Low        |

Note: \* The SSU and IIC share the same vector address. When using the IIC, shift the SSU to standby mode using CKSTPR2.

#### 3.4.3 Interrupt Enable Register 2 (IENR2)

IENR2 enables the A/D converter, timer B1, and asynchronous event counter interrupts.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                            |

|--------|----------|------------------|-----|----------------------------------------------------------------------------------------|

| 7      | _        | 0                | _   | Reserved                                                                               |

|        |          |                  |     | The write value should always be 0.                                                    |

| 6      | IENAD    | 0                | R/W | A/D Converter Interrupt Request Enable                                                 |

|        |          |                  |     | The A/D converter interrupt request is enabled when this bit is set to 1.              |

| 5 to 3 |          | All 0            |     | Reserved                                                                               |

|        |          |                  |     | The write value should always be 0.                                                    |

| 2      | IENTB1   | 0                | R/W | Timer B1 Interrupt Request Enable                                                      |

|        |          |                  |     | The timer B1 interrupt request is enabled when this bit is set to 1.                   |

| 1      |          | 0                |     | Reserved                                                                               |

|        |          |                  |     | The write value should always be 0.                                                    |

| 0      | IENEC    | 0                | R/W | Asynchronous Event Counter Interrupt Request Enable                                    |

|        |          |                  |     | The asynchronous event counter interrupt request is enabled when this bit is set to 1. |

## 5.2 Mode Transitions and States of LSI

Figure 5.1 shows the possible transitions among these operating modes. A transition is made from the program execution state to the program halt state of the program by executing a SLEEP instruction. Interrupts allow for returning from the program halt state to the program execution state of the program. A direct transition between active mode and subactive mode, which are both program execution states, can be made without halting the program. The operating frequency can also be changed in the same modes by making a transition directly from active mode to active mode, and from subactive mode to subactive mode. RES input enables transitions from a mode to the reset state. Table 5.2 shows the transition conditions of each mode after the SLEEP instruction is executed and a mode to return by an interrupt. Table 5.3 shows the internal states of the LSI in each mode.

## 6.4 Flash Memory Programming/Erasure

A software method using the CPU is employed to program and erase flash memory in the onboard programming modes. Depending on the FLMCR1 setting, the flash memory operates in one of the following four modes: Programming mode, programming-verifying mode, erasing mode, and erasing-verifying mode. The programming control program in boot mode and the user programming/erasing control program in user program mode use these operating modes in combination to perform programming/erasure. Flash memory programming and erasing should be performed in accordance with the descriptions in section 6.4.1, Programming/Programming-Verifying and section 6.4.2, Erasing/Erasing-Verifying, respectively.

### 6.4.1 Programming/Programming-Verifying

When writing data or programs to the flash memory, the programming/programming-verifying flowchart shown in figure 6.3 should be followed. Performing programming operations according to this flowchart will enable data or programs to be written to the flash memory without subjecting the chip to voltage stress or sacrificing program data reliability.

- 1. Programming must be performed on an erased area. Do not reprogram an address to which data has already been programmed.

- 2. Programming should be carried out 128 bytes at a time. A 128-byte data transfer must be performed even if programming fewer than 128 bytes. In this case, the remaining area must be filled with H'FF.

- 3. Prepare the following data storage areas in RAM: A 128-byte programming data area, a 128-byte reprogramming data area, and a 128-byte additional-programming data area. Perform reprogramming data computation according to table 6.4, and additional programming data computation according to table 6.5.

- 4. Consecutively transfer 128 bytes of data in bytes from the reprogramming data area or additional-programming data area to the flash memory. The programming address and 128-byte data are latched in the flash memory. The lower eight bits of the start address in the flash memory destination area must be H'00 or H'80.

- 5. The time during which the P bit is set to 1 is the programming time. Table 6.6 shows the allowable programming times.

- 6. The watchdog timer (WDT) is set to prevent overprogramming due to program runaway, etc. An overflow cycle of approximately 6.6 ms is allowed.

- 7. For a dummy write to a verifying address, write 1-byte of data H'FF to an address whose lower two bits are B'00. Verifying data can be read in words or in longwords from the address to which a dummy write was performed.

# Section 7 RAM

This LSI has an on-chip high-speed static RAM. The RAM is connected to the CPU by a 16-bit data bus, enabling two-state access by the CPU to both byte data and word data.

| Product Classification |            | RAM Size  | RAM Address      |

|------------------------|------------|-----------|------------------|

| Flash memory version   | H8/38602RF | 1 Kbyte   | H'FB80 to H'FF7F |

| Masked ROM version     | H8/38602R  | 1 Kbyte   | H'FB80 to H'FF7F |

|                        | H8/38600R  | 512 bytes | H'FD80 to H'FF7F |

### 8.2.6 Input Pull-Up MOS

Port 3 has an on-chip input pull-up MOS function that can be controlled by software. When a PCR3 bit is cleared to 0, setting the corresponding PUCR3 bit to 1 turns on the input pull-up MOS for that pin. The input pull-up MOS function is in the off state after a reset.

(n = 2 to 0)

| PCR3n             | (   | )  | 1   |

|-------------------|-----|----|-----|

| PUCR3n            | 0   | 1  | х   |

| Input Pull-Up MOS | Off | On | Off |

[Legend] x: Don't care.

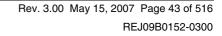

## 8.3 Port 8

Port 8 is an I/O port also functioning as a timer W I/O pin. Figure 8.3 shows its pin configuration.

Figure 8.3 Port 8 Pin Configuration

Port 8 has the following registers.

- Port data register 8 (PDR8)

- Port control register 8 (PCR8)

- Port pull-up control register 8 (PUCR8)

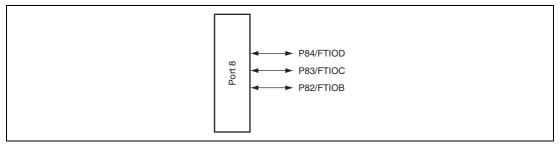

Figure 10.13 PWM Mode Example (TOB, TOC, and TOD = 1: initial output values are set to 1)

#### 11.4.3 Data Reading Procedure

When the seconds, minutes, hours, or day-of-week datum is updated while time data is being read, the data obtained may not be correct, and so the time data must be read again. Figure 11.4 shows an example in which correct data is not obtained. In this example, since only RSECDR is read after data update, about 1-minute inconsistency occurs.

To avoid reading in this timing, the following processing must be performed.

- 1. Check the setting of the BSY bit, and when the BSY bit changes from 1 to 0, read from the second, minute, hour, and day-of-week registers. When about 62.5 ms is passed after the BSY bit is set to 1, the registers are updated, and the BSY bit is cleared to 0.

- 2. When INT in RTCCR1 is cleared to 0 and an interrupt is used, read from the second, minute, hour, and day-of-week registers after the relevant flag in RTCFLG is set to 1 and the BSY bit is confirmed to be 0.

When INT in RTCCR1 is set to 1 and an interrupt is used, read from the second, minute, hour, and day-of-week registers after the relevant flag in RTCFLG is set to 1.

3. Read from the second, minute, hour, and day-of-week registers twice in a row, and if there is no change in the read data, the read data is used.

|                 | <b>Before update</b> RWKDR = H'03, RHDDR = H'13, RMINDR = H'46, RSECDR = H'59<br>BSY bit = 0                              |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| Ņ               | (1) Day-of-week data register read H'03                                                                                   |

| g flo           | (2) Hour data register read H'13                                                                                          |

| isse            | (3) Minute data register read H'46                                                                                        |

| Processing flow | BSY bit -> 1 (under data update)<br>After update RWKDR = H'03, RHDDR = H'13, RMINDR = H'47, RSECDR = H'00<br>BSY bit -> 0 |

|                 | (4) Second data register read H'00                                                                                        |

Figure 11.4 Example: Reading of Inaccurate Time Data

# Section 14 Serial Communication Interface 3 (SCI3, IrDA)

The serial communication interface 3 (SCI3) can handle both asynchronous and clock synchronous serial communication. In the asynchronous method, serial data communication can be carried out using standard asynchronous communication chips such as a Universal Asynchronous Receiver/Transmitter (UART) or an Asynchronous Communication Interface Adapter (ACIA).

The SCI3 can transmit and receive IrDA communication waveforms based on the Infrared Data Association (IrDA) standard version 1.0.

## 14.1 Features

- Choice of asynchronous or clock synchronous serial communication mode

- Full-duplex communication capability

The transmitter and receiver are mutually independent, enabling transmission and reception to be executed simultaneously.

Double-buffering is used in both the transmitter and the receiver, enabling continuous transmission and continuous reception of serial data.

- On-chip baud rate generator allows any bit rate to be selected

- On-chip baud rate generator, internal clock, or external clock can be selected as a transfer clock source.

- Six interrupt sources

Transmit-end, transmit-data-empty, receive-data-full, overrun error, framing error, and parity error.

• Use of module standby mode enables this module to be placed in standby mode independently when not used. (The SCI3 is halted as the initial value. For details, refer to section 5.4, Module Standby Function.)

Asynchronous mode

- Data length: 7, 8, or 5 bits

- Stop bit length: 1 or 2 bits

- Parity: Even, odd, or none

- Receive error detection: Parity, overrun, and framing errors

- Break detection: Break can be detected by reading the RXD3 pin level directly in the case of a framing error

#### 14.4.2 SCI3 Initialization

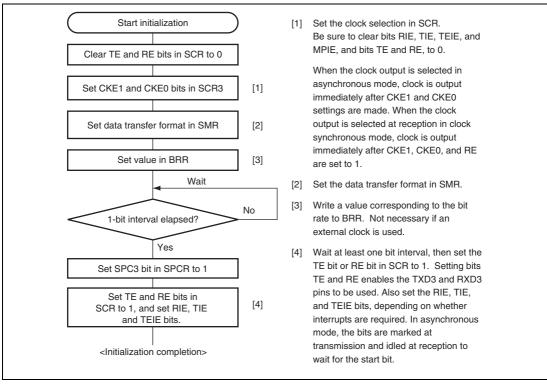

Follow the flowchart as shown in figure 14.4 to initialize the SCI3. When the TE bit is cleared to 0, the TDRE flag is set to 1. Note that clearing the RE bit to 0 does not initialize the contents of the RDRF, PER, FER, and OER flags, or the contents of RDR. When the external clock is used in asynchronous mode, the clock must be supplied even during initialization. When the external clock is used in clock synchronous mode, the clock must not be supplied during initialization.

Figure 14.4 Sample SCI3 Initialization Flowchart

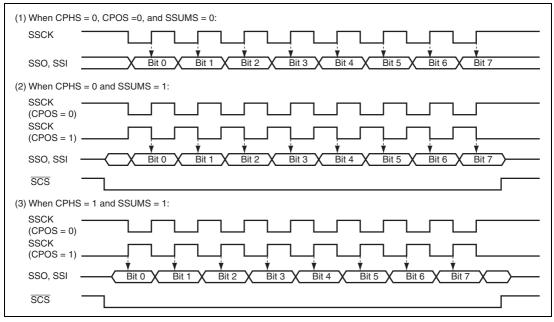

#### 15.4.2 Relationship between Clock Polarity and Phase, and Data

Relationship between clock polarity and phase, and transfer data changes according to a combination of the SSUMS bit in SSCRL and the CPOS and CPHS bits in SSMR. Figure 15.2 shows the relationship.

MSB-first transfer or LSB first transfer can be selected by the setting of the MLS bit in SSMR. When the MLS bit is 0, transfer is started from LSB to MSB. When the MLS bit is 1, transfer is started from MSB to LSB.

Figure 15.2 Relationship between Clock Polarity and Phase, and Data

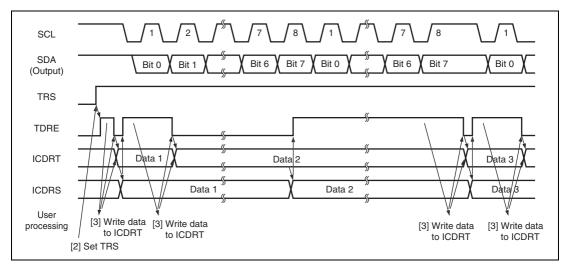

### (2) Transmit Operation

In transmit mode, transmit data is output from SDA, in synchronization with the fall of the transfer clock. The transfer clock is output when MST in ICCR1 is 1, and is input when MST is 0. For transmit mode operation timing, refer to figure 16.14. The transmission procedure and operations in transmit mode are described below.

- 1. Set the ICE bit in ICCR1 to 1. Set the MST and CKS3 to CKS0 bits in ICCR1 to 1. (Initial setting)

- 2. Set the TRS bit in ICCR1 to select the transmit mode. Then, TDRE in ICSR is set.

- 3. Confirm that TDRE has been set. Then, write the transmit data to ICDRT. The data is transferred from ICDRT to ICDRS, and TDRE is set automatically. The continuous transmission is performed by writing data to ICDRT every time TDRE is set. When changing from transmit mode to receive mode, clear TRS while TDRE is 1.

Figure 16.14 Transmit Mode Operation Timing

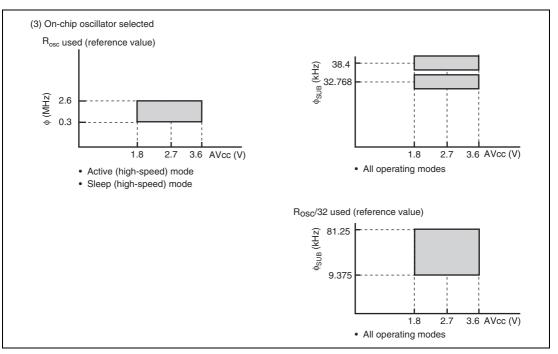

Figure 21.7 Analog Power Supply Voltage and Operating Frequency Range of A/D Converter (2)

|                                                           |                                     |                              |                       |                     |                   | Valu            | es      |           |               |

|-----------------------------------------------------------|-------------------------------------|------------------------------|-----------------------|---------------------|-------------------|-----------------|---------|-----------|---------------|

| Item                                                      | Symbol                              | Applicable Pin               | s Test Co             | ondition            | Min.              | Тур.            | Max.    | Un        | it Notes      |

| Permissible                                               | <b>—І</b> <sub>он</sub>             | All output pins              | V <sub>cc</sub> = 2.7 | 7 V to 3.6 V        | _                 | _               | 2.0     | mA        |               |

| output high<br>current<br>(per pin)                       |                                     |                              | Other th              | nan above           | _                 | _               | 0.2     |           |               |

| Permissible<br>output high<br>current (total<br>Notes: 1. | ,                                   | All output pins              | t measure             | ement.              | _                 | _               | 10.0    | mA        |               |

|                                                           | Mode                                | s aannig canon               | RES Pin               | Internal            | State             | Othe            | er Pins | Oscillat  | or Pins       |

|                                                           | Active (hi<br>mode (I <sub>op</sub> | gh-speed)<br><sub>E1</sub> ) | V <sub>cc</sub>       | Only CP             | Only CPU operates |                 |         |           | r: Crystal    |

|                                                           | Active (m                           | edium-speed)                 |                       |                     |                   |                 |         | resonator |               |

|                                                           | mode (I <sub>op</sub>               | <sub>E2</sub> )              |                       |                     |                   |                 |         |           | k oscillator: |

|                                                           | Sleep mode                          |                              | $V_{cc}$              | Only on-<br>operate | chip timers       | V <sub>cc</sub> |         | Pin X1 =  | n X1 = GND    |

| Mode                                               | RES Pin         | Internal State                         | Other Pins      | <b>Oscillator Pins</b>                                |

|----------------------------------------------------|-----------------|----------------------------------------|-----------------|-------------------------------------------------------|

| Active (high-speed)<br>mode (I <sub>OPE1</sub> )   | V <sub>cc</sub> | Only CPU operates                      | V <sub>cc</sub> | System clock oscillator: Crystal                      |

| Active (medium-speed)<br>mode (I <sub>OPE2</sub> ) |                 |                                        |                 | resonator<br>Subclock oscillator:                     |

| Sleep mode                                         | $V_{cc}$        | Only on-chip timers operate            | $V_{cc}$        | <sup>−</sup> Pin X1 = GND                             |

| Subactive mode                                     | V <sub>cc</sub> | Only CPU operates                      | V <sub>cc</sub> | System clock                                          |

| Subsleep mode                                      | $V_{cc}$        | Only on-chip timers operate, CPU stops | V <sub>cc</sub> | oscillator: Crystal resonator                         |

| Watch mode                                         | V <sub>cc</sub> | Only timer base operates, CPU stops    | $V_{cc}$        | Subclock oscillator:<br>Crystal resonator             |

| Standby mode                                       | V <sub>cc</sub> | CPU and timers both stop, SUBSTP = 1   | V <sub>cc</sub> | System clock<br>oscillator: Crystal<br>resonator      |

|                                                    |                 |                                        |                 | Subclock oscillator:<br>Pin X1 = Crystal<br>resonator |

2. Excludes current in pull-up MOS transistors and output buffers.

3. Used for the determination of user mode or boot mode when the reset is released.

4. When bits IRQ0S1 and IRQ0S0 are set to B'01 or B'10, and bits IRQ1S1 and IRQ1S0 are set to B'01 or B'10, the maximum value is given  $V_{cc}$  + 0.3 (V).

|      |            |         | Addressing Mode and<br>Instruction Length (bytes) |   |      |           |            |     |          |     |   |                                                                                                   |    |           |       |      |     |    |        | . of<br>es* <sup>1</sup> |

|------|------------|---------|---------------------------------------------------|---|------|-----------|------------|-----|----------|-----|---|---------------------------------------------------------------------------------------------------|----|-----------|-------|------|-----|----|--------|--------------------------|

|      | Mnemonic   |         |                                                   |   | @ERn | @(d, ERn) | -ERn/@ERn+ | la  | @(d, PC) | @aa |   | Operation                                                                                         |    | Con       | ditio | on C | ode |    | Normal | Advanced                 |

|      |            | Operand | XX#                                               | R | 0    | ø         | 0          | @aa | 0        | 0   | 1 |                                                                                                   | T  | н         | N     | z    | ۷   | С  | ٩      | Ad                       |

| NEG  | NEG.B Rd   | В       |                                                   | 2 |      |           |            |     |          |     |   | $0\text{Rd8} \rightarrow \text{Rd8}$                                                              |    |           |       |      |     |    | :      | 2                        |

|      | NEG.W Rd   | w       |                                                   | 2 |      |           |            |     |          |     |   | $0-Rd16 \rightarrow Rd16$                                                                         | -  | \$        | \$    | \$   | \$  | \$ | :      | 2                        |

|      | NEG.L ERd  | L       |                                                   | 2 |      |           |            |     |          |     |   | $0ERd32 \rightarrow ERd32$                                                                        | -  | \$        | \$    | \$   | \$  | \$ | :      | 2                        |

| EXTU | EXTU.W Rd  | w       |                                                   | 2 |      |           |            |     |          |     |   | $0 \rightarrow (\text{obits 15 to 8})$ of Rd16)                                                   | -  | -         | 0     | \$   | 0   | -  | :      | 2                        |

|      | EXTU.L ERd | L       | 2 2 0 → (<br>bits 31 to 16> of ERd32)             |   |      |           |            |     |          | -   | - | 0                                                                                                 | \$ | 0         | -     | :    | 2   |    |        |                          |

| EXTS | EXTS.W Rd  | w       |                                                   | 2 |      |           |            |     |          |     |   | ( <bit 7=""> of Rd16) <math>\rightarrow</math><br/>(<bits 15="" 8="" to=""> of Rd16)</bits></bit> | -  | \$ \$ 0 _ |       | -    | :   | 2  |        |                          |

|      | EXTS.L ERd | L       |                                                   | 2 |      |           |            |     |          |     |   | ( <bit 15=""> of ERd32) →<br/>(<bits 16="" 31="" to=""> of<br/>ERd32)</bits></bit>                | _  | -         | \$    | \$   | 0   | -  | :      | 2                        |

## 4. Shift Instructions

|       |             |              |     |    |      |           |             | Mod<br>ngth |          |      |   |           |   |     |                |                   |                |                | No.<br>State |    |

|-------|-------------|--------------|-----|----|------|-----------|-------------|-------------|----------|------|---|-----------|---|-----|----------------|-------------------|----------------|----------------|--------------|----|

|       | Mnemonic    | Operand Size |     |    | @ERn | @(d, ERn) | @-ERn/@ERn+ | a           | @(d, PC) | @ aa |   | Operation | ( | Con | Normal         | Advanced          |                |                |              |    |

|       |             | ď            | xx# | Rn | 0    | 0         | 8           | @aa         | 0        | 0    | Ι |           | Т | н   | Ν              | z                 | ۷              | с              | ٥N           | Ad |

| SHAL  | SHAL.B Rd   | В            |     | 2  |      |           |             |             |          |      |   | - C 0     | — | —   | $\updownarrow$ | $\updownarrow$    | $\updownarrow$ | ↕              | 2            | 2  |

|       | SHAL.W Rd   | w            |     | 2  |      |           |             |             |          |      |   |           | — | —   | $\updownarrow$ | $\updownarrow$    | $\updownarrow$ | $\updownarrow$ | 2            | 2  |

|       | SHAL.L ERd  | L            |     | 2  |      |           |             |             |          |      |   | MSB LSB   | — | -   | $\updownarrow$ | $\updownarrow$    | $\updownarrow$ | $\updownarrow$ | 2            | 2  |

| SHAR  | SHAR.B Rd   | в            |     | 2  |      |           |             |             |          |      |   |           | — | -   | $\updownarrow$ | $\updownarrow$    | 0              | $\updownarrow$ | 2            | 2  |

|       | SHAR.W Rd   | w            |     | 2  |      |           |             |             |          |      |   |           | — | -   | $\updownarrow$ | $\updownarrow$    | 0              | $\updownarrow$ | 2            | 2  |

|       | SHAR.L ERd  | L            |     | 2  |      |           |             |             |          |      |   | MSB LSB   | _ | -   | $\updownarrow$ | $\updownarrow$    | 0              | $\updownarrow$ | 2            | 2  |

| SHLL  | SHLL.B Rd   | В            |     | 2  |      |           |             |             |          |      |   |           | _ | -   | $\updownarrow$ | $\updownarrow$    | 0              | $\updownarrow$ | 2            | 2  |

|       | SHLL.W Rd   | w            |     | 2  |      |           |             |             |          |      |   |           | _ | -   | $\updownarrow$ | $\updownarrow$    | 0              | $\updownarrow$ | 2            | 2  |

|       | SHLL.L ERd  | L            |     | 2  |      |           |             |             |          |      |   | MSB LSB   |   | -   | $\updownarrow$ | $\Rightarrow$     | 0              | $\updownarrow$ | 2            | 2  |

| SHLR  | SHLR.B Rd   | В            |     | 2  |      |           |             |             |          |      |   |           | _ | -   | $\updownarrow$ | $\Leftrightarrow$ | 0              | $\updownarrow$ | 2            | 2  |

|       | SHLR.W Rd   | W            |     | 2  |      |           |             |             |          |      |   |           | _ | —   | $\updownarrow$ | $\Leftrightarrow$ | 0              | $\updownarrow$ | 2            | 2  |

|       | SHLR.L ERd  | L            |     | 2  |      |           |             |             |          |      |   | MSB LSB   | _ | —   | $\updownarrow$ | $\Leftrightarrow$ | 0              | $\updownarrow$ | 2            | 2  |

| ROTXL | ROTXL.B Rd  | В            |     | 2  |      |           |             |             |          |      |   |           | — | —   | $\updownarrow$ | $\Leftrightarrow$ | 0              | $\updownarrow$ | 2            | 2  |

|       | ROTXL.W Rd  | w            |     | 2  |      |           |             |             |          |      |   |           | — | —   | $\updownarrow$ | $\Rightarrow$     | 0              | $\updownarrow$ | 2            | 2  |

|       | ROTXL.L ERd | L            |     | 2  |      |           |             |             |          |      |   | MSB 🗕 LSB | — | —   | $\updownarrow$ | $\updownarrow$    | 0              | $\updownarrow$ | 2            | 2  |

| ROTXR | ROTXR.B Rd  | в            |     | 2  |      |           |             |             |          |      |   |           | — | -   | $\updownarrow$ | $\updownarrow$    | 0              | $\updownarrow$ | 2            | 2  |

|       | ROTXR.W Rd  | w            |     | 2  |      |           |             |             |          |      |   |           | — | -   | $\updownarrow$ | $\updownarrow$    | 0              | $\updownarrow$ | 2            | 2  |

|       | ROTXR.L ERd | L            |     | 2  |      |           |             |             |          |      |   | MSB → LSB | _ | _   | €              | €                 | 0              | $\updownarrow$ | 2            | 2  |

| ROTL  | ROTL.B Rd   | В            |     | 2  |      |           |             |             |          |      |   |           |   | 0   | €              | 2                 | 2              |                |              |    |

|       | ROTL.W Rd   | w            |     | 2  |      |           |             |             |          |      |   |           |   | _   | $\updownarrow$ | $\updownarrow$    | 0              | \$             | 2            | 2  |

|       | ROTL.L ERd  | L            |     | 2  |      |           |             |             |          |      |   | MSB 🔶 LSB |   | _   | €              | €                 | 0              | $\updownarrow$ | 2            | 2  |

| ROTR  | ROTR.B Rd   | В            |     | 2  |      |           |             |             |          |      |   |           | — | -   | €              | €                 | 0              | €              | 2            | 2  |

|       | ROTR.W Rd   | W            |     | 2  |      |           |             |             |          |      |   |           | — | -   | €              | $\updownarrow$    | 0              | €              | 2            | 2  |

|       | ROTR.L ERd  | L            |     | 2  |      |           |             |             |          |      |   | MSB LSB   |   | -   | ↕              | €                 | 0              | \$             | 2            | 2  |

## A.2 Operation Code Map

## Table A.2 Operation Code Map (1)

|                                                     | 1                                                    |       | 0                  | 0                  |   |       |     |                  |             |                             |     |      |     |      |    |     |     |     |

|-----------------------------------------------------|------------------------------------------------------|-------|--------------------|--------------------|---|-------|-----|------------------|-------------|-----------------------------|-----|------|-----|------|----|-----|-----|-----|

|                                                     |                                                      | ш     | Table A-2<br>(2)   | Table A-2<br>(2)   |   |       | BLE |                  |             |                             |     |      |     |      |    |     |     |     |

|                                                     |                                                      | ш     | ADDX               | SUBX               |   |       | BGT | JSR              |             | A-2                         |     |      |     |      |    |     |     |     |

|                                                     |                                                      | D     | >                  | ۵.                 |   |       | BLT |                  |             | Table A-2<br>(3)            |     |      |     |      |    |     |     |     |

| .0.                                                 | I.                                                   | U     | NOM                | CMP                |   |       | BGE | BSR              | ,           |                             |     |      |     |      |    |     |     |     |

| f BH is                                             | I BH IS                                              | ш     | Table A-2<br>(2)   | Table A-2<br>(2)   |   |       | BMI |                  | MOV         | EEPMOV                      |     |      |     |      |    |     |     |     |

| ant bit o                                           | ant dit o                                            | A     | Table A-2 T<br>(2) | Table A-2 T<br>(2) |   |       | BPL | JMP              |             |                             |     |      |     |      |    |     |     |     |

| signific                                            | signific                                             | თ     | Ë                  | Ţ                  |   |       | BVS |                  |             | Table A-2 Table A-2 (2) (2) |     |      |     |      |    |     |     |     |

| - Instruction when most significant bit of BH is 0. | ▲—Instruction when most significant bit of Bri is 1. | 8     | ADD                | SUB                |   |       | BVC | Table A-2<br>(2) |             | MOV Ta                      |     |      |     |      |    |     |     |     |

| tion wh                                             |                                                      | 2     | LDC                | Table A-2<br>(2)   |   | MOV.B | BEQ | TRAPA Ta         | BST<br>BIST |                             | ADD | ADDX | CMP | SUBX | OR | XOR | AND | MOV |

| struc                                               | struc                                                |       |                    |                    |   | ≥     |     | F                | ă \         | J 1                         |     |      |     |      |    |     |     |     |

|                                                     | ≅<br>↓                                               | 9     | ANDC               | AND.B              |   |       | BNE | RTE              | AND         | BAND<br>BIAND               |     |      |     |      |    |     |     |     |

|                                                     | 7                                                    | ß     | XORC               | XOR.B              |   |       | BCS | BSR              | XOR         | BXOR<br>BIXOR               |     |      |     |      |    |     |     |     |

| byte<br>BL                                          |                                                      | 4     | ORC                | OR.B               |   |       | BCC | RTS              | OR          | BOR<br>BIOR                 |     |      |     |      |    |     |     |     |

| 2nd byte<br>BH BL                                   | _                                                    | e     | LDC                | Table A-2<br>(2)   |   |       | BLS | NXVID            |             | BTST                        |     |      |     |      |    |     |     |     |

| 1st byte<br>AH AL                                   | _                                                    | N     | STC                | Table A-2 -<br>(2) |   |       | BHI | MULXU            |             | BCLR                        |     |      |     |      |    |     |     |     |

| 1st  <br>AH                                         |                                                      | -     | Table A-2<br>(2)   | Table A-2 1<br>(2) |   |       | BRN | DIVXU            |             | BNOT                        |     |      |     |      |    |     |     |     |

| n code:                                             |                                                      | 0     | T                  | Table A-2 T<br>(2) |   |       | BRA | MULXU            |             | BSET                        |     |      |     |      |    |     |     |     |

| Instruction code:                                   |                                                      | AH AL | 0                  | -                  | 2 | ю     | 4   | 2                | 9           | 7                           | 8   | 6    | A   | В    | O  | ۵   | ш   | LL. |

#### A.3 Number of Execution States

The status of execution for each instruction of the H8/300H CPU and the method of calculating the number of states required for instruction execution are shown below. Table A.4 shows the number of cycles of each type occurring in each instruction, such as instruction fetch and data read/write. Table A.3 shows the number of states required for each cycle. The total number of states required for execution of an instruction can be calculated by the following expression:

Execution states =  $I \times S_{I} + J \times S_{J} + K \times S_{K} + L \times S_{L} + M \times S_{M} + N \times S_{N}$

Examples: When instruction is fetched from on-chip ROM, and an on-chip RAM is accessed.

BSET #0, @FF00

From table A.4:

$I=L=2, \quad J=K=M=N{=}0$

From table A.3:  $S_1 = 2$ ,  $S_1 = 2$

Number of states required for execution  $= 2 \times 2 + 2 \times 2 = 8$

When instruction is fetched from on-chip ROM, branch address is read from on-chip ROM, and on-chip RAM is used for stack area.

JSR @@ 30

From table A.4:

$I=2, \quad J=K=1, \quad L=M=N=0$

From table A.3:

$$S_{_{\rm I}}=S_{_{\rm J}}=S_{_{\rm K}}=2$$

Number of states required for execution =  $2 \times 2 + 1 \times 2 + 1 \times 2 = 8$