Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 12MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                              |

| Number of I/O              | 26                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 768 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                             |

| Data Converters            | A/D 8x8b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-LCC (J-Lead)                                                         |

| Supplier Device Package    | 28-PLCC (11.48x11.48)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lpc935fa-129 |

## 2.2 Additional features

- A high performance 80C51 CPU provides instruction cycle times of 111 ns to 222 ns for all instructions except multiply and divide when executing at 18 MHz. This is six times the performance of the standard 80C51 running at the same clock frequency. A lower clock frequency for the same performance results in power savings and reduced EMI.

- Serial flash In-Circuit Programming (ICP) allows simple production coding with commercial EPROM programmers. Flash security bits prevent reading of sensitive application programs.

- Serial flash In-System Programming (ISP) allows coding while the device is mounted in the end application.

- In-Application Programming (IAP) of the flash code memory. This allows changing the code in a running application.

- Watchdog timer with separate on-chip oscillator, requiring no external components. The watchdog prescaler is selectable from eight values.

- Low voltage reset (brownout detect) allows a graceful system shutdown when power fails. May optionally be configured as an interrupt.

- Idle and two different power-down reduced power modes. Improved wake-up from Power-down mode (a LOW interrupt input starts execution). Typical power-down current is 1 μA (total power-down with voltage comparators disabled).

- Active-LOW reset. On-chip power-on reset allows operation without external reset components. A reset counter and reset glitch suppression circuitry prevent spurious and incomplete resets. A software reset function is also available.

- Configurable on-chip oscillator with frequency range options selected by user programmed flash configuration bits. Oscillator options support frequencies from 20 kHz to the maximum operating frequency of 18 MHz.

- Oscillator fail detect. The watchdog timer has a separate fully on-chip oscillator allowing it to perform an oscillator fail detect function.

- Programmable port output configuration options: quasi-bidirectional, open drain, push-pull, input-only.

- Port 'input pattern match' detect. Port 0 may generate an interrupt when the value of the pins match or do not match a programmable pattern.

- LED drive capability (20 mA) on all port pins. A maximum limit is specified for the entire chip.

- Controlled slew rate port outputs to reduce EMI. Outputs have approximately 10 ns minimum ramp times.

- Only power and ground connections are required to operate the P89LPC933/934/935/936 when internal reset option is selected.

- Four interrupt priority levels.

- Eight keypad interrupt inputs, plus two additional external interrupt inputs.

- Schmitt trigger port inputs.

- Second data pointer.

- Emulation support.

# 3. Product comparison overview

<u>Table 1</u> highlights the differences between the four devices. For a complete list of device features please see <u>Section 2 "Features and benefits"</u>.

Table 1. Product comparison overview

| Device    | Flash memory | Sector size | ADC1 | ADC0 | CCU | Data EEPROM |

|-----------|--------------|-------------|------|------|-----|-------------|

| P89LPC933 | 4 kB         | 1 kB        | Χ    | -    | -   | -           |

| P89LPC934 | 8 kB         | 1 kB        | X    | -    | -   | -           |

| P89LPC935 | 8 kB         | 1 kB        | X    | X    | Χ   | X           |

| P89LPC936 | 16 kB        | 2 kB        | Χ    | Χ    | Χ   | X           |

# 4. Ordering information

Table 2. Ordering information

| Type number  | Package |                                                                                                                |          |  |  |  |  |

|--------------|---------|----------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|              | Name    | Description                                                                                                    | Version  |  |  |  |  |

| P89LPC935FA  | PLCC28  | plastic leaded chip carrier; 28 leads                                                                          | SOT261-2 |  |  |  |  |

| P89LPC933HDH | TSSOP28 | plastic thin shrink small outline                                                                              | SOT361-1 |  |  |  |  |

| P89LPC933FDH |         | package; 28 leads; body width 4.4 mm                                                                           |          |  |  |  |  |

| P89LPC934FDH |         |                                                                                                                |          |  |  |  |  |

| P89LPC935FDH |         |                                                                                                                |          |  |  |  |  |

| P89LPC936FDH |         |                                                                                                                |          |  |  |  |  |

| P89LPC935FHN | HVQFN28 | plastic thermal enhanced very thin quad flat package; no leads; 28 terminals; body $6 \times 6 \times 0.85$ mm | SOT788-1 |  |  |  |  |

# 4.1 Ordering options

Table 3. Ordering options

| Type number  | Flash memory | Temperature range | Frequency       |

|--------------|--------------|-------------------|-----------------|

| P89LPC933HDH | 4 kB         | −40 °C to +125 °C | 0 MHz to 18 MHz |

| P89LPC933FDH | 4 kB         | −40 °C to +85 °C  | _               |

| P89LPC935FA  | 8 kB         | _                 |                 |

| P89LPC934FDH | _            |                   |                 |

| P89LPC935FDH | _            |                   |                 |

| P89LPC935FHN | _            |                   |                 |

| P89LPC936FDH | 16 kB        |                   |                 |

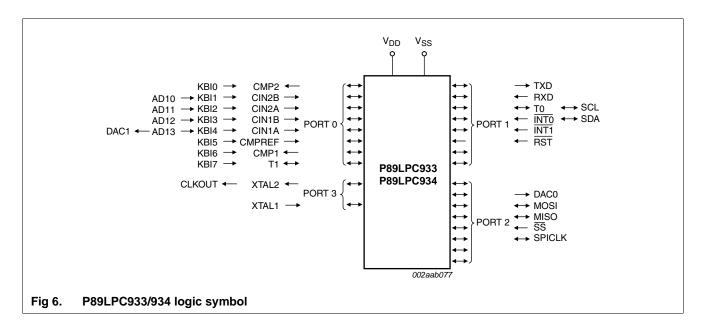

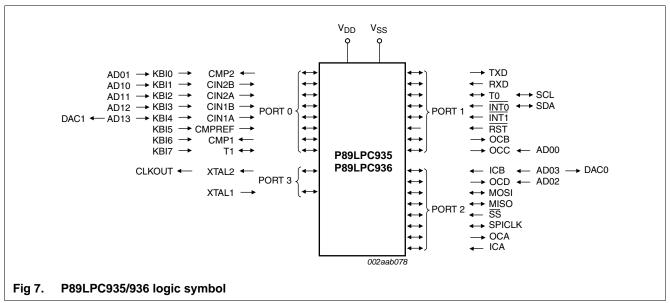

# 7. Logic symbols

Special function registers - P89LPC933/934 ...continued Table 5.

\* indicates SFRs that are bit addressable.

| Name   | Description     | _     | Bit functions and addresses | Reset | value     |

|--------|-----------------|-------|-----------------------------|-------|-----------|

|        |                 | addr. | MSB LSB                     | Hex   | Binary    |

| WDL    | Watchdog load   | C1H   |                             | FF    | 1111 1111 |

| WFEED1 | Watchdog feed 1 | C2H   |                             |       |           |

| WFEED2 | Watchdog feed 2 | СЗН   |                             |       |           |

- [1] Unimplemented bits in SFRs (labeled '-') are X (unknown) at all times. Unless otherwise specified, ones should not be written to these bits since they may be used for other purposes in future derivatives. The reset values shown for these bits are logic 0s although they are unknown when read.

- [2] BRGR1 and BRGR0 must only be written if BRGEN in BRGCON SFR is logic 0. If any are written while BRGEN = 1, the result is unpredictable.

- All ports are in input only (high-impedance) state after power-up.

- [4] The RSTSRC register reflects the cause of the P89LPC933/934/935/936 reset. Upon a power-up reset, all reset source flags are cleared except POF and BOF; the power-on reset value is xx11 0000.

- [5] The only reset source that affects these SFRs is power-on reset.

- On power-on reset, the TRIM SFR is initialized with a factory preprogrammed value. Other resets will not cause initialization of the TRIM register.

- After reset, the value is 1110 01x1, i.e., PRE2 to PRE0 are all logic 1, WDRUN = 1 and WDCLK = 1. WDTOF bit is logic 1 after watchdog reset and is logic 0 after power-on reset. Other resets will not affect WDTOF.

P89LPC933/934/935/936

NXP

Semiconductors

**Table 6. Special function registers - P89LPC935/936** \* *indicates SFRs that are bit addressable.*

| Name     | Description                        | SFR    | Bit function | ons and ad  | dresses |       |        |        |        |        | Reset | value     |

|----------|------------------------------------|--------|--------------|-------------|---------|-------|--------|--------|--------|--------|-------|-----------|

|          |                                    | addr.  | MSB          |             |         |       |        |        |        | LSB    | Hex   | Binary    |

|          | Bit a                              | ddress | E7           | E6          | E5      | E4    | E3     | E2     | E1     | E0     |       |           |

| ACC*     | Accumulator                        | E0H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| ADCON0   | A/D control register 0             | 8EH    | ENBI0        | ENADCI<br>0 | TMM0    | EDGE0 | ADCI0  | ENADC0 | ADCS01 | ADCS00 | 00    | 0000 0000 |

| ADCON1   | A/D control register 1             | 97H    | ENBI1        | ENADCI<br>1 | TMM1    | EDGE1 | ADCI1  | ENADC1 | ADCS11 | ADCS10 | 00    | 0000 0000 |

| ADINS    | A/D input select                   | АЗН    | ADI13        | ADI12       | ADI11   | ADI10 | ADI03  | ADI02  | ADI01  | ADI00  | 00    | 0000 0000 |

| ADMODA   | A/D mode register A                | C0H    | BNDI1        | BURST1      | SCC1    | SCAN1 | BNDI0  | BURST0 | SCC0   | SCAN0  | 00    | 0000 0000 |

| ADMODB   | A/D mode register B                | A1H    | CLK2         | CLK1        | CLK0    | -     | ENDAC1 | ENDAC0 | BSA1   | BSA0   | 00    | 000x 0000 |

| AD0BH    | A/D_0 boundary high register       | BBH    |              |             |         |       |        |        |        |        | FF    | 1111 1111 |

| AD0BL    | A/D_0 boundary low register        | A6H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD0DAT0  | A/D_0 data register 0              | C5H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD0DAT1  | A/D_0 data register 1              | C6H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD0DAT2  | A/D_0 data register 2              | C7H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD0DAT3  | A/D_0 data register 3              | F4H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD1BH    | A/D_1 boundary high register       | C4H    |              |             |         |       |        |        |        |        | FF    | 1111 1111 |

| AD1BL    | A/D_1 boundary low register        | ВСН    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD1DAT0  | A/D_1 data register 0              | D5H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD1DAT1  | A/D_1 data register 1              | D6H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD1DAT2  | A/D_1 data register 2              | D7H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AD1DAT3  | A/D_1 data register 3              | F5H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| AUXR1    | Auxiliary function register        | A2H    | CLKLP        | EBRR        | ENT1    | ENT0  | SRST   | 0      | -      | DPS    | 00    | 0000 00x0 |

|          | Bit a                              | ddress | F7           | F6          | F5      | F4    | F3     | F2     | F1     | F0     |       |           |

| B*       | B register                         | F0H    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| BRGR0[2] | Baud rate generator rate low       | BEH    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| BRGR1[2] | Baud rate generator rate high      | BFH    |              |             |         |       |        |        |        |        | 00    | 0000 0000 |

| BRGCON   | Baud rate generator control        | BDH    | -            | -           | -       | -     | -      | -      | SBRGS  | BRGEN  | 00[2] | xxxx xx00 |

| CCCRA    | Capture compare A control register | EAH    | ICECA2       | ICECA1      | ICECA0  | ICESA | ICNFA  | FCOA   | OCMA1  | OCMA0  | 00    | 0000 0000 |

Product data sheet

**Table 6. Special function registers - P89LPC935/936** ...continued \* indicates SFRs that are bit addressable.

| Name                | Description                          | SFR    | Bit function | ons and ad  | ldresses    |         |         |              |              |              | Reset    | value     |

|---------------------|--------------------------------------|--------|--------------|-------------|-------------|---------|---------|--------------|--------------|--------------|----------|-----------|

| Name<br>RSTSRC      |                                      | addr.  | MSB          |             |             |         |         |              |              | LSB          | Hex      | Binary    |

| RSTSRC              | Reset source register                | DFH    | -            | -           | BOF         | POF     | R_BK    | R_WD         | R_SF         | R_EX         |          | [4]       |

| RTCCON              | Real-time clock control              | D1H    | RTCF         | RTCS1       | RTCS0       | -       | -       | -            | ERTC         | RTCEN        | 60[3][5] | 011x xx00 |

| RTCH                | Real-time clock register high        | D2H    |              |             |             |         |         |              |              |              | 00[5]    | 0000 0000 |

| RTCL                | Real-time clock register low         | D3H    |              |             |             |         |         |              |              |              | 00[5]    | 0000 0000 |

| SADDR               | Serial port address register         | A9H    |              |             |             |         |         |              |              |              | 00       | 0000 0000 |

| SADEN               | Serial port address enable           | В9Н    |              |             |             |         |         |              |              |              | 00       | 0000 0000 |

| SBUF                | Serial Port data buffer register     | 99H    |              |             |             |         |         |              |              |              | XX       | xxxx xxxx |

|                     | Bit a                                | ddress | 9F           | 9E          | 9D          | 9C      | 9B      | 9A           | 99           | 98           |          |           |

| SCON*               | Serial port control                  | 98H    | SM0/FE       | SM1         | SM2         | REN     | TB8     | RB8          | TI           | RI           | 00       | 0000 0000 |

| SSTAT               | Serial port extended status register | BAH    | DBMOD        | INTLO       | CIDIS       | DBISEL  | FE      | BR           | OE           | STINT        | 00       | 0000 0000 |

| SP                  | Stack pointer                        | 81H    |              |             |             |         |         |              |              |              | 07       | 0000 0111 |

| SPCTL               | SPI control register                 | E2H    | SSIG         | SPEN        | DORD        | MSTR    | CPOL    | CPHA         | SPR1         | SPR0         | 04       | 0000 0100 |

| SPSTAT              | SPI status register                  | E1H    | SPIF         | WCOL        | -           | -       | -       | -            | -            | -            | 00       | 00xx xxxx |

| SPDAT               | SPI data register                    | ЕЗН    |              |             |             |         |         |              |              |              | 00       | 0000 0000 |

| TAMOD               | Timer 0 and 1 auxiliary mode         | 8FH    | -            | -           | -           | T1M2    | -       | -            | -            | T0M2         | 00       | xxx0 xxx0 |

|                     | Bit a                                | ddress | 8F           | 8E          | 8D          | 8C      | 8B      | 8A           | 89           | 88           |          |           |

| TCON*               | Timer 0 and 1 control                | 88H    | TF1          | TR1         | TF0         | TR0     | IE1     | IT1          | IE0          | IT0          | 00       | 0000 0000 |

| TCR20*              | CCU control register 0               | C8H    | PLEEN        | HLTRN       | HLTEN       | ALTCD   | ALTAB   | TDIR2        | TMOD21       | TMOD20       | 00       | 0000 0000 |

| TCR21               | CCU control register 1               | F9H    | TCOU2        | -           | -           | -       | PLLDV.3 | PLLDV.2      | PLLDV.1      | PLLDV.0      | 00       | 0xxx 0000 |

| TH0                 | Timer 0 high                         | 8CH    |              |             |             |         |         |              |              |              | 00       | 0000 0000 |

| TH1                 | Timer 1 high                         | 8DH    |              |             |             |         |         |              |              |              | 00       | 0000 0000 |

| TH2                 | CCU timer high                       | CDH    |              |             |             |         |         |              |              |              | 00       | 0000 0000 |

| TICR2               | CCU interrupt control register       | С9Н    | TOIE2        | TOCIE2<br>D | TOCIE2<br>C | TOCIE2B | TOCIE2A | -            | TICIE2B      | TICIE2A      | 00       | 0000 0x00 |

| TIFR2               | CCU interrupt flag register          | E9H    | TOIF2        | TOCF2D      | TOCF2C      | TOCF2B  | TOCF2A  | -            | TICF2B       | TICF2A       | 00       | 0000 0x00 |

| TIFR2 TISE2 TL0 TL1 | CCU interrupt status encode register | DEH    | -            | -           | -           | -       | -       | ENCINT.<br>2 | ENCINT.<br>1 | ENCINT.<br>0 | 00       | xxxx x000 |

| TL0                 | Timer 0 low                          | 8AH    |              |             |             |         |         |              |              |              | 00       | 0000 0000 |

| TL1                 | Timer 1 low                          | 8BH    |              |             |             |         |         |              |              |              | 00       | 0000 0000 |

external clock input on X1) and if the RTC is not using the crystal oscillator as its clock source. This allows external devices to synchronize to the P89LPC933/934/935/936. This output is enabled by the ENCLK bit in the TRIM register.

The frequency of this clock output is  $\frac{1}{2}$  that of the CCLK. If the clock output is not needed in Idle mode, it may be turned off prior to entering Idle, saving additional power.

# 8.4 On-chip RC oscillator option

The P89LPC933/934/935/936 has a 6-bit TRIM register that can be used to tune the frequency of the RC oscillator. During reset, the TRIM value is initialized to a factory preprogrammed value to adjust the oscillator frequency to 7.373 MHz  $\pm$  1 % at room temperature. End-user applications can write to the TRIM register to adjust the on-chip RC oscillator to other frequencies.

# 8.5 Watchdog oscillator option

The watchdog has a separate oscillator which has a frequency of 400 kHz. This oscillator can be used to save power when a high clock frequency is not needed.

# 8.6 External clock input option

In this configuration, the processor clock is derived from an external source driving the P3.1/XTAL1 pin. The rate may be from 0 Hz up to 18 MHz. The P3.0/XTAL2 pin may be used as a standard port pin or a clock output. When using an oscillator frequency above 12 MHz, the reset input function of P1.5 must be enabled. An external circuit is required to hold the device in reset at power-up until VDD has reached its specified level. When system power is removed VDD will fall below the minimum specified operating voltage. When using an oscillator frequency above 12 MHz, in some applications, an external brownout detect circuit may be required to hold the device in reset when VDD falls below the minimum specified operating voltage.

# 8.13 I/O ports

The P89LPC933/934/935/936 has four I/O ports: Port 0, Port 1, Port 2, and Port 3. Ports 0, 1 and 2 are 8-bit ports, and Port 3 is a 2-bit port. The exact number of I/O pins available depends upon the clock and reset options chosen, as shown in <u>Table 8</u>.

Table 8. Number of I/O pins available

| Clock source                                                     | Reset option                               | Number of I/O pins (28-pin package) |

|------------------------------------------------------------------|--------------------------------------------|-------------------------------------|

| On-chip oscillator or watchdog oscillator                        | No external reset (except during power-up) | 26                                  |

|                                                                  | External RST pin supported                 | 25                                  |

| External clock input                                             | No external reset (except during power-up) | 25                                  |

|                                                                  | External RST pin supported[1]              | 24                                  |

| Low/medium/high speed oscillator (external crystal or resonator) | No external reset (except during power-up) | 24                                  |

|                                                                  | External RST pin supported[1]              | 23                                  |

<sup>[1]</sup> Required for operation above 12 MHz.

## 8.13.1 Port configurations

All but three I/O port pins on the P89LPC933/934/935/936 may be configured by software to one of four types on a bit-by-bit basis. These are: quasi-bidirectional (standard 80C51 port outputs), push-pull, open drain, and input-only. Two configuration registers for each port select the output type for each port pin.

- 1. P1.5 (RST) can only be an input and cannot be configured.

- 2. P1.2 (SCL/T0) and P1.3 (SDA/INT0) may only be configured to be either input-only or open-drain.

## 8.13.1.1 Quasi-bidirectional output configuration

Quasi-bidirectional output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic HIGH, it is weakly driven, allowing an external device to pull the pin LOW. When the pin is driven LOW, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open-drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes.

The P89LPC933/934/935/936 is a 3 V device, but the pins are 5 V-tolerant. In quasi-bidirectional mode, if a user applies 5 V on the pin, there will be a current flowing from the pin to  $V_{DD}$ , causing extra power consumption. Therefore, applying 5 V in quasi-bidirectional mode is discouraged.

A quasi-bidirectional port pin has a Schmitt trigger input that also has a glitch suppression circuit.

## 8.13.1.2 Open-drain output configuration

The open-drain output configuration turns off all pull-ups and only drives the pull-down transistor of the port driver when the port latch contains a logic 0. To be used as a logic output, a port configured in this manner must have an external pull-up, typically a resistor tied to  $V_{DD}$ .

P89LPC933\_934\_935\_936

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

An open-drain port pin has a Schmitt trigger input that also has a glitch suppression circuit.

## 8.13.1.3 Input-only configuration

The input-only port configuration has no output drivers. It is a Schmitt trigger input that also has a glitch suppression circuit.

## 8.13.1.4 Push-pull output configuration

The push-pull output configuration has the same pull-down structure as both the open-drain and the quasi-bidirectional output modes, but provides a continuous strong pull-up when the port latch contains a logic 1. The push-pull mode may be used when more source current is needed from a port output. A push-pull port pin has a Schmitt trigger input that also has a glitch suppression circuit.

# 8.13.2 Port 0 analog functions

The P89LPC933/934/935/936 incorporates two Analog Comparators. In order to give the best analog function performance and to minimize power consumption, pins that are being used for analog functions must have the digital outputs and digital inputs disabled.

Digital outputs are disabled by putting the port output into the Input-Only (high-impedance) mode.

Digital inputs on Port 0 may be disabled through the use of the PT0AD register, bits 1:5. On any reset, PT0AD[1:5] defaults to logic 0s to enable digital functions.

### 8.13.3 Additional port features

After power-up, all pins are in Input-Only mode.

Remark: Please note that this is different from the LPC76x series of devices.

- After power-up, all I/O pins except P1.5, may be configured by software.

- Pin P1.5 is input only. Pins P1.2 and P1.3 and are configurable for either input-only or open-drain.

Every output on the P89LPC933/934/935/936 has been designed to sink typical LED drive current. However, there is a maximum total output current for all ports which must not be exceeded. Please refer to <u>Table 11 "Static characteristics"</u> for detailed specifications.

All ports pins that can function as an output have slew rate controlled outputs to limit noise generated by quickly switching output signals. The slew rate is factory-set to approximately 10 ns rise and fall times.

# 8.14 Power monitoring functions

The P89LPC933/934/935/936 incorporates power monitoring functions designed to prevent incorrect operation during initial power-up and power loss or reduction during operation. This is accomplished with two hardware functions: Power-on detect and brownout detect.

Capture Noise Filter bit. If set, the capture logic needs to see four consecutive samples of the same value in order to recognize an edge as a capture event. An event counter can be set to delay a capture by a number of capture events.

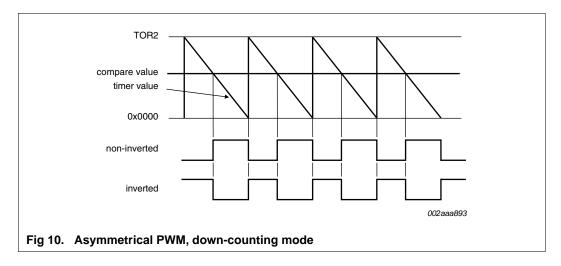

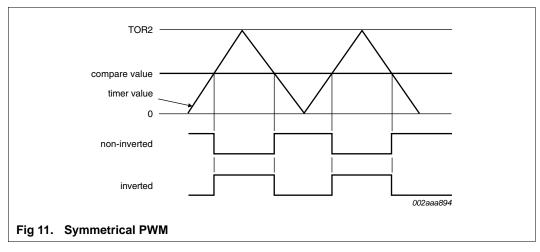

# 8.19.6 PWM operation

PWM operation has two main modes, symmetrical and asymmetrical.

In asymmetrical PWM operation the CCU timer operates in down-counting mode regardless of the direction control bit.

In symmetrical mode, the timer counts up/down alternately. The main difference from basic timer operation is the operation of the compare module, which in PWM mode is used for PWM waveform generation.

As with basic timer operation, when the PWM (compare) pins are connected to the compare logic, their logic state remains unchanged. However, since bit FCO is used to hold the halt value, only a compare event can change the state of the pin.

# 8.21 I<sup>2</sup>C-bus serial interface

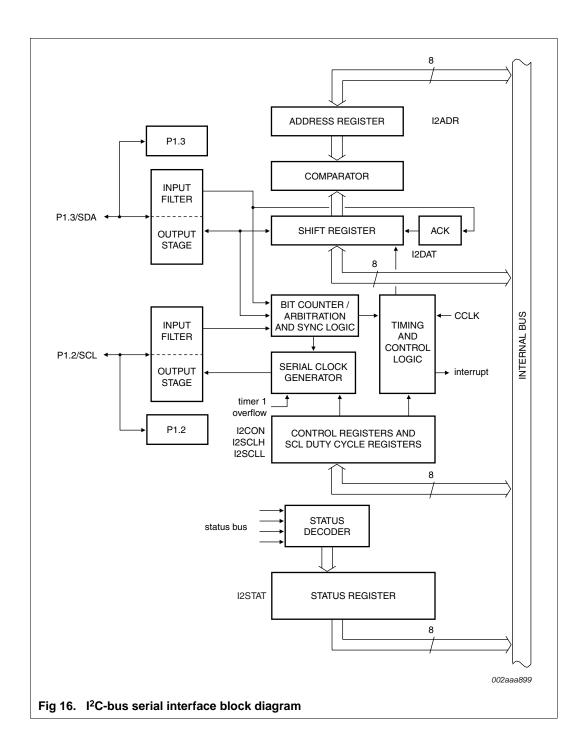

The I<sup>2</sup>C-bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus, and it has the following features:

- Bidirectional data transfer between masters and slaves

- Multi master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- The I<sup>2</sup>C-bus may be used for test and diagnostic purposes.

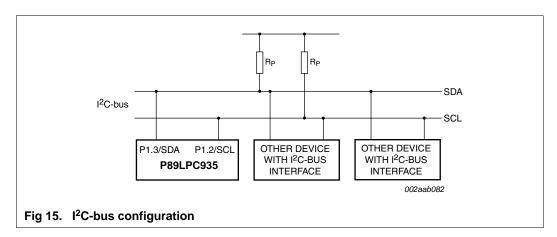

A typical I<sup>2</sup>C-bus configuration is shown in <u>Figure 15</u>. The P89LPC933/934/935/936 device provides a byte-oriented I<sup>2</sup>C-bus interface that supports data transfers up to 400 kHz.

# 8.25 Watchdog timer

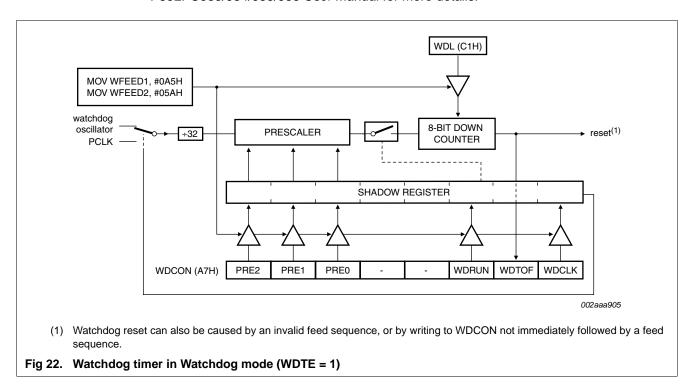

The watchdog timer causes a system reset when it underflows as a result of a failure to feed the timer prior to the timer reaching its terminal count. It consists of a programmable 12-bit prescaler, and an 8-bit down counter. The down counter is decremented by a tap taken from the prescaler. The clock source for the prescaler is either the PCLK or the nominal 400 kHz watchdog oscillator. The watchdog timer can only be reset by a power-on reset. When the watchdog feature is disabled, it can be used as an interval timer and may generate an interrupt. Figure 22 shows the watchdog timer in Watchdog mode. Feeding the watchdog requires a two-byte sequence. If PCLK is selected as the watchdog clock and the CPU is powered-down, the watchdog is disabled. The watchdog timer has a time-out period that ranges from a few  $\mu$ s to a few seconds. Please refer to the P89LPC933/934/935/936 *User manual* for more details.

### 8.26 Additional features

## 8.26.1 Software reset

The SRST bit in AUXR1 gives software the opportunity to reset the processor completely, as if an external reset or watchdog reset had occurred. Care should be taken when writing to AUXR1 to avoid accidental software resets.

### 8.26.2 Dual data pointers

The dual Data Pointers (DPTR) provides two different Data Pointers to specify the address used with certain instructions. The DPS bit in the AUXR1 register selects one of the two Data Pointers. Bit 2 of AUXR1 is permanently wired as a logic 0 so that the DPS bit may be toggled (thereby switching Data Pointers) simply by incrementing the AUXR1 register, without the possibility of inadvertently altering other bits in the register.

P89LPC933\_934\_935\_936

# 10. Limiting values

Table 10. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                   | Parameter                                      | Conditions                                                         | Min  | Max                   | Unit |

|--------------------------|------------------------------------------------|--------------------------------------------------------------------|------|-----------------------|------|

| T <sub>amb(bias)</sub>   | bias ambient temperature                       |                                                                    | -55  | +125                  | °C   |

| T <sub>stg</sub>         | storage temperature                            |                                                                    | -65  | +150                  | °C   |

| I <sub>OH(I/O)</sub>     | HIGH-level output current per input/output pin |                                                                    | -    | 20                    | mA   |

| I <sub>OL(I/O)</sub>     | LOW-level output current per input/output pin  |                                                                    | -    | 20                    | mA   |

| I <sub>I/Otot(max)</sub> | maximum total input/output current             |                                                                    | -    | 100                   | mA   |

| V <sub>xtal</sub>        | crystal voltage                                | on XTAL1, XTAL2 pin to V <sub>SS</sub>                             | -    | V <sub>DD</sub> + 0.5 | V    |

| V <sub>n</sub>           | voltage on any other pin                       | except XTAL1, XTAL2 to V <sub>SS</sub>                             | -0.5 | +5.5                  | V    |

| P <sub>tot(pack)</sub>   | total power dissipation (per package)          | based on package heat<br>transfer, not device power<br>consumption | -    | 1.5                   | W    |

<sup>[1]</sup> The following applies to <u>Table 10</u>:

a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum

b) Parameters are valid over ambient temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

# 12. Dynamic characteristics

Table 12. Dynamic characteristics (12 MHz)

$V_{DD} = 2.4 \text{ V to } 3.6 \text{ V unless otherwise specified.}$

$T_{amb} = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  for industrial,  $-40 \,^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$  for extended, unless otherwise specified. [1][2]

| Symbol               | Parameter                                     | Conditions                 | Varia                  | Variable clock                         |       |       | Unit |

|----------------------|-----------------------------------------------|----------------------------|------------------------|----------------------------------------|-------|-------|------|

|                      |                                               |                            | Min                    | Max                                    | Min   | Max   |      |

| f <sub>osc(RC)</sub> | internal RC oscillator frequency              |                            | 7.189                  | 7.557                                  | 7.189 | 7.557 | MHz  |

| f <sub>osc(WD)</sub> | internal watchdog oscillator frequency        |                            | 320                    | 520                                    | 320   | 520   | kHz  |

| f <sub>osc</sub>     | oscillator frequency                          |                            | 0                      | 12                                     | -     | -     | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time                              | see Figure 27              | 83                     | -                                      | -     | -     | ns   |

| f <sub>CLKLP</sub>   | low-power select clock frequency              |                            | 0                      | 8                                      | -     | -     | MHz  |

| Glitch filte         | er                                            |                            |                        |                                        |       |       |      |

| t <sub>gr</sub>      | glitch rejection time                         | P1.5/RST pin               | -                      | 50                                     | -     | 50    | ns   |

|                      |                                               | any pin except<br>P1.5/RST | -                      | 15                                     | -     | 15    | ns   |

| t <sub>sa</sub>      | signal acceptance time                        | P1.5/RST pin               | 125                    | -                                      | 125   | -     | ns   |

|                      |                                               | any pin except<br>P1.5/RST | 50                     | -                                      | 50    | -     | ns   |

| External of          | clock                                         |                            |                        |                                        |       |       |      |

| t <sub>CHCX</sub>    | clock HIGH time                               | see Figure 27              | 33                     | $T_{\text{cy(CLK)}} - t_{\text{CLCX}}$ | 33    | -     | ns   |

| t <sub>CLCX</sub>    | clock LOW time                                | see Figure 27              | 33                     | $T_{\text{cy(CLK)}} - t_{\text{CHCX}}$ | 33    | -     | ns   |

| t <sub>CLCH</sub>    | clock rise time                               | see Figure 27              | -                      | 8                                      | -     | 8     | ns   |

| t <sub>CHCL</sub>    | clock fall time                               | see Figure 27              | -                      | 8                                      | -     | 8     | ns   |

| Shift regis          | ster (UART mode 0)                            |                            |                        |                                        |       |       |      |

| $T_{XLXL}$           | serial port clock cycle time                  | see Figure 25              | 16T <sub>cy(CLK)</sub> | -                                      | 1333  | -     | ns   |

| $t_{QVXH}$           | output data set-up to clock rising edge time  | see <u>Figure 25</u>       | 13T <sub>cy(CLK)</sub> | -                                      | 1083  | -     | ns   |

| t <sub>XHQX</sub>    | output data hold after clock rising edge time | see <u>Figure 25</u>       | -                      | $T_{cy(CLK)} + 20$                     | -     | 103   | ns   |

| t <sub>XHDX</sub>    | input data hold after clock rising edge time  | see Figure 25              | -                      | 0                                      | -     | 0     | ns   |

| t <sub>XHDV</sub>    | input data valid to clock rising edge time    | see Figure 25              | 150                    | -                                      | 150   | -     | ns   |

| SPI interfa          | ace                                           |                            |                        |                                        |       |       |      |

| f <sub>SPI</sub>     | SPI operating frequency                       |                            |                        |                                        |       |       |      |

|                      | slave                                         |                            | 0                      | CCLK/6                                 | 0     | 2.0   | MHz  |

|                      | master                                        |                            | -                      | CCLK/4                                 | -     | 3.0   | MHz  |

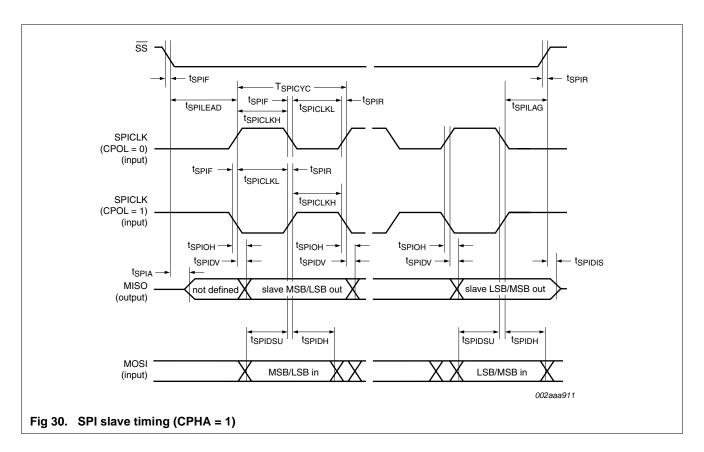

| T <sub>SPICYC</sub>  | SPI cycle time                                | see <u>Figure 26, 28,</u>  |                        |                                        |       |       |      |

|                      | slave                                         | <u>29,</u> <u>30</u>       | <sup>6</sup> ∕cclk     | -                                      | 500   | -     | ns   |

|                      | master                                        | _                          | ⁴∕cclk                 | -                                      | 333   | -     | ns   |

| t <sub>SPILEAD</sub> | SPI enable lead time                          | see Figure 29, 30          |                        |                                        |       |       |      |

|                      | slave                                         |                            | 250                    | -                                      | 250   | -     | ns   |

P89LPC933\_934\_935\_936

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

60 of 77

Table 12. Dynamic characteristics (12 MHz) ...continued

$V_{DD} = 2.4 \text{ V to } 3.6 \text{ V unless otherwise specified.}$

$T_{amb} = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  for industrial,  $-40 \,^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$  for extended, unless otherwise specified. [1][2]

| Symbol               | Parameter                            | Conditions                                 | Variab             | ole clock | f <sub>osc</sub> = 1 | 12 MHz | Unit |

|----------------------|--------------------------------------|--------------------------------------------|--------------------|-----------|----------------------|--------|------|

|                      |                                      |                                            | Min                | Max       | Min                  | Max    |      |

| t <sub>SPILAG</sub>  | SPI enable lag time                  | see <u>Figure 29,</u> 30                   |                    |           |                      |        |      |

|                      | slave                                | _                                          | 250                | -         | 250                  | -      | ns   |

| t <sub>SPICLKH</sub> | SPICLK HIGH time                     | see <u>Figure 26, 28,</u>                  |                    |           |                      |        |      |

|                      | master                               | <u>29</u> , <u>30</u>                      | <sup>2</sup> /cclk | -         | 165                  | -      | ns   |

|                      | slave                                |                                            | <sup>3</sup> /cclk | -         | 250                  | -      | ns   |

| tSPICLKL             | SPICLK LOW time                      | see <u>Figure 26,</u> <u>28,</u>           |                    |           |                      |        |      |

|                      | master                               | <u>29</u> , <u>30</u>                      | <sup>2</sup> /CCLK | -         | 165                  | -      | ns   |

|                      | slave                                |                                            | <sup>3</sup> /CCLK | -         | 250                  | -      | ns   |

| t <sub>SPIDSU</sub>  | SPI data set-up time                 | see <u>Figure 26, 28,</u>                  |                    |           |                      |        |      |

|                      | master or slave                      | <u>29</u> , <u>30</u>                      | 100                | -         | 100                  | -      | ns   |

| t <sub>SPIDH</sub>   | SPI data hold time                   | see <u>Figure 26, 28,</u>                  |                    |           |                      |        |      |

|                      | master or slave                      | <u>29</u> , <u>30</u>                      | 100                | -         | 100                  | -      | ns   |

| t <sub>SPIA</sub>    | SPI access time                      | see <u>Figure 29</u> , <u>30</u>           |                    |           |                      |        |      |

|                      | slave                                |                                            | 0                  | 120       | 0                    | 120    | ns   |

| t <sub>SPIDIS</sub>  | SPI disable time                     | see <u>Figure 29</u> , <u>30</u>           |                    |           |                      |        |      |

|                      | slave                                | _                                          | 0                  | 240       | -                    | 240    | ns   |

| t <sub>SPIDV</sub>   | SPI enable to output data valid time | see <u>Figure 26, 28,</u><br>29, <u>30</u> |                    |           |                      |        |      |

|                      | slave                                |                                            | -                  | 240       | -                    | 240    | ns   |

|                      | master                               | _                                          | -                  | 167       | -                    | 167    | ns   |

| t <sub>SPIOH</sub>   | SPI output data hold time            | see <u>Figure 26, 28,</u><br>29, <u>30</u> | 0                  | -         | 0                    | -      | ns   |

| t <sub>SPIR</sub>    | SPI rise time                        | see <u>Figure 26, 28,</u>                  |                    |           |                      |        |      |

|                      | SPI outputs<br>(SPICLK, MOSI, MISO)  | <u>29, 30</u>                              | -                  | 100       | -                    | 100    | ns   |

|                      | SPI inputs (SPICLK, MOSI, MISO, SS)  |                                            | -                  | 2000      | -                    | 2000   | ns   |

| SPIF                 | SPI fall time                        | see <u>Figure 26, 28,</u>                  |                    |           |                      |        |      |

| OI IF                | SPI outputs<br>(SPICLK, MOSI, MISO)  | <u>29,</u> <u>30</u>                       | -                  | 100       | -                    | 100    | ns   |

|                      | SPI inputs (SPICLK, MOSI, MISO, SS)  |                                            | -                  | 2000      | -                    | 2000   | ns   |

<sup>[1]</sup> Parameters are valid over ambient temperature range unless otherwise specified.

<sup>[2]</sup> Parts are tested to 2 MHz, but are guaranteed to operate down to 0 Hz.

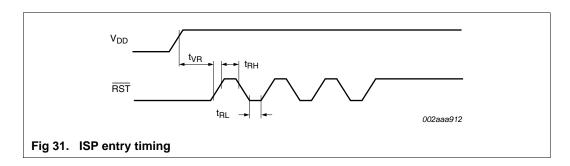

# 12.2 ISP entry mode

## Table 14. Dynamic characteristics, ISP entry mode

$V_{DD}$  = 2.4 V to 3.6 V, unless otherwise specified.

$T_{amb} = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  for industrial, -40  $^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$  for extended, unless otherwise specified.

| arrio           | •                                          | •          |     | •   |     |      |

|-----------------|--------------------------------------------|------------|-----|-----|-----|------|

| Symbol          | Parameter                                  | Conditions | Min | Тур | Max | Unit |

| $t_{VR}$        | RST delay from V <sub>DD</sub> active time |            | 50  | -   | -   | μS   |

| t <sub>RH</sub> | RST HIGH time                              |            | 1   | -   | 32  | μS   |

| t <sub>RL</sub> | RST LOW time                               |            | 1   | -   | -   | μS   |

# 13.2 ADC electrical characteristics

# Table 16. ADC electrical characteristics

$V_{DD}$  = 2.4 V to 3.6 V, unless otherwise specified.

$T_{amb} = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  for industrial, -40  $^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$  for extended, unless otherwise specified.

All limits valid for an external source impedance of less than 10 k $\Omega$ .

| Symbol                     | Parameter                     | Conditions       | Min                  | Тур | Max                    | Unit |

|----------------------------|-------------------------------|------------------|----------------------|-----|------------------------|------|

| $V_{IA}$                   | analog input voltage          |                  | V <sub>SS</sub> -0.2 | -   | V <sub>DD</sub> +0.2   | V    |

| C <sub>iss</sub>           | input capacitance             |                  | -                    | -   | 15                     | pF   |

| E <sub>D</sub>             | differential linearity error  |                  | -                    | -   | ±1                     | LSB  |

| E <sub>L(adj)</sub>        | integral non-linearity        |                  | -                    | -   | ±1                     | LSB  |

| E <sub>O</sub>             | offset error                  |                  | -                    | -   | ±2                     | LSB  |

| E <sub>G</sub>             | gain error                    |                  | -                    | -   | ±1                     | %    |

| E <sub>u(tot)</sub>        | total unadjusted error        |                  | -                    | -   | ±2                     | LSB  |

| M <sub>CTC</sub>           | channel-to-channel matching   |                  | -                    | -   | ±1                     | LSB  |

| $\alpha_{\text{ct(port)}}$ | crosstalk between port inputs | 0 kHz to 100 kHz | -                    | -   | -60                    | dB   |

| SR <sub>in</sub>           | input slew rate               |                  | -                    | -   | 100                    | V/ms |

| T <sub>cy(ADC)</sub>       | ADC clock cycle time          |                  | 111                  | -   | 2000                   | ns   |

| t <sub>ADC</sub>           | ADC conversion time           | A/D enabled      | -                    | -   | 13T <sub>cy(ADC)</sub> | ns   |

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's

own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

### 17.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

# 18. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

# 19. Contents

| 1        | General description              | . 1 | 8.15.3  | Total Power-down mode                     |    |

|----------|----------------------------------|-----|---------|-------------------------------------------|----|

| 2        | Features and benefits            | . 1 | 8.16    | Reset                                     |    |

| 2.1      | Principal features               | . 1 | 8.16.1  | Reset vector                              | 33 |

| 2.2      | Additional features              |     | 8.17    | Timers/counters 0 and 1                   | 34 |

| 3        | Product comparison overview      |     | 8.17.1  | Mode 0                                    | 34 |

| _        |                                  |     | 8.17.2  | Mode 1                                    |    |

| 4        | Ordering information             |     | 8.17.3  | Mode 2                                    |    |

| 4.1      | Ordering options                 |     | 8.17.4  | Mode 3                                    | 34 |

| 5        | Block diagram                    | . 4 | 8.17.5  | Mode 6                                    | 34 |

| 6        | Pinning information              | . 5 | 8.17.6  | Timer overflow toggle output              | 34 |

| 6.1      | Pinning                          | . 5 | 8.18    | RTC/system timer                          | 34 |

| 6.2      | Pin description                  |     | 8.19    | CCU (P89LPC935/936)                       | 35 |

| 7        | Logic symbols                    |     | 8.19.1  | CCU clock                                 | 35 |

|          |                                  |     | 8.19.2  | CCUCLK prescaling                         | 35 |

| 8        | Functional description           |     | 8.19.3  | Basic timer operation                     | 35 |

| 8.1      | Special function registers       |     | 8.19.4  | Output compare                            | 35 |

| 8.2      | Enhanced CPU                     |     | 8.19.5  | Input capture                             | 35 |

| 8.3      | Clocks                           |     | 8.19.6  | PWM operation                             | 36 |

| 8.3.1    | Clock definitions                |     | 8.19.7  | Alternating output mode                   | 37 |

| 8.3.2    | CPU clock (OSCCLK)               |     | 8.19.8  | PLL operation                             | 37 |

| 8.3.3    | Low speed oscillator option      |     | 8.19.9  | CCU interrupts                            |    |

| 8.3.4    | Medium speed oscillator option   |     | 8.20    | UART                                      | 38 |

| 8.3.5    | High speed oscillator option     |     | 8.20.1  | Mode 0                                    | 38 |

| 8.3.6    | Clock output                     |     | 8.20.2  | Mode 1                                    | 39 |

| 8.4      | On-chip RC oscillator option     |     | 8.20.3  | Mode 2                                    | 39 |

| 8.5      | Watchdog oscillator option       |     | 8.20.4  | Mode 3                                    | 39 |

| 8.6      | External clock input option      |     | 8.20.5  | Baud rate generator and selection         | 39 |

| 8.7      | CCLK wake-up delay               |     | 8.20.6  | Framing error                             | 39 |

| 8.8      | CCLK modification: DIVM register |     | 8.20.7  | Break detect                              | 40 |

| 8.9      | Low power select                 |     | 8.20.8  | Double buffering                          | 40 |

| 8.10     | Memory organization              |     | 8.20.9  | Transmit interrupts with double           |    |

| 8.11     | Data RAM arrangement             |     |         | buffering enabled (modes 1, 2 and 3)      | 40 |

| 8.12     | Interrupts                       |     | 8.20.10 | The 9 <sup>th</sup> bit (bit 8) in double |    |

| 8.12.1   | External interrupt inputs        |     |         | buffering (modes 1, 2 and 3)              | 40 |

| 8.13     | I/O ports                        |     | 8.21    | I <sup>2</sup> C-bus serial interface     |    |

| 8.13.1   | Port configurations              |     | 8.22    | SPI                                       |    |

| 8.13.1.1 | 3                                |     | 8.22.1  | Typical SPI configurations                |    |

| 8.13.1.2 | - 1                              |     | 8.23    | Analog comparators                        |    |

| 8.13.1.3 | , , ,                            |     | 8.23.1  | Internal reference voltage                |    |

| 8.13.1.4 | 1 1                              | 31  | 8.23.2  | Comparator interrupt                      |    |

| 8.13.2   | Port 0 analog functions          | 31  | 8.23.3  | Comparators and power reduction modes     | 47 |

| 8.13.3   | Additional port features         |     | 8.24    | Keypad interrupt                          |    |

| 8.14     | Power monitoring functions       |     | 8.25    | Watchdog timer                            |    |

| 8.14.1   | Brownout detection               |     | 8.26    | Additional features                       |    |

| 8.14.2   | Power-on detection               |     | 8.26.1  | Software reset                            |    |

| 8.15     | Power reduction modes            |     | 8.26.2  | Dual data pointers                        |    |

| 8.15.1   | Idle mode                        |     | 8.27    | Data EEPROM (P89LPC935/936)               |    |

| 8.15.2   | Power-down mode                  | 32  | 8.28    | Flash program memory                      |    |

|          |                                  |     |         | 1                                         |    |

continued >>