### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8052                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 12.58MHz                                                        |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                      |

| Peripherals                | POR, PSM, Temp Sensor, WDT                                      |

| Number of I/O              | 34                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | 640 x 8                                                         |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                    |

| Data Converters            | A/D 3x16b, 4x24b; D/A 1x12b                                     |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 56-VFQFN Exposed Pad, CSP                                       |

| Supplier Device Package    | 56-LFCSP-VQ (8x8)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc824bcpz |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **ADUC824\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

### EVALUATION KITS

ADuC824 QuickStart Development System

### **DOCUMENTATION**

#### **Application Notes**

- AN-1074: Understanding the Serial Download Protocol (Formerly uC004)

- AN-282: Fundamentals of Sampled Data Systems

- AN-644: Frequency Measurement Using Timer 2 on a MicroConverter <sup>®</sup> (uC013)

- AN-645: Interfacing an HD44780 Character LCD to a MicroConverter <sup>®</sup> (uC014)

- AN-660: XY-Matrix Keypad Interface to MicroConverter<sup>®</sup>

- AN-709: RTD Interfacing and Linearization Using an ADuC8xx MicroConverter<sup>®</sup>

- AN-759: Expanding the Number of DAC Outputs on the ADuC8xx and ADuC702x Families (uC012)

- UC-001: MicroConverter® I2C® Compatible Interface

- UC-006: A 4-wire UART-to-PC Interface

- UC-009: Addressing 16MB of External Data Memory

- UC-015: An ADuC824-Based Temperature-Logger

- UC-018: Uses of the Time Interval Counter

#### Data Sheet

- ADuC824: MicroConverter<sup>®</sup> = 24-Bit ADC + 16-Bit ADC + 12-Bit DAC + Flash MCU Data Sheet

- ADuC824: Errata Sheet

#### **User Guides**

- ADuC824 Quick Reference Guide

- UG-041: ADuC8xx Evaluation Kit Getting Started User Guide

### TOOLS AND SIMULATIONS $\Box$

• Sigma-Delta ADC Tutorial

### REFERENCE MATERIALS

#### **Technical Articles**

- DDS Circuit Generates Precise PWM Waveforms

- · Integrated Route Taken to Pulse Oximetry

### DESIGN RESOURCES

- ADUC824 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all ADUC824 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

### TABLE OF CONTENTS

| FEATURES                              | . 1 |

|---------------------------------------|-----|

| GENERAL DESCRIPTION                   | . 1 |

| SPECIFICATIONS                        | . 3 |

| TIMING SPECIFICATIONS                 | . 8 |

| ABSOLUTE MAXIMUM RATINGS              |     |

| PIN CONFIGURATION                     |     |

| ORDERING GUIDE                        |     |

| PIN FUNCTION DESCRIPTIONS             |     |

| ADuC824 BLOCK DIAGRAM                 |     |

| MEMORY ORGANIZATION                   |     |

|                                       |     |

| OVERVIEW OF MCU-RELATED SFRS          |     |

| Accumulator (ACC)                     |     |

| B SFR (B)                             |     |

| Stack Pointer (SP)                    |     |

| Data Pointer (DPTR)                   |     |

| Program Status Word (PSW)             | 23  |

| Power Control (PCON)                  | 23  |

| SPECIAL FUNCTION REGISTERS            | 24  |

| SFR INTERFACE TO THE PRIMARY AND      |     |

| AUXILIARY ADCs                        | 25  |

| ADCSTAT                               | 25  |

| ADCMODE                               |     |

| ADC0CON                               |     |

| ADC1CON                               |     |

| SF                                    |     |

| ICON                                  |     |

| ADC0H/ADC0M/ADC0L                     |     |

| ADC1H/ADC1L                           |     |

| OF0H/OF0M/OF0L                        |     |

| OF1H/OF1L                             |     |

| GN0H/GN0M/GN0L                        |     |

|                                       |     |

| GN1H/GN1L                             |     |

| PRIMARY AND AUXILIARY ADC DESCRIPTION |     |

| Overview                              |     |

| Primary ADC                           |     |

| Auxiliary ADC                         | 32  |

| PRIMARY AND AUXILIARY ADC NOISE       |     |

| PERFORMANCE                           |     |

| Analog Input Channels                 |     |

| Primary and Auxiliary ADC Inputs      |     |

| Analog Input Ranges                   |     |

| Programmable Gain Amplifier           | 34  |

| Bipolar/Unipolar Inputs               | 34  |

| Burnout Currents                      | 34  |

| Excitation Currents                   | 35  |

| Reference Input                       | 35  |

| Reference Detect                      | 35  |

| Sigma-Delta Modulator                 | 35  |

| Digital Filter                        | 35  |

| ADC Chopping                          | 36  |

|                                       | 37  |

| Sulfitution                           | 51  |

| NONVOLATILE FLASH/EE MEMORY                | 37 |

|--------------------------------------------|----|

| Flash/EE Memory Overview                   |    |

| Flash/EE Memory and the ADuC824            |    |

| ADuC824 Flash/EE Memory Reliability        | 37 |

| Using the Flash/EE Program Memory          |    |

| Flash/EE Program Memory Security           |    |

| Using the Flash/EE Data Memory             |    |

| USER INTERFACE TO OTHER ON-CHIP ADuC824    |    |

| PERIPHERALS                                | 41 |

| DAC                                        | 41 |

| On-Chip PLL                                |    |

| Time Interval Counter (TIC)                | 43 |

| Watchdog Timer                             | 46 |

| Power Supply Monitor                       | 47 |

| Serial Peripheral Interface                | 48 |

| I <sup>2</sup> C-Compatible Interface      | 50 |

| 8051-COMPATIBLE ON-CHIP PERIPHERALS        |    |

| Parallel I/O Ports 0-3                     |    |

| Timers/Counters                            |    |

| TIMER/COUNTER 0 AND 1 OPERATING MODES      |    |

| UART Serial Interface                      |    |

| Interrupt System                           | 60 |

| ADuC824 HARDWARE DESIGN CONSIDERATIONS     |    |

| Clock Oscillator                           |    |

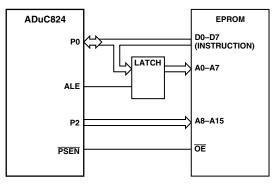

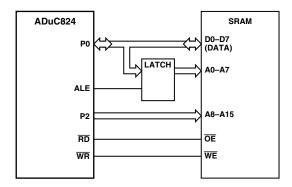

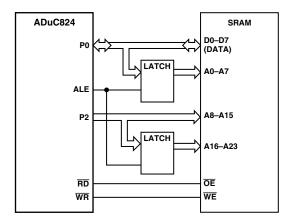

| External Memory Interface                  |    |

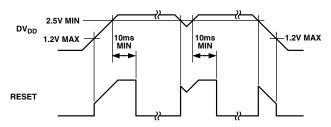

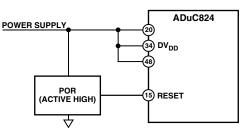

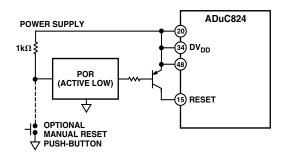

| Power-On Reset Operation                   |    |

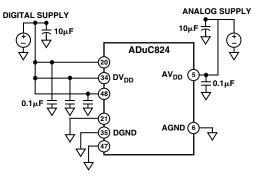

| Power Supplies                             |    |

| Power Consumption                          |    |

| Power-Saving Modes                         |    |

| Grounding and Board Layout Recommendations |    |

| ADuC824 System Self-Identification         | 65 |

| OTHER HARDWARE CONSIDERATIONS              |    |

| In-Circuit Serial Download Access          |    |

| Embedded Serial Port Debugger              |    |

| Single-Pin Emulation Mode                  |    |

| Enhanced-Hooks Emulation Mode              |    |

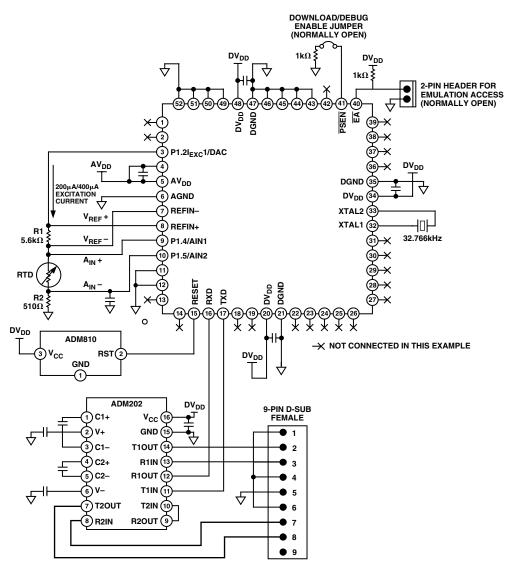

| Typical System Configuration               |    |

| QUICKSTART DEVELOPMENT SYSTEM              |    |

| OUTLINE DIMENSIONS                         |    |

| Revision History                           | 68 |

| Parameter                                      | ADuC824BS        | <b>Test Conditions/Comments</b>                         | Unit                    |

|------------------------------------------------|------------------|---------------------------------------------------------|-------------------------|

| TRANSDUCER BURNOUT CURRENT S                   | OURCES           |                                                         |                         |

| AIN+ Current                                   | -100             | AIN+ is the Selected Positive Input to                  | nA typ                  |

|                                                |                  | the Primary ADC                                         | -51                     |

| AIN- Current                                   | +100             | AIN- is the Selected Negative Input to                  | nA typ                  |

|                                                |                  | the Auxiliary ADC                                       |                         |

| Initial Tolerance @ 25°C Drift                 | ±10              |                                                         | % typ                   |

| Drift                                          | 0.03             |                                                         | %/°C typ                |

|                                                | 0.05             |                                                         | , or C typ              |

| EXCITATION CURRENT SOURCES                     |                  |                                                         |                         |

| Output Current                                 | -200             | Available from Each Current Source                      | μA typ                  |

| Initial Tolerance @ 25°C                       | ±10              |                                                         | % typ                   |

| Drift                                          | 200              |                                                         | ppm/°C typ              |

| Initial Current Matching @ 25°C                | ±1               | Matching Between Both Current Sources                   | % typ                   |

| Drift Matching                                 | 20               |                                                         | ppm/°C typ              |

| Line Regulation (AV <sub>DD</sub> )            | 1                | $AV_{DD} = 5 V + 5\%$                                   | µA/V typ                |

| Load Regulation                                | 0.1              |                                                         | µA/V typ                |

| Output Compliance                              | $AV_{DD} - 0.6$  |                                                         | V max                   |

|                                                | AGND             |                                                         | min                     |

| LOGIC INPUTS                                   |                  |                                                         |                         |

| All Inputs Except SCLOCK, RESET,               |                  |                                                         |                         |

| and XTAL1                                      |                  |                                                         |                         |

|                                                | 0.0              | DV = 5V                                                 | <b>X</b> 7              |

| V <sub>INL</sub> , Input Low Voltage           | 0.8              | $DV_{DD} = 5 V$                                         | V max                   |

| <b>X7 T . TT' 1 X7 1</b> .                     | 0.4              | $DV_{DD} = 3 V$                                         | V max                   |

| V <sub>INH</sub> , Input High Voltage          | 2.0              |                                                         | V min                   |

| SCLOCK and RESET Only                          |                  |                                                         |                         |

| (Schmitt-Triggered Inputs) <sup>2</sup>        |                  |                                                         |                         |

| $V_{T+}$                                       | 1.3/3            | $DV_{DD} = 5 V$                                         | V min/V max             |

|                                                | 0.95/2.5         | $DV_{DD} = 3 V$                                         | V min/V max             |

| $V_{T-}$                                       | 0.8/1.4          | $DV_{DD} = 5 V$                                         | V min/V max             |

|                                                | 0.4/1.1          | $DV_{DD} = 3 V$                                         | V min/V max             |

| $V_{T+} - V_{T-}$                              | 0.3/0.85         | $DV_{DD} = 5 V$                                         | V min/V max             |

|                                                | 0.3/0.85         | $DV_{DD} = 3 V$                                         | V min/V max             |

| Input Currents                                 |                  |                                                         |                         |

| Port 0, P1.2–P1.7, EA                          | ±10              | $V_{IN} = 0 V \text{ or } V_{DD}$                       | μA max                  |

| SCLOCK, SDATA/MOSI, MISO, $\overline{SS}^{12}$ | -10 min, -40 max | $V_{IN} = 0 V, DV_{DD} = 5 V,$ Internal Pull-Up         | μA min/μA max           |

|                                                | ±10              | $V_{IN} = V_{DD}, DV_{DD} = 5 V$                        | μA max                  |

| RESET                                          | ±10              | $V_{IN} = 0 V, DV_{DD} = 5 V$                           | μA max                  |

|                                                | 35 min, 105 max  | $V_{\rm IN} = V_{\rm DD}, DV_{\rm DD} = 5 V,$           | $\mu A \min/\mu A \max$ |

|                                                |                  | Internal Pull-Down                                      |                         |

| P1.0, P1.1, Ports 2 and 3                      | ±10              | $V_{IN} = V_{DD}, DV_{DD} = 5 V$                        | µA max                  |

|                                                | -180             | $V_{IN} = 2 V, DV_{DD} = 5 V$                           | µA min                  |

|                                                | -660             |                                                         | µA max                  |

|                                                | -20              | $V_{IN} = 450 \text{ mV}, \text{DV}_{DD} = 5 \text{ V}$ | µA min                  |

|                                                | -75              |                                                         | μA max                  |

| Input Capacitance                              | 5                | All Digital Inputs                                      | pF typ                  |

|                                                |                  |                                                         | r- 'Jr                  |

| CRYSTAL OSCILLATOR (XTAL1 AND X                | TAL2)            |                                                         |                         |

| Logic Inputs, XTAL1 Only                       | 1                |                                                         |                         |

| V <sub>INL</sub> , Input Low Voltage           | 0.8              | $DV_{DD} = 5 V$                                         | V max                   |

|                                                | 0.4              | $DV_{DD} = 3 V$                                         | V max                   |

| V <sub>INH</sub> , Input High Voltage          | 3.5              | $DV_{DD} = 5 V$                                         | V min                   |

|                                                | 2.5              | $DV_{DD} = 3 V$                                         | V min                   |

| XTAL1 Input Capacitance                        | 18               |                                                         | pF typ                  |

| XTAL2 Output Capacitance                       | 18               |                                                         | pF typ                  |

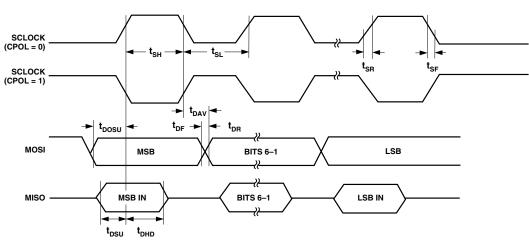

| Parameter         | •                                        | Min | Тур | Max | Unit | Figure |

|-------------------|------------------------------------------|-----|-----|-----|------|--------|

| SPI MAST          | ER MODE TIMING (CPHA = 0)                |     |     |     |      |        |

| t <sub>SL</sub>   | SCLOCK Low Pulsewidth*                   |     | 630 |     | ns   | 9      |

| t <sub>SH</sub>   | SCLOCK High Pulsewidth*                  |     | 630 |     | ns   | 9      |

| t <sub>DAV</sub>  | Data Output Valid after SCLOCK Edge      |     |     | 50  | ns   | 9      |

| t <sub>DOSU</sub> | Data Output Setup before SCLOCK Edge     |     |     | 150 | ns   | 9      |

| t <sub>DSU</sub>  | Data Input Setup Time before SCLOCK Edge | 100 |     |     | ns   | 9      |

| t <sub>DHD</sub>  | Data Input Hold Time after SCLOCK Edge   | 100 |     |     | ns   | 9      |

| t <sub>DF</sub>   | Data Output Fall Time                    |     | 10  | 25  | ns   | 9      |

| t <sub>DR</sub>   | Data Output Rise Time                    |     | 10  | 25  | ns   | 9      |

| t <sub>SR</sub>   | SCLOCK Rise Time                         |     | 10  | 25  | ns   | 9      |

| t <sub>SF</sub>   | SCLOCK Fall Time                         |     | 10  | 25  | ns   | 9      |

\*Characterized under the following conditions:

a. Core clock divider bits CD2, CD1, and CD0 bits in PLLCON SFR set to 0, 1, and 1 respectively, i.e., core clock frequency = 1.57 MHz and b. SPI bit-rate selection bits SPR1 and SPR0 bits in SPICON SFR set to 0 and 0 respectively.

Figure 9. SPI Master Mode Timing (CPHA = 0)

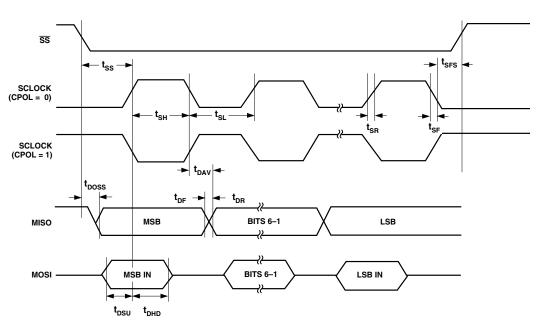

| Parameter                        | ſ                                            | Min | Тур | Max | Unit | Figure |

|----------------------------------|----------------------------------------------|-----|-----|-----|------|--------|

| SPI SLAVE MODE TIMING (CPHA = 0) |                                              |     |     |     |      |        |

| t <sub>SS</sub>                  | SS to SCLOCK Edge                            | 0   |     |     | ns   | 11     |

| t <sub>SL</sub>                  | SCLOCK Low Pulsewidth                        |     | 330 |     | ns   | 11     |

| t <sub>SH</sub>                  | SCLOCK High Pulsewidth                       |     | 330 |     | ns   | 11     |

| t <sub>DAV</sub>                 | Data Output Valid after SCLOCK Edge          |     |     | 50  | ns   | 11     |

| t <sub>DSU</sub>                 | Data Input Setup Time before SCLOCK Edge     | 100 |     |     | ns   | 11     |

| t <sub>DHD</sub>                 | Data Input Hold Time after SCLOCK Edge       | 100 |     |     | ns   | 11     |

| t <sub>DF</sub>                  | Data Output Fall Time                        |     | 10  | 25  | ns   | 11     |

| t <sub>DR</sub>                  | Data Output Rise Time                        |     | 10  | 25  | ns   | 11     |

| t <sub>SR</sub>                  | SCLOCK Rise Time                             |     | 10  | 25  | ns   | 11     |

| t <sub>SF</sub>                  | SCLOCK Fall Time                             |     | 10  | 25  | ns   | 11     |

| t <sub>SSR</sub>                 | SS to SCLOCK Edge                            |     |     | 50  | ns   | 11     |

| t <sub>DOSS</sub>                | Data Output Valid after $\overline{SS}$ Edge |     |     | 20  | ns   | 11     |

| t <sub>SFS</sub>                 | SS High after SCLOCK Edge                    | 0   |     |     | ns   | 11     |

Figure 11. SPI Slave Mode Timing (CPHA = 0)

#### ADCMODE (ADC Mode Register)

Used to control the operational mode of both ADCs.

| SFR Address            | D1H |

|------------------------|-----|

| Power-On Default Value | 00H |

| Bit Addressable        | No  |

|                        |     |

|   |   | 1      | 1      | 1 |     |     |     |

|---|---|--------|--------|---|-----|-----|-----|

| _ | _ | ADC0EN | ADC1EN | — | MD2 | MD1 | MD0 |

|   |   |        |        |   |     |     |     |

Table IV. ADCMODE SFR Bit Designations

| Bit | Name   | Descr  | iption                                                                                       |           |                                                                       |  |  |  |  |  |

|-----|--------|--------|----------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------|--|--|--|--|--|

| 7   |        | Reserv | Reserved for Future Use                                                                      |           |                                                                       |  |  |  |  |  |

| 6   | _      | Reserv | Reserved for Future Use                                                                      |           |                                                                       |  |  |  |  |  |

| 5   | ADC0EN | Primar | y ADC E                                                                                      | Inable    |                                                                       |  |  |  |  |  |

|     |        |        | Set by the user to enable the Primary ADC and place it in the mode selected in MD2–MD0 below |           |                                                                       |  |  |  |  |  |

|     |        |        |                                                                                              |           | ace the Primary ADC in power-down mode.                               |  |  |  |  |  |

| 4   | ADC1EN |        | ary ADC                                                                                      |           |                                                                       |  |  |  |  |  |

|     |        |        |                                                                                              |           | the Auxiliary ADC and place it in the mode selected in MD2–MD0 below  |  |  |  |  |  |

|     |        |        | Cleared by the user to place the Auxiliary ADC in power-down mode.                           |           |                                                                       |  |  |  |  |  |

| 3   | _      |        | Reserved for Future Use                                                                      |           |                                                                       |  |  |  |  |  |

| 2   | MD2    | Primar | y and Au                                                                                     | xiliary A | DC Mode bits.                                                         |  |  |  |  |  |

| 1   | MD1    | These  | bits selec                                                                                   | t the ope | erational mode of the enabled ADC as follows:                         |  |  |  |  |  |

| 0   | MD0    | MD2    | MD1                                                                                          | MD        | 0                                                                     |  |  |  |  |  |

|     |        | 0      | 0                                                                                            | 0         | Power-Down Mode (Power-On Default)                                    |  |  |  |  |  |

|     |        | 0      | 0                                                                                            | 1         | Idle Mode                                                             |  |  |  |  |  |

|     |        |        |                                                                                              |           | In Idle Mode the ADC filter and modulator are held in a reset state   |  |  |  |  |  |

|     |        |        |                                                                                              |           | although the modulator clocks are still provided.                     |  |  |  |  |  |

|     |        | 0      | 1                                                                                            | 0         | Single Conversion Mode                                                |  |  |  |  |  |

|     |        |        |                                                                                              |           | In Single Conversion Mode, a single conversion is performed on the    |  |  |  |  |  |

|     |        |        |                                                                                              |           | enabled ADC. On completion of the conversion, the ADC data regis-     |  |  |  |  |  |

|     |        |        |                                                                                              |           | ters (ADC0H/M/L and/or ADC1H/L) are updated, the relevant flags       |  |  |  |  |  |

|     |        |        |                                                                                              |           | in the ADCSTAT SFR are written, and power-down is re-entered with     |  |  |  |  |  |

|     |        |        |                                                                                              |           | the MD2-MD0 accordingly being written to 000.                         |  |  |  |  |  |

|     |        | 0      | 1                                                                                            | 1         | Continuous Conversion                                                 |  |  |  |  |  |

|     |        |        |                                                                                              |           | In continuous conversion mode the ADC data registers are regularly    |  |  |  |  |  |

|     |        |        |                                                                                              |           | updated at the selected update rate (see SF register)                 |  |  |  |  |  |

|     |        | 1      | 0                                                                                            | 0         | Internal Zero-Scale Calibration                                       |  |  |  |  |  |

|     |        |        |                                                                                              |           | Internal short is automatically connected to the enabled ADC(s)       |  |  |  |  |  |

|     |        | 1      | 0                                                                                            | 1         | Internal Full-Scale Calibration                                       |  |  |  |  |  |

|     |        |        |                                                                                              |           | Internal or External $V_{REF}$ (as determined by XREF0 and XREF1 bits |  |  |  |  |  |

|     |        |        |                                                                                              |           | in ADC0/1CON) is automatically connected to the ADC input for         |  |  |  |  |  |

|     |        |        |                                                                                              | 0         | this calibration.                                                     |  |  |  |  |  |

|     |        | 1      | 1                                                                                            | 0         | System Zero-Scale Calibration                                         |  |  |  |  |  |

|     |        |        |                                                                                              |           | User should connect system zero-scale input to the ADC input pins     |  |  |  |  |  |

|     |        |        |                                                                                              |           | as selected by CH1/CH0 and ACH1/ACH0 bits in the ADC0/1CON            |  |  |  |  |  |

|     |        |        | 1                                                                                            | 1         | register.                                                             |  |  |  |  |  |

|     |        | 1      | 1                                                                                            | 1         | System Full-Scale Calibration                                         |  |  |  |  |  |

|     |        |        |                                                                                              |           | User should connect system full-scale input to the ADC input pins as  |  |  |  |  |  |

|     |        |        |                                                                                              |           | selected by CH1/CH0 and ACH1/ACH0 bits in the ADC0/1CON               |  |  |  |  |  |

|     |        |        |                                                                                              |           | register.                                                             |  |  |  |  |  |

#### NOTES

Any change to the MD bits will immediately reset both ADCs. A write to the MD2-0 bits with no change is also treated as a reset. (See exception to this in Note 3 below.)

If ADC0CON is written when AD0EN = 1, or if AD0EN is changed from 0 to 1, then both ADCs are also immediately reset. In other words, the Primary ADC is given priority over the Auxiliary ADC and any change requested on the primary ADC is immediately responded to.

3. On the other hand, if ADC1CON is written or if ADC1EN is changed from 0 to 1, only the Auxiliary ADC is reset. For example, if the Primary ADC is continuously converting when the Auxiliary ADC change or enable occurs, the primary ADC continues undisturbed. Rather than allow the Auxiliary ADC to operate with a phase difference from the primary ADC, the Auxiliary ADC will fall into step with the outputs of the primary ADC. The result is that the first conversion time for the Auxiliary ADC will be delayed up to three outputs while the Auxiliary ADC update rate is synchronized to the Primary ADC.

4. Once ADCMODE has been written with a calibration mode, the RDY0/1 bits (ADCSTAT) are immediately reset and the calibration commences. On completion, the appropriate calibration registers are written, the relevant bits in ADCSTAT are written, and the MD2–0 bits are reset to 000 to indicate the ADC is back in power-down mode.

5. Any calibration request of the Auxiliary ADC while the temperature sensor is selected will fail to complete. Although the RDY1 bit will be set at the end of the calibration cycle, no update of the calibration SFRs will take place and the ERR1 bit will be set.

6. Calibrations are performed at maximum SF (see SF SFR) value guaranteeing optimum calibration operation.

#### ADC0CON (Primary ADC Control Register)

Used to configure the Primary ADC for range, channel selection, external Ref enable, and unipolar or bipolar coding.

| SFR Address            | D2H |

|------------------------|-----|

| Power-On Default Value | 07H |

| Bit Addressable        | No  |

| — | XREF0 | CH1 | CH0 | UNI0 | RN2 | RN1 | RN0 |

|---|-------|-----|-----|------|-----|-----|-----|

#### Table V. ADC0CON SFR Bit Designations

| Bit | Name  | Descripti         | on                                                                                                     |             |                                                                         |  |  |  |  |

|-----|-------|-------------------|--------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------|--|--|--|--|

| 7   |       | Reserved f        | Reserved for Future Use                                                                                |             |                                                                         |  |  |  |  |

| 6   | XREF0 | Primary A         | DC Exte                                                                                                | rnal Refe   | rence Select Bit                                                        |  |  |  |  |

|     |       | Set by user       | to enable                                                                                              | le the Prin | nary ADC to use the external reference via REFIN(+)/REFIN(-).           |  |  |  |  |

|     |       | <i>Cleared</i> by | <i>Cleared</i> by user to enable the Primary ADC to use the internal bandgap reference ( $V_{REF} = 1$ |             |                                                                         |  |  |  |  |

| 5   | CH1   | Primary A         |                                                                                                        |             |                                                                         |  |  |  |  |

| 4   | CH0   | Written by        | the differential input pairs used by the Primary ADC as follows:                                       |             |                                                                         |  |  |  |  |

|     |       | CH1               | CH0                                                                                                    |             | re Input Negative Input                                                 |  |  |  |  |

|     |       | 0                 | 0                                                                                                      | AIN1        | AIN2                                                                    |  |  |  |  |

|     |       | 0                 | 1                                                                                                      | AIN3        | AIN4                                                                    |  |  |  |  |

|     |       | 1                 | 0                                                                                                      | AIN2        |                                                                         |  |  |  |  |

|     |       | 1                 | 1                                                                                                      | AIN3        | AIN2                                                                    |  |  |  |  |

| 3   | UNI0  | Primary A         | -                                                                                                      |             |                                                                         |  |  |  |  |

|     |       |                   |                                                                                                        |             | coding, i.e., zero differential input will result in 000000 hex output. |  |  |  |  |

|     |       |                   |                                                                                                        |             | olar coding, zero differential input will result in 800000 hex output.  |  |  |  |  |

| 2   | RN2   | Primary A         |                                                                                                        | -           |                                                                         |  |  |  |  |

| 1   | RN1   |                   |                                                                                                        |             | the Primary ADC input range as follows:                                 |  |  |  |  |

| 0   | RN0   | RN2               | RN1                                                                                                    | RN0         | Selected Primary ADC Input Range ( $V_{REF} = 2.5 \text{ V}$ )          |  |  |  |  |

|     |       | 0                 | 0                                                                                                      | 0           | $\pm 20 \text{ mV}$                                                     |  |  |  |  |

|     |       | 0                 | 0                                                                                                      | 1           | $\pm 40 \text{ mV}$                                                     |  |  |  |  |

|     |       | 0                 | 1                                                                                                      | 0           | $\pm 80 \text{ mV}$                                                     |  |  |  |  |

|     |       | 0                 | 1                                                                                                      | 1           | $\pm 160 \text{ mV}$                                                    |  |  |  |  |

|     |       | 1                 | 0                                                                                                      | 0           | $\pm 320 \text{ mV}$                                                    |  |  |  |  |

|     |       | 1                 | 0                                                                                                      | 1           | $\pm 640 \text{ mV}$                                                    |  |  |  |  |

|     |       |                   | 1                                                                                                      | 0           | ±1.28 V                                                                 |  |  |  |  |

|     |       |                   | 1                                                                                                      | 1           | ±2.56 V                                                                 |  |  |  |  |

#### ADC1CON (Auxiliary ADC Control Register)

Used to configure the Auxiliary ADC for channel selection, external Ref enable and unipolar or bipolar coding. It should be noted that the Auxiliary ADC only operates on a fixed input range of  $\pm V_{REF}$ .

| SFR Address            | D3H |

|------------------------|-----|

| Power-On Default Value | 00H |

| Bit Addressable        | No  |

|                        |     |

| _ | XREF1 | ACH1 | ACH0 | UNI1 | _ | — | _ |

|---|-------|------|------|------|---|---|---|

|---|-------|------|------|------|---|---|---|

#### Table VI. ADC1CON SFR Bit Designations

| Bit | Name  | Descript   | ion            |                        |                                                          |

|-----|-------|------------|----------------|------------------------|----------------------------------------------------------|

| 7   | _     | Reserved   | for Future U   | Jse                    |                                                          |

| 6   | XREF1 | Auxiliary  | ADC Extern     | nal Reference Bit      |                                                          |

|     |       | Set by use | er to enable t | the Auxiliary ADC t    | o use the external reference via REFIN(+)/REFIN(-).      |

|     |       | Cleared by | y user to ena  | ble the Auxiliary AI   | OC to use the internal bandgap reference.                |

| 5   | ACH1  | Auxiliary  | ADC Chann      | nel Selection Bits     |                                                          |

| 4   | ACH0  | Written by | y the user to  | select the single-ende | d input pins used to drive the Auxiliary ADC as follows: |

|     |       | ACH1       | ACH0           | Positive Input         | Negative Input                                           |

|     |       | 0          | 0              | AIN3                   | AGND                                                     |

|     |       | 0          | 1              | AIN4                   | AGND                                                     |

|     |       | 1          | 0              | Temp Sensor*           | AGND (Temp. Sensor routed to the ADC input)              |

|     |       | 1          | 1              | AIN5                   | AGND                                                     |

| 3   | UNI1  | Auxiliary  | ADC Unipo      | olar Bit               |                                                          |

|     |       | Set by use | er to enable   | unipolar coding, i.e., | zero input will result in 0000 hex output.               |

|     |       | Cleared by | y user to ena  | ble bipolar coding, z  | zero input will result in 8000 hex output.               |

| 2   | _     | Reserved   | for Future U   | Jse                    |                                                          |

| 1   | —     | Reserved   | for Future U   | Jse                    |                                                          |

| 0   | —     | Reserved   | for Future U   | Jse                    |                                                          |

\*NOTES

1. When the temperature sensor is selected, user code must select internal reference via XREF1 bit above and clear the UNI1 bit (ADC1CON.3) to select bipolar coding.

The temperature sensor is factory calibrated to yield conversion results 8000H at 0 °C.

A +1°C change in temperature will result in a +1 LSB change in the ADC1H register ADC conversion result.

#### SF (Sinc Filter Register)

The number in this register sets the decimation factor and thus the output update rate for the Primary and Auxiliary ADCs. This SFR cannot be written by user software while either ADC is active. The update rate applies to both Primary and Auxiliary ADCs and is calculated as follows:

$$f_{ADC} = \frac{1}{3} \times \frac{1}{8 \mathcal{S} F} \times f_{MOD}$$

Where:

$$f_{ADC}$$

= ADC Output Update Rate

$f_{MOD}$  = Modulator Clock Frequency = 32.768 kHz SF = Decimal Value of SF Register

The allowable range for SF is 0Dhex to FFhex. Examples of SF values and corresponding conversion update rate  $(f_{ADC})$  and con-

version time ( $t_{ADC}$ ) are shown in Table VII, the power-on default value for the SF register is 45hex, resulting in a default ADC update rate of just under 20 Hz. Both ADC inputs are chopped to minimize offset errors, which means that the settling time for a single conversion or the time to a first conversion result in continuous conversion mode is  $2 \times t_{ADC}$ . As mentioned earlier, all calibration cycles will be carried out automatically with a maximum, i.e., FFhex, SF value to ensure optimum calibration performance. Once a calibration cycle has completed, the value in the SF register will be that programmed by user software.

Table VII. SF SFR Bit Designations

| SF(dec) | SF(hex) | f <sub>ADC</sub> (Hz) | t <sub>ADC</sub> (ms) |

|---------|---------|-----------------------|-----------------------|

| 13      | 0D      | 105.3                 | 9.52                  |

| 69      | 45      | 19.79                 | 50.34                 |

| 255     | FF      | 5.35                  | 186.77                |

The absolute input voltage range on the auxiliary ADC is restricted to between AGND -30 mV to AVDD +30 mV. The slightly negative absolute input voltage limit does allow the possibility of monitoring small signal bipolar signals using the single-ended auxiliary ADC front end.

#### **Programmable Gain Amplifier**

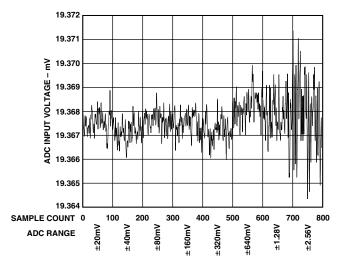

The output from the buffer on the primary ADC is applied to the input of the on-chip programmable gain amplifier (PGA). The PGA can be programmed through eight different unipolar input ranges and bipolar ranges. The PGA gain range is programmed via the range bits in the ADC0CON SFR. With the external reference select bit set in the ADC0CON SFR and an external 2.5 V reference, the unipolar ranges are 0 mV to 20 mV, 0 mV to 40 mV, 0 mV to 80 mV, 0 mV to 160 mV, 0 mV to 320 mV, 0 mV to 640 mV, 0 V to 1.28 V, and 0 to 2.56 V, while the bipolar ranges are  $\pm 20 \text{ mV}$ ,  $\pm 40 \text{ mV}$ ,  $\pm 80 \text{ mV}$ ,  $\pm 160 \text{ mV}$ ,  $\pm$  320 mV,  $\pm$  640 mV,  $\pm$  1.28 V, and  $\pm$  2.56 V. These are the nominal ranges that should appear at the input to the on-chip PGA. An ADC range matching specification of 2 µV (typ) across all ranges means that calibration need only be carried out at a single gain range and does not have to be repeated when the PGA gain range is changed.

Typical matching across ranges is shown in Figure 20 below. Here, the primary ADC is configured in bipolar mode with an external 2.5 V reference, while just greater than 19 mV is forced on its inputs. The ADC continuously converts the DC input voltage at an update rate of 5.35 Hz, i.e., SF = FFhex. In total, 800 conversion results are gathered. The first 100 results are gathered with the primary ADC operating in the  $\pm 20$  mV range. The ADC range is then switched to  $\pm 40$  mV and 100 more conversion results are gathered, and so on until the last group of 100 samples are gathered with the ADC configured in the  $\pm 2.56$  V range. From Figure 20, The variation in the sample mean through each range, i.e., the range matching, is seen to be of the order of 2  $\mu$ V.

The auxiliary ADC does not incorporate a PGA and is configured for a fixed single input range of 0 to  $V_{\rm REF}.$

Figure 20. Primary ADC Range Matching

#### **Bipolar/Unipolar Inputs**

The analog inputs on the ADuC824 can accept either unipolar or bipolar input voltage ranges. Bipolar input ranges do not imply that the part can handle negative voltages with respect to system AGND.

Unipolar and bipolar signals on the AIN(+) input on the primary ADC are referenced to the voltage on the respective AIN(-) input. For example, if AIN(-) is 2.5 V and the primary ADC is configured for an analog input range of 0 mV to 20 mV, the input voltage range on the AIN(+) input is 2.5 V to 2.52 V. If AIN(-) is 2.5 V and the ADuC824 is configured for an analog input range of 1.28 V, the analog input range on the AIN(+) input is 1.22 V to 3.78 V (i.e.,  $2.5 V \pm 1.28 V$ ).

As mentioned earlier, the auxiliary ADC input is a single-ended input with respect to the system AGND. In this context a bipolar signal on the auxiliary ADC can only span 30 mV negative with respect to AGND before violating the voltage input limits for this ADC.

Bipolar or unipolar options are chosen by programming the Primary and Auxiliary Unipolar enable bits in the ADC0CON and ADC1CON SFRs respectively. This programs the relevant ADC for either unipolar or bipolar operation. Programming for either unipolar or bipolar operation does not change any of the input signal conditioning; it simply changes the data output coding and the points on the transfer function where calibrations occur. When an ADC is configured for unipolar operation, the output coding is natural (straight) binary with a zero differential input voltage resulting in a code of 000 . . . 000, a midscale voltage resulting in a code of 100 . . . 000, and a full-scale input voltage resulting in a code of 111 ... 111. When an ADC is configured for bipolar operation, the coding is offset binary with a negative full-scale voltage resulting in a code of 000...000, a zero differential voltage resulting in a code of 100...000, and a positive full-scale voltage resulting in a code of 111...111.

#### **Burnout Currents**

The primary ADC on the ADuC824 contains two 100 nA constant current generators, one sourcing current from AVDD to AIN(+), and one sinking from AIN(-) to AGND. The currents are switched to the selected analog input pair. Both currents are either on or off, depending on the Burnout Current Enable (BO) bit in the ICON SFR (see Table VIII). These currents can be used to verify that an external transducer is still operational before attempting to take measurements on that channel. Once the burnout currents are turned on, they will flow in the external transducer circuit, and a measurement of the input voltage on the analog input channel can be taken. If the resultant voltage measured is full-scale, this indicates that the transducer has gone open-circuit. If the voltage measured is 0 V, it indicates that the transducer has short circuited. For normal operation, these burnout currents are turned off by writing a 0 to the BO bit in the ICON SFR. The current sources work over the normal absolute input voltage range specifications.

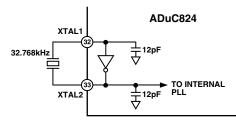

#### **ON-CHIP PLL**

The ADuC824 is intended for use with a 32.768 kHz watch crystal. A PLL locks onto a multiple (384) of this to provide a stable 12.582912 MHz clock for the system. The core can operate at this frequency or at binary submultiples of it to allow power saving in cases where maximum core performance is not required. The default core clock is the PLL clock divided by 8 or 1.572864 MHz. The ADC clocks are also derived from the PLL clock, with the modulator rate being the same as the crystal oscillator frequency. The above choice of frequencies ensures that the modulators and the core will be synchronous, regardless of the core clock rate. The PLL control register is PLLCON.

| PLLCON          |           | PLL Control | l Register |      |     |     |      |

|-----------------|-----------|-------------|------------|------|-----|-----|------|

| SFR Address     |           | D7H         |            |      |     |     |      |

| Power-On Defau  | ılt Value | 03H         |            |      |     |     |      |

| Bit Addressable |           | No          |            |      |     |     |      |

|                 |           |             |            |      |     |     | · `` |

| OSC_PD          | LOCK      | —           | LTEA       | FINT | CD2 | CD1 | CD0  |

Table XV. PLLCON SFR Bit Designations

| Bit | Name   | Descrij   | otion           |                   |                                                                         |

|-----|--------|-----------|-----------------|-------------------|-------------------------------------------------------------------------|

| 7   | OSC_PD | Oscillat  | or Power-do     | wn Bit            |                                                                         |

|     |        | Set by u  | ser to halt th  | ne 32 kHz oscill  | ator in power-down mode.                                                |

|     |        | Cleared   | by user to en   | hable the 32 kH   | z oscillator in power-down mode.                                        |

|     |        | This fea  | ture allows     | the TIC to cont   | tinue counting even in power-down mode.                                 |

| 6   | LOCK   | PLL Lo    | ck Bit          |                   |                                                                         |

|     |        | This is a | a read only b   | oit.              |                                                                         |

|     |        | Set auto  | matically at j  | power-on to ind   | icate the PLL loop is correctly tracking the crystal clock. If the      |

|     |        | external  | crystal beco    | omes subsequer    | ntly disconnected the PLL will rail and the core will halt.             |

|     |        | Cleared   | automaticall    | y at power-on t   | to indicate the PLL is not correctly tracking the crystal clock.        |

|     |        | This ma   | y be due to     | the absence of a  | crystal clock or an external crystal at power-on. In this mode,         |

|     |        | the PLI   | output can      | be 12.58 MHz      | ± 20%.                                                                  |

| 5   | _      |           |                 |                   | written with '0.'                                                       |

| 4   | LTEA   | Reading   | , this bit retu | arns the state of | f the external $\overline{\text{EA}}$ pin latched at reset or power-on. |

| 3   | FINT   | Fast Int  | errupt Resp     | onse Bit          |                                                                         |

|     |        |           |                 |                   | any interrupt to be executed at the fastest core clock frequency,       |

|     |        |           |                 |                   | CD2–0 bits (see below). Once user code has returned from an             |

|     |        |           |                 |                   | ecution at the core clock selected by the CD2-0 bits.                   |

|     |        |           |                 |                   | nterrupt response feature.                                              |

| 2   | CD2    |           |                 | Divider Bits      |                                                                         |

| 1   | CD1    |           |                 |                   | ency at which the microcontroller core will operate.                    |

| 0   | CD0    | CD2       | CD1             | CD0               | Core Clock Frequency (MHz)                                              |

|     |        | 0         | 0               | 0                 | 12.582912                                                               |

|     |        | 0         | 0               | 1                 | 6.291456                                                                |

|     |        | 0         | 1               | 0                 | 3.145728                                                                |

|     |        | 0         | 1               | 1                 | 1.572864 (Default Core Clock Frequency)                                 |

|     |        | 1         | 0               | 0                 | 0.786432                                                                |

|     |        | 1         | 0               | 1                 | 0.393216                                                                |

|     |        |           | 1               | 0                 | 0.196608                                                                |

|     |        | 1         | 1               | 1                 | 0.098304                                                                |

#### TIME INTERVAL COUNTER (TIC)

A time interval counter is provided on-chip for counting longer intervals than the standard 8051-compatible timers are capable of. The TIC is capable of timeout intervals ranging from 1/128th second to 255 hours. Furthermore, this counter is clocked by the crystal oscillator rather than the PLL and thus has the ability to remain active in power-down mode and time long power-down intervals. This has obvious applications for remote battery-powered sensors where regular widely spaced readings are required.

Six SFRs are associated with the time interval counter, TIMECON being its control register. Depending on the configuration of the IT0 and IT1 bits in TIMECON, the selected time counter register

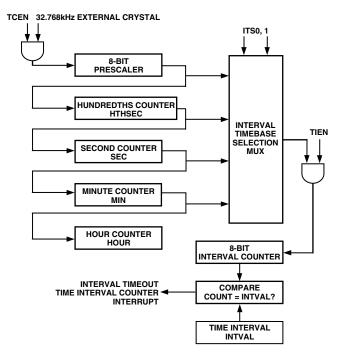

overflow will clock the interval counter. When this counter is equal to the time interval value loaded in the INTVAL SFR, the TII bit (TIMECON.2) is set and generates an interrupt if enabled (See IEIP2 SFR description under Interrupt System later in this data sheet.) If the ADuC824 is in power-down mode, again with TIC interrupt enabled, the TII bit will wake up the device and resume code execution by vectoring directly to the TIC interrupt service vector address at 0053 hex. The TIC-related SFRs are described in Table XVI. Note also that the timebase SFRs can be written initially with the current time, the TIC can then be controlled and accessed by user software. In effect, this facilitates the implementation of a real-time clock. A block diagram of the TIC is shown in Figure 32.

Figure 32. TIC, Simplified Block Diagram

—

| TIMECON         |          | TIC Control | Register |     |     |      |      |

|-----------------|----------|-------------|----------|-----|-----|------|------|

| SFR Address     |          | A1H         |          |     |     |      |      |

| Power-On Defau  | lt Value | 00H         |          |     |     |      |      |

| Bit Addressable |          | No          |          |     |     |      |      |

|                 |          |             |          |     |     |      |      |

| _               | _        | ITS1        | ITS0     | STI | TII | TIEN | ICEN |

#### Table XVI. TIMECON SFR Bit Designations

| Bit | Name | Description                                                                                            |

|-----|------|--------------------------------------------------------------------------------------------------------|

| 7   | _    | Reserved for Future Use                                                                                |

| 6   | _    | Reserved for Future Use. For future product code compatibility this bit should be written as a '1.'    |

| 5   | ITS1 | Interval Timebase Selection Bits.                                                                      |

| 4   | ITS0 | Written by user to determine the interval counter update rate.                                         |

|     |      | ITS1 ITS0 Interval Timebase                                                                            |

|     |      | 0 0 1/128 Second                                                                                       |

|     |      | 0 1 Seconds                                                                                            |

|     |      | 1 0 Minutes                                                                                            |

|     |      | 1 1 Hours                                                                                              |

| 3   | STI  | Single Time Interval Bit                                                                               |

|     |      | Set by user to generate a single interval timeout. If set, a timeout will clear the TIEN bit.          |

|     |      | Cleared by user to allow the interval counter to be automatically reloaded and start counting again at |

|     |      | each interval timeout.                                                                                 |

| 2   | TII  | TIC Interrupt Bit                                                                                      |

|     |      | Set when the 8-bit Interval Counter matches the value in the INTVAL SFR.                               |

|     |      | Cleared by user software.                                                                              |

| 1   | TIEN | Time Interval Enable Bit                                                                               |

|     |      | Set by user to enable the 8-bit time interval counter.                                                 |

|     |      | Cleared by user to disable and clear the contents of the interval counter.                             |

| 0   | TCEN | Time Clock Enable Bit                                                                                  |

|     |      | Set by user to enable the time clock to the time interval counters.                                    |

|     |      | Cleared by user to disable the clock to the time interval counters and clear the time interval SFRs.   |

|     |      | The time registers (HTHSEC, SEC, MIN and HOUR) can be written while TCEN is low.                       |

#### SERIAL PERIPHERAL INTERFACE

The ADuC824 integrates a complete hardware Serial Peripheral Interface (SPI) interface on-chip. SPI is an industry standard synchronous serial interface that allows eight bits of data to be synchronously transmitted and received simultaneously, i.e., full duplex. It should be noted that the SPI physical interface is shared with the I<sup>2</sup>C interface and therefore the user can only enable one or the other interface at any given time (see SPE in SPICON below). The system can be configured for Master or Slave operation and typically consists of four pins, namely:

#### MISO (Master In, Slave Out Data I/O Pin), Pin#14

The MISO (master in slave out) pin is configured as an input line in master mode and an output line in slave mode. The MISO line on the master (data in) should be connected to the MISO line in the slave device (data out). The data is transferred as byte wide (8-bit) serial data, MSB first.

#### MOSI (Master Out, Slave In Pin), Pin#27

The MOSI (master out slave in) pin is configured as an output line in master mode and an input line in slave mode. The MOSI line on the master (data out) should be connected to the MOSI line in the slave device (data in). The data is transferred as byte wide (8-bit) serial data, MSB first.

#### SCLOCK (Serial Clock I/O Pin), Pin#26

The master clock (SCLOCK) is used to synchronize the data being transmitted and received through the MOSI and MISO data

lines. A single data bit is transmitted and received in each SCLOCK period. Therefore, a byte is transmitted/received after eight SCLOCK periods. The SCLOCK pin is configured as an output in master mode and as an input in slave mode. In master mode the bit-rate, polarity and phase of the clock are controlled by the CPOL, CPHA, SPR0 and SPR1 bits in the SPICON SFR (see Table XIX). In slave mode the SPICON register will have to be configured with the phase and polarity (CPHA and CPOL) of the expected input clock. In both master and slave mode the data is transmitted on one edge of the SCLOCK signal and sampled on the other. It is important therefore that the CPHA and CPOL are configured the same for the master and slave devices.

#### **SS** (Slave Select Input Pin), Pin#13

The Slave Select ( $\overline{SS}$ ) input pin is only used when the ADuC824 is configured in slave mode to enable the SPI peripheral. This line is active low. Data is only received or transmitted in slave mode when the  $\overline{SS}$  pin is low, allowing the ADuC824 to be used in single master, multislave SPI configurations. If CPHA = 1 then the  $\overline{SS}$  input may be permanently pulled low. With CPHA = 0 then the  $\overline{SS}$  input must be driven low before the first bit in a byte wide transmission or reception and return high again after the last bit in that byte wide transmission or reception. In SPI Slave Mode, the logic level on the external  $\overline{SS}$  pin (Pin# 13), can be read via the SPR0 bit in the SPICON SFR.

The following SFR registers are used to control the SPI interface.

| SPICON                                                   | SPI Control Re    | egister |  |  |

|----------------------------------------------------------|-------------------|---------|--|--|

| SFR Address<br>Power-On Default Value<br>Bit Addressable | F8H<br>04H<br>Yes |         |  |  |

|                                                          |                   |         |  |  |

| ISPI | WCOL | SPE | SPIM | CPOL | СРНА | SPR1 | SPR0 |

|------|------|-----|------|------|------|------|------|

|------|------|-----|------|------|------|------|------|

#### Table XIX. SPICON SFR Bit Designations

| Bit | Name  | Description                                                                                                                     |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------|

| 7   | ISPI  | SPI Interrupt Bit                                                                                                               |

|     |       | Set by MicroConverter at the end of each SPI transfer.                                                                          |

|     |       | Cleared directly by user code or indirectly by reading the SPIDAT SFR.                                                          |

| 6   | WCOL  | Write Collision Error Bit                                                                                                       |

|     |       | Set by MicroConverter if SPIDAT is written to while an SPI transfer is in progress.                                             |

|     |       | Cleared by user code.                                                                                                           |

| 5   | SPE   | SPI Interface Enable Bit                                                                                                        |

|     |       | Set by user to enable the SPI interface.                                                                                        |

|     |       | Cleared by user to enable the $I^2C$ interface.                                                                                 |

| 4   | SPIM  | SPI Master/Slave Mode Select Bit                                                                                                |

|     |       | Set by user to enable Master Mode operation (SCLOCK is an output).                                                              |

|     |       | Cleared by user to enable Slave Mode operation (SCLOCK is an input).                                                            |

| 3   | CPOL* | Clock Polarity Select Bit                                                                                                       |

|     |       | Set by user if SCLOCK idles high.                                                                                               |

|     |       | Cleared by user if SCLOCK idles low.                                                                                            |

| 2   | CPHA* | Clock Phase Select Bit                                                                                                          |

|     |       | Set by user if leading SCLOCK edge is to transmit data.                                                                         |

|     |       | Cleared by user if trailing SCLOCK edge is to transmit data.                                                                    |

| 1   | SPR1  | SPI Bit-Rate Select Bits                                                                                                        |

| 0   | SPR0  | These bits select the SCLOCK rate (bit-rate) in Master Mode as follows:                                                         |

|     |       | SPR1 SPR0 Selected Bit Rate SPR1 SPR0 Selected Bit Rate                                                                         |

|     |       | $0 \qquad 0 \qquad f_{\text{CORE}}/2 \qquad 1 \qquad 0 \qquad f_{\text{CORE}}/8$                                                |

|     |       | $1 	 f_{CORE}/4 	 1 	 1 	 f_{CORE}/16$                                                                                          |

|     |       | In SPI Slave Mode, i.e., SPIM = 0, the logic level on the external $\overline{SS}$ pin (Pin# 13), can be read via the SPR0 bit. |

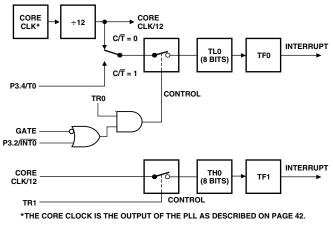

#### **TIMER/COUNTER 0 AND 1 OPERATING MODES**

The following paragraphs describe the operating modes for timer/ counters 0 and 1. Unless otherwise noted, assume that these modes of operation are the same for timer 0 as for timer 1.

#### Mode 0 (13-Bit Timer/Counter)

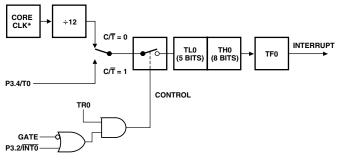

Mode 0 configures an 8-bit timer/counter with a divide-by-32 prescaler. Figure 34 shows mode 0 operation.

#### \*THE CORE CLOCK IS THE OUTPUT OF THE PLL AS DESCRIBED ON PAGE 42.

#### Figure 34. Timer/Counter 0, Mode 0

In this mode, the timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the timer overflow flag TF0. The overflow flag, TF0, can then be used to request an interrupt. The counted input is enabled to the timer when TR0 = 1 and either Gate = 0 or  $\overline{INT0} = 1$ . Setting Gate = 1 allows the timer to be controlled by external input  $\overline{INT0}$ , to facilitate pulsewidth measurements. TR0 is a control bit in the special function register TCON; Gate is in TMOD. The 13-bit register consists of all eight bits of TH0 and the lower five bits of TL0. The upper three bits of TL0 are indeterminate and should be ignored. Setting the run flag (TR0) does not clear the registers.

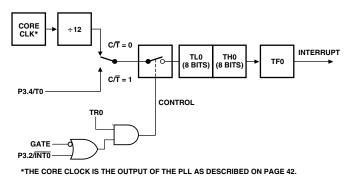

#### Mode 1 (16-Bit Timer/Counter)

Mode 1 is the same as Mode 0, except that the timer register is running with all 16 bits. Mode 1 is shown in Figure 35.

Figure 35. Timer/Counter 0, Mode 1

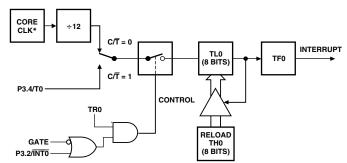

#### Mode 2 (8-Bit Timer/Counter with Auto Reload)

Mode 2 configures the timer register as an 8-bit counter (TL0) with automatic reload, as shown in Figure 36. Overflow from TL0 not only sets TF0, but also reloads TL0 with the contents of TH0, which is preset by software. The reload leaves TH0 unchanged.

\*THE CORE CLOCK IS THE OUTPUT OF THE PLL AS DESCRIBED ON PAGE 42.

Figure 36. Timer/Counter 0, Mode 2

#### Mode 3 (Two 8-Bit Timer/Counters)

Mode 3 has different effects on timer 0 and timer 1. Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0. Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. This configuration is shown in Figure 37. TL0 uses the timer 0 control bits: C/T, Gate, TR0, INT0, and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from timer 1. Thus, TH0 now controls the "timer 1" interrupt. Mode 3 is provided for applications requiring an extra 8-bit timer or counter.

When timer 0 is in Mode 3, timer 1 can be turned on and off by switching it out of, and into, its own Mode 3, or can still be used by the serial interface as a *Baud Rate Generator*. In fact, it can be used, in any application not requiring an interrupt from timer 1 itself.

Figure 37. Timer/Counter 0, Mode 3

| SFR Address C8H            |

|----------------------------|

| 51 K Address Coll          |

| Power-On Default Value 00H |

| Bit Addressable Yes        |

| TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | CNT2 | CAP2 |  |

|-----|------|------|------|-------|-----|------|------|--|

|-----|------|------|------|-------|-----|------|------|--|

#### Table XXV. T2CON SFR Bit Designations

| Bit | Name  | Description                                                                                           |

|-----|-------|-------------------------------------------------------------------------------------------------------|

| 7   | TF2   | Timer 2 Overflow Flag                                                                                 |

|     |       | Set by hardware on a Timer 2 overflow. TF2 will not be set when either RCLK or TCLK = 1.              |

|     |       | Cleared by user software.                                                                             |

| 6   | EXF2  | Timer 2 External Flag                                                                                 |

|     |       | Set by hardware when either a capture or reload is caused by a negative transition on T2EX and        |

|     |       | EXEN2 = 1.                                                                                            |

|     |       | Cleared by user user software.                                                                        |

| 5   | RCLK  | Receive Clock Enable Bit                                                                              |

|     |       | Set by user to enable the serial port to use Timer 2 overflow pulses for its receive clock in serial  |

|     |       | port Modes 1 and 3.                                                                                   |

|     |       | Cleared by user to enable Timer 1 overflow to be used for the receive clock.                          |

| 4   | TCLK  | Transmit Clock Enable Bit                                                                             |

|     |       | Set by user to enable the serial port to use Timer 2 overflow pulses for its transmit clock in serial |

|     |       | port Modes 1 and 3.                                                                                   |

|     |       | Cleared by user to enable Timer 1 overflow to be used for the transmit clock.                         |

| 3   | EXEN2 | Timer 2 External Enable Flag                                                                          |

|     |       | Set by user to enable a capture or reload to occur as a result of a negative transition on T2EX if    |

|     |       | Timer 2 is not being used to clock the serial port.                                                   |

|     |       | Cleared by user for Timer 2 to ignore events at T2EX.                                                 |

| 2   | TR2   | Timer 2 Start/Stop Control Bit                                                                        |

|     |       | Set by user to start Timer 2.                                                                         |

|     |       | Cleared by user to stop Timer 2.                                                                      |

| 1   | CNT2  | Timer 2 Timer or Counter Function Select Bit                                                          |

|     |       | Set by user to select counter function (input from external T2 pin).                                  |

|     |       | Cleared by user to select timer function (input from on-chip core clock).                             |

| 0   | CAP2  | Timer 2 Capture/Reload Select Bit                                                                     |

|     |       | Set by user to enable captures on negative transitions at T2EX if $EXEN2 = 1$ .                       |

|     |       | Cleared by user to enable auto-reloads with Timer 2 overflows or negative transitions at T2EX         |

|     |       | when $EXEN2 = 1$ . When either $RCLK = 1$ or $TCLK = 1$ , this bit is ignored and the timer is        |

|     |       | forced to autoreload on Timer 2 overflow.                                                             |

#### **Timer/Counter 2 Data Registers**

Timer/Counter 2 also has two pairs of 8-bit data registers associated with it. These are used as both timer data registers and timer capture/reload registers.

#### TH2 and TL2

Timer 2, data high byte and low byte. SFR Address = CDhex, CChex respectively.

#### **RCAP2H and RCAP2L**

Timer 2, Capture/Reload byte and low byte. SFR Address = CBhex, CAhex respectively.

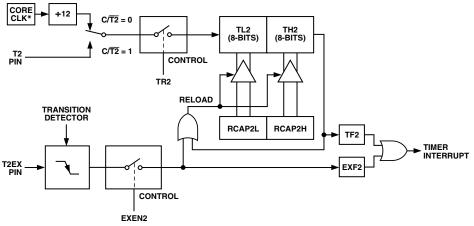

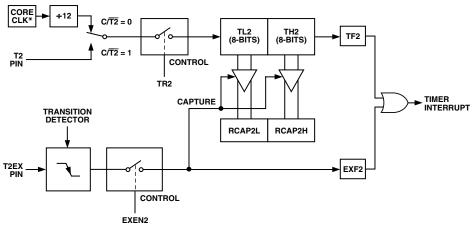

#### Timer/Counter 2 Operating Modes

The following paragraphs describe the operating modes for timer/ counter 2. The operating modes are selected by bits in the T2CON SFR as shown in Table XXVI.

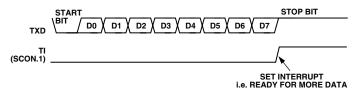

| RCLK (or) TCLK | CAP2 | TR2 | MODE              |