Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f13k22-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

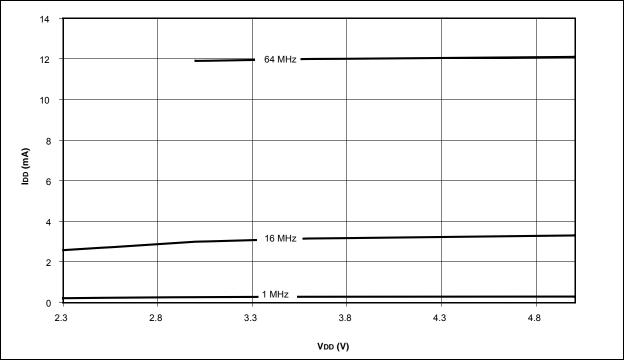

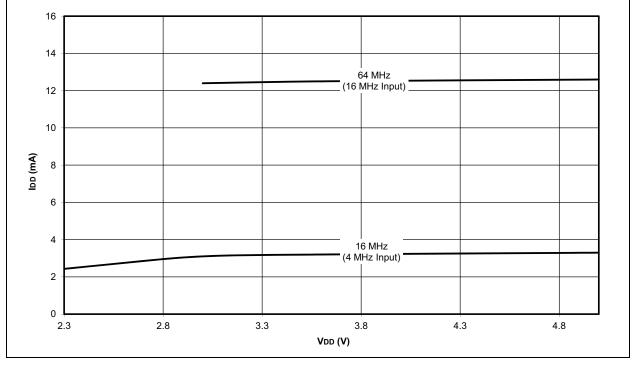

### 2.6 Internal Oscillator

The internal oscillator module contains two independent oscillators which are:

- · LFINTOSC: Low-Frequency Internal Oscillator

- HFINTOSC: High-Frequency Internal Oscillator

When operating with either oscillator, OSC1 will be an I/O and OSC2 will be either an I/O or CLKOUT. The CLKOUT function is selected by the FOSC bits of the CONFIG1H Configuration register. When OSC2 is configured as CLKOUT, the frequency at the pin is the frequency of the Internal Oscillator divided by 4.

### 2.6.1 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a 31 kHz internal clock source. The LFINTOSC oscillator is the clock source for:

- · Power-up Timer

- Watchdog Timer

- · Fail-Safe Clock Monitor

The LFINTOSC is enabled when any of the following conditions are true:

- Power-up Timer is enabled (PWRTEN = 0)

- Watchdog Timer is enabled (WDTEN = 1)

- Watchdog Timer is enabled by software (WDTEN = 0 and SWDTEN = 1)

- Fail-Safe Clock Monitor is enabled (FCMEM = 1)

- SCS1 = 1 and IRCF<2:0> = 000 and INTSRC = 0

- FOSC<3:0> selects the internal oscillator as the primary clock and IRCF<2:0> = 000 and INTSRC = 0

- IESO = 1 (Two-Speed Start-up) and IRCF<2:0> = 000 and INTSRC = 0

### 2.6.2 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision oscillator that is factory-calibrated to operate at 16 MHz. The output of the HFINTOSC connects to a postscaler and a multiplexer (see Figure 2-1). One of eight frequencies can be selected using the IRCF<2:0> bits of the OSCCON register. The following frequencies are available from the HFINTOSC:

- 16 MHZ

- 8 MHZ

- 4 MHZ

- 2 MHZ

- 1 MHZ (Default after Reset)

- 500 kHz

- 250 kHz

- 31 kHz

The HFIOFS bit of the OSCCON register indicates whether the HFINTOSC is stable.

- Note 1: Selecting 31 kHz from the HFINTOSC oscillator requires IRCF<2:0> = 000 and the INTSRC bit of the OSCTUNE register to be set. If the INTSRC bit is clear, the system clock will come from the LFINTOSC.

- 2: Additional adjustments to the frequency of the HFINTOSC can made via the OSCTUNE registers. See Register 2-3 for more details.

The HFINTOSC is enabled if any of the following conditions are true:

- SCS1 = 1 and IRCF<2:0>  $\neq$  000

- SCS1 = 1 and IRCF<2:0> = 000 and INTSRC = 1

- FOSC<3:0> selects the internal oscillator as the primary clock and

- IRCF<2:0> ≠ 000 or

- IRCF<2:0> = 000 and INTSRC = 1

- IESO = 1 (Two-Speed Start-up) and

- IRCF<2:0> ≠ 000 or

- IRCF<2:0> = 000 and INTSRC = 1

- FCMEM = 1 (Fail-Safe Clock Monitoring) and

- IRCF<2:0>  $\neq$  000 or

- IRCF<2:0> = 000 and INTSRC = 1

### 4.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed one byte at a time. A write to program memory is executed on blocks of 16 or 8 bytes at a time depending on the specific device (See Table 4-1). Program memory is erased in blocks of 64 bytes at a time. The difference between the write and erase block sizes requires from 4 to 8 block writes to restore the contents of a single block erase. A Bulk Erase operation can not be issued from user code.

| TABLE 4-1: | WRITE/ERASE BLOCK SIZES |

|------------|-------------------------|

|------------|-------------------------|

| Device         | Write Block<br>Size (bytes) | Erase Block<br>Size (bytes) |  |  |

|----------------|-----------------------------|-----------------------------|--|--|

| PIC18(L)F13K22 | 8                           | 64                          |  |  |

| PIC18(L)F14K22 | 16                          | 64                          |  |  |

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

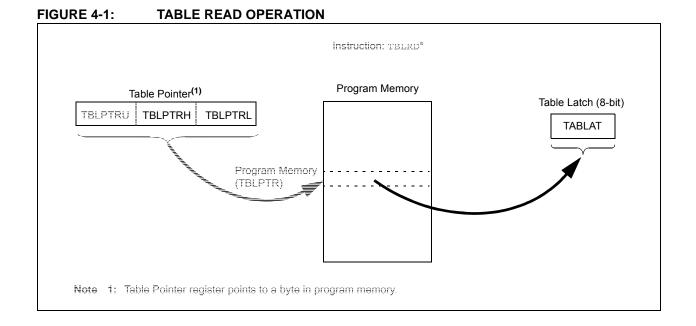

### 4.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16-bit wide, while the data RAM space is 8-bit wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 4-1 shows the operation of a table read.

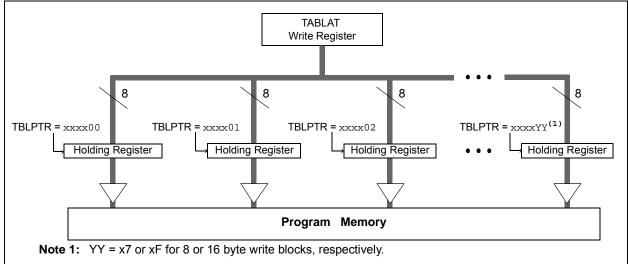

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 4.5** "Writing **to Flash Program Memory**". Figure 4-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word-aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

© 2009-2016 Microchip Technology Inc.

### 4.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the Microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The write initiate sequence for EECON2, shown as steps 4 through 6 in **Section 4.4.1** "**Flash Program Memory Erase Sequence**", is used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing the internal Flash. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

### 4.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory is:

- 1. Load Table Pointer register with address of block being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- · clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the block erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

|          | MOVLW | CODE_ADDR_UPPER | ; load TBLPTR with the base     |

|----------|-------|-----------------|---------------------------------|

|          | MOVWF | TBLPTRU         | ; address of the memory block   |

|          | MOVLW | CODE_ADDR_HIGH  |                                 |

|          | MOVWF | TBLPTRH         |                                 |

|          | MOVLW | CODE_ADDR_LOW   |                                 |

|          | MOVWF | TBLPTRL         |                                 |

| ERASE_BL | OCK   |                 |                                 |

|          | BSF   | EECON1, EEPGD   | ; point to Flash program memory |

|          | BCF   | EECON1, CFGS    | ; access Flash program memory   |

|          | BSF   | EECON1, WREN    | ; enable write to memory        |

|          | BSF   | EECON1, FREE    | ; enable block Erase operation  |

|          | BCF   | INTCON, GIE     | ; disable interrupts            |

| Required | MOVLW | 55h             |                                 |

| Sequence | MOVWF | EECON2          | ; write 55h                     |

|          | MOVLW | 0AAh            |                                 |

|          | MOVWF | EECON2          | ; write OAAh                    |

|          | BSF   | EECON1, WR      | ; start erase (CPU stall)       |

|          | BSF   | INTCON, GIE     | ; re-enable interrupts          |

### EXAMPLE 4-2: ERASING A FLASH PROGRAM MEMORY BLOCK

### 4.5 Writing to Flash Program Memory

The programming block size is 8 or 16 bytes, depending on the device (See Table 4-1). Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. There are only as many holding registers as there are bytes in a write block (See Table 4-1).

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 8, or 16 times, depending on the device, for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. After all the holding registers have been written, the programming operation of that block of memory is started by configuring the EECON1 register for a program memory write and performing the long write sequence. The long write is necessary for programming the internal Flash. Instruction execution is halted during a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all holding registers before executing a long write operation.

### 4.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the block erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write the 8 or 16 byte block into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Repeat steps 6 to 13 for each block until all 64 bytes are written.

- 15. Verify the memory (table read).

This procedure will require about 6 ms to update each write block of memory. An example of the required code is given in Example 4-3.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the bytes in the holding registers.

Example 6-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 6-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES<3:0>).

### EQUATION 6-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L                |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | (ARG1L • ARG2L)                          |

|           |   |                                          |

### EXAMPLE 6-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ;                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| L |        |             |                   |

Example 6-4 shows the sequence to do a 16 x 16 signed multiply. Equation 6-2 shows the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

### EQUATION 6-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L                                        |

|-----------|---|------------------------------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$                         |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$                            |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$                            |

|           |   | $(ARG1L \bullet ARG2L) +$                                        |

|           |   | $(-1 \bullet ARG2H < 7 > \bullet ARG1H: ARG1L \bullet 2^{16}) +$ |

|           |   | $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$    |

|           |   |                                                                  |

### EXAMPLE 6-4:

### 16 x 16 SIGNED MULTIPLY ROUTINE

| MOVF           | ARG1L, W          |                    |

|----------------|-------------------|--------------------|

| MULWF          | ARG2L             | ; ARG1L * ARG2L -> |

|                |                   | ; PRODH:PRODL      |

| MOVFF          | PRODH, RES1       | ;                  |

| MOVFF          | PRODL, RESO       | ;                  |

| ;              |                   |                    |

| MOVF           | ARG1H, W          |                    |

| MULWF          | ARG2H             | ; ARG1H * ARG2H -> |

|                |                   | ; PRODH:PRODL      |

| MOVEE          | PRODH, RES3       |                    |

| MOVFF          |                   |                    |

| ;              | FRODE, RESZ       | 1                  |

| MOVF           | ADC11 W           |                    |

|                | ARG1L, W<br>ARG2H |                    |

| MOTME          | ARGZH             | ; ARG1L * ARG2H -> |

|                |                   | ; PRODH:PRODL      |

|                | PRODL, W          | ;                  |

| ADDWF          | RES1, F           | ; Add cross        |

| MOVF           |                   | ; products         |

|                | RES2, F           | ;                  |

| CLRF           | WREG              | ;                  |

| ADDWFC         | RES3, F           | ;                  |

| ;              |                   |                    |

| MOVF           | ARG1H, W          | ;                  |

| MULWF          | ARG2L             | ; ARG1H * ARG2L -> |

|                |                   | ; PRODH:PRODL      |

| MOVF           | PRODL, W          | ;                  |

| ADDWF          | RES1, F           | ; Add cross        |

| MOVF           | PRODH, W          | ; products         |

|                | RES2, F           | ;                  |

| CLRF           | WREG              | ;                  |

| ADDWFC         | RES3, F           | ;                  |

| ;              |                   |                    |

| BTFSS          | ARG2H, 7          | ; ARG2H:ARG2L neg? |

| BRA            | ,<br>SIGN ARG1    | ; no, check ARG1   |

| MOVF           | ARG1L, W          | ;                  |

| SUBWF          | RES2              | ;                  |

| MOVF           | ARG1H, W          | i                  |

| SUBWFB         |                   |                    |

| ;              | 1.000             |                    |

| ,<br>SIGN ARG1 |                   |                    |

| BTFSS          | ARG1H, 7          | ; ARG1H:ARG1L neg? |

| BIF55<br>BRA   |                   |                    |

|                | CONT_CODE         | ; no, done<br>;    |

| MOVF           | ARG2L, W          |                    |

| SUBWF          | RES2              | ;                  |

| MOVF           | ARG2H, W          | ;                  |

| SUBWFB         | RES3              |                    |

| ;              |                   |                    |

| CONT_CODE      |                   |                    |

| :              |                   |                    |

|                |                   |                    |

### 7.6 **PIE Registers**

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1 and PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 7-6: PIE1: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 1

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|-------|--------|--------|--------|

| —     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |       |       |       |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                 |

|-------|------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter Interrupt Enable bit                   |

|       | 1 = Enables the A/D interrupt                              |

|       | 0 = Disables the A/D interrupt                             |

| bit 5 | RCIE: EUSART Receive Interrupt Enable bit                  |

|       | <ol> <li>Enables the EUSART receive interrupt</li> </ol>   |

|       | 0 = Disables the EUSART receive interrupt                  |

| bit 4 | TXIE: EUSART Transmit Interrupt Enable bit                 |

|       | 1 = Enables the EUSART transmit interrupt                  |

|       | 0 = Disables the EUSART transmit interrupt                 |

| bit 3 | SSPIE: Master Synchronous Serial Port Interrupt Enable bit |

|       | 1 = Enables the MSSP interrupt                             |

|       | 0 = Disables the MSSP interrupt                            |

| bit 2 | CCP1IE: CCP1 Interrupt Enable bit                          |

|       | 1 = Enables the CCP1 interrupt                             |

|       | 0 = Disables the CCP1 interrupt                            |

| bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit             |

|       | 1 = Enables the TMR2 to PR2 match interrupt                |

|       | 0 = Disables the TMR2 to PR2 match interrupt               |

| bit 0 | TMR1IE: TMR1 Overflow Interrupt Enable bit                 |

|       | 1 = Enables the TMR1 overflow interrupt                    |

|       | 0 = Disables the TMR1 overflow interrupt                   |

|       |                                                            |

| Name     | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on page |

|----------|----------|-----------|---------|---------|---------|--------|---------------|--------|----------------------------|

| ANSEL    | ANS7     | ANS6      | ANS5    | ANS4    | ANS3    | ANS2   | ANS1          | ANS0   | 247                        |

| ANSELH   | _        | -         | _       | -       | ANS11   | ANS10  | ANS9          | ANS8   | 247                        |

| CCP1CON  | P1M1     | P1M0      | DC1B1   | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1        | CCP1M0 | 246                        |

| ECCP1AS  | ECCPASE  | ECCPAS2   | ECCPAS1 | ECCPAS0 | PSSAC1  | PSSAC0 | PSSBD1        | PSSBD0 | 246                        |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RABIE   | TMR0IF | <b>INT0IF</b> | RABIF  | 244                        |

| INTCON2  | RABPU    | INTEDG0   | INTEDG1 | INTEDG2 | _       | TMR0IP | _             | RABIP  | 244                        |

| INTCON3  | INT2IP   | INT1IP    | _       | INT2IE  | INT1IE  | _      | INT2IF        | INT1IF | 244                        |

| LATC     | LATC7    | LATC6     | LATC5   | LATC4   | LATC3   | LATC2  | LATC1         | LATC0  | 247                        |

| PORTC    | RC7      | RC6       | RC5     | RC4     | RC3     | RC2    | RC1           | RC0    | 247                        |

| PSTRCON  | _        | -         | _       | STRSYNC | STRD    | STRC   | STRB          | STRA   | 246                        |

| VREFCON1 | D1EN     | D1LPS     | DAC1OE  |         | D1PSS1  | D1PSS0 |               | D1NSS  | 246                        |

| SLRCON   | _        | -         | _       | -       | _       | SLRC   | SLRB          | SLRA   | 247                        |

| SSPCON1  | WCOL     | SSPOV     | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1         | SSPM0  | 245                        |

| TRISC    | TRISC7   | TRISC6    | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1        | TRISC0 | 247                        |

| T1CON    | RD16     | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS        | TMR10N | 245                        |

| T3CON    | RD16     |           | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS        | TMR3ON | 246                        |

| TABLE 8-6: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|------------|--------------------------------------------|

|            |                                            |

## 14.3.4.5 Clock Synchronization and the CKP bit

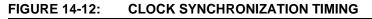

When the CKP bit is cleared, the SCL output is forced to '0'. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 14-12).

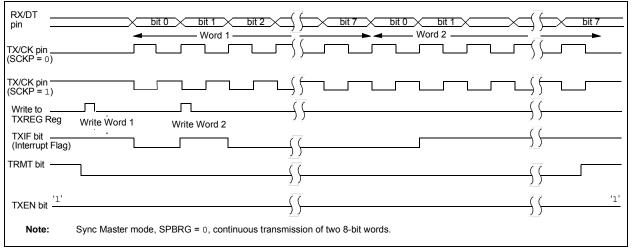

## 15.4.1.5 Synchronous Master Transmission Set-up

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 15.3 "EUSART Baud Rate Generator (BRG)").

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RX/DT and TX/CK I/O pins.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE, GIE and PEIE interrupt enable bits.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

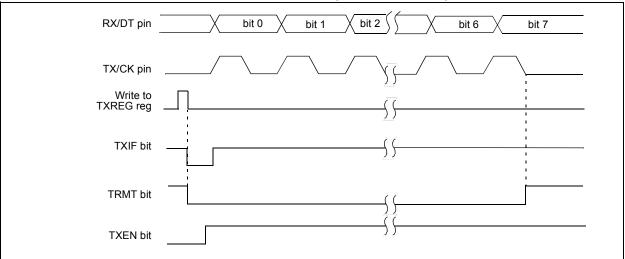

### FIGURE 15-10: SYNCHRONOUS TRANSMISSION

### FIGURE 15-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| Name      | Bit 7       | Bit 6       | Bit 5         | Bit 4         | Bit 3       | Bit 2        | Bit 1      | Bit 0      | Reset<br>Values<br>on page |

|-----------|-------------|-------------|---------------|---------------|-------------|--------------|------------|------------|----------------------------|

| BAUDCON   | ABDOVF      | RCIDL       | DTRXP         | CKTXP         | BRG16       | _            | WUE        | ABDEN      | 247                        |

| INTCON    | GIE/GIEH    | PEIE/GIEL   | TMR0IE        | INT0IE        | RABIE       | TMR0IF       | INT0IF     | RABIF      | 245                        |

| IPR1      | —           | ADIP        | RCIP          | TXIP          | SSPIP       | CCP1IP       | TMR2IP     | TMR1IP     | 248                        |

| PIE1      | —           | ADIE        | RCIE          | TXIE          | SSPIE       | CCP1IE       | TMR2IE     | TMR1IE     | 248                        |

| PIR1      | —           | ADIF        | RCIF          | TXIF          | SSPIF       | CCP1IF       | TMR2IF     | TMR1IF     | 248                        |

| RCREG     | EUSART R    | eceive Regi | ster          |               |             |              |            |            | 247                        |

| RCSTA     | SPEN        | RX9         | SREN          | CREN          | ADDEN       | FERR         | OERR       | RX9D       | 247                        |

| SPBRG     | EUSART B    | aud Rate Ge | enerator Re   | gister, Low E | Byte        |              |            |            | 247                        |

| SPBRGH    | EUSART B    | aud Rate Ge | enerator Re   | gister, High  | Byte        |              |            |            | 247                        |

| TXSTA     | CSRC        | TX9         | TXEN          | SYNC          | SENDB       | BRGH         | TRMT       | TX9D       | 247                        |

| Legend: - | – = unimple | mented, rea | d as '0'. Sha | aded cells a  | re not used | for synchron | ous master | reception. |                            |

### TABLE 15-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

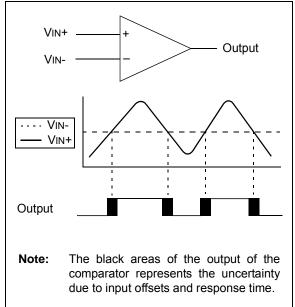

### 17.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-Change

- Wake-up from Sleep

- Programmable Speed/Power optimization

- · PWM shutdown

- · Programmable and fixed voltage reference

### 17.1 Comparator Overview

A single comparator is shown in Figure 17-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

### FIGURE 17-1: SINGLE COMPARATOR

### 17.5 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in **Section 26.0 "Electrical Specifications"**. If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. Each comparator is turned off by clearing the CxON bit of the CMxCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE2 register and the PEIE bit of the INTCON register must be set. The instruction following the SLEEP instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

### 17.6 Effects of a Reset

A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their Off states.

#### **Register Definitions: FVR Control** 20.3

| R/W-0            | R/W-0                                                                                                                                                                                      | R/W-0                                                                                                                                                                    | R/W-1                                                                                                                                                                | U-0                                                                                                                                           | U-0               | U-0              | U-0          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|--------------|

|                  |                                                                                                                                                                                            |                                                                                                                                                                          |                                                                                                                                                                      | 0-0                                                                                                                                           | 0-0               | 0-0              | 0-0          |

| FVR1EN           | FVR1ST                                                                                                                                                                                     | EVR18                                                                                                                                                                    | S<1:0>                                                                                                                                                               | —                                                                                                                                             | —                 | —                | —            |

| bit 7            |                                                                                                                                                                                            |                                                                                                                                                                          |                                                                                                                                                                      |                                                                                                                                               |                   |                  | bit C        |

| Legend:          |                                                                                                                                                                                            |                                                                                                                                                                          |                                                                                                                                                                      |                                                                                                                                               |                   |                  |              |

| R = Readable     | e bit                                                                                                                                                                                      | W = Writable                                                                                                                                                             | bit                                                                                                                                                                  | U = Unimpler                                                                                                                                  | nented bit, read  | as '0'           |              |

| u = Bit is unc   | hanged                                                                                                                                                                                     | x = Bit is unki                                                                                                                                                          | nown                                                                                                                                                                 | -n/n = Value a                                                                                                                                | at POR and BOI    | R/Value at all c | other Resets |

| '1' = Bit is set | t                                                                                                                                                                                          | '0' = Bit is cle                                                                                                                                                         | ared                                                                                                                                                                 |                                                                                                                                               |                   |                  |              |

| bit 7            | 0 = Fixed Vol                                                                                                                                                                              | ed Voltage Ref<br>ltage Referenc<br>ltage Referenc                                                                                                                       | e is disabled                                                                                                                                                        | le bit                                                                                                                                        |                   |                  |              |

| bit 7<br>bit 6   | 0 = Fixed Vol<br>1 = Fixed Vol<br><b>FVR1ST:</b> Fixe                                                                                                                                      | tage Referenc<br>tage Referenc<br>ed Voltage Refe                                                                                                                        | e is disabled<br>e is enabled<br>erence Ready                                                                                                                        | y Flag bit                                                                                                                                    |                   |                  |              |

| bit 6            | 0 = Fixed Vol<br>1 = Fixed Vol<br>FVR1ST: Fixed<br>0 = Fixed Vol<br>1 = Fixed Vol<br>FVR1S<1:0>:<br>00 = Fixed Vol<br>01 = Fixed Vol<br>01 = Fixed Vol                                     | tage Reference<br>tage Reference<br>d Voltage Reference<br>tage Reference<br>tage Reference<br>Fixed Voltage<br>oltage Reference<br>oltage Reference                     | e is disabled<br>e is enabled<br>erence Ready<br>e output is no<br>e output is re<br>Reference S<br>ce Peripheral<br>ce Peripheral                                   | y Flag bit<br>ot ready or not e<br>ady for use<br>Selection bits<br>output is off<br>output is 1x (1.                                         | 024V)             |                  |              |

| bit 6            | 0 = Fixed Vol<br>1 = Fixed Vol<br>FVR1ST: Fixed<br>0 = Fixed Vol<br>1 = Fixed Vol<br>FVR1S<1:0>:<br>00 = Fixed Vol<br>01 = Fixed Vol<br>10 = Fixed Vol<br>10 = Fixed Vol                   | tage Reference<br>tage Reference<br>d Voltage Reference<br>tage Reference<br>tage Reference<br>fixed Voltage<br>oftage Reference<br>oftage Reference<br>oftage Reference | e is disabled<br>e is enabled<br>erence Ready<br>e output is no<br>e output is re<br>Reference S<br>ce Peripheral<br>ce Peripheral<br>ce Peripheral                  | y Flag bit<br>ot ready or not e<br>ady for use<br>Selection bits<br>output is off                                                             | 024V)<br>048V)(1) |                  |              |

|                  | 0 = Fixed Vol<br>1 = Fixed Vol<br>FVR1ST: Fixed<br>0 = Fixed Vol<br>1 = Fixed Vol<br>FVR1S<1:0>:<br>00 = Fixed Vol<br>01 = Fixed Vol<br>10 = Fixed Vol<br>11 = Fixed Vol<br>11 = Fixed Vol | tage Reference<br>tage Reference<br>d Voltage Reference<br>tage Reference<br>tage Reference<br>fixed Voltage<br>oftage Reference<br>oftage Reference<br>oftage Reference | e is disabled<br>e is enabled<br>erence Ready<br>e output is no<br>e output is re<br>Reference S<br>ce Peripheral<br>ce Peripheral<br>ce Peripheral<br>ce Peripheral | y Flag bit<br>ot ready or not e<br>ady for use<br>Gelection bits<br>output is off<br>output is 1x (1.<br>output is 2x (2.<br>output is 4x (4. | 024V)<br>048V)(1) |                  |              |

#### \_\_\_\_\_ ...... . .

Note 1: Fixed Voltage Reference output cannot exceed VDD.

### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name     | Bit 7  | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values on<br>Page |

|----------|--------|--------|------------|-------|-------|-------|-------|-------|----------------------------|

| VREFCON0 | FVR1EN | FVR1ST | FVR1S<1:0> |       | _     |       | —     | —     | 232                        |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by the FVR module.

| POP                                                                   | Рор Тор                                  | Pop Top of Return Stack                                        |                                                    |                                                                |  |  |  |  |

|-----------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| Syntax:                                                               | POP                                      |                                                                |                                                    |                                                                |  |  |  |  |

| Operands:                                                             | None                                     | None                                                           |                                                    |                                                                |  |  |  |  |

| Operation:                                                            | $(TOS) \rightarrow bi$                   | (TOS) $\rightarrow$ bit bucket                                 |                                                    |                                                                |  |  |  |  |

| Status Affected:                                                      | None                                     |                                                                |                                                    |                                                                |  |  |  |  |

| Encoding:                                                             | 0000                                     | 0000                                                           | 0000                                               | 0 0110                                                         |  |  |  |  |

| Description:                                                          | then becom<br>was pushed<br>This instruc | s discard<br>nes the p<br>d onto th<br>ction is pr<br>properly | ed. The<br>revious<br>e return<br>rovided<br>manag | TOS value<br>value that<br>stack.<br>to enable<br>e the return |  |  |  |  |

| Words:                                                                | 1                                        |                                                                |                                                    |                                                                |  |  |  |  |

| Cycles:                                                               | 1                                        |                                                                |                                                    |                                                                |  |  |  |  |

| Q Cycle Activity:                                                     |                                          |                                                                |                                                    |                                                                |  |  |  |  |

| Q1                                                                    | Q2                                       | Q3                                                             | 3                                                  | Q4                                                             |  |  |  |  |

| Decode                                                                | No<br>operation                          | POP 1<br>valu                                                  |                                                    | No<br>operation                                                |  |  |  |  |

| Example:                                                              | POP<br>GOTO                              | NEW                                                            |                                                    |                                                                |  |  |  |  |

| Before Instruct<br>TOS<br>Stack (1 I<br>After Instructio<br>TOS<br>PC | evel down)                               | = (                                                            | )031A2I<br>)14332I<br>)14332I<br>)14332I<br>NEW    | 1                                                              |  |  |  |  |

| PUS         | H                                             | Push Top                                                                                   | p of Return Stack                    |                                          |                               |                                     |  |

|-------------|-----------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------|-------------------------------|-------------------------------------|--|

| Synta       | ax:                                           | PUSH                                                                                       |                                      |                                          |                               |                                     |  |

| Oper        | ands:                                         | None                                                                                       |                                      |                                          |                               |                                     |  |

| Oper        | ation:                                        | $({\rm PC} + 2) \rightarrow$                                                               | TOS                                  |                                          |                               |                                     |  |

| Statu       | s Affected:                                   | None                                                                                       |                                      |                                          |                               |                                     |  |

| Enco        | ding:                                         | 0000                                                                                       | 0000                                 | 000                                      | 00                            | 0101                                |  |

| Desc        | ription:                                      | The PC + 2<br>the return si<br>value is pus<br>This instruc<br>software sta<br>then pushin | ack. T<br>hed d<br>tion al<br>ick by | he prev<br>own on<br>ows imp<br>modifyii | ious<br>the s<br>blem<br>ng T | TOS<br>stack.<br>enting a<br>OS and |  |

| Word        | ls:                                           | 1                                                                                          |                                      |                                          |                               |                                     |  |

| Cycle       | es:                                           | 1                                                                                          |                                      |                                          |                               |                                     |  |

| QC          | ycle Activity:                                |                                                                                            |                                      |                                          |                               |                                     |  |

|             | Q1                                            | Q2                                                                                         | (                                    | 23                                       |                               | Q4                                  |  |

|             | Decode                                        | PUSH<br>PC + 2 onto                                                                        |                                      | NO                                       |                               | No                                  |  |

|             |                                               | return stack                                                                               | ope                                  | ration                                   | oł                            | peration                            |  |

| <u>Exan</u> | nple:                                         |                                                                                            |                                      |                                          | o                             |                                     |  |

|             | n <u>ple</u> :<br>Before Instruc<br>TOS<br>PC | return stack                                                                               | =                                    | 345Ah<br>0124h                           | oţ                            |                                     |  |

|                                                                                                                                                                                                                                                                                                             | RETURN Return from Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RETURN {s}                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| <b>S</b> ∈ [0,1]                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Operation: $(TOS) \rightarrow PC,$<br>if $s = 1$<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow Status,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| None                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 0000                                                                                                                                                                                                                                                                                                        | 0000 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 001s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |