# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

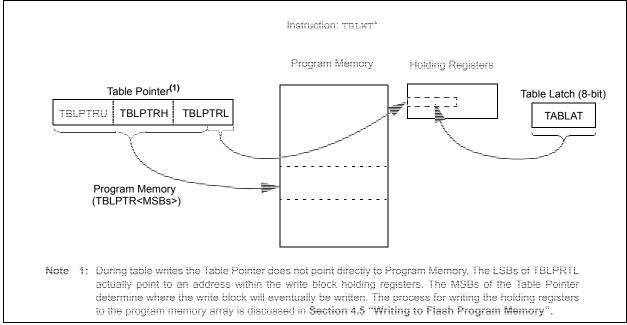

| Speed                      | 64MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

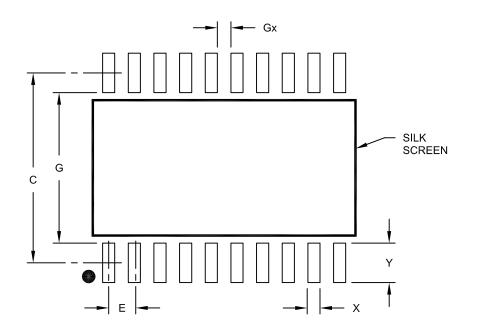

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f13k22-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 OSCILLATOR MODULE

### 2.1 Overview

The oscillator module has a variety of clock sources and features that allow it to be used in a wide range of applications, maximizing performance and minimizing power consumption. Figure 2-1 illustrates a block diagram of the oscillator module.

Key features of the oscillator module include:

- System Clocks

- System Clock Selection

- Primary External Oscillator

- Secondary External Oscillator

- Internal Oscillator

- Oscillator Start-up Timer

- System Clock Selection

- · Clock Switching

- 4x Phase Lock Loop Frequency Multiplier

- · CPU Clock Divider

- Two-Speed Start-up Mode

- · Fail-Safe Clock Monitoring

## 2.2 System Clocks

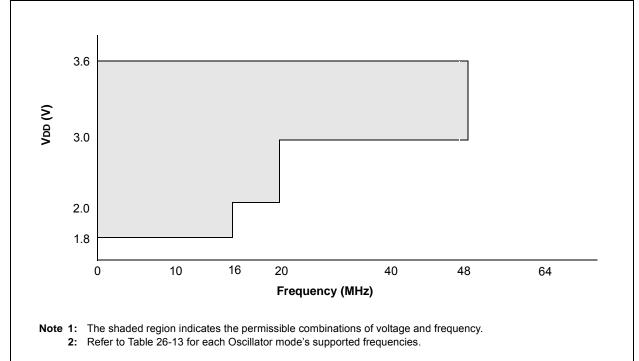

The PIC18(L)F1XK22 can be operated in 13 different oscillator modes. The user can program these using the available Configuration bits. In addition, clock support functions such as Fail-Safe and two Start-up can also be configured.

The available Primary oscillator options include:

- External Clock, low power (ECL)

- · External Clock, medium power (ECM)

- External Clock, high power (ECH)

- External Clock, low power, CLKOUT function on RA4/OSC2 (ECCLKOUTL)

- External Clock, medium power, CLKOUT function on RA4/OSC2 (ECCLKOUTM)

- External Clock, high power, CLKOUT function on RA4/OSC2 (ECCLKOUTH)

- External Crystal (XT)

- High-speed Crystal (HS)

- Low-power crystal (LP)

- External Resistor/Capacitor (EXTRC)

- External RC, CLKOUT function on RA4/OSC2

- 31.25 kHz 16 MHz internal oscillator (INTOSC)

- 31.25 kHz 16 MHz internal oscillator, CLKOUT function on RA4/OSC2

Additionally, the 4x PLL may be enabled in hardware or software (under certain conditions) for increased oscillator speed.

### 2.3 System Clock Selection

The SCS bits of the OSCCON register select between the following clock sources:

- Primary External Oscillator

- · Secondary External Oscillator

- · Internal Oscillator

- **Note:** The frequency of the system clock will be referred to as FOSC throughout this document.

| TABLE 2-1: SYSTEM CLOCK SELECTIC | ON |

|----------------------------------|----|

|----------------------------------|----|

| Configuration               | Selection                          |

|-----------------------------|------------------------------------|

| SCS <1:0>                   | System Clock                       |

| 1x                          | Internal Oscillator                |

| 01                          | Secondary External Oscillator      |

| 00<br>(Default after Reset) | Oscillator defined by<br>FOSC<3:0> |

The default state of the SCS bits sets the system clock to be the oscillator defined by the FOSC bits of the CONFIG1H Configuration register. The system clock will always be defined by the FOSC bits until the SCS bits are modified in software.

When the Internal Oscillator is selected as the system clock, the IRCF bits of the OSCCON register and the INTSRC bit of the OSCTUNE register will select either the LFINTOSC or the HFINTOSC. The LFINTOSC is selected when the IRCF<2:0> = 000 and the INTSRC bit is clear. All other combinations of the IRCF bits and the INTSRC bit will select the HFINTOSC as the system clock.

# 2.4 Primary External Oscillator

The Primary External Oscillator's mode of operation is selected by setting the FOSC<3:0> bits of the CONFIG1H Configuration register. The oscillator can be set to the following modes:

- LP: Low-Power Crystal

- XT: Crystal/Ceramic Resonator

- · HS: High-Speed Crystal Resonator

- RC: External RC Oscillator

- EC: External Clock

Additionally, the Primary External Oscillator may be shut down under firmware control to save power.

| Name     | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>page |

|----------|----------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| CONFIG1H | IESO     | FCMEN     | PCLKEN  | PLL_EN  | FOSC3   | FOSC2  | FOSC1  | FOSC0  | 251                        |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RABIE   | TMR0IF | INT0IF | RABIF  | 245                        |

| OSCCON   | IDLEN    | IRCF2     | IRCF1   | IRCF0   | OSTS    | HFIOFS | SCS1   | SCS0   | 246                        |

| OSCCON2  | _        | _         | _       | _       | —       | PRI_SD | HFIOFL | LFIOFS | 246                        |

| OSCTUNE  | INTSRC   | PLLEN     | TUN5    | TUN4    | TUN3    | TUN2   | TUN1   | TUN0   | 248                        |

| IPR2     | OSCFIP   | C1IP      | C2IP    | EEIP    | BCLIP   | -      | TMR3IP | _      | 248                        |

| PIE2     | OSCFIE   | C1IE      | C2IE    | EEIE    | BCLIE   | —      | TMR3IE | —      | 248                        |

| PIR2     | OSCFIF   | C1IF      | C2IF    | EEIF    | BCLIF   | _      | TMR3IF | —      | 248                        |

| T1CON    | RD16     | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 246                        |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators. Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

#### 3.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Figure 3-1) contains the Stack Pointer value, the STKFUL (Stack Full) bit and the STKUNF (Stack Underflow) bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKOVF bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 23.1 "Configuration Bits"** for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKOVF bit and reset the device. The STKOVF bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKOVF bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an |  |

|-------|-------------------------------------------|--|

|       | underflow has the effect of vectoring the |  |

|       | program to the Reset vector, where the    |  |

|       | stack conditions can be verified and      |  |

|       | appropriate actions can be taken. This is |  |

|       | not the same as a Reset, as the contents  |  |

|       | of the SFRs are not affected.             |  |

#### 3.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

| R/C-0                  | R/C-0                 | U-0              | R/W-0                       | R/W-0            | R/W-0             | R/W-0          | R/W-0                  |  |

|------------------------|-----------------------|------------------|-----------------------------|------------------|-------------------|----------------|------------------------|--|

| STKOVF <sup>(1)</sup>  | STKUNF <sup>(1)</sup> | —                | SP4                         | SP3              | SP2               | SP1            | SP0                    |  |

| bit 7                  |                       |                  |                             |                  |                   |                | bit 0                  |  |

|                        |                       |                  |                             |                  |                   |                |                        |  |

| Legend:                |                       |                  |                             |                  |                   |                |                        |  |

| R = Readable bit W = W |                       | W = Writable     | <pre>/ = Writable bit</pre> |                  | U = Unimplemented |                | C = Clearable only bit |  |

| -n = Value at POR      |                       | '1' = Bit is set |                             | '0' = Bit is cle | ared              | x = Bit is unk | nown                   |  |

#### REGISTER 3-1: STKPTR: STACK POINTER REGISTER

| bit 7   | STKOVF: Stack Overflow Flag bit <sup>(1)</sup>                                                            |

|---------|-----------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Stack became full or overflowed</li><li>0 = Stack has not become full or overflowed</li></ul> |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup>                                                           |

|         | <ol> <li>1 = Stack underflow occurred</li> <li>0 = Stack underflow did not occur</li> </ol>               |

| bit 5   | Unimplemented: Read as '0'                                                                                |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits                                                                      |

|         |                                                                                                           |

Note 1: Bit 7 and bit 6 are cleared by user software or by a POR.

# 4.2 Control Registers

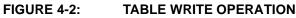

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- · EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

### 4.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 4-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When EEPGD is clear, any subsequent operations will operate on the data EEPROM memory. When EEPGD is set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When CFGS is set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 23.0 "Special Features of the CPU"**). When CFGS is clear, memory selection access is determined by EEPGD. The FREE bit allows the program memory erase operation. When FREE is set, an erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. The WREN bit is clear on power-up.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |

The WR control bit initiates write operations. The WR bit cannot be cleared, only set, by firmware. Then WR bit is cleared by hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit of the PIR2 register is set when the write is complete. The EEIF flag stays set until cleared by firmware.

# 6.0 8 x 8 HARDWARE MULTIPLIER

## 6.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 6-1.

#### 6.2 Operation

Example 6-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 6-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 6-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MULWF ARG2 ; ARG1 * ARG2 -><br>; PRODH:PRODL |

|----------------------------------------------|

|                                              |

| / PRODE /                                    |

## EXAMPLE 6-2: 8 x 8 SIGNED MULTIPLY

| MOVF  | ARG1, W  |   |                |

|-------|----------|---|----------------|

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                  |                           | Program           | Cycles | Time     |          |         |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

| 8 x 8 unsigned   | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |  |

|                  | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |

| 0 0 · · ·        | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |  |

| 10 × 10 uppigned | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |

|                  | Hardware multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs   |  |

#### TABLE 6-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

#### 7.4 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0         | R/W-x |

|----------|-----------|--------|--------|-------|--------|---------------|-------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RABIE | TMR0IF | <b>INT0IF</b> | RABIF |

| bit 7    |           |        |        |       |        |               | bit 0 |

| <b>-</b>          |                                                                                                                                                                                                                                                                                                 |                                    |                                        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------|

| Legend:           |                                                                                                                                                                                                                                                                                                 |                                    |                                        |

| R = Readable bit  | W = Writable bit                                                                                                                                                                                                                                                                                | U = Unimplemented bit, read as '0' |                                        |

| -n = Value at POR | '1' = Bit is set                                                                                                                                                                                                                                                                                | '0' = Bit is cleared               | x = Bit is unknown                     |

| bit 7             | <b>GIE/GIEH:</b> Global Interrupt Enable bit<br><u>When IPEN = 0</u> :<br>1 = Enables all inmasked interrupts<br>0 = Disables all interrupts including peripherals<br><u>When IPEN = 1</u> :<br>1 = Enables all high priority interrupts<br>0 = Disables all interrupts including low priority  |                                    |                                        |

| bit 6             | PEIE/GIEL: Peripheral Interrupt Enable bit         When IPEN = 0:         1 = Enables all unmasked peripheral interrupts         0 = Disables all peripheral interrupts         When IPEN = 1:         1 = Enables all low priority interrupts         0 = Disables all low priority interrupts |                                    |                                        |

| bit 5             | <b>TMROIE:</b> TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 overflow interrupt<br>0 = Disables the TMR0 overflow interrupt                                                                                                                                                        |                                    |                                        |

| bit 4             | INTOIE: INTO External Interrupt Enable bit<br>1 = Enables the INTO external interrupt<br>0 = Disables the INTO external interrupt                                                                                                                                                               |                                    |                                        |

| bit 3             | <b>RABIE:</b> RA and RB Port Change Interrupt Enable bit <sup>(2</sup><br>1 = Enables the RA and RB port change interrupt<br>0 = Disables the RA and RB port change interrupt                                                                                                                   |                                    |                                        |

| bit 2             | <b>TMR0IF:</b> TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared by<br>0 = TMR0 register did not overflow                                                                                                                                                   | software)                          |                                        |

| bit 1             | INT0IF: INT0 External Interrupt Flag bit<br>1 = The INT0 external interrupt occurred (must be clear<br>0 = The INT0 external interrupt did not occur                                                                                                                                            | red by software)                   |                                        |

| bit 0             | <b>RABIF:</b> RA and RB Port Change Interrupt Flag bit <sup>(1)</sup><br>1 = At least one of the RA <5:0> or RB<7:4> pins char<br>0 = None of the RA<5:0> or RB<7:4> pins have chang                                                                                                            |                                    | re)                                    |

|                   | smatch condition will continue to set the RABIF bit. Read eared.                                                                                                                                                                                                                                | ng PORTA and PORTB will end the m  | ismatch condition and allow the bit to |

2: RA and RB port change interrupts also require the individual pin IOCA and IOCB enable.

| U-0                                               | U-0             | R/W-x                 | R/W-x | R-x                                     | R/W-x | R/W-x | R/W-x |

|---------------------------------------------------|-----------------|-----------------------|-------|-----------------------------------------|-------|-------|-------|

| _                                                 | —               | RA5                   | RA4   | RA3                                     | RA2   | RA1   | RA0   |

| bit 7                                             |                 |                       |       |                                         |       |       | bit ( |

|                                                   |                 |                       |       |                                         |       |       |       |

| Legend:                                           |                 |                       |       |                                         |       |       |       |

| R = Readal                                        | ole bit         | W = Writable          | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value a                                      | at POR          | '1' = Bit is set      |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

|                                                   |                 |                       |       |                                         |       |       |       |

| bit 7-6                                           | Unimplemen      | ted: Read as '0       | כי    |                                         |       |       |       |

| bit 5-0 RA<5:0>: PORTA I/O Pin bit <sup>(1)</sup> |                 | (1)                   |       |                                         |       |       |       |

|                                                   | 1 = Port pin is | 1 = Port pin is > Vін |       |                                         |       |       |       |

|                                                   | 0 = Port pin is | s < Vil               |       |                                         |       |       |       |

#### **REGISTER 8-1: PORTA: PORTA REGISTER**

**Note 1:** The RA3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0). Otherwise, RA3 reads as '0'. This bit is read-only.

#### REGISTER 8-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | U-1 | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|-----|--------|--------|--------|

| —     | —   | TRISA5 | TRISA4 |     | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |        |        |     |        |        | bit 0  |

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit <sup>(1)</sup><br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                                        |

|         | •                                                                                                                                                                 |

**Note 1:** TRISA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |

|---------|----------|-----------|---------|---------|-------|--------|--------|-------|----------------------------|

| ANSELH  | —        | —         | —       |         | ANS11 | ANS10  | ANS9   | ANS8  | 247                        |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RABIE | TMR0IF | INT0IF | RABIF | 244                        |

| INTCON2 | RABPU    | INTEDG0   | INTEDG1 | INTEDG2 | _     | TMR0IP | —      | RABIP | 244                        |

| IOCB    | IOCB7    | IOCB6     | IOCB5   | IOCB4   |       |        |        |       | 247                        |

| LATB    | LATB7    | LATB6     | LATB5   | LATB4   | _     | _      | —      | _     | 247                        |

| PORTB   | RB7      | RB6       | RB5     | RB4     | _     | —      | _      | _     | 247                        |

| RCSTA   | SPEN     | RX9       | SREN    | CREN    | ADDEN | FERR   | OERR   | RX9D  | 246                        |

| SLRCON  | —        | —         | —       | _       | _     | SLRC   | SLRB   | SLRA  | 247                        |

| SSPCON1 | WCOL     | SSPOV     | SSPEN   | CKP     | SSPM3 | SSPM2  | SSPM1  | SSPM0 | 245                        |

| TRISB   | TRISB7   | TRISB6    | TRISB5  | TRISB4  |       | _      |        |       | 247                        |

| TXSTA   | CSRC     | TX9       | TXEN    | SYNC    | SENDB | BRGH   | TRMT   | TX9D  | 246                        |

| WPUB    | WPUB7    | WPUB6     | WPUB5   | WPUB4   |       | _      | _      | _     | 247                        |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

| P1M<  | 1:0>                      | Signal                    | ⁰ ;◄         | Pulse<br>Width | ►<br>                | PR2+1                                 |

|-------|---------------------------|---------------------------|--------------|----------------|----------------------|---------------------------------------|

| 00    | (Single Output)           | P1A Modulated             |              |                |                      |                                       |

|       |                           | P1A Modulated             | <br>         | ►<br>av(1)     | Delay <sup>(1)</sup> |                                       |

| 10    | (Half-Bridge)             | P1B Modulated             |              | ay             |                      |                                       |

|       |                           | P1A Active                |              |                | · · ·                | · · · · · · · · · · · · · · · · · · · |

|       | (Full-Bridge,<br>Forward) | P1B Inactive              | - :          |                | I                    | <u> </u>                              |

|       |                           | P1C Inactive              | _ <u> </u>   |                |                      | i                                     |

|       |                           | P1D Modulated             | =<br>        |                |                      |                                       |

|       |                           | P1A Inactive              | _ :          |                |                      |                                       |

| 11    | (Full-Bridge,<br>Reverse) | P1B Modulated             | = — <u>j</u> |                |                      |                                       |

|       | 1000130)                  | P1C Active                | _ <u>;</u>   |                |                      |                                       |

|       |                           | P1D Inactive              | _ <u>_ </u>  |                |                      |                                       |

| Relat | tionships:                | c * (PR2 + 1) * (TMR2 Pre |              |                |                      | •                                     |

#### FIGURE 13-5: **EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)**

Delay = 4 \* Tosc \* (PWM1CON<6:0>)

Note 1: Dead-band delay is programmed using the PWM1CON register (Section 13.4.6 "Programmable Dead-Band Delay Mode").

# 14.2.8 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in Full Power mode; in the case of the Sleep mode, all clocks are halted.

In all Idle modes, a clock is provided to the peripherals. That clock could be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See **Section 18.0 "Power-Managed Modes"** for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

When MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller:

- From Sleep, in Slave mode

- From Idle, in Slave or Master mode

If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any Power-Managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

#### 14.2.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 14.2.10 BUS MODE COMPATIBILITY

Table 14-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| TABLE 14-1: | SPI BUS MODES |

|-------------|---------------|

|-------------|---------------|

| Standard SPI Mode | Control Bits State |     |  |  |

|-------------------|--------------------|-----|--|--|

| Terminology       | СКР                | CKE |  |  |

| 0, 0              | 0                  | 1   |  |  |

| 0, 1              | 0                  | 0   |  |  |

| 1, 0              | 1                  | 1   |  |  |

| 1, 1              | 1                  | 0   |  |  |

There is also an SMP bit which controls when the data is sampled.

| TABLE 14-2. REGISTERS ASSOCIATED WITT SPLOPERATION |           |               |             |        |        |        |        |        |                            |  |  |

|----------------------------------------------------|-----------|---------------|-------------|--------|--------|--------|--------|--------|----------------------------|--|--|

| Name                                               | Bit 7     | Bit 6         | Bit 5       | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |  |  |

| INTCON                                             | GIE/GIEH  | PEIE/GIEL     | TMR0IE      | INT0IE | RABIE  | TMR0IF | INT0IF | RABIF  | 245                        |  |  |

| IPR1                                               | —         | ADIP          | RCIP        | TXIP   | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 248                        |  |  |

| PIE1                                               | —         | ADIE          | RCIE        | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 248                        |  |  |

| PIR1                                               | —         | ADIF          | RCIF        | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 248                        |  |  |

| TRISB                                              | TRISB7    | TRISB6        | TRISB5      | TRISB4 | —      | _      | _      | _      | 248                        |  |  |

| TRISC                                              | TRISC7    | TRISC6        | TRISC5      | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 248                        |  |  |

| SSPBUF                                             | SSP Recei | ve Buffer/Tra | ansmit Regi | ster   |        |        |        |        | 246                        |  |  |

| SSPCON1                                            | WCOL      | SSPOV         | SSPEN       | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 246                        |  |  |

| SSPSTAT                                            | SMP       | CKE           | D/A         | Р      | S      | R/W    | UA     | BF     | 246                        |  |  |

TABLE 14-2:

REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: Shaded cells are not used by the MSSP in SPI mode.

| R/W-0        | R/W-0                                                   | R/W-0                                               | R/W-0                | R/W-0                    | R/W-0                   | R/W-0               | R/W-0              |

|--------------|---------------------------------------------------------|-----------------------------------------------------|----------------------|--------------------------|-------------------------|---------------------|--------------------|

| GCEN         | ACKSTAT                                                 | ACKDT <sup>(2)</sup>                                | ACKEN <sup>(1)</sup> | RCEN <sup>(1)</sup>      | PEN <sup>(1)</sup>      | RSEN <sup>(1)</sup> | SEN <sup>(1)</sup> |

| bit 7        |                                                         |                                                     |                      |                          |                         |                     | bit                |

|              |                                                         |                                                     |                      |                          |                         |                     |                    |

| Legend:      |                                                         |                                                     |                      |                          |                         |                     |                    |

| R = Readab   |                                                         | W = Writable                                        |                      | -                        | mented bit, rea         |                     |                    |

| -n = Value a | t POR                                                   | '1' = Bit is se                                     | t                    | '0' = Bit is cle         | ared                    | x = Bit is unkr     | nown               |

| bit 7        | GCEN: Gene                                              | eral Call Enable                                    | e bit (Slave mo      | de only)                 |                         |                     |                    |

|              | 1 = Generate                                            |                                                     | n a general call     |                          | or 00h is rece          | ived in the SSP     | SR                 |

| bit 6        | ACKSTAT: A                                              | cknowledge St                                       | atus bit (Maste      | r Transmit mo            | de only)                |                     |                    |

|              |                                                         |                                                     | eceived from sl      |                          |                         |                     |                    |

|              |                                                         | •                                                   | ved from slave       |                          | (0)                     |                     |                    |

| bit 5        |                                                         | -                                                   | a bit (Master Re     | eceive mode or           | nly) <sup>(2)</sup>     |                     |                    |

|              | 1 = Not Ackn<br>0 = Acknowle                            | 0                                                   |                      |                          |                         |                     |                    |

| bit 4        | ACKEN: Ack                                              | knowledge Seq                                       | uence Enable         | bit (Master Red          | ceive mode on           | ly) <sup>(1)</sup>  |                    |

|              | Automat                                                 | Acknowledge so<br>ically cleared b<br>edge sequence | y hardware.          | A and SCL pir            | ns and transmi          | t ACKDT data b      | it.                |

| bit 3        |                                                         | • ·                                                 | (Master mode of      | only) <sup>(1)</sup>     |                         |                     |                    |

|              |                                                         | Receive mode                                        | •                    | 5,                       |                         |                     |                    |

|              | 0 = Receive                                             | Idle                                                |                      |                          |                         |                     |                    |

| bit 2        | PEN: Stop C                                             | ondition Enable                                     | e bit (Master m      | ode only) <sup>(1)</sup> |                         |                     |                    |

|              | 1 = Initiate St<br>0 = Stop cone                        |                                                     | n SDA and SC         | L pins. Automa           | atically cleared        | by hardware.        |                    |

| bit 1        | RSEN: Repe                                              | ated Start Con                                      | dition Enable b      | it (Master mod           | le only) <sup>(1)</sup> |                     |                    |

|              |                                                         | Repeated Start                                      |                      | DA and SCL pi            | ins. Automatic          | ally cleared by h   | ardware.           |

| bit 0        | SEN: Start C                                            | ondition Enabl                                      | e/Stretch Enab       | le bit <sup>(1)</sup>    |                         |                     |                    |

|              | <u>In Master mo</u><br>1 = Initiate St<br>0 = Start con | tart condition o                                    | n SDA and SC         | L pins. Automa           | atically cleared        | by hardware.        |                    |

|              |                                                         |                                                     |                      | ave transmit an          | nd slave receiv         | e (stretch enabl    | ed)                |

| Note 1: F    | or bits ACKEN, I                                        |                                                     |                      |                          |                         | lle mode, these     |                    |

# REGISTER 14-5: SSPCON2: MSSP CONTROL REGISTER (I<sup>2</sup>C MODE)

be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).2: Value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

|        |                |            |                             |                  | <b>616 =</b> 0 |                             |                   |            |                             |                  |            |                             |

|--------|----------------|------------|-----------------------------|------------------|----------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fosc = 4.000 MHz |                |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _          | _                           | _                | _              | _                           | _                 |            | _                           | 300              | 0.16       | 207                         |

| 1200   | —              | _          | —                           | 1202             | 0.16           | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404           | 0.16       | 207                         | 2404             | 0.16           | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615           | 0.16       | 51                          | 9615             | 0.16           | 25                          | 9600              | 0.00       | 23                          | —                |            | _                           |

| 10417  | 10417          | 0.00       | 47                          | 10417            | 0.00           | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231          | 0.16       | 25                          | 19.23k           | 0.16           | 12                          | 19.2k             | 0.00       | 11                          | —                | _          | _                           |

| 57.6k  | 55556          | -3.55      | 8                           | —                | _              | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | _              | _          | _                           | —                |                | —                           | 115.2k            | 0.00       | 1                           | —                | _          | —                           |

# TABLE 15-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                |            |                               |                   | SYNC = 0, BRGH = 0, BRG16 = 1 |                               |                   |            |                               |                    |            |                               |

|--------|----------------|------------|-------------------------------|-------------------|-------------------------------|-------------------------------|-------------------|------------|-------------------------------|--------------------|------------|-------------------------------|

| BAUD   | Fosc           | = 48.00    | 0 MHz                         | Fosc = 18.432 MHz |                               |                               | Fosc = 12.000 MHz |            |                               | Fosc = 11.0592 MHz |            |                               |

| RATE   | Actual<br>Rate | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate    | %<br>Error                    | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) |

| 300    | 300.0          | 0.00       | 9999                          | 300.0             | 0.00                          | 3839                          | 300               | 0.00       | 2499                          | 300.0              | 0.00       | 2303                          |

| 1200   | 1200.1         | 0.00       | 2499                          | 1200              | 0.00                          | 959                           | 1200              | 0.00       | 624                           | 1200               | 0.00       | 575                           |

| 2400   | 2400           | 0.00       | 1249                          | 2400              | 0.00                          | 479                           | 2404              | 0.16       | 311                           | 2400               | 0.00       | 287                           |

| 9600   | 9615           | 0.16       | 311                           | 9600              | 0.00                          | 119                           | 9615              | 0.16       | 77                            | 9600               | 0.00       | 71                            |

| 10417  | 10417          | 0.00       | 287                           | 10378             | -0.37                         | 110                           | 10417             | 0.00       | 71                            | 10473              | 0.53       | 65                            |

| 19.2k  | 19.23k         | 0.16       | 155                           | 19.20k            | 0.00                          | 59                            | 19.23k            | 0.16       | 38                            | 19.20k             | 0.00       | 35                            |

| 57.6k  | 57.69k         | 0.16       | 51                            | 57.60k            | 0.00                          | 19                            | 57.69k            | 0.16       | 12                            | 57.60k             | 0.00       | 11                            |

| 115.2k | 115.38k        | 0.16       | 25                            | 115.2k            | 0.00                          | 9                             |                   | _          | —                             | 115.2k             | 0.00       | 5                             |

|        |                |            |                               |                  | SYNC = 0, BRGH = 0, BRG16 = 1 |                               |                |            |                               |                |            |                               |  |

|--------|----------------|------------|-------------------------------|------------------|-------------------------------|-------------------------------|----------------|------------|-------------------------------|----------------|------------|-------------------------------|--|

| BAUD   | Fos            | c = 8.000  | ) MHz                         | Fosc = 4.000 MHz |                               | Fosc = 3.6864 MHz             |                |            | Fosc = 1.000 MHz              |                |            |                               |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate   | %<br>Error                    | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) |  |

| 300    | 299.9          | -0.02      | 1666                          | 300.1            | 0.04                          | 832                           | 300.0          | 0.00       | 767                           | 300.5          | 0.16       | 207                           |  |

| 1200   | 1199           | -0.08      | 416                           | 1202             | 0.16                          | 207                           | 1200           | 0.00       | 191                           | 1202           | 0.16       | 51                            |  |

| 2400   | 2404           | 0.16       | 207                           | 2404             | 0.16                          | 103                           | 2400           | 0.00       | 95                            | 2404           | 0.16       | 25                            |  |

| 9600   | 9615           | 0.16       | 51                            | 9615             | 0.16                          | 25                            | 9600           | 0.00       | 23                            | _              | _          | _                             |  |

| 10417  | 10417          | 0.00       | 47                            | 10417            | 0.00                          | 23                            | 10473          | 0.53       | 21                            | 10417          | 0.00       | 5                             |  |

| 19.2k  | 19.23k         | 0.16       | 25                            | 19.23k           | 0.16                          | 12                            | 19.20k         | 0.00       | 11                            | _              | _          | _                             |  |

| 57.6k  | 55556          | -3.55      | 8                             | —                | _                             | _                             | 57.60k         | 0.00       | 3                             | —              | _          | _                             |  |

| 115.2k | —              | _          | _                             | —                | _                             | _                             | 115.2k         | 0.00       | 1                             | —              | _          | _                             |  |

| Name    | Bit 7    | Bit 6                    | Bit 5       | Bit 4        | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------|--------------------------|-------------|--------------|--------|--------|--------|--------|----------------------------|

| BAUDCON | ABDOVF   | RCIDL                    | DTRXP       | CKTXP        | BRG16  | —      | WUE    | ABDEN  | 247                        |

| INTCON  | GIE/GIEH | PEIE/GIEL                | TMR0IE      | INT0IE       | RABIE  | TMR0IF | INT0IF | RABIF  | 245                        |

| IPR1    |          | ADIP                     | RCIP        | TXIP         | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 248                        |

| PIE1    | —        | ADIE                     | RCIE        | TXIE         | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 248                        |

| PIR1    |          | ADIF                     | RCIF        | TXIF         | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 248                        |

| RCSTA   | SPEN     | RX9                      | SREN        | CREN         | ADDEN  | FERR   | OERR   | RX9D   | 247                        |

| SPBRG   | EUSART B | Baud Rate G              | enerator Re | gister, Low  | Byte   |        |        |        | 247                        |

| SPBRGH  | EUSART B | Baud Rate G              | enerator Re | gister, High | Byte   |        |        |        | 247                        |

| TRISC   | TRISC7   | TRISC6                   | TRISC5      | TRISC4       | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 248                        |

| TXREG   | EUSART T | EUSART Transmit Register |             |              |        |        |        |        | 247                        |

| TXSTA   | CSRC     | TX9                      | TXEN        | SYNC         | SENDB  | BRGH   | TRMT   | TX9D   | 247                        |

TABLE 15-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

#### 15.4.1.6 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver must be disabled by setting the corresponding TRIS bits when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

## 15.4.1.7 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver must be disabled by setting the associated TRIS bit when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 15.4.1.8 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# 17.5 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in **Section 26.0 "Electrical Specifications"**. If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. Each comparator is turned off by clearing the CxON bit of the CMxCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE2 register and the PEIE bit of the INTCON register must be set. The instruction following the SLEEP instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

# 17.6 Effects of a Reset

A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their Off states.

|              |                                |               |                | REGISTER 2      |                  |          |       |

|--------------|--------------------------------|---------------|----------------|-----------------|------------------|----------|-------|

| U-0          | U-0                            | U-0           | R/P-1          | R/P-1           | R/P-1            | R/P-1    | R/P-1 |

| —            | —                              | _             | WDTPS3         | WDTPS2          | WDTPS1           | WDTPS0   | WDTEN |

| bit 7        |                                |               |                |                 |                  |          | bit   |

| Legend:      |                                |               |                |                 |                  |          |       |

| R = Readab   | ole bit                        | P = Program   | mable bit      | U = Unimplen    | nented bit, read | l as '0' |       |

| -n = Value w | vhen device is unp             | programmed    |                | x = Bit is unkr | nown             |          |       |

|              | •                              | 0             |                |                 |                  |          |       |

| bit 7-5      | Unimplement                    | ted: Read as  | ʻ0'            |                 |                  |          |       |

| bit 4-1      | WDTPS<3:0>                     | : Watchdog T  | imer Postscale | Select bits     |                  |          |       |

|              | 1111 <b>= 1:32,7</b>           | 68            |                |                 |                  |          |       |

|              | 1110 <b>= 1</b> : <b>16</b> ,3 | 384           |                |                 |                  |          |       |

|              | 1101 <b>= 1:8,1</b> 9          |               |                |                 |                  |          |       |

|              | 1100 <b>= 1:4,0</b> 9          |               |                |                 |                  |          |       |

|              | 1011 <b>= 1:2,0</b> 4          |               |                |                 |                  |          |       |

|              | 1010 = 1:1,02                  |               |                |                 |                  |          |       |

|              | 1001 = 1:512                   |               |                |                 |                  |          |       |

|              | 1000 = 1:256                   |               |                |                 |                  |          |       |

|              | 0111 = 1:128                   |               |                |                 |                  |          |       |

|              | 0110 = 1:64<br>0101 = 1:32     |               |                |                 |                  |          |       |

|              | 0101 = 1.32<br>0100 = 1.16     |               |                |                 |                  |          |       |

|              | 0100 = 1.10<br>0011 = 1.8      |               |                |                 |                  |          |       |

|              | 0011 = 1.8<br>0010 = 1.4       |               |                |                 |                  |          |       |

|              | 0010 = 1.4<br>0001 = 1.2       |               |                |                 |                  |          |       |

|              | 0000 = 1:1                     |               |                |                 |                  |          |       |

| bit 0        | WDTEN: Wat                     | obdog Timor I | Enable bit     |                 |                  |          |       |

|              |                                |               | I. SWDTEN bit  | has no effect   |                  |          |       |

|              | 0 = WDT is co                  | ways chabled  |                |                 |                  |          |       |

| BCF                                                                         | Bit Clear                                                                                                                                                   | f                                                                                                         |                                                                                                 |                                                                           |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| Syntax:                                                                     | BCF f, b                                                                                                                                                    | {,a}                                                                                                      |                                                                                                 |                                                                           |  |

| Operands:                                                                   | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                                                                                       |                                                                                                           |                                                                                                 |                                                                           |  |

| Operation:                                                                  | $0 \rightarrow f < b >$                                                                                                                                     |                                                                                                           |                                                                                                 |                                                                           |  |

| Status Affected:                                                            | None                                                                                                                                                        |                                                                                                           |                                                                                                 |                                                                           |  |

| Encoding:                                                                   | 1001                                                                                                                                                        | bbba                                                                                                      | ffff                                                                                            | ffff                                                                      |  |

|                                                                             | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>Section 24<br>Bit-Oriente<br>Literal Offs | he BSR i<br>(default).<br>nd the e:<br>led, this i<br>Literal O<br>hever $f \le$<br>.2.3 "By<br>ed Instru | s used to a<br>attended in<br>nstruction<br>ffset Addre<br>95 (5Fh).<br>te-Oriente<br>ctions in | select the<br>struction<br>operates<br>essing<br>See<br>ed and<br>Indexed |  |

| Words:                                                                      | 1                                                                                                                                                           |                                                                                                           |                                                                                                 |                                                                           |  |

| Cycles:                                                                     | 1                                                                                                                                                           |                                                                                                           |                                                                                                 |                                                                           |  |

| Q Cycle Activity:                                                           |                                                                                                                                                             |                                                                                                           |                                                                                                 |                                                                           |  |

| Q1                                                                          | Q2                                                                                                                                                          | Q3                                                                                                        | 3                                                                                               | Q4                                                                        |  |

| Decode                                                                      | Read<br>register 'f'                                                                                                                                        | Proce<br>Dat                                                                                              |                                                                                                 | Write<br>gister 'f'                                                       |  |

| Example:                                                                    | BCF F                                                                                                                                                       | LAG_RE                                                                                                    | G, 7, (                                                                                         | C                                                                         |  |

| Before Instruction<br>FLAG_REG = C7h<br>After Instruction<br>FLAG_REG = 47h |                                                                                                                                                             |                                                                                                           |                                                                                                 |                                                                           |  |

| BN                                        |                 | Branch if                                                                                                                | Negativ                                                                   | /e                                   |                                               |  |  |  |  |  |

|-------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Synta                                     | ax:             | BN n                                                                                                                     |                                                                           |                                      |                                               |  |  |  |  |  |

| Oper                                      | ands:           | -128 ≤ n ≤ 1                                                                                                             | 27                                                                        |                                      |                                               |  |  |  |  |  |

| Oper                                      | ation:          |                                                                                                                          | if NEGATIVE bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                  |                                      |                                               |  |  |  |  |  |

| Statu                                     | s Affected:     | None                                                                                                                     |                                                                           |                                      |                                               |  |  |  |  |  |

| Enco                                      | ding:           | 1110                                                                                                                     | 0110                                                                      | nnnr                                 | n nnnn                                        |  |  |  |  |  |

| Desc                                      | ription:        | If the NEGA<br>program will<br>The 2's con<br>added to the<br>incremented<br>instruction,<br>PC + 2 + 2r<br>2-cycle inst | l branch.<br>pplement<br>e PC. Sin<br>d to fetch<br>the new<br>n. This in | numbe<br>ice the<br>the ne<br>addres | er '2n' is<br>PC will hav<br>ext<br>s will be |  |  |  |  |  |

| Word                                      | ls:             | 1                                                                                                                        |                                                                           |                                      |                                               |  |  |  |  |  |

| Cycle                                     | es:             | 1(2)                                                                                                                     |                                                                           |                                      |                                               |  |  |  |  |  |