#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f13k22-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.8 Oscillator Start-up Timer

The Primary External Oscillator, when configured for LP, XT or HS modes, incorporates an Oscillator Start-up Timer (OST). The OST ensures that the oscillator starts and provides a stable clock to the oscillator module. The OST times out when 1024 oscillations on OSC1 have occurred. During the OST period, with the system clock set to the Primary External Oscillator, the program counter does not increment suspending program execution. The OST period will occur following:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Wake-up from Sleep

- · Oscillator being enabled

- Expiration of Power-up Timer (PWRT)

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Start-up mode can be selected. See **Section 2.11** "**Two-Speed Start-up Mode**" for more information.

## 2.9 Clock Switching

The device contains circuitry to prevent clock "glitches" due to a change of the system clock source. To accomplish this, a short pause in the system clock occurs during the clock switch. If the new clock source is not stable (e.g., OST is active), the device will continue to execute from the old clock source until the new clock source becomes stable. The timing of a clock switch is as follows:

- 1. SCS<1:0> bits of the OSCCON register are modified.

- 2. The system clock will continue to operate from the old clock until the new clock is ready.

- Clock switch circuitry waits for two consecutive rising edges of the old clock after the new clock is ready.

- 4. The system clock is held low, starting at the next falling edge of the old clock.

- 5. Clock switch circuitry waits for an additional two rising edges of the new clock.

- On the next falling edge of the new clock, the low hold on the system clock is release and the new clock is switched in as the system clock.

- 7. Clock switch is complete.

Refer to Figure 2-5 for more details.

| Old Clock                  | li liiii | - Elinear Alassa (Carasta A | <br> | Republica |

|----------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------|------|-----------|

| New Clock                  |                                                                                                                |                             |      |           |

| New Cit Peacy              |                                                                                                                |                             | <br> |           |

| IRCF <2:0>                 | beli Chi 🗴 Sabeli Naw                                                                                          |                             |      |           |

| System Clock               |                                                                                                                |                             |      |           |

|                            |                                                                                                                |                             |      |           |

| Low Space Nig<br>Old Clock | 93 <b>8338</b> 893<br>                                                                                         | Clock Sync                  | <br> | Running   |

|                            |                                                                                                                | Cieck Syne                  |      | Running   |

| ORI ORICE                  |                                                                                                                | Clock Byne                  |      |           |

| OKI OKAX                   |                                                                                                                | Clock Gyne                  |      | 9         |

## FIGURE 2-5: CLOCK SWITCH TIMING

| File Name | Bit 7                                                                                                                              | Bit 6           | Bit 5          | Bit 4         | Bit 3             | Bit 2           | Bit 1            | Bit 0           | Value on<br>POR, BOR | Details<br>on<br>page: |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---------------|-------------------|-----------------|------------------|-----------------|----------------------|------------------------|

| TOSU      | _                                                                                                                                  | _               | _              | Top-of-Stack  | Upper Byte (TO    | S<20:16>)       |                  |                 | 0 000                | 245, 25                |

| TOSH      | Top-of-Stack,                                                                                                                      | High Byte (TC   | )<br>S<15:8>)  |               |                   |                 |                  |                 | 0000 000             | 245, 25                |

| TOSL      | Top-of-Stack,                                                                                                                      | Low Byte (TO    | S<7:0>)        |               |                   |                 |                  |                 | 0000 000             | 245, 25                |

| STKPTR    | STKOVF                                                                                                                             | STKUNF          | _              | SP4           | SP3               | SP2             | SP1              | SP0             | 00-0 000             | 245, 26                |

| PCLATU    | _                                                                                                                                  | _               | _              | Holding Regi  | ister for PC<20:1 | 6>              |                  |                 | 0 000                | 245, 25                |

| PCLATH    | Holding Regi                                                                                                                       | ster for PC<15  | :8>            |               |                   |                 |                  |                 | 0000 000             | 245, 25                |

| PCL       | PC, Low Byte                                                                                                                       | e (PC<7:0>)     |                |               |                   |                 |                  |                 | 0000 000             | 245, 25                |

| TBLPTRU   | _                                                                                                                                  | _               | _              | Program Mer   | mory Table Point  | er Upper Byte   | (TBLPTR<20:1     | 6>)             | 0 000                | 245, 48                |

| TBLPTRH   | Program Mer                                                                                                                        | nory Table Poi  | nter, High Byt | e (TBLPTR<1   | 5:8>)             |                 |                  |                 | 0000 000             | 245, 48                |

| TBLPTRL   | Program Mer                                                                                                                        | nory Table Poi  | nter, Low Byte | e (TBLPTR<7:  | 0>)               |                 |                  |                 | 0000 000             | 245, 48                |

| TABLAT    | Program Mer                                                                                                                        | nory Table Lat  | ch             |               | ,                 |                 |                  |                 | 0000 000             | 245, 48                |

| PRODH     | Product Regi                                                                                                                       | ster, High Byte | )              |               |                   |                 |                  |                 | xxxx xxx             | x 245, 58              |

| PRODL     | Product Regi                                                                                                                       | ster, Low Byte  |                |               |                   |                 |                  |                 | xxxx xxx             | x 245, 58              |

| INTCON    | GIE/GIEH                                                                                                                           | PEIE/GIEL       | TMR0IE         | INTOIE        | RABIE             | TMR0IF          | INTOIF           | RABIF           | 0000 000:            |                        |

| INTCON2   | RABPU                                                                                                                              | INTEDG0         | INTEDG1        | INTEDG2       | _                 | TMR0IP          | _                | RABIP           | 1111 -1-             |                        |

| INTCON3   | INT2IP                                                                                                                             | INT1IP          | _              | INT2IE        | INT1IE            | _               | INT2IF           | INT1IF          | 11-0 0-0             | -                      |

| INDF0     | Uses content                                                                                                                       | s of FSR0 to a  | ddress data n  | nemory – valu | e of FSR0 not cl  | nanged (not a p | hysical registe  | r)              | N/A                  | 245, 41                |

| POSTINC0  |                                                                                                                                    |                 |                |               | e of FSR0 post-i  | • • •           | , ,              | ,               | N/A                  | 245. 41                |

| POSTDEC0  |                                                                                                                                    |                 |                |               |                   | N/A             | 245, 41          |                 |                      |                        |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)                             |                 |                |               |                   | N/A             | 245, 41          |                 |                      |                        |

| PLUSW0    | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W |                 |                |               |                   | , ,             | N/A              | 245, 41         |                      |                        |

| FSR0H     | _                                                                                                                                  |                 | _              |               | Indirect Data M   | emory Address   | s Pointer 0, Hig | h Byte          | 000                  | 245, 41                |

| FSR0L     | Indirect Data                                                                                                                      | Memory Addre    | ess Pointer 0, | Low Byte      |                   | ,               | , 0              |                 | xxxx xxx             |                        |

| WREG      | Working Reg                                                                                                                        |                 | ,              | ,             |                   |                 |                  |                 | xxxx xxx             |                        |

| INDF1     | Uses content                                                                                                                       | s of FSR1 to a  | ddress data n  | nemory – valu | e of FSR1 not cl  | nanged (not a p | physical registe | r)              | N/A                  | 245, 41                |

| POSTINC1  |                                                                                                                                    |                 |                | -             | e of FSR1 post-i  |                 |                  |                 | N/A                  | 245, 41                |

| POSTDEC1  | Uses content                                                                                                                       | s of FSR1 to a  | ddress data n  | nemory – valu | e of FSR1 post-   | decremented (r  | not a physical r | egister)        | N/A                  | 245, 41                |

| PREINC1   | Uses content                                                                                                                       | s of FSR1 to a  | ddress data n  | nemory – valu | e of FSR1 pre-ir  | cremented (no   | t a physical reg | gister)         | N/A                  | 245, 41                |

| PLUSW1    | Uses content<br>of FSR1 offse                                                                                                      |                 | ddress data n  | nemory – valu | e of FSR1 pre-in  | cremented (no   | t a physical reg | jister) – value | N/A                  | 245, 41                |

| FSR1H     | _                                                                                                                                  | _               | _              | _             | Indirect Data M   | emory Address   | s Pointer 1, Hig | h Byte          | 000                  | 246, 41                |

| FSR1L     | Indirect Data                                                                                                                      | Memory Addre    | ess Pointer 1, | Low Byte      |                   | -               | -                | -               | xxxx xxx             | x 246, 41              |

| BSR       |                                                                                                                                    | _               | _              | _             | Bank Select Re    | egister         |                  |                 | 000                  | 246, 30                |

| INDF2     | Uses content                                                                                                                       | s of FSR2 to a  | ddress data n  | nemory – valu | e of FSR2 not cl  |                 | physical registe | r)              | N/A                  | 246, 41                |

| POSTINC2  |                                                                                                                                    |                 |                |               | e of FSR2 post-i  | • • •           | , ,              | ,               | N/A                  | 246, 41                |

| POSTDEC2  |                                                                                                                                    |                 |                | · · ·         | e of FSR2 post-   |                 |                  | • /             | N/A                  | 246, 41                |

| PREINC2   |                                                                                                                                    |                 |                | -             | e of FSR2 pre-ir  |                 |                  |                 | N/A                  | 246, 41                |

| PLUSW2    |                                                                                                                                    | s of FSR2 to a  |                | -             | e of FSR2 pre-in  |                 |                  |                 | N/A                  | 246, 41                |

| FSR2H     | _                                                                                                                                  | _               | —              | _             | Indirect Data M   | emory Address   | s Pointer 2, Hig | h Byte          | 000                  | 246, 41                |

| FSR2L     |                                                                                                                                    | Memory Addre    | ess Pointer 2. | Low Byte      |                   | -               |                  | -               | XXXX XXX             |                        |

| STATUS    | _                                                                                                                                  | _               |                | N             | OV                | Z               | DC               | С               | x xxx                |                        |

$\label{eq:legend: second sec$

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise it is disabled and reads as '0'. See Section 22.4 "Brown-out Reset (BOR)".

2: The RA3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0). Otherwise, RA3 reads as '0'. This bit is read-only.

3: Unimplemented, read as '1'.

| R/W-x      | K R/W-x              | U-0                                 | R/W-0           | R/W-x                         | R/W-0           | R/S-0                                  | R/S-0          |

|------------|----------------------|-------------------------------------|-----------------|-------------------------------|-----------------|----------------------------------------|----------------|

| EEPGI      | D CFGS               | —                                   | FREE            | WRERR                         | WREN            | WR                                     | RD             |

| bit 7      |                      |                                     |                 |                               |                 |                                        | bit 0          |

|            |                      |                                     |                 |                               |                 |                                        |                |

| Legend:    |                      |                                     |                 |                               |                 |                                        |                |

| R = Read   |                      | W = Writable                        |                 |                               |                 |                                        |                |

|            | n be set by software |                                     |                 | -                             | nented bit, rea |                                        |                |

| -n = Value | e at POR             | '1' = Bit is set                    |                 | '0' = Bit is cle              | ared            | x = Bit is unkr                        | IOWN           |

| bit 7      | <b>EEPGD:</b> Flas   | h Program or [                      | Data EEPROM     | 1 Memory Selec                | ct bit          |                                        |                |

|            |                      | lash program r                      |                 | 2                             |                 |                                        |                |

|            | 0 = Access d         | ata EEPROM                          | memory          |                               |                 |                                        |                |

| bit 6      | CFGS: Flash          | Program/Data                        | EEPROM or       | Configuration S               | elect bit       |                                        |                |

|            |                      | onfiguration re                     |                 | 214                           |                 |                                        |                |

|            |                      | lash program o                      |                 |                               |                 |                                        |                |

| bit 5      | •                    | ted: Read as '                      |                 | .,                            |                 |                                        |                |

| bit 4      |                      | Row (Block) E                       |                 |                               |                 |                                        |                |

|            |                      | e program men                       |                 |                               | PIR on the ne   | ext WR comman                          | IC             |

|            | 0 = Perform  v       |                                     |                 |                               |                 |                                        |                |

| bit 3      | WRERR: Flas          | sh Program/Da                       | ta EEPROM B     | Error Flag bit <sup>(1)</sup> |                 |                                        |                |

|            |                      |                                     |                 |                               | et during self- | timed programn                         | ning in normal |

|            |                      | , or an improp                      |                 | pt)                           |                 |                                        |                |

|            | 0 = 1 he write       | operation con                       | npleted         |                               |                 |                                        |                |

| bit 2      |                      | Program/Data                        |                 |                               |                 |                                        |                |

|            |                      |                                     |                 |                               |                 |                                        |                |

| 1.11.4     |                      | 2                                   | lasn program    | data EEPROM                   |                 |                                        |                |

| bit 1      | WR: Write Co         |                                     | 1 orooo/write a |                               |                 | and avala ar writ                      |                |

|            |                      |                                     |                 |                               |                 | ase cycle or writ<br>e write is comple |                |

|            |                      |                                     |                 | ed) by software               |                 |                                        | 010.           |

|            | 0 = Write cyc        | le to the EEPR                      | ROM is comple   | ete                           |                 |                                        |                |

| bit 0      | RD: Read Co          | ntrol bit                           |                 |                               |                 |                                        |                |

|            |                      |                                     |                 |                               |                 | hardware. The R                        |                |

|            | •                    | ot cleared) by s<br>initiate an EEF |                 | it cannot be set              | when EEPGD      | = 1 or CFGS =                          | 1.)            |

| Note 1:    | When a WRERR c       | occurs, the FF                      | PGD and CFG     | S bits are not c              | leared. This a  | llows tracing of                       | the            |

|            | error condition.     | ,                                   |                 |                               |                 |                                        |                |

#### REGISTER 4-1: EECON1: DATA EEPROM CONTROL 1 REGISTER

## 4.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 4.2.3 TBLPTR – TABLE POINTER REGISTER

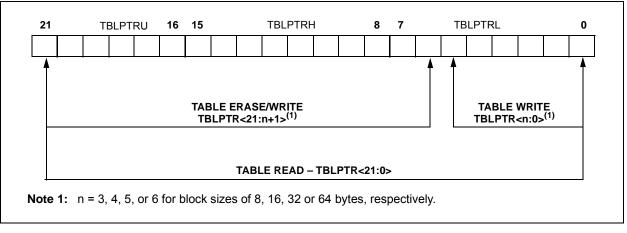

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 4-2. These operations on the TBLPTR affect only the low-order 21 bits.

## 4.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register.

When a TBLWT is executed the byte in the TABLAT register is written, not to Flash memory but, to a holding register in preparation for a program memory write. The holding registers constitute a write block which varies depending on the device (See Table 4-1). The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

When a program memory write is executed the entire holding register block is written to the Flash memory at the address determined by the MSbs of the TBLPTR. The 3, 4, or 5 LSBs are ignored during Flash memory writes. For more detail, see **Section 4.5** "Writing to **Flash Program Memory**".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 4-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

#### TABLE 4-2: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |  |  |  |  |

|--------------------|---------------------------------------------|--|--|--|--|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |  |  |  |  |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |  |  |  |  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |  |  |  |  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |  |  |  |  |

#### FIGURE 4-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

| U-0               | U-0 | R/W-x            | R/W-x | U-0               | R/W-x              | R/W-x            | R/W-x |

|-------------------|-----|------------------|-------|-------------------|--------------------|------------------|-------|

|                   | —   | LATA5            | LATA4 | —                 | LATA2              | LATA1            | LATA0 |

| bit 7             |     |                  |       |                   |                    |                  | bit 0 |

|                   |     |                  |       |                   |                    |                  |       |

| Legend:           |     |                  |       |                   |                    |                  |       |

| R = Readable bit  |     | W = Writable bi  | t     | U = Unimpleme     | ented bit, read as | ʻ0'              |       |

| -n = Value at POI | २   | '1' = Bit is set |       | '0' = Bit is clea | red                | x = Bit is unkno | wn    |

## REGISTER 8-3: LATA: PORTA DATA LATCH REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-4 LATA<5:4>: RA<5:4> Port I/O Output Latch Register bits

bit 3 Unimplemented: Read as '0'

bit 2-0 LATA<2:0>: RA<2:0> Port I/O Output Latch Register bits

#### REGISTER 8-4: WPUA: WEAK PULL-UP PORTA REGISTER

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1                | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|----------------------|-------|-------|-------|

| —     | —   | WPUA5 | WPUA4 | WPUA3 <sup>(1)</sup> | WPUA2 | WPUA1 | WPUA0 |

| bit 7 |     |       |       |                      |       |       | bit 0 |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | ʻ0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Enable bit

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

#### REGISTER 8-5: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     |     | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | ʻ0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: PORTA I/O Pin bit 1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

#### 14.3.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF bit of the SSPSTAT register is set, or bit SSPOV bit of the SSPCON1 register is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF of the PIR1 register, must be cleared by software.

When the SEN bit of the SSPCON2 register is set, SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting the CKP bit of the SSPCON1 register. See **Section 14.3.4** "**Clock Stretching**" for more detail.

#### 14.3.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin SCK/SCL is held low regardless of SEN (see Section 14.3.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin SCK/SCL should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 14-9).

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPBUF register. Again, pin SCK/SCL must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

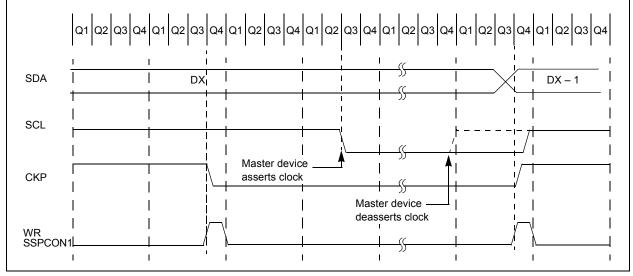

## 14.3.4.5 Clock Synchronization and the CKP bit

When the CKP bit is cleared, the SCL output is forced to '0'. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 14-12).

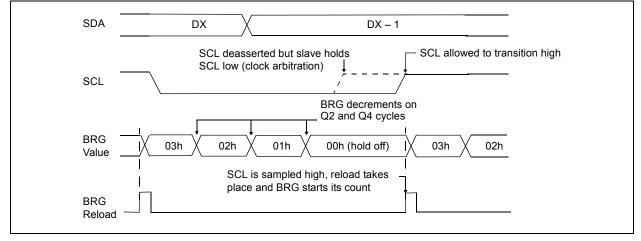

#### 14.3.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 14-18).

#### FIGURE 14-18: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

## 15.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRG register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF Interrupt Flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 15.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 15-7), and asynchronously if the device is in Sleep mode (Figure 15-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 15.3.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### <u>WUE Bit</u>

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared by hardware by a rising edge on RX/DT. The interrupt condition is then cleared by software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

#### 16.2.10 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

| Note: | Analog pin control is performed by the |

|-------|----------------------------------------|

|       | ANSEL and ANSELH registers. For        |

|       | ANSEL and ANSELH registers, see        |

|       | Register 8-14 and Register 8-15,       |

|       | respectively.                          |

#### REGISTER 16-1: ADCON0: A/D CONTROL REGISTER 0

| U-0                                                                  | U-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0   | R/W-0 |  |  |

|----------------------------------------------------------------------|-----|-------|-------|-----------------------------------------|-------|---------|-------|--|--|

| —                                                                    |     | CHS3  | CHS2  | CHS1                                    | CHS0  | GO/DONE | ADON  |  |  |

| bit 7 bit 0                                                          |     |       |       |                                         |       |         |       |  |  |

|                                                                      |     |       |       |                                         |       |         |       |  |  |

| Legend:                                                              |     |       |       |                                         |       |         |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |       |       | ad as '0'                               |       |         |       |  |  |

| -n = Value at POR '1' = Bit is set                                   |     |       |       | '0' = Bit is cleared x = Bit is unknown |       |         |       |  |  |

#### bit 7-6 Unimplemented: Read as '0'

| bit 5-2 | CHS<3:0>: Analog Channel Select bits                                                                  |

|---------|-------------------------------------------------------------------------------------------------------|

|         | 0000 <b>= ANO</b>                                                                                     |

|         | 0001 = AN1                                                                                            |

|         | 0010 <b>= AN2</b>                                                                                     |

|         | 0011 <b>= AN3</b>                                                                                     |

|         | 0100 <b>= AN4</b>                                                                                     |

|         | 0101 <b>= AN5</b>                                                                                     |

|         | 0110 <b>= AN6</b>                                                                                     |

|         | 0111 = AN7                                                                                            |

|         | 1000 <b>= AN8</b>                                                                                     |

|         | 1001 = AN9                                                                                            |

|         | 1010 = AN10                                                                                           |

|         | 1011 = AN11                                                                                           |

|         | 1100 = Reserved                                                                                       |

|         | 1101 = Reserved                                                                                       |

|         | $1110 = DAC^{(2)}$<br>$1111 = FVR^{(2)}$                                                              |

|         |                                                                                                       |

| bit 1   | GO/DONE: A/D Conversion Status bit                                                                    |

|         | 1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.                |

|         | This bit is automatically cleared by hardware when the A/D conversion has completed.                  |

|         | 0 = A/D conversion completed/not in progress                                                          |

| bit 0   | ADON: ADC Enable bit                                                                                  |

|         | 1 = ADC is enabled                                                                                    |

|         | 0 = ADC is disabled and consumes no operating current                                                 |

| Note 1: | Selecting reserved channels will yield unpredictable results as unimplemented input channels are left |

|         | floating.                                                                                             |

| 2:      | See Section 20.0 "Fixed Voltage Reference (FVR)" for more information.                                |

| Name   | Bit 7                          | Bit 6     | Bit 5  | Bit 4      | Bit 3        | Bit 2  | Bit 1   | Bit 0  | Reset<br>Values<br>on page |  |

|--------|--------------------------------|-----------|--------|------------|--------------|--------|---------|--------|----------------------------|--|

| ADRESH | A/D Result Register, High Byte |           |        |            |              |        |         |        |                            |  |

| ADRESL |                                |           | A/C    | Result Reg | ister, Low B | yte    |         |        | 247                        |  |

| ADCON0 | _                              | _         | CHS3   | CHS2       | CHS1         | CHS0   | GO/DONE | ADON   | 247                        |  |

| ADCON1 | _                              | _         | _      |            | PVCFG1       | PVCFG0 | NVCFG1  | NVCFG0 | 247                        |  |

| ADCON2 | ADFM                           |           | ACQT2  | ACQT1      | ACQT0        | ADCS2  | ADCS1   | ADCS0  | 247                        |  |

| ANSEL  | ANS7                           | ANS6      | ANS5   | ANS4       | ANS3         | ANS2   | ANS1    | ANS0   | 248                        |  |

| ANSELH | —                              | —         | —      | _          | ANS11        | ANS10  | ANS9    | ANS8   | 248                        |  |

| INTCON | GIE/GIEH                       | PEIE/GIEL | TMR0IE | INT0IE     | RABIE        | TMR0IF | INT0IF  | RABIF  | 245                        |  |

| IPR1   | _                              | ADIP      | RCIP   | TXIP       | SSPIP        | CCP1IP | TMR2IP  | TMR1IP | 248                        |  |

| PIE1   | _                              | ADIE      | RCIE   | TXIE       | SSPIE        | CCP1IE | TMR2IE  | TMR1IE | 248                        |  |

| PIR1   | _                              | ADIF      | RCIF   | TXIF       | SSPIF        | CCP1IF | TMR2IF  | TMR1IF | 248                        |  |

| TRISA  | _                              | —         | TRISA5 | TRISA4     | (1)          | TRISA2 | TRISA1  | TRISA0 | 248                        |  |

| TRISB  | TRISB7                         | TRISB6    | TRISB5 | TRISB4     | —            | —      | —       | —      | 248                        |  |

| TRISC  | TRISC7                         | TRISC6    | TRISC5 | TRISC4     | TRISC3       | TRISC2 | TRISC1  | TRISC0 | 248                        |  |

TABLE 16-2:

REGISTERS ASSOCIATED WITH A/D OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Unimplemented, read as '1'.

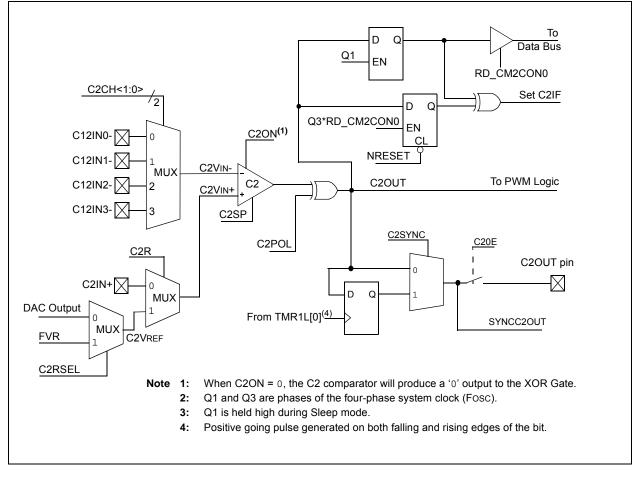

## 17.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-Change

- Wake-up from Sleep

- Programmable Speed/Power optimization

- · PWM shutdown

- · Programmable and fixed voltage reference

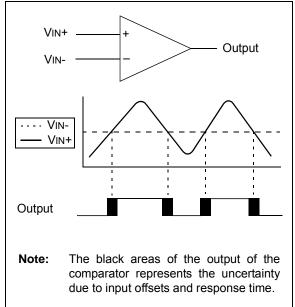

## 17.1 Comparator Overview

A single comparator is shown in Figure 17-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

#### FIGURE 17-1: SINGLE COMPARATOR

# PIC18(L)F1XK22

## 18.0 POWER-MANAGED MODES

PIC18(L)F1XK22 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- Sleep mode

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> microcontroller devices. One is the clock switching feature which allows the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC microcontroller devices, where all device clocks are stopped.

## 18.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions:

- Whether or not the CPU is to be clocked

- The selection of a clock source

The IDLEN bit of the OSCCON register controls CPU clocking, while the SCS<1:0> bits of the OSCCON register select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 18-1.

## 18.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- The primary clock, as defined by the FOSC<3:0> Configuration bits

- The secondary clock (the Timer1 oscillator)

- The internal oscillator block

#### 18.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. Refer to **Section 2.9 "Clock Switching"** for more information.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit of the OSCCON register.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mode     | OSCCON Bits          |          | Module            | Clocking | Available Clock and Oscillator Source                                                                                           |

|----------|----------------------|----------|-------------------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| wode     | IDLEN <sup>(1)</sup> | SCS<1:0> | 0> CPU Peripheral |          | Available Clock and Oscillator Source                                                                                           |

| Sleep    | 0                    | N/A      | Off               | Off      | None – All clocks are disabled                                                                                                  |

| PRI_RUN  | N/A                  | 00       | Clocked           | Clocked  | Primary – LP, XT, HS, RC, EC and Internal<br>Oscillator Block <sup>(2)</sup> .<br>This is the normal full power execution mode. |

| SEC_RUN  | N/A                  | 01       | Clocked           | Clocked  | Secondary – Timer1 Oscillator                                                                                                   |

| RC_RUN   | N/A                  | 1x       | Clocked           | Clocked  | Internal Oscillator Block <sup>(2)</sup>                                                                                        |

| PRI_IDLE | 1                    | 00       | Off               | Clocked  | Primary – LP, XT, HS, HSPLL, RC, EC                                                                                             |

| SEC_IDLE | 1                    | 01       | Off               | Clocked  | Secondary – Timer1 Oscillator                                                                                                   |

| RC_IDLE  | 1                    | 1x       | Off               | Clocked  | Internal Oscillator Block <sup>(2)</sup>                                                                                        |

#### TABLE 18-1: POWER-MANAGED MODES

**Note 1:** IDLEN reflects its value when the SLEEP instruction is executed.

2: Includes HFINTOSC and HFINTOSC postscaler, as well as the LFINTOSC source.

## 22.5 Device Reset Timers

PIC18(L)F1XK22 devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 22.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of PIC18(L)F1XK22 devices is an 11-bit counter which uses the LFINTOSC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the LFINTOSC clock and will vary from chip-to-chip due to temperature and process variation. See **Section 26.0 "Electrical Specifications"** for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 22.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from all power-managed modes that stop the external oscillator.

## 22.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 22.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 22-3, Figure 22-4, Figure 22-5, Figure 22-6 and Figure 22-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 22-3 through 22-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire, after which, bringing  $\overline{\text{MCLR}}$  high will allow program execution to begin immediately (Figure 22-5). This is useful for testing purposes or to synchronize more than one PIC18(L)F1XK22 device operating in parallel.

| Oscillator     | Power-up <sup>(2)</sup> ar                             | Exit from                       |                                 |  |

|----------------|--------------------------------------------------------|---------------------------------|---------------------------------|--|

| Configuration  | <b>PWRTEN =</b> 0                                      | PWRTEN = 1                      | Power-Managed Mode              |  |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |  |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |  |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | _                               | _                               |  |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | —                               | _                               |  |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   | _                               | _                               |  |

#### TABLE 22-2: TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

2: 2 ms is the nominal time required for the PLL to lock.

## 24.1.1 STANDARD INSTRUCTION SET

| ADD     | DLW               | ADD litera                          | ADD literal to W |     |       |      |  |  |  |

|---------|-------------------|-------------------------------------|------------------|-----|-------|------|--|--|--|

| Synt    | ax:               | ADDLW                               | ADDLW k          |     |       |      |  |  |  |

| Oper    | ands:             | $0 \leq k \leq 255$                 |                  |     |       |      |  |  |  |

| Oper    | ation:            | $(W) + k \rightarrow V$             | Ν                |     |       |      |  |  |  |

| Statu   | is Affected:      | N, OV, C, D                         | )C, Z            |     |       |      |  |  |  |

| Enco    | oding:            | 0000                                | 1111             | kkk | k }   | kkk  |  |  |  |

| Desc    | cription:         | The conten<br>8-bit literal '<br>W. |                  |     |       |      |  |  |  |

| Word    | ds:               | 1                                   |                  |     |       |      |  |  |  |

| Cycle   | es:               | 1                                   | 1                |     |       |      |  |  |  |

| QC      | ycle Activity:    |                                     |                  |     |       |      |  |  |  |

|         | Q1                | Q2                                  | Q3               | 3   | Q     | 4    |  |  |  |

|         | Decode            | Read<br>literal 'k'                 | Proce<br>Data    |     | Write | to W |  |  |  |

|         |                   |                                     |                  |     |       |      |  |  |  |

| Exar    | nple:             | ADDLW 1                             | .5h              |     |       |      |  |  |  |

|         | Before Instruc    | tion                                |                  |     |       |      |  |  |  |

| W = 10h |                   |                                     |                  |     |       |      |  |  |  |

|         | After Instruction | on                                  |                  |     |       |      |  |  |  |

|         | W =               | 25h                                 |                  |     |       |      |  |  |  |

|         |                   |                                     |                  |     |       |      |  |  |  |

|         |                   |                                     |                  |     |       |      |  |  |  |

| ADDWF            | ADD W to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | ADDWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Status Affected: | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Encoding:        | 0010 01da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Description:     | Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '0', the ASR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| QC | ycle Activity:                |                      |              |                 |      |                      |  |  |

|----|-------------------------------|----------------------|--------------|-----------------|------|----------------------|--|--|

|    | Q1                            |                      | Q2           | G               | 23   | Q4                   |  |  |

|    | Decode                        | Read<br>register 'f' |              | Process<br>Data |      | Write to destination |  |  |

|    | Example:<br>Before Instruc    |                      | DDWF         | REG,            | 0, 0 |                      |  |  |

|    | W<br>REG<br>After Instruction | =<br>=<br>on         | 17h<br>0C2h  |                 |      |                      |  |  |

|    | W<br>REG                      | =<br>=               | 0D9h<br>0C2h |                 |      |                      |  |  |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

## 24.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB® IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18(L)F1XK22 family of devices. This includes the MPLAB<sup>®</sup> C18 C compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- · A command line option

- · A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

## 26.3 DC Characteristics

## TABLE 26-1:SUPPLY VOLTAGE

| PIC18LF       | 1XK22  |                                                           | Standard Operating Conditions (unless otherwise stated) |       |      |       |                                            |  |  |  |  |

|---------------|--------|-----------------------------------------------------------|---------------------------------------------------------|-------|------|-------|--------------------------------------------|--|--|--|--|

| PIC18F1       | XK22   |                                                           | Standard Operating Conditions (unless otherwise stated) |       |      |       |                                            |  |  |  |  |

| Param.<br>No. | Sym.   | Characteristic                                            | Min.                                                    | Тур.† | Max. | Units | Conditions                                 |  |  |  |  |

| D001          | Vdd    | Supply Voltage                                            |                                                         |       |      |       |                                            |  |  |  |  |

|               |        | PIC18LF1XK22                                              | 1.8                                                     | _     | 3.6  | V     | Fosc ≤ 16 MHz                              |  |  |  |  |

|               |        |                                                           | 2.0                                                     |       | 3.6  | V     | Fosc ≤ 20 MHz                              |  |  |  |  |

|               |        |                                                           | 3.0                                                     |       | 3.6  | V     | $FOSC \le 64 \text{ MHz} \le 85^{\circ}C$  |  |  |  |  |

|               |        |                                                           | 3.0                                                     | _     | 3.6  | V     | $Fosc \le 48 \text{ MHz} \le 125^{\circ}C$ |  |  |  |  |

| D001          |        | PIC18F1XK22                                               | 2.3                                                     | -     | 5.5  | V     | Fosc ≤ 20 MHz                              |  |  |  |  |

|               |        |                                                           | 3.0                                                     |       | 5.5  | V     | $FOSC \le 64 \text{ MHz} \le 85^{\circ}C$  |  |  |  |  |

|               |        |                                                           | 3.0                                                     |       | 5.5  | V     | $FOSC \le 48 \text{ MHz} \le 125^{\circ}C$ |  |  |  |  |

| D002*         | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                 |                                                         |       |      |       |                                            |  |  |  |  |

|               |        | PIC18LF1XK22                                              | 1.5                                                     | _     | _    | V     | Device in Sleep mode                       |  |  |  |  |

| D002*         |        | PIC18F1XK22                                               | 1.7                                                     | _     | _    | V     | Device in Sleep mode                       |  |  |  |  |

|               | VPOR*  | Power-on Reset Release Voltage                            |                                                         | 1.6   | _    | V     |                                            |  |  |  |  |

|               | VPORR* | Power-on Reset Rearm Voltage                              | _                                                       | 0.8   | _    | V     |                                            |  |  |  |  |

| D004*         | SVDD   | VDD Rise Rate to ensure internal<br>Power-on Reset signal | 0.05                                                    | —     | —    | V/ms  |                                            |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

## TABLE 26-13: OSCILLATOR PARAMETERS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                          |                    |      |              |      |            |                                                                                                             |  |  |

|---------------|---------------------------------------------------------|----------------------------------------------------------|--------------------|------|--------------|------|------------|-------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                                           | Freq.<br>Tolerance | Min. | Typ.†        | Max. | Units      | Conditions                                                                                                  |  |  |

| OS08          | HFosc                                                   | Internal Calibrated HFINTOSC<br>Frequency <sup>(2)</sup> | ±2%<br>±3%         |      | 16.0<br>16.0 |      | MHz<br>MHz | $\begin{array}{l} 0^{\circ}C \leq TA \leq 60^{\circ}C \\ 60^{\circ}C \leq TA \leq +85^{\circ}C \end{array}$ |  |  |

|               |                                                         |                                                          | ±5%                | —    | 16.0         | —    | MHz        |                                                                                                             |  |  |

| OS09          | LFosc                                                   | Internal LFINTOSC Frequency                              | 0                  | _    | 31.25        | _    | kHz        |                                                                                                             |  |  |

| OS10*         | TIOSC ST                                                | HFINTOSC                                                 | —                  | _    | 5            | 8    | μS         | VDD = 2.0V, -40°C to +85°C                                                                                  |  |  |