Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D.L.II.                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f13k22-i-ss |

#### 2.7.1 OSCTUNE REGISTER

The HFINTOSC is factory-calibrated, but can be adjusted in software by writing to the TUN<5:0> bits of the OSCTUNE register (Register 2-3).

The default value of the TUN<5:0> is '000000'. The value is a 6-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift, while giving no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. The operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer

(PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

The OSCTUNE register also implements the INTSRC and PLLEN bits, which control certain features of the internal oscillator block.

The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected. This is covered in greater detail in **Section 2.6.1** "**LFINTOSC**".

The PLLEN bit controls the operation of the frequency multiplier. For more details about the function of the PLLEN bit see Section 2.10 "4x Phase Lock Loop Frequency Multiplier".

#### REGISTER 2-3: OSCTUNE: OSCILLATOR TUNING REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| INTSRC | PLLEN | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7  |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7 INTSRC: Internal Oscillator Low-Frequency Source Select bit

1 = 31.25 kHz device clock derived from 16 MHz HFINTOSC source (divide-by-512 enabled)

0 = 31 kHz device clock derived directly from LFINTOSC internal oscillator

bit 6 PLLEN: Frequency Multiplier PLL bit

1 = PLL enabled (for HFINTOSC 8 MHz and 16 MHz only)

0 = PLL disabled

bit 5-0 **TUN<5:0>:** Frequency Tuning bits

011111 = Maximum frequency

011110 =

000001 =

000000 = Oscillator module is running at the factory-calibrated frequency.

111111 =

• • •

100000 = Minimum frequency

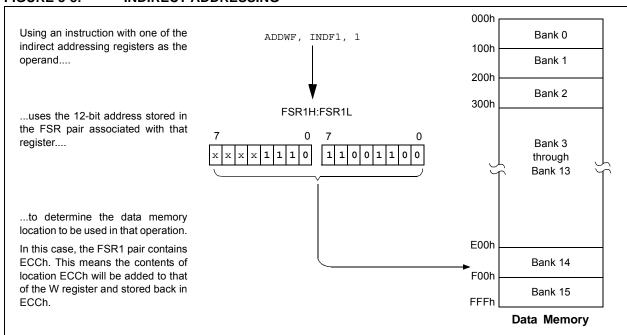

### 3.4.3.1 FSR Registers and the INDF Operand

At the core of indirect addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. Each FSR pair holds a 12-bit value, therefore the four upper bits of the FSRnH register are not used. The 12-bit FSR value can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because indirect addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

## 3.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers which cannot be directly read or written. Accessing these registers actually accesses the location to which the associated FSR register pair points, and also performs a specific action on the FSR value. They are:

- POSTDEC: accesses the location to which the FSR points, then automatically decrements the FSR by 1 afterwards

- POSTINC: accesses the location to which the FSR points, then automatically increments the FSR by 1 afterwards

- PREINC: automatically increments the FSR by 1, then uses the location to which the FSR points in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the location to which the result points in the operation.

In this context, accessing an INDF register uses the value in the associated FSR register without changing it. Similarly, accessing a PLUSW register gives the FSR value an offset by that in the W register; however, neither W nor the FSR is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR register.

#### FIGURE 3-8: INDIRECT ADDRESSING

#### REGISTER 7-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0  | U-0   |

|--------|-------|-------|-------|-------|-----|--------|-------|

| OSCFIF | C1IF  | C2IF  | EEIF  | BCLIF | _   | TMR3IF |       |

| bit 7  |       |       |       |       |     |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 OSCFIF: Oscillator Fail Interrupt Flag bit

1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by software)

0 = Device clock operating

bit 6 C1IF: Comparator C1 Interrupt Flag bit

1 = Comparator C1 output has changed (must be cleared by software)

0 = Comparator C1 output has not changed

bit 5 **C2IF:** Comparator C2 Interrupt Flag bit

1 = Comparator C2 output has changed (must be cleared by software)

0 = Comparator C2 output has not changed

bit 4 **EEIF:** Data EEPROM/Flash Write Operation Interrupt Flag bit

1 = The write operation is complete (must be cleared by software)

0 = The write operation is not complete or has not been started

bit 3 **BCLIF:** Bus Collision Interrupt Flag bit

1 = A bus collision occurred (must be cleared by software)

0 = No bus collision occurred

bit 2 Unimplemented: Read as '0'

bit 1 TMR3IF: TMR3 Overflow Interrupt Flag bit

1 = TMR3 register overflowed (must be cleared by software)

0 = TMR3 register did not overflow

bit 0 **Unimplemented:** Read as '0'

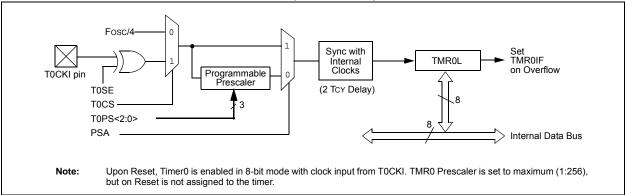

#### 9.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected with the T0CS bit of the T0CON register. In Timer mode (T0CS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 9.3** "**Prescaler**"). Timer0 incrementing is inhibited for two instruction cycles following a TMR0 register write. The user can work around this by adjusting the value written to the TMR0 register to compensate for the anticipated missing increments.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE of the T0CON register; clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements (see Table 26-17) to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

### 9.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0 which is neither directly readable nor writable (refer to Figure 9-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without the need to verify that the read of the high and low byte were valid. Invalid reads could otherwise occur due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. Writing to TMR0H does not directly affect Timer0. Instead, the high byte of Timer0 is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### FIGURE 9-1: TIMERO BLOCK DIAGRAM (8-BIT MODE)

### 13.4.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCP pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HFINTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

### 13.4.8.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the RC\_RUN Power-Managed mode and the OSCFIF bit of the PIR2 register will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

#### 13.4.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the enhanced CCP module to reset to a state compatible with the standard CCP module.

TABLE 13-3: REGISTERS ASSOCIATED WITH ECCP1 MODULE AND TIMER1 TO TIMER3

| Name    | Bit 7                                            | Bit 6          | Bit 5          | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |  |

|---------|--------------------------------------------------|----------------|----------------|----------|----------|--------|---------|---------|----------------------------|--|

| CCPR1H  | CCPR1H Capture/Compare/PWM Register 1, High Byte |                |                |          |          |        |         |         |                            |  |

| CCPR1L  | Capture/Co                                       | mpare/PWM      | Register 1, Lo | ow Byte  |          |        |         |         | 247                        |  |

| CCP1CON | P1M1                                             | P1M0           | DC1B1          | DC1B0    | CCP1M3   | CCP1M2 | CCP1M1  | CCP1M0  | 247                        |  |

| ECCP1AS | ECCPASE                                          | ECCPAS2        | ECCPAS1        | ECCPAS0  | PSSAC1   | PSSAC0 | PSSBD1  | PSSBD0  | 247                        |  |

| INTCON  | GIE/GIEH                                         | PEIE/GIEL      | TMR0IE         | INT0IE   | RABIE    | TMR0IF | INT0IF  | RABIF   | 245                        |  |

| IPR1    | _                                                | ADIP           | RCIP           | TXIP     | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 248                        |  |

| IPR2    | OSCFIP                                           | C1IP           | C2IP           | EEIP     | BCLIP    | _      | TMR3IP  | _       | 248                        |  |

| PIE1    | _                                                | ADIE           | RCIE           | TXIE     | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 248                        |  |

| PIE2    | OSCFIE                                           | C1IE           | C2IE           | EEIE     | BCLIE    | _      | TMR3IE  | _       | 248                        |  |

| PIR1    | _                                                | ADIF           | RCIF           | TXIF     | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 248                        |  |

| PIR2    | OSCFIF                                           | C1IF           | C2IF           | EEIF     | BCLIF    | _      | TMR3IF  | _       | 248                        |  |

| PR2     | Timer2 Peri                                      | od Register    |                |          |          |        |         |         | 246                        |  |

| PWM1CON | PRSEN                                            | PDC6           | PDC5           | PDC4     | PDC3     | PDC2   | PDC1    | PDC0    | 247                        |  |

| RCON    | IPEN                                             | SBOREN         | _              | RI       | TO       | PD     | POR     | BOR     | 246                        |  |

| TMR1H   | Timer1 Reg                                       | ister, High By | rte            |          |          |        |         |         | 246                        |  |

| TMR1L   | Timer1 Reg                                       | ister, Low By  | te             |          |          |        |         |         | 246                        |  |

| TMR2    | Timer2 Reg                                       | ister          |                |          |          |        |         |         | 246                        |  |

| TMR3H   | Timer3 Reg                                       | ister, High By | rte            |          |          |        |         |         | 247                        |  |

| TMR3L   | Timer3 Register, Low Byte                        |                |                |          |          |        |         | 247     |                            |  |

| TRISC   | TRISC7                                           | TRISC6         | TRISC5         | TRISC4   | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 248                        |  |

| T1CON   | RD16                                             | T1RUN          | T1CKPS1        | T1CKPS0  | T10SCEN  | T1SYNC | TMR1CS  | TMR10N  | 246                        |  |

| T2CON   | _                                                | T2OUTPS3       | T2OUTPS2       | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 246                        |  |

| T3CON   | RD16                                             | _              | T3CKPS1        | T3CKPS0  | T3CCP1   | T3SYNC | TMR3CS  | TMR3ON  | 247                        |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during ECCP operation.

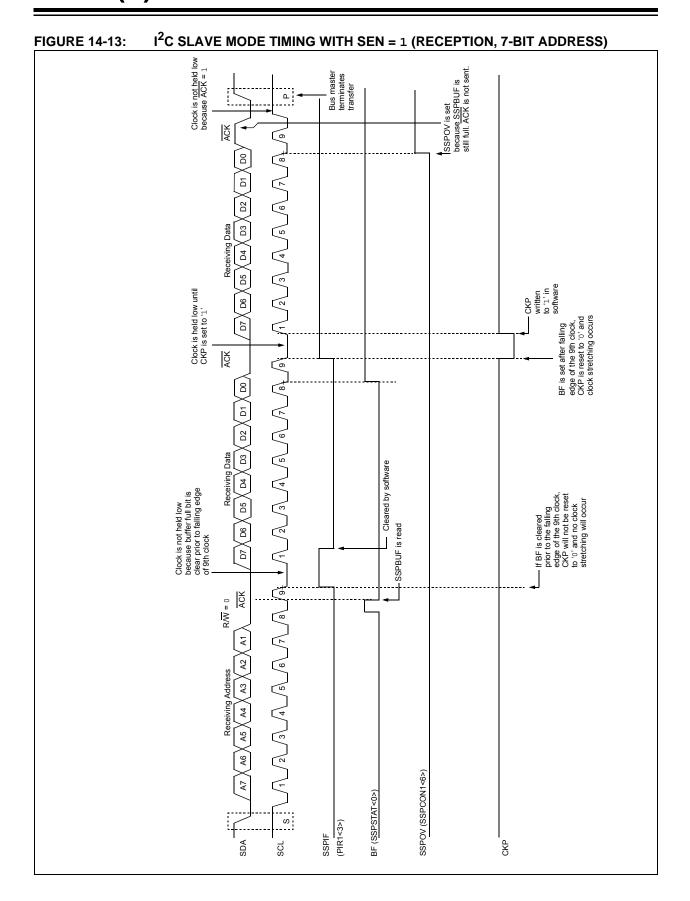

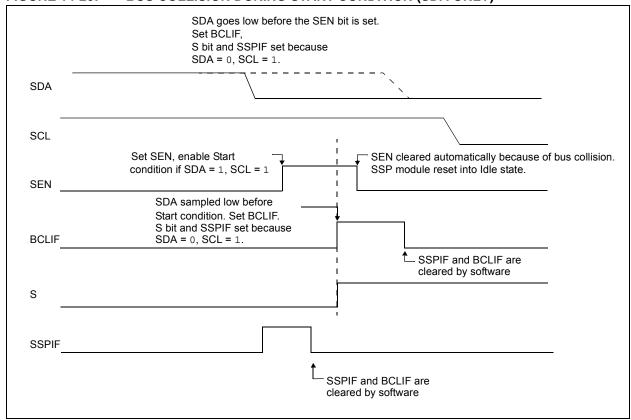

### 14.3.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- SDA or SCL are sampled low at the beginning of the Start condition (Figure 14-26).

- b) SCL is sampled low before SDA is asserted low (Figure 14-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 14-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 14-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

FIGURE 14-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

#### 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will, depending on the ACQT bits of the ADCON2 register, either immediately start the Analog-to-Digital conversion or start an acquisition delay followed by the Analog-to-Digital conversion.

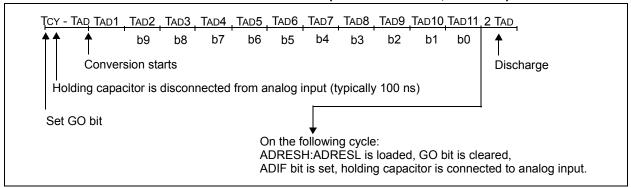

Figure 16-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into SLEEP mode before the conversion begins.

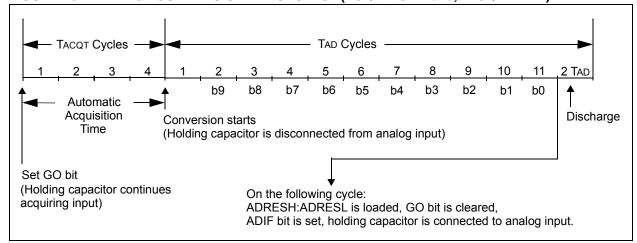

Figure 16-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT<2:0> bits are set to '010' which selects a 4 TAD acquisition time before the conversion starts.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 16.2.9 "A/D Conversion Procedure".

#### FIGURE 16-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 16-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

#### REGISTER 16-3: ADCON2: A/D CONTROL REGISTER 2

| R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| ADFM  | _   | ACQT2 | ACQT1 | ACQT0 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

bit 7 ADFM: A/D Conversion Result Format Select bit

1 = Right justified0 = Left justified

bit 6 **Unimplemented:** Read as '0'

bit 5-3

ACQT<2:0>: A/D Acquisition Time Select bits. Acquisition time is the duration that the A/D charge holding capacitor remains connected to A/D channel from the instant the GO/DONE bit is set until conversions begins.

000 = 0(1) 001 = 2 TAD 010 = 4 TAD 011 = 6 TAD 100 = 8 TAD 101 = 12 TAD 110 = 16 TAD 111 = 20 TAD

bit 2-0 ADCS<2:0>: A/D Conversion Clock Select bits

000 = Fosc/2 001 = Fosc/8 010 = Fosc/32

011 = FRC<sup>(1)</sup> (clock derived from a dedicated internal oscillator = 600 kHz nominal)

100 = Fosc/4 101 = Fosc/16 110 = Fosc/64

111 = FRC<sup>(1)</sup> (clock derived from a dedicated internal oscillator = 600 kHz nominal)

Note 1: When the A/D clock source is selected as FRC then the start of conversion is delayed by one instruction cycle after the GO/DONE bit is set to allow the SLEEP instruction to be executed.

#### REGISTER 16-4: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES9 | ADRES8 | ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 ADRES<9:2>: ADC Result Register bits

Upper 8 bits of 10-bit conversion result

#### REGISTER 16-5: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x  | R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|--------|-------|-------|-------|-------|-------|-------|

| ADRES1 | ADRES0 | _     | _     | _     | _     | _     | _     |

| bit 7  |        |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 ADRES<1:0>: ADC Result Register bits

Lower 2 bits of 10-bit conversion result

bit 5-0 Reserved: Do not use.

#### REGISTER 16-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x  | R/W-x  |

|-------|-------|-------|-------|-------|-------|--------|--------|

| _     | _     | _     | _     | _     | _     | ADRES9 | ADRES8 |

| bit 7 |       |       |       |       |       |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-2 **Reserved**: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits

Upper 2 bits of 10-bit conversion result

#### REGISTER 16-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 ADRES<7:0>: ADC Result Register bits

Lower 8 bits of 10-bit conversion result

#### 17.2 Comparator Control

Each comparator has a separate control and Configuration register: CM1CON0 for Comparator C1 and CM2CON0 for Comparator C2. In addition, Comparator C2 has a second control register, CM2CON1, for controlling the interaction with Timer1 and simultaneous reading of both comparator outputs.

The CM1CON0 and CM2CON0 registers (see Registers 17-1 and 17-2, respectively) contain the control and status bits for the following:

- Enable

- · Input selection

- · Reference selection

- · Output selection

- · Output polarity

- · Speed selection

#### 17.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 17.2.2 COMPARATOR INPUT SELECTION

The CxCH<1:0> bits of the CMxCON0 register direct one of four analog input pins to the comparator inverting input.

| Note: |        |                                          | d C12INx- p<br>priate bits n |     | •   |  |  |

|-------|--------|------------------------------------------|------------------------------|-----|-----|--|--|

|       | the    | ANSEL                                    | register                     | and | the |  |  |

|       | corre  | corresponding TRIS bits must also be set |                              |     |     |  |  |

|       | to dis | sable the ou                             | tput drivers.                |     |     |  |  |

### 17.2.3 COMPARATOR REFERENCE SELECTION

Setting the CxR bit of the CMxCON0 register directs an internal voltage reference or an analog input pin to the noninverting input of the comparator. See **Section 20.0 "Fixed Voltage Reference (FVR)"** for more information on the Internal Voltage Reference module.

### 17.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CM2CON1 register. In order to make the output available for an external connection, the following conditions must be true:

- CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- CxON bit of the CMxCON0 register must be set

- **Note 1:** The CxOE bit overrides the PORT data latch. Setting the CxON has no impact on the port override.

- 2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 17.2.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 17-1 shows the output state versus input conditions, including polarity control.

TABLE 17-1: COMPARATOR OUTPUT STATE vs. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVIN- > CxVIN+ | 0     | 0     |

| CxVIN- < CxVIN+ | 0     | 1     |

| CxVIN- > CxVIN+ | 1     | 1     |

| CxVIN- < CxVIN+ | 1     | 0     |

#### 17.2.6 COMPARATOR SPEED SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the normal speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

#### 17.3 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 26.0** "Electrical Specifications" for more details.

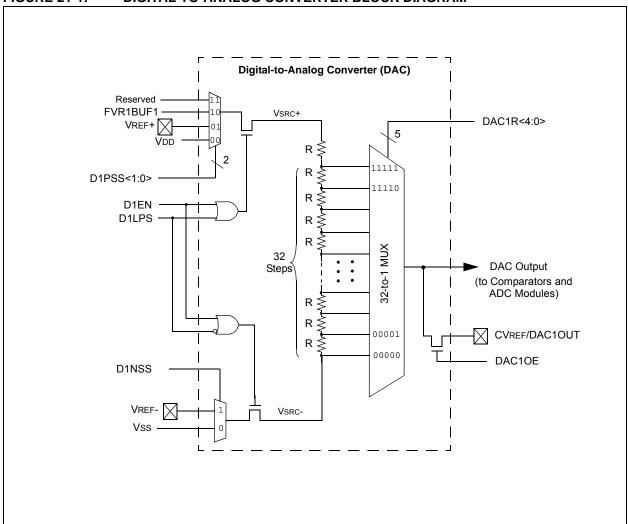

FIGURE 21-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

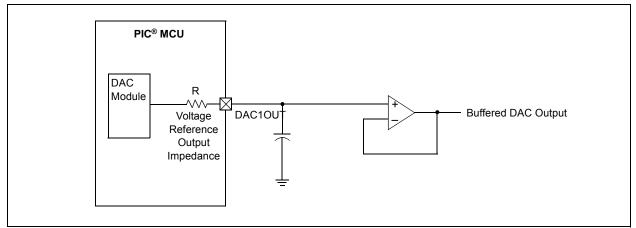

### FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

BNC Branch if Not Carry

Syntax: BNC n

Operands:  $-128 \le n \le 127$ Operation: if CARRY bit is '0'

$(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0011 nnnn nnnn

Description: If the CARRY bit is '0', then the program will branch.

The 2's complement number '2n' is added to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

Words: 1 Cycles: 1(2)

Q Cycle Activity: If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | ʻn'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BNC Jump

Before Instruction

PC = address (HERE)

After Instruction

If CARRY = 0;

PC = address (Jump)

If CARRY = 1;

PC = address (HERE + 2)

BNN Branch if Not Negative

Syntax: BNN n

Operands:  $-128 \le n \le 127$

Operation: if NEGATIVE bit is '0'

$(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0111 nnnn nnnn

Description: If the NEGATIVE bit is '0', then the program will branch.

The 2's complement number '2n' is added to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

Words: 1

Cycles: 1(2)

Q Cycle Activity: If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | ʻn'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BNN Jump

Before Instruction

PC = address (HERE)

After Instruction

If NEGATIVE = 0;

PC = address (Jump)

If NEGATIVE = 1;

PC = address (HERE + 2)

SLEEP Syntax: Operands: None Operation:  $00h \rightarrow WDT$ ,  $0 \rightarrow WDT$  postscaler,  $1 \rightarrow \overline{TO}$

$0 \rightarrow \overline{PD}$ TO, PD

Status Affected:

Encoding: 0000 0000 0000 0011 The Power-down Status bit  $(\overline{PD})$  is Description:

cleared. The Time-out Status bit (TO) is set. Watchdog Timer and its posts-

caler are cleared.

The processor is put into Sleep mode

with the oscillator stopped.

Words: Cycles:

Q Cycle Activity:

| Q1     | Q2        | Q3      | Q4    |

|--------|-----------|---------|-------|

| Decode | No        | Process | Go to |

|        | operation | Data    | Sleep |

Example: SLEEP

Before Instruction

TO = ? PD =

After Instruction

TO = 1 † PD =

† If WDT causes wake-up, this bit is cleared.

#### **SUBFWB** Subtract f from W with borrow

SUBFWB f {,d {,a}} Operands:  $0 \le f \le 255$  $d \in [0,1]$

Syntax:

Description:

$a \in [0,1]$ Operation:  $(W) - (f) - (\overline{C}) \rightarrow dest$

Status Affected: N, OV, C, DC, Z

Encoding: 01da ffff ffff 0101

> (borrow) from W (2's complement method). If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored in

Subtract register 'f' and CARRY flag

register 'f' (default). If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See **Section 24.2.3** "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset

Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example 1: SUBFWB REG, 1, 0

Before Instruction REG 3 2 1

After Instruction REG FF W 2 C Z = 0

Ν ; result is negative

Example 2: SUBFWB REG, 0, 0

2

Before Instruction REG W =

5 1 After Instruction 2 REG

3 W = C = = Ω Ν = 0

; result is positive Example 3: SUBFWB REG, 1, 0

Before Instruction

REG W 2 С 0 After Instruction

REG 0 W C Z 2 = =

; result is zero = 1

#### TABLE 26-9: I/O PORTS (CONTINUED)

| DC CHARACTERISTICS                    |  |           | Standard Operating Conditions (unless otherwise stated) |      |                               |            | otherwise stated)                                                          |

|---------------------------------------|--|-----------|---------------------------------------------------------|------|-------------------------------|------------|----------------------------------------------------------------------------|

| Param. No. Characteristic             |  | Min.      | Typ.†                                                   | Max. | Units                         | Conditions |                                                                            |

| VOL Output Low Voltage <sup>(4)</sup> |  |           |                                                         |      |                               |            |                                                                            |

| D080                                  |  | I/O ports | _                                                       | -    | Vss+0.6<br>Vss+0.6<br>Vss+0.6 | V          | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 3 mA, VDD = VDDMIN |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

- Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

- 2: Negative current is defined as current sourced by the pin.

- 3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 4: Including OSC2 in CLKOUT mode.

**TABLE 26-11: THERMAL CHARACTERISTICS**

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                        |      |       |                                                          |  |  |  |

|---------------|---------------------------------------------------------|----------------------------------------|------|-------|----------------------------------------------------------|--|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                         | Тур. | Units | Conditions                                               |  |  |  |

| TH01          | θЈА                                                     | Thermal Resistance Junction to Ambient | 62.2 | °C/W  | 20-pin PDIP package                                      |  |  |  |

|               |                                                         |                                        | 75.0 | °C/W  | 20-pin SOIC package                                      |  |  |  |

|               |                                                         |                                        | 89.3 | °C/W  | 20-pin SSOP package                                      |  |  |  |

|               |                                                         |                                        | 43.0 | °C/W  | 20-pin QFN 4x4mm package                                 |  |  |  |

| TH02          | θЈС                                                     | Thermal Resistance Junction to Case    | 27.5 | °C/W  | 20-pin PDIP package                                      |  |  |  |

|               |                                                         |                                        | 23.1 | °C/W  | 20-pin SOIC package                                      |  |  |  |

|               |                                                         |                                        | 31.1 | °C/W  | 20-pin SSOP package                                      |  |  |  |

|               |                                                         |                                        | 5.3  | °C/W  | 20-pin QFN 4x4mm package                                 |  |  |  |

| TH03          | ТЈМАХ                                                   | Maximum Junction Temperature           | 150  | °C    |                                                          |  |  |  |

| TH04          | PD                                                      | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |  |  |  |

| TH05          | PINTERNAL                                               | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |  |

| TH06          | Pı/o                                                    | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |  |

| TH07          | PDER                                                    | Derated Power                          | _    | W     | PDER = PDMAX (TJ - TA)/θJA <sup>(2)</sup>                |  |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature.

**3:** T<sub>J</sub> = Junction Temperature.

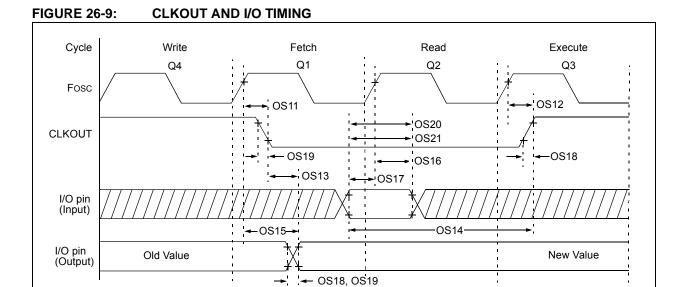

**TABLE 26-15: CLKOUT AND I/O TIMING PARAMETERS**

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                           |               |          |          |       |                                                      |  |  |

|---------------|---------------------------------------------------------|-----------------------------------------------------------|---------------|----------|----------|-------|------------------------------------------------------|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                                            | Min.          | Тур.†    | Max.     | Units | Conditions                                           |  |  |

| OS11          | TosH2cĸL                                                | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                           | _             | _        | 70       | ns    | V <sub>DD</sub> = 3.3-5.0V                           |  |  |

| OS12          | TosH2ckH                                                | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                           | _             | _        | 72       | ns    | V <sub>DD</sub> = 3.3-5.0V                           |  |  |

| OS13          | TCKL2IOV                                                | CLKOUT↓ to Port out valid <sup>(1)</sup>                  | _             | _        | 20       | ns    |                                                      |  |  |

| OS14          | TIOV2CKH                                                | Port input valid before CLKOUT <sup>(1)</sup>             | Tosc + 200 ns | _        | _        | ns    |                                                      |  |  |

| OS15          | TosH2IOV                                                | Fosc↑ (Q1 cycle) to Port out valid                        | _             | 50       | 70*      | ns    | VDD = 3.3-5.0V                                       |  |  |

| OS16          | TosH2ıol                                                | Fosc↑ (Q2 cycle) to Port input invalid (I/O in hold time) | 50            | _        | _        | ns    | VDD = 3.3-5.0V                                       |  |  |

| OS17          | TioV2osH                                                | Port input valid to Fosc↑ (Q2 cycle) (I/O in setup time)  | 20            | _        | _        | ns    |                                                      |  |  |

| OS18          | TioR                                                    | Port output rise time <sup>(2)</sup>                      |               | 40<br>15 | 72<br>32 | ns    | V <sub>DD</sub> = 1.8V<br>V <sub>DD</sub> = 3.3-5.0V |  |  |

| OS19          | TioF                                                    | Port output fall time <sup>(2)</sup>                      | _             | 28<br>15 | 55<br>30 | ns    | V <sub>DD</sub> = 1.8V<br>V <sub>DD</sub> = 3.3-5.0V |  |  |

| OS20*         | TINP                                                    | INT pin input high or low time                            | 25            | _        | _        | ns    |                                                      |  |  |

| OS21*         | TRBP                                                    | PORTB interrupt-on-change new input level time            | 25            | _        | _        | ns    |                                                      |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

<sup>2:</sup> Includes OSC2 in CLKOUT mode.

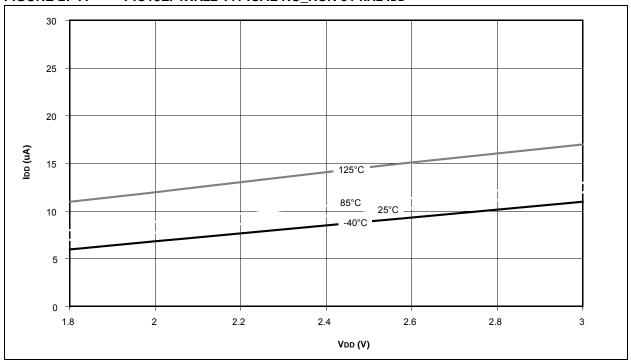

FIGURE 27-7: PIC18LF1XK22 TYPICAL RC\_RUN 31 kHz IDD

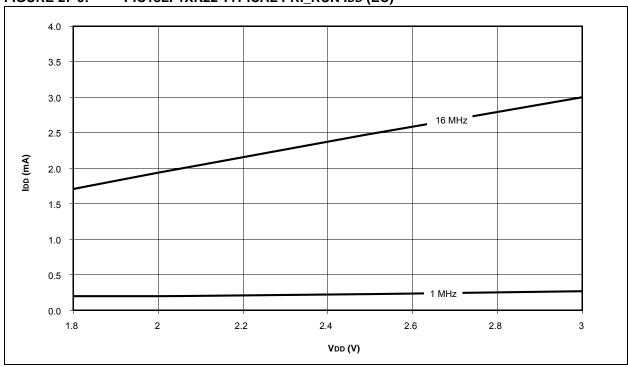

FIGURE 27-8: PIC18LF1XK22 TYPICAL RC\_RUN IDD

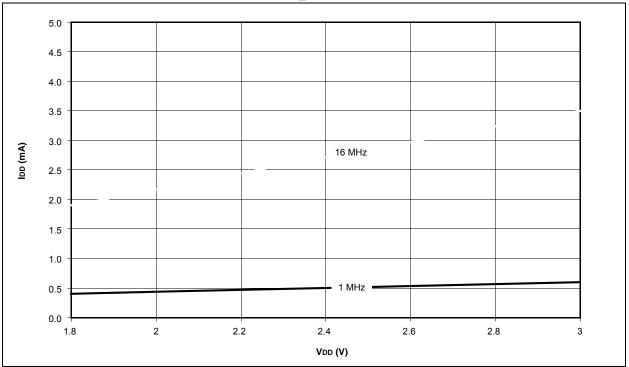

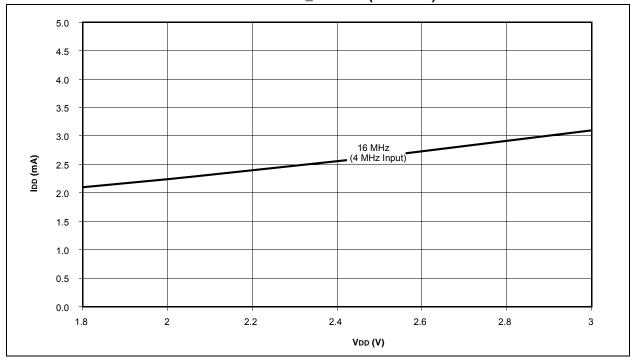

FIGURE 27-10: PIC18LF1XK22 TYPICAL PRI\_RUN IDD (HS + PLL)

**APPENDIX B: DEVICE**

**DIFFERENCES**

The differences between the devices listed in this data sheet are shown in Table .

TABLE B-1: DEVICE DIFFERENCES

| Features                      | PIC18F13K22                                             | PIC18F14K22                                             | PIC18LF13K22                                            | PIC18LF14K22                                            |

|-------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Program Memory (Bytes)        | 8192                                                    | 16384                                                   | 8192                                                    | 16384                                                   |

| Program Memory (Instructions) | 4096                                                    | 8192                                                    | 4096                                                    | 8192                                                    |

| Data Memory SRAM (bytes)      | 256                                                     | 512                                                     | 256                                                     | 512                                                     |

| Data Memory EEPROM (bytes)    | 256                                                     | 256                                                     | 256                                                     | 256                                                     |

| VDD Min <sup>(V)</sup>        | 2.3                                                     | 2.3                                                     | 1.8                                                     | 1.8                                                     |

| VDD Max <sup>(V)</sup>        | 5.5                                                     | 5.5                                                     | 3.6                                                     | 3.6                                                     |

| Packages                      | 20-pin PDIP<br>20-pin SOIC<br>20-pin SSOP<br>20-Pin QFN |