#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

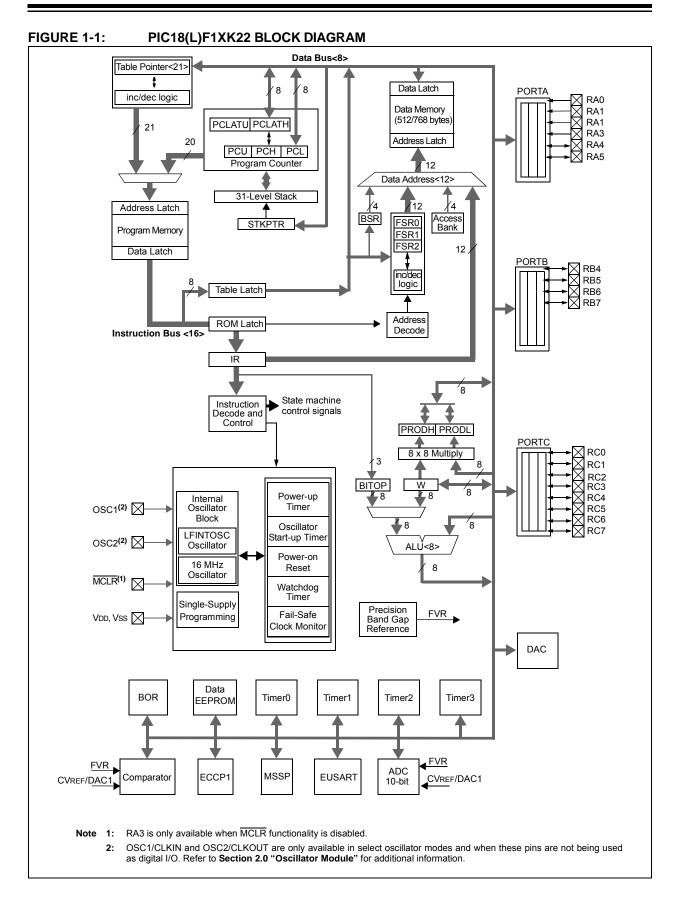

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f13k22t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 4.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 5.0 "Data EEPROM Memory"**.

#### 3.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte Program Memory (PC) space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

This family of devices contain the following:

- PIC18(L)F13K22: 8 Kbytes of Flash Memory, up to 4,096 single-word instructions

- PIC18(L)F14K22: 16 Kbytes of Flash Memory, up to 8,192 single-word instructions

PIC18 devices have two interrupt vectors and one Reset vector. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory map for PIC18(L)F1XK22 devices is shown in Figure 3-1. Memory block details are shown in Figure 3-2.

#### FIGURE 3-1: PROGRAM MEMORY MAP AND STACK FOR PIC18(L)F1XK22 DEVICES

|                                    | PC<                        | 20:0>           |                |                                               |

|------------------------------------|----------------------------|-----------------|----------------|-----------------------------------------------|

| CALL, RCALL, RET<br>RETFIE, RETLW  | URN                        | 21              |                |                                               |

|                                    | Stack Level 1              |                 |                |                                               |

|                                    |                            | •               |                |                                               |

|                                    | Stack L                    | evel 31         |                |                                               |

|                                    | Reset                      | Vector          | 0000h          |                                               |

|                                    |                            | nterrupt Vector | 0008h          |                                               |

|                                    |                            |                 |                |                                               |

|                                    | Low Priority Ir            | nterrupt Vector | 0018h          |                                               |

| On-Chip<br>Program Memory<br>1FFFh | On-Chip<br>Program Memory  |                 |                |                                               |

| 2000h                              |                            |                 |                |                                               |

| PIC18(L)F13K22                     | 3FFFh<br>4000h             |                 |                |                                               |

|                                    |                            |                 |                | ace                                           |

| Read '0'                           | PIC18(L)F14K22<br>Read '0' |                 |                | User Memory Space                             |

| Read 0                             | Read 0                     |                 | 1FFFFFh200000h | <u>,                                     </u> |

#### 4.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed one byte at a time. A write to program memory is executed on blocks of 16 or 8 bytes at a time depending on the specific device (See Table 4-1). Program memory is erased in blocks of 64 bytes at a time. The difference between the write and erase block sizes requires from 4 to 8 block writes to restore the contents of a single block erase. A Bulk Erase operation can not be issued from user code.

| TABLE 4-1: | WRITE/ERASE BLOCK SIZES |

|------------|-------------------------|

|------------|-------------------------|

| Device         | Write Block<br>Size (bytes) | Erase Block<br>Size (bytes) |  |

|----------------|-----------------------------|-----------------------------|--|

| PIC18(L)F13K22 | 8                           | 64                          |  |

| PIC18(L)F14K22 | 16                          | 64                          |  |

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

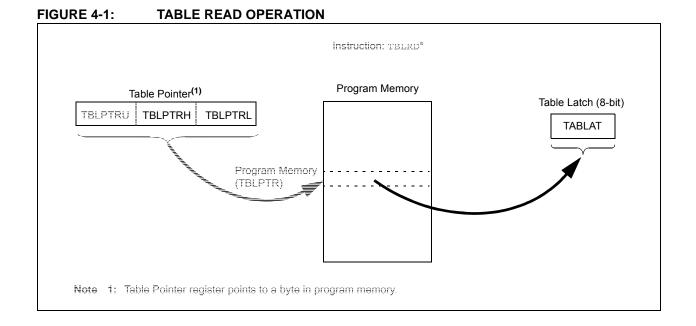

#### 4.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16-bit wide, while the data RAM space is 8-bit wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 4-1 shows the operation of a table read.

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 4.5** "Writing **to Flash Program Memory**". Figure 4-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word-aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

© 2009-2016 Microchip Technology Inc.

| <b>TABLE 8-2</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|--------------------|--------------------------------------------|

|--------------------|--------------------------------------------|

| Name    | Bit 7    | Bit 6     | Bit 5                 | Bit 4                 | Bit 3                | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values on<br>page |

|---------|----------|-----------|-----------------------|-----------------------|----------------------|--------|---------------|--------|----------------------------|

| ANSEL   | ANS7     | ANS6      | ANS5                  | ANS4                  | ANS3                 | ANS2   | ANS1          | ANS0   | 247                        |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE                | INT0IE                | RABIE                | TMR0IF | <b>INT0IF</b> | RABIF  | 244                        |

| INTCON2 | RABPU    | INTEDG0   | INTEDG1               | INTEDG2               | _                    | TMR0IP |               | RABIP  | 244                        |

| IOCA    | —        | _         | IOCA5                 | IOCA4                 | IOCA3 <sup>(2)</sup> | IOCA2  | IOCA1         | IOCA0  | 247                        |

| LATA    | _        |           | LATA5 <sup>(1)</sup>  | LATA4 <sup>(1)</sup>  | _                    | LATA2  | LATA1         | LATA0  | 247                        |

| PORTA   | —        | —         | RA5 <sup>(1)</sup>    | RA4 <sup>(1)</sup>    | RA3 <sup>(2)</sup>   | RA2    | RA1           | RA0    | 247                        |

| SLRCON  | —        | _         | _                     | _                     | —                    | SLRC   | SLRB          | SLRA   | 247                        |

| TRISA   | —        | _         | TRISA5 <sup>(1)</sup> | TRISA4 <sup>(1)</sup> | _(3)                 | TRISA2 | TRISA1        | TRISA0 | 247                        |

| WPUA    |          |           | WPUA5                 | WPUA4                 | WPUA3 <sup>(2)</sup> | WPUA2  | WPUA1         | WPUA0  | 244                        |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA<5:4> and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

2: Implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0).

**3:** Unimplemented, read as '1'.

### FIGURE 13-4: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

| P1M<  | <1:0>              | Signal                                                                    | 0 ◀          | Pulse<br>Width |                       | 1                     |

|-------|--------------------|---------------------------------------------------------------------------|--------------|----------------|-----------------------|-----------------------|

|       |                    |                                                                           | -            |                | Period                |                       |

| 00    | (Single Output)    | P1A Modulated                                                             | <br>Delay    |                | Delay <sup>(1)</sup>  | Į                     |

|       |                    | P1A Modulated                                                             |              |                |                       | ;                     |

| 10    | (Half-Bridge)      | P1B Modulated                                                             |              |                |                       | <u>\</u>              |

|       |                    | P1A Active                                                                | - :          |                |                       | <br>                  |

| 01    | (Full-Bridge,      | P1B Inactive                                                              | - ¦          |                | 1<br>1<br>1           |                       |

| 01    | Forward)           | P1C Inactive                                                              | _ ;<br>;     |                |                       |                       |

|       |                    | P1D Modulated                                                             |              |                |                       |                       |

|       |                    | P1A Inactive                                                              | - :          |                | 1<br>1                |                       |

| 11    | (Full-Bridge,      | P1B Modulated                                                             |              |                |                       |                       |

|       | Reverse)           | P1C Active                                                                | - ;          |                |                       | <br>i<br>i            |

|       |                    | P1D Inactive                                                              | _ '          |                | 1<br>1<br>1           | <u>_</u>              |

| Relat | • Pulse Width = To | c * (PR2 + 1) * (TMR2 Pre<br>DSC * (CCPR1L<7:0>:CCP<br>2 * (PWM1CON<6:0>) |              | (TMR2 Prescal  | e Value)              | ·                     |

| No    |                    |                                                                           | using the PW | M1CON registe  | er (Section 13.4.6 "P | rogrammable Dead-Band |

#### 13.4.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits of the PSTRCON register, as shown in Table 13-2.

| Note: | The associated TRIS bits must be set to      |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|

|       | output ('0') to enable the pin output driver |  |  |  |  |

|       | in order to see the PWM signal on the pin    |  |  |  |  |

While the PWM Steering mode is active, CCP1M<1:0> bits of the CCP1CON register select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 13.4.4 "Enhanced PWM Auto-shutdown mode"**. An auto-shutdown event will only affect pins that have PWM outputs enabled.

#### **REGISTER 13-4: PSTRCON: PULSE STEERING CONTROL REGISTER<sup>(1)</sup>**

| U-0   | U-0 | U-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 |

|-------|-----|-----|---------|-------|-------|-------|-------|

| —     | —   | —   | STRSYNC | STRD  | STRC  | STRB  | STRA  |

| bit 7 |     |     |         |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                             |    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| bit 4   | STRSYNC: Steering Sync bit                                                                                                                                             |    |

|         | <ul> <li>1 = Output steering update occurs on next PWM period</li> <li>0 = Output steering update occurs at the beginning of the instruction cycle boundary</li> </ul> |    |

| bit 3   | STRD: Steering Enable bit D                                                                                                                                            |    |

|         | 1 = P1D pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                 |    |

|         | 0 = P1D pin is assigned to port pin                                                                                                                                    |    |

| bit 2   | STRC: Steering Enable bit C                                                                                                                                            |    |

|         | 1 = P1C pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                 |    |

|         | 0 = P1C pin is assigned to port pin                                                                                                                                    |    |

| bit 1   | STRB: Steering Enable bit B                                                                                                                                            |    |

|         | 1 = P1B pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                 |    |

|         | 0 = P1B pin is assigned to port pin                                                                                                                                    |    |

| bit 0   | STRA: Steering Enable bit A                                                                                                                                            |    |

|         | 1 = P1A pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                 |    |

|         | 0 = P1A pin is assigned to port pin                                                                                                                                    |    |

| Noto 1: | The DWM Steering mode is available only when the CCD1CON register hits CCD1M< $3:25 - 11$                                                                              | an |

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

|                             |         |                  |       |                                    |       | •               |       |  |  |  |

|-----------------------------|---------|------------------|-------|------------------------------------|-------|-----------------|-------|--|--|--|

| R/W-0                       | R/W-0   | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |  |

| ADD7                        | ADD6    | ADD5             | ADD4  | ADD3                               | ADD2  | ADD1            | ADD0  |  |  |  |

| bit 7                       |         |                  |       |                                    |       |                 | bit 0 |  |  |  |

|                             |         |                  |       |                                    |       |                 |       |  |  |  |

| Legend:                     | Legend: |                  |       |                                    |       |                 |       |  |  |  |

| R = Readable                | bit     | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |

| -n = Value at POR '1' = Bit |         | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |  |  |  |

|                             |         |                  |       |                                    |       |                 |       |  |  |  |

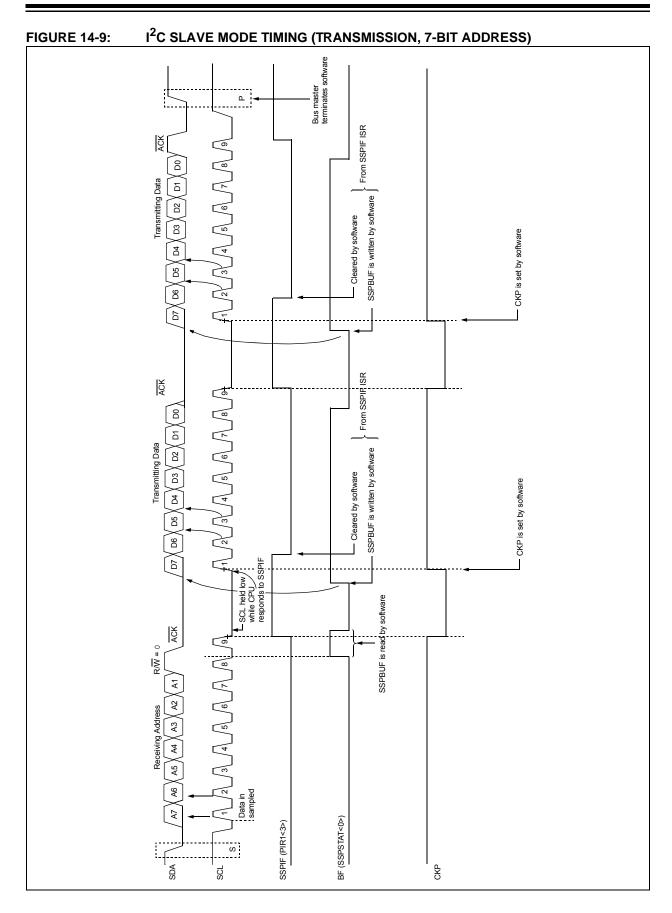

### REGISTER 14-7: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

#### Master mode:

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

#### <u>10-Bit Slave mode — Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care." Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<9:8>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care."

#### <u>10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 7-1 ADD<6:0>: 7-bit address

bit 0 Not used: Unused in this mode. Bit state is a "don't care."

| R/W-0         | R/W-0                      | R/W-0                                | R/W-0            | R/W-0           | R-0              | R-0                                 | R-x   |

|---------------|----------------------------|--------------------------------------|------------------|-----------------|------------------|-------------------------------------|-------|

| SPEN          | RX9                        | SREN                                 | CREN             | ADDEN           | FERR             | OERR                                | RX9D  |

| bit 7         |                            | ·                                    |                  | ·               | ·                | ·                                   | bit   |

| Legend:       |                            |                                      |                  |                 |                  |                                     |       |

| R = Readable  | e bit                      | W = Writable                         | e bit            | U = Unimple     | emented bit, rea | ıd as '0'                           |       |

| -n = Value at | POR                        | '1' = Bit is se                      | t                | ʻ0' = Bit is cl | eared            | x = Bit is unkr                     | nown  |

| bit 7         | SPEN: Seria                | al Port Enable b                     | bit              |                 |                  |                                     |       |

|               | •                          | ort enabled (co<br>ort disabled (he  | •                | T and TX/CK     | pins as serial p | ort pins)                           |       |

| bit 6         | <b>RX9:</b> 9-bit R        | eceive Enable                        | bit              |                 |                  |                                     |       |

|               |                            | 9-bit reception<br>8-bit reception   |                  |                 |                  |                                     |       |

| bit 5         | SREN: Sing                 | le Receive Ena                       | ble bit          |                 |                  |                                     |       |

|               | Asynchrono                 | <u>us mode</u> :                     |                  |                 |                  |                                     |       |

|               | Don't care                 |                                      |                  |                 |                  |                                     |       |

|               | -                          | <u>s mode – Mast</u>                 |                  |                 |                  |                                     |       |

|               |                            | s single receive<br>s single receive |                  |                 |                  |                                     |       |

|               |                            | eared after receive                  |                  | lete.           |                  |                                     |       |

|               |                            | s mode – Slave                       |                  |                 |                  |                                     |       |

|               | Don't care                 |                                      |                  |                 |                  |                                     |       |

| bit 4         | CREN: Cont                 | tinuous Receive                      | e Enable bit     |                 |                  |                                     |       |

|               | Asynchrono                 | <u>us mode</u> :                     |                  |                 |                  |                                     |       |

|               | 1 = Enables                |                                      |                  |                 |                  |                                     |       |

|               | 0 = Disable                |                                      |                  |                 |                  |                                     |       |

|               | Synchronou                 |                                      |                  |                 |                  |                                     |       |

|               |                            | s continuous re<br>s continuous re   |                  | DIE DIT CREN    | IS Cleared (URE  | N overrides SRI                     | EN)   |

| bit 3         | ADDEN: Ad                  | dress Detect E                       | nable bit        |                 |                  |                                     |       |

|               | -                          | <u>us mode 9-bit (</u>               |                  |                 |                  |                                     |       |

|               | 0 = Disable                |                                      | ction, all bytes |                 |                  | ouffer when RSR<br>n be used as par |       |

|               | Don't care                 |                                      |                  |                 |                  |                                     |       |

| bit 2         |                            | ning Error bit                       |                  |                 |                  |                                     |       |

|               | 1 = Framing<br>0 = No fram |                                      | updated by rea   | ading RCREG     | register and re  | ceive next valid                    | byte) |

| bit 1         | OERR: Ove                  | rrun Error bit                       |                  |                 |                  |                                     |       |

|               | 1 = Overrur<br>0 = No over | n error (can be<br>rrun error        | cleared by clea  | aring bit CREN  | 1)               |                                     |       |

| bit 0         | RX9D: Ninth                | bit of Receive                       | d Data           |                 |                  |                                     |       |

|               |                            |                                      |                  |                 |                  |                                     |       |

#### REGISTER 15-2-ROSTA: RECEIVE STATUS AND CONTROL REGISTER

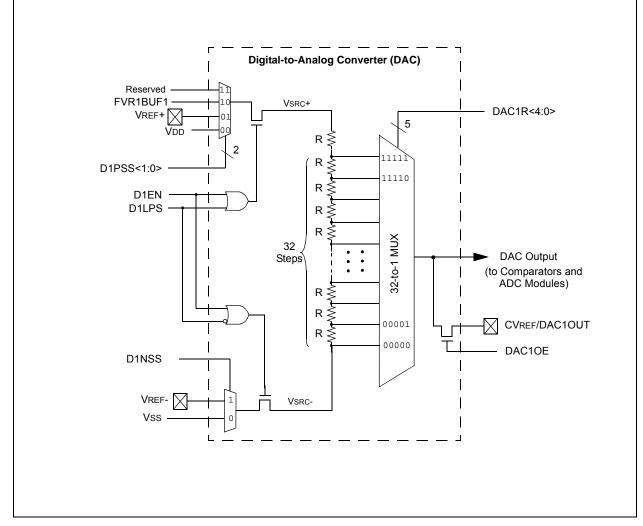

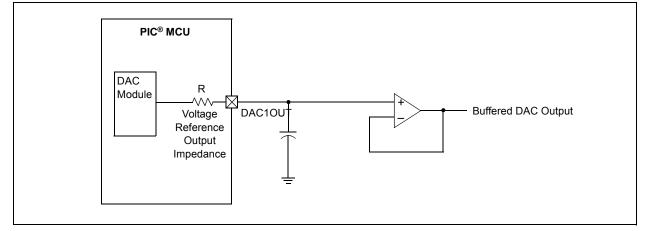

#### FIGURE 21-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

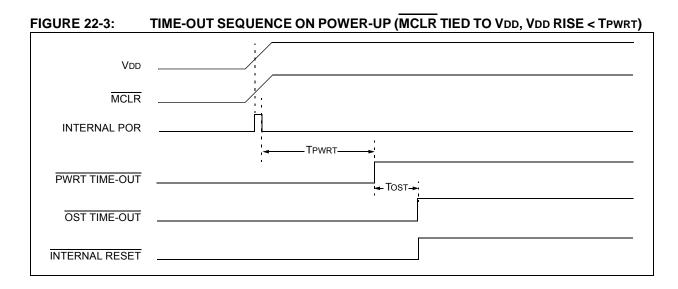

#### FIGURE 22-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

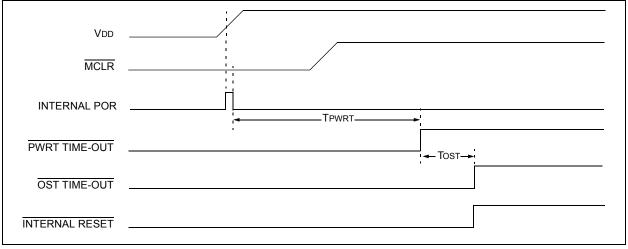

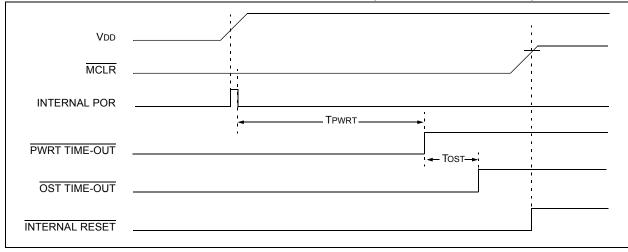

#### FIGURE 22-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

### 23.0 SPECIAL FEATURES OF THE CPU

PIC18(L)F1XK22 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- · Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 2.0 "Oscillator Module"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18(L)F1XK22 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

| BNC          | BNOV Branch if Not Overflow              |                                                                                                                                                                                                                                                                                          |               |                   |                |  |  |  |  |

|--------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|----------------|--|--|--|--|

| Synta        | ax:                                      | BNOV n                                                                                                                                                                                                                                                                                   |               |                   |                |  |  |  |  |

| Oper         | ands:                                    | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                             | 27            |                   |                |  |  |  |  |

| Oper         | ation:                                   | if OVERFL(<br>(PC) + 2 + 2                                                                                                                                                                                                                                                               |               | '0'               |                |  |  |  |  |

| Statu        | s Affected:                              | None                                                                                                                                                                                                                                                                                     | None          |                   |                |  |  |  |  |

| Enco         | ding:                                    | 1110                                                                                                                                                                                                                                                                                     | 0101          | nnnn              | nnnn           |  |  |  |  |

| Desc         | ription:                                 | If the OVERFLOW bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |               |                   |                |  |  |  |  |

| Word         | IS:                                      | 1                                                                                                                                                                                                                                                                                        |               |                   |                |  |  |  |  |

| Cycle        | es:                                      | 1(2)                                                                                                                                                                                                                                                                                     |               |                   |                |  |  |  |  |

| Q C<br>If Ju | •                                        |                                                                                                                                                                                                                                                                                          |               |                   |                |  |  |  |  |

|              | Q1                                       | Q2                                                                                                                                                                                                                                                                                       | Q3            |                   | Q4             |  |  |  |  |

|              | Decode                                   | Read literal<br>'n'                                                                                                                                                                                                                                                                      | Proce<br>Data |                   | ite to PC      |  |  |  |  |

|              | No<br>operation                          | No<br>operation                                                                                                                                                                                                                                                                          | No<br>operat  |                   | No<br>peration |  |  |  |  |

| If No        | o Jump:                                  |                                                                                                                                                                                                                                                                                          |               | -                 |                |  |  |  |  |

|              | Q1                                       | Q2                                                                                                                                                                                                                                                                                       | Q3            |                   | Q4             |  |  |  |  |

|              | Decode                                   | Read literal<br>'n'                                                                                                                                                                                                                                                                      | Proce<br>Data |                   | No<br>peration |  |  |  |  |

|              |                                          | 11                                                                                                                                                                                                                                                                                       | Data          |                   |                |  |  |  |  |

| Exan         | <u>nple</u> :                            | HERE                                                                                                                                                                                                                                                                                     | BNOV 3        | Jump              |                |  |  |  |  |

|              | Before Instruc<br>PC<br>After Instructio | = ad                                                                                                                                                                                                                                                                                     | dress (1      | IERE )            |                |  |  |  |  |

|              | If OVERI<br>PC<br>If OVERI<br>PC         | FLOW = 0;<br>= add<br>FLOW = 1;                                                                                                                                                                                                                                                          | dress (J      | Jump)<br>IERE + 2 | 2)             |  |  |  |  |

| BNZ                                                                                                                                                                                                                                                                                          | Branch if                                                                                          | Not Zer                                                 | 0               |                                            |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------|--------------------------------------------|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                      | BNZ n                                                                                              |                                                         |                 |                                            |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                    | -128 ≤ n ≤ ′                                                                                       | $-128 \le n \le 127$                                    |                 |                                            |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                   | if ZERO bit<br>(PC) + 2 +                                                                          |                                                         |                 |                                            |  |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                             | None                                                                                               |                                                         |                 |                                            |  |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                    | 1110                                                                                               | 0001                                                    | nnnn            | nnnn                                       |  |  |  |  |

| Description:<br>If the ZERO bit is '0', then the prog<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will h<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then<br>2-cycle instruction. |                                                                                                    |                                                         |                 |                                            |  |  |  |  |

| Words:                                                                                                                                                                                                                                                                                       | 1                                                                                                  |                                                         |                 |                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                              | 1(2)                                                                                               |                                                         |                 |                                            |  |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                                      | 1(2)                                                                                               |                                                         |                 |                                            |  |  |  |  |

| Q Cycle Activity:<br>If Jump:                                                                                                                                                                                                                                                                |                                                                                                    | 02                                                      |                 | 04                                         |  |  |  |  |

| Q Cycle Activity:<br>If Jump:<br>Q1                                                                                                                                                                                                                                                          | Q2                                                                                                 | Q3                                                      | 20 1            | Q4<br>Avrito to PC                         |  |  |  |  |

| Q Cycle Activity:<br>If Jump:                                                                                                                                                                                                                                                                |                                                                                                    | Q3<br>Proces<br>Data                                    |                 | Q4<br>Write to PC                          |  |  |  |  |

| Q Cycle Activity:<br>If Jump:<br>Q1                                                                                                                                                                                                                                                          | Q2<br>Read literal                                                                                 | Proces                                                  |                 |                                            |  |  |  |  |

| Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation                                                                                                                                                                                                                             | Q2<br>Read literal<br>'n'                                                                          | Proces<br>Data                                          |                 | Write to PC                                |  |  |  |  |

| Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:                                                                                                                                                                                                              | Q2<br>Read literal<br>'n'<br>No<br>operation                                                       | Proces<br>Data<br>No<br>operati                         |                 | Write to PC                                |  |  |  |  |

| Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:<br>Q1                                                                                                                                                                                                        | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2                                                 | Proces<br>Data<br>No<br>operati<br>Q3                   | on              | Write to PC<br>No<br>operation<br>Q4       |  |  |  |  |

| If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:                                                                                                                                                                                                                                   | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal                                 | Proces<br>Data<br>No<br>operati<br>Q3<br>Proces         | on              | Write to PC<br>No<br>operation<br>Q4<br>No |  |  |  |  |

| Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:<br>Q1                                                                                                                                                                                                        | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2                                                 | Proces<br>Data<br>No<br>operati<br>Q3                   | on              | Write to PC<br>No<br>operation<br>Q4       |  |  |  |  |

| Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:<br>Q1                                                                                                                                                                                                        | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal                                 | Proces<br>Data<br>No<br>operati<br>Q3<br>Proces<br>Data | on              | Write to PC<br>No<br>operation<br>Q4<br>No |  |  |  |  |

| Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:<br>Q1<br>Decode                                                                                                                                                                                              | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal<br>'n'<br>HERE<br>ction<br>= ad | Proces<br>Data<br>No<br>operati<br>Q3<br>Proces<br>Data | on<br>ss<br>ump | Write to PC<br>No<br>operation<br>Q4<br>No |  |  |  |  |

| SUBWFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Su        | Ibtract          | W from                          | f with         | Borrow      |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|---------------------------------|----------------|-------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SL        | JBWFB            | f {,d {,a                       | a}}            |             |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 ≤       | ≦ f ≤ 255        |                                 |                |             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | <b>d</b> ∈ [0,1] |                                 |                |             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | a ∈ [0,1]        |                                 |                |             |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • • •     | . ,              | $(\overline{C}) \rightarrow de$ | st             |             |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ν,        | OV, C, E         | DC, Z                           |                |             |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (         | 0101             | 10da                            | fff            | f ffff      |  |  |  |

| Encoding:       0101       10da       ffff       ffff         Description:       Subtract W and the CARRY flag<br>(borrow) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |           |                  |                                 |                |             |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1         |                  |                                 |                |             |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1         |                  |                                 |                |             |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •         |                  |                                 |                |             |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | Q2               | Q                               | 3              | Q4          |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I         | Read             | Proc                            |                | Write to    |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | reg       | gister 'f'       | Da                              | ta             | destination |  |  |  |

| Example 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | UBWFB            | REG, 1                          | L, O           |             |  |  |  |

| Before Instruct<br>REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tion<br>= | 19h              | (000                            | 1 100          | 11)         |  |  |  |

| W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | =         | 0Dh              | (000                            |                |             |  |  |  |

| C<br>After Instructio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | =         | 1                |                                 |                |             |  |  |  |

| REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | =         | 0Ch              | (000                            | 0 101          | 1)          |  |  |  |

| W<br>C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | =         | 0Dh<br>1         | (000                            | 0 110          | 1)          |  |  |  |

| Z<br>N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | =         | 0                |                                 |                |             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | =         | 0                |                                 | It is po       | sitive      |  |  |  |

| Example 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | UBWFB            | REG, 0                          | , 0            |             |  |  |  |

| Before Instruct<br>REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | =         | 1Bh              | (000                            | 1 101          | 1)          |  |  |  |

| W<br>C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | =         | 1Ah<br>0         | (000                            | 1 101          | 0)          |  |  |  |

| After Instructio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | 0                |                                 |                |             |  |  |  |

| REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | =         | 1Bh              | (000                            | 1 101          | 1)          |  |  |  |

| W<br>C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | =         | 00h<br>1         |                                 |                |             |  |  |  |

| Z<br>N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | =         | 1<br>0           | ; resu                          | lt is ze       | ro          |  |  |  |

| Example 3:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | UBWFB            | REG, 1                          | I 0            |             |  |  |  |

| Before Instruct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | IOBWI B          | KEG, 1                          | L, U           |             |  |  |  |