Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

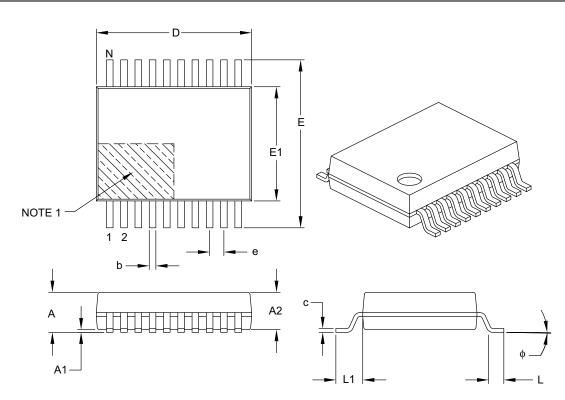

| Mounting Type              | Surface Mount                                                              |

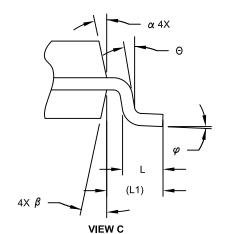

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f14k22-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

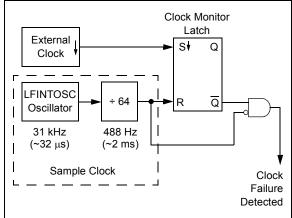

#### 2.12 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the CONFIG1H Configuration register. The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC and RC).

FIGURE 2-6: FSCM BLOCK DIAGRAM

#### 2.12.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 2-6. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

#### 2.12.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSCFIF of the PIR2 register. The OSCFIF flag will generate an interrupt if the OSCFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation. An automatic transition back to the failed clock source will not occur.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 2.12.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared by either one of the following:

- Any Reset

- · By toggling the SCS1 bit of the OSCCON register

Both of these conditions restart the OST. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device automatically switches over to the external clock source. The Fail-Safe condition need not be cleared before the OSCFIF flag is cleared.

#### 2.12.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

| File Name | Bit 7        | Bit 6                      | Bit 5          | Bit 4        | Bit 3          | Bit 2                         | Bit 1     | Bit 0   | Value on<br>POR, BOR | Details<br>on<br>page: |

|-----------|--------------|----------------------------|----------------|--------------|----------------|-------------------------------|-----------|---------|----------------------|------------------------|

| TMR0H     | Timer0 Regis | ter, High Byte             |                |              |                |                               |           |         | 0000 0000            | 246, 92                |

| TMR0L     | Timer0 Regis | ter, Low Byte              |                |              |                |                               |           |         | xxxx xxxx            | 246, 92                |

| T0CON     | TMR0ON       | T08BIT                     | TOCS           | T0SE         | PSA            | T0PS2                         | T0PS1     | T0PS0   | 1111 1111            | 246, 91                |

| OSCCON    | IDLEN        | IRCF2                      | IRCF1          | IRCF0        | OSTS           | HFIOFS                        | SCS1      | SCS0    | 0011 qq00            | 246, 17                |

| OSCCON2   | _            | _                          | _              | _            | _              | PRI_SD                        | HFIOFL    | LFIOFS  | 10x                  | 246, 18                |

| WDTCON    | _            | _                          | _              | _            | _              | _                             | _         | SWDTEN  | 0                    | 246, 260               |

| RCON      | IPEN         | SBOREN <sup>(1)</sup>      | -              | RI           | TO             | PD                            | POR       | BOR     | 0q-1 11q0            | 237,<br>246, 71        |

| TMR1H     | Timer1 Regis | ter, High Byte             |                |              |                |                               |           |         | xxxx xxxx            | 246, 94                |

| TMR1L     | Timer1 Regis | ter, Low Bytes             |                |              |                |                               |           |         | xxxx xxxx            | 246, 94                |

| T1CON     | RD16         | T1RUN                      | T1CKPS1        | T1CKPS0      | T10SCEN        | T1SYNC                        | TMR1CS    | TMR10N  | 0000 0000            | 246, 94                |

| TMR2      | Timer2 Regis | ter                        |                | •            |                |                               |           | •       | 0000 0000            | 246, 100               |

| PR2       | Timer2 Perio | d Register                 |                |              |                |                               |           |         | 1111 1111            | 246, 100               |

| T2CON     | _            | T2OUTPS3                   | T2OUTPS2       | T2OUTPS1     | T2OUTPS0       | TMR2ON                        | T2CKPS1   | T2CKPS0 | -000 0000            | 246, 100               |

| SSPBUF    | SSP Receive  | Buffer/Transn              | nit Register   |              |                |                               |           |         | xxxx xxxx            | 246,<br>128, 130       |

| SSPADD    | SSP Address  | Register in I <sup>2</sup> | C Slave Mode   | . SSP Baud R | ate Reload Reg | ister in I <sup>2</sup> C Mas | ter Mode. |         | 0000 0000            | 246, 147               |

| SSPSTAT   | SMP          | CKE                        | D/A            | Р            | S              | R/W                           | UA        | BF      | 0000 0000            | 246,<br>128, 137       |

| SSPCON1   | WCOL         | SSPOV                      | SSPEN          | СКР          | SSPM3          | SSPM2                         | SSPM1     | SSPM0   | 0000 0000            | 246,<br>128, 138       |

| SSPCON2   | GCEN         | ACKSTAT                    | ACKDT          | ACKEN        | RCEN           | PEN                           | RSEN      | SEN     | 0000 0000            | 246, 139               |

| ADRESH    | A/D Result R | egister, High E            | yte            |              |                |                               |           |         | xxxx xxxx            | 247, 197               |

| ADRESL    | A/D Result R | egister, Low B             | yte            |              |                |                               |           |         | xxxx xxxx            | 247, 197               |

| ADCON0    | —            | —                          | CHS3           | CHS2         | CHS1           | CHS0                          | GO/DONE   | ADON    | 00 0000              | 247, 203               |

| ADCON1    | _            | _                          | _              | _            | PVCFG1         | PVCFG0                        | NVCFG1    | NVCFG0  | 0000                 | 247, 204               |

| ADCON2    | ADFM         | _                          | ACQT2          | ACQT1        | ACQT0          | ADCS2                         | ADCS1     | ADCS0   | 0-00 0000            | 247, 205               |

| CCPR1H    | Capture/Com  | pare/PWM Re                | gister 1, High | Byte         |                |                               |           |         | xxxx xxxx            | 247, 126               |

| CCPR1L    | Capture/Com  | pare/PWM Re                | gister 1, Low  | Byte         |                |                               |           |         | xxxx xxxx            | 247, 126               |

| CCP1CON   | P1M1         | P1M0                       | DC1B1          | DC1B0        | CCP1M3         | CCP1M2                        | CCP1M1    | CCP1M0  | 0000 0000            | 247, 106               |

| VREFCON2  | _            | _                          | _              |              |                | DAC1R<4:0>                    |           |         | 0 0000               | 247, 236               |

| VREFCON1  | D1EN         | D1LPS                      | DAC10E         |              | D1PSS          | S<1:0>                        | —         | D1NSS   | 000- 00-0            | 247, 235               |

| VREFCON0  | FVR1EN       | FVR1ST                     | FVR1           | S<1:0>       | —              | _                             | —         | _       | 0001                 | 247, 232               |

| PSTRCON   | —            | —                          | —              | STRSYNC      | STRD           | STRC                          | STRB      | STRA    | 0 0001               | 247, 123               |

| BAUDCON   | ABDOVF       | RCIDL                      | DTRXP          | CKTXP        | BRG16          | —                             | WUE       | ABDEN   | 0100 0-00            | 247, 181               |

| PWM1CON   | PRSEN        | PDC6                       | PDC5           | PDC4         | PDC3           | PDC2                          | PDC1      | PDC0    | 0000 0000            | 247, 122               |

| ECCP1AS   | ECCPASE      | ECCPAS2                    | ECCPAS1        | ECCPAS0      | PSSAC1         | PSSAC0                        | PSSBD1    | PSSBD0  | 0000 0000            | 247, 118               |

| TMR3H     | Timer3 Regis | ter, High Byte             |                | •            | •              |                               |           | •       | xxxx xxxx            | 247, 102               |

| TMR3L     | Timer3 Regis | ter, Low Byte              |                |              |                |                               |           |         | xxxx xxxx            | 247, 102               |

| T3CON     | RD16         | _                          | T3CKPS1        | T3CKPS0      | T3CCP1         | T3SYNC                        | TMR3CS    | TMR3ON  | 0-00 0000            | 247, 102               |

TABLE 3-2: REGISTER FILE SUMMARY (PIC18(L)F1XK22) (CONTINUED)

$\label{eq:logend: second sec$

Note 1:

The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise it is disabled and reads as '0'. See Section 22.4 "Brown-out Reset (BOR)".

The RA3 bit is only available when Master Clear Reset is disabled (MCL RE Configuration bit = 0). Otherwise, RA3 reads as '0'. This is a set of the section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bit = 0). Otherwise, RA3 reads as '0'. This is a set of the section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). Otherwise, RA3 reads as '0'. This is a set of the section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). Otherwise, RA3 reads as '0'. This is a set of the section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). Otherwise, RA3 reads as '0'. This is a set of the section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). Otherwise, RA3 reads as '0'. This is a set of the section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). Otherwise, RA3 reads as '0'. This is a set of the section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits = 0). The section 2.1 when Master Clear Reset is disabled (MCL RE Configuration bits

2: The RA3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0). Otherwise, RA3 reads as '0'. This bit is read-only.

3: Unimplemented, read as '1'.

| EXAMPLE 4-3:   | WRIII         | NG TO FLASH PROGR              | AM MEMORY (CONTINUED)                   |

|----------------|---------------|--------------------------------|-----------------------------------------|

|                | DECFSZ<br>BRA | COUNTER<br>WRITE_WORD_TO_HREGS | ; loop until holding registers are full |

| PROGRAM_MEMORY |               |                                |                                         |

|                | BSF           | EECON1, EEPGD                  | ; point to Flash program memory         |

|                | BCF           | EECON1, CFGS                   | ; access Flash program memory           |

|                | BSF           | EECON1, WREN                   | ; enable write to memory                |

|                | BCF           | INTCON, GIE                    | ; disable interrupts                    |

|                | MOVLW         | 55h                            |                                         |

| Required       | MOVWF         | EECON2                         | ; write 55h                             |

| Sequence       | MOVLW         | 0AAh                           |                                         |

|                | MOVWF         | EECON2                         | ; write OAAh                            |

|                | BSF           | EECON1, WR                     | ; start program (CPU stall)             |

|                | DCFSZ         | COUNTER2                       | ; repeat for remaining write blocks     |

|                | BRA           | WRITE_BYTE_TO_HREGS            | ;                                       |

|                | BSF           | INTCON, GIE                    | ; re-enable interrupts                  |

|                | BCF           | EECON1, WREN                   | ; disable write to memory               |

|                |               |                                |                                         |

MUDITING TO FLACU BROODAM MEMORY (CONTINUED)

#### 4.5.2 WRITE VERIFY

EVANDLE 4 2.

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 4.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed <u>if needed</u>. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

#### 4.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See **Section 23.0** "**Special Features of the CPU**" for more detail.

#### 4.6 Flash Program Operation During Code Protection

See Section 23.3 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                              | Bit 6         | Bit 5       | Bit 4         | Bit 3      | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values on<br>page |

|---------|--------------------------------------------------------------------|---------------|-------------|---------------|------------|--------|--------|-------|----------------------------|

| EECON1  | EEPGD                                                              | CFGS          | _           | FREE          | WRERR      | WREN   | WR     | RD    | 247                        |

| EECON2  | EEPROM C                                                           | Control Regis | ster 2 (not | a physical r  | egister)   |        |        |       | 247                        |

| INTCON  | GIE/GIEH                                                           | PEIE/GIEL     | TMR0IE      | INT0IE        | RABIE      | TMR0IF | INT0IF | RABIF | 245                        |

| IPR2    | OSCFIP                                                             | C1IP          | C2IP        | EEIP          | BCLIP      | _      | TMR3IP | _     | 248                        |

| PIE2    | OSCFIE                                                             | C1IE          | C2IE        | EEIE          | BCLIE      | _      | TMR3IE | —     | 248                        |

| PIR2    | OSCFIF                                                             | C1IF          | C2IF        | EEIF          | BCLIF      | _      | TMR3IF | _     | 248                        |

| TABLAT  | Program M                                                          | emory Table   | Latch       |               |            |        |        |       | 245                        |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)                |               |             |               |            |        |        | 245   |                            |

| TBLPTRU | — — bit 21 Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |               |             |               |            |        |        | 245   |                            |

| TBPLTRH | Program M                                                          | emory Table   | Pointer H   | ligh Byte (TE | BLPTR<15:8 | >)     |        |       | 245                        |

TABLE 4-3:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

#### 7.9 INTx Pin Interrupts

External interrupts on the INT0, INT1 and INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the INTx pin, the corresponding flag bit, INTxF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxE. Flag bit, INTxF, must be cleared by software in the Interrupt Service Routine before reenabling the interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP and INT2IP of the INTCON3 register. There is no priority bit associated with INT0. It is always a highpriority interrupt source.

#### 7.10 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE of the INTCON register. Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP of the INTCON2 register. See **Section 9.0 "Timer0 Module"** for further details on the Timer0 module.

#### 7.11 PORTA and PORTB Interrupt-on-Change

An input change on PORTA or PORTB sets flag bit, RABIF of the INTCON register. The interrupt can be enabled/disabled by setting/clearing enable bit, RABIE of the INTCON register. Pins must also be individually enabled with the IOCA and IOCB register. Interrupt priority for PORTA and PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RABIP of the INTCON2 register.

# 7.12 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see **Section 3.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 7-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

#### EXAMPLE 7-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

| MOVWF<br>MOVFF<br>MOVFF<br>; | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR_TEMP | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere<br>; BSR_TMEP located anywhere |

|------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------|

| ; USER I                     | SR CODE                                        |                                                                                              |

| ;                            |                                                |                                                                                              |

| MOVFF                        | BSR_TEMP, BSR                                  | ; Restore BSR                                                                                |

| MOVF                         | W_TEMP, W                                      | ; Restore WREG                                                                               |

| MOVFF                        | STATUS_TEMP, STATUS                            | ; Restore STATUS                                                                             |

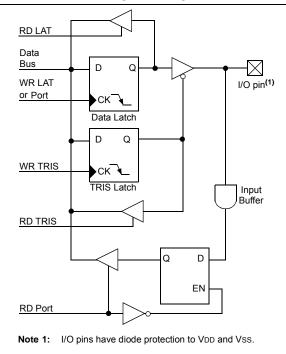

# 8.0 I/O PORTS

There are up to three ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The PORTA Data Latch (LATA register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 8-1.

# 8.1 PORTA, TRISA and LATA Registers

PORTA is a 6-bit wide, bidirectional port, with the exception of RA3, which is input-only and its TRIS bit will always read as '1'. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the PORT latch.

The PORTA Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

All of the PORTA pins are individually configurable as interrupt-on-change pins. Control bits in the IOCA register enable (when set) or disable (when clear) the interrupt function for each pin.

When set, the RABIE bit of the INTCON register enables interrupts on all pins which also have their corresponding IOCA bit set. When clear, the RABIE bit disables all interrupt-on-changes.

Only pins configured as inputs can cause this interrupt to occur (i.e., any pin configured as an output is excluded from the interrupt-on-change comparison).

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTA. The 'mismatch' outputs of the last read are OR'd together to set the PORTA Change Interrupt flag bit (RABIF) in the INTCON register.

| U-0          | U-0                       | R/W-x            | R/W-x | R-x              | R/W-x            | R/W-x           | R/W-x |

|--------------|---------------------------|------------------|-------|------------------|------------------|-----------------|-------|

| _            | —                         | RA5              | RA4   | RA3              | RA2              | RA1             | RA0   |

| bit 7        |                           |                  |       |                  |                  |                 | bit ( |

|              |                           |                  |       |                  |                  |                 |       |

| Legend:      |                           |                  |       |                  |                  |                 |       |

| R = Readal   | ole bit                   | W = Writable     | bit   | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value a | at POR                    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                           |                  |       |                  |                  |                 |       |

| bit 7-6      | Unimplemen                | ted: Read as 'o  | כי    |                  |                  |                 |       |

| bit 5-0      | <b>RA&lt;5:0&gt;</b> : PC | RTA I/O Pin bit  | (1)   |                  |                  |                 |       |

|              | 1 = Port pin is           | s > Vih          |       |                  |                  |                 |       |

|              | 0 = Port pin is           | s < Vil          |       |                  |                  |                 |       |

#### **REGISTER 8-1: PORTA: PORTA REGISTER**

**Note 1:** The RA3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0). Otherwise, RA3 reads as '0'. This bit is read-only.

#### REGISTER 8-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | U-1 | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|-----|--------|--------|--------|

| —     | —   | TRISA5 | TRISA4 |     | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |        |        |     |        |        | bit 0  |

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit <sup>(1)</sup><br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                                        |

|         | •                                                                                                                                                                 |

**Note 1:** TRISA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

| R/W-0                             | R/W-0                   | R/W-0            | R/W-0                       | R/W-0                                      | R/W-0          | R/W-0 | R/W-0        |  |  |  |

|-----------------------------------|-------------------------|------------------|-----------------------------|--------------------------------------------|----------------|-------|--------------|--|--|--|

| PRSEN                             | PDC6                    | PDC5             | PDC4                        | PDC3                                       | PDC2           | PDC1  | PDC0         |  |  |  |

| bit 7                             |                         | -<br>-           |                             | •                                          |                |       | bit          |  |  |  |

|                                   |                         |                  |                             |                                            |                |       |              |  |  |  |

| Legend:                           |                         |                  |                             |                                            |                |       |              |  |  |  |

| R = Readable bit W = Writable bit |                         |                  |                             | U = Unimplemented bit, read as '0'         |                |       |              |  |  |  |

| -n = Value at                     | POR                     | '1' = Bit is set |                             | '0' = Bit is cleared x = Bit is unknown    |                |       |              |  |  |  |

| bit 7                             | 1 = Upon au<br>away; th | e PWM restarts   | he ECCPASE<br>automatically | E bit clears auto<br>y<br>st be cleared by | ,              |       | n event goe: |  |  |  |

|                                   | •                       |                  |                             | st be cleared by                           | Soliware to re |       |              |  |  |  |

#### REGISTER 13-3: PWM1CON: ENHANCED PWM CONTROL REGISTER

bit 6-0 PDC<6:0>: PWM Delay Count bits

> PDCn = Number of Fosc/4 (4 \* Tosc) cycles between the scheduled time when a PWM signal should transition active and the actual time it transitions active

#### 14.2.6 SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

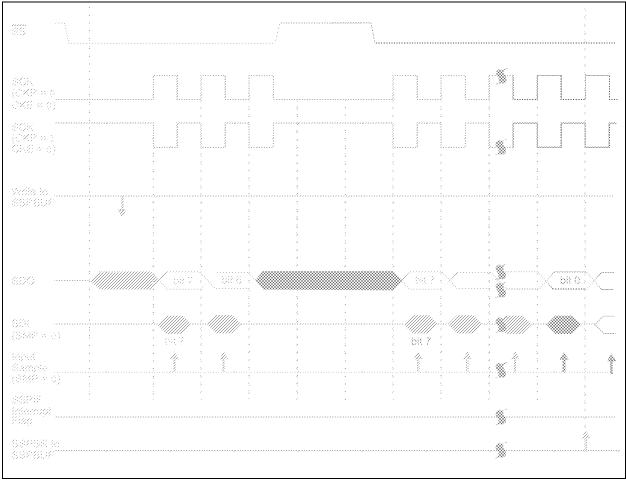

#### 14.2.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100). When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- 2: When the SPI is used in Slave mode with CKE set the SS pin control must also be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

#### FIGURE 14-4: SLAVE SYNCHRONIZATION WAVEFORM

# PIC18(L)F1XK22

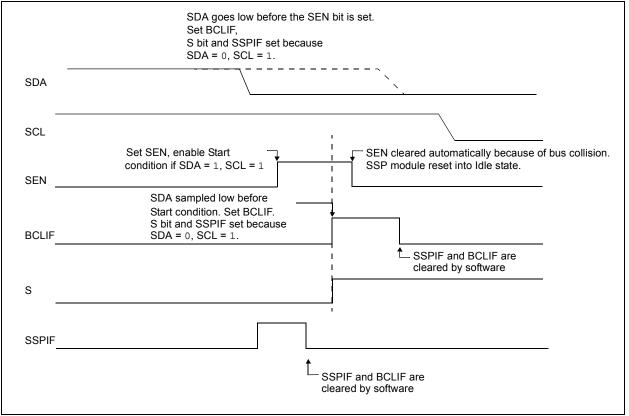

# 14.3.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 14-26).

- b) SCL is sampled low before SDA is asserted low (Figure 14-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 14-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 14-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

# PIC18(L)F1XK22

# 21.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- · ADC input channel

- DAC1OUT pin

The Digital-to-Analog Converter (DAC) can be enabled by setting the D1EN bit of the VREFCON1 register.

# 21.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DAC1R<4:0> bits of the VREFCON2 register.

The DAC output voltage is determined by the following equations:

### EQUATION 21-1: DAC OUTPUT VOLTAGE

$$Vout = \left( (VSRC+ - VSRC-) \times \frac{DACR < 4:0>}{2^5} \right) + VSRC-$$

$$VSRC+ = VDD, VREF+ \text{ or } FVR1$$

$$VSRC- = VSS \text{ or } VREF-$$

# 21.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 26.0** "**Electrical Specifications**".

#### 21.3 Low-Power Voltage State

In order for the DAC module to consume the least amount of power, one of the two voltage reference input sources to the resistor ladder must be disconnected. Either the positive voltage source, (VSRC+), or the negative voltage source, (VSRC-) can be disabled. The negative voltage source is disabled by setting the D1LPS bit in the VREFCON1 register. Clearing the D1LPS bit in the VREFCON1 register disables the positive voltage source.

#### 21.4 Output Clamped to Positive Voltage Source

The DAC output voltage can be set to VSRC+ with the least amount of power consumption by performing the following:

- Clearing the D1EN bit in the VREFCON1 register.

- Setting the D1LPS bit in the VREFCON1 register.

- Configuring the D1PSS bits to the proper positive source.

- Configuring the DAC1Rx bits to '11111' in the VREFCON2 register.

This is also the method used to output the voltage level from the FVR to an output pin. See **Section 21.6 "DAC Voltage Reference Output"** for more information.

### 21.5 Output Clamped to Negative Voltage Source

The DAC output voltage can be set to VSRC- with the least amount of power consumption by performing the following:

- Clearing the D1EN bit in the VREFCON1 register.

- Clearing the DAC1R bit in the VREFCON1 register.

- Configuring the D1PSS bits to the proper negative source.

- Configuring the DAC1Rx bits to '00000' in the VREFCON2 register.

This allows the comparator to detect a zero-crossing while not consuming additional current through the DAC module.

# 21.6 DAC Voltage Reference Output

The DAC can be output to the DAC1OUT (CVREF) pin by setting the DAC1OE bit of the VREFCON1 register to '1'. Selecting the DAC reference voltage for output on the DAC1OUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DAC1OUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DAC1OUT. Figure 21-2 shows an example buffering technique.

| Register | Address | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |

|----------|---------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|--|

| ADRESH   | FC4h    | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |

| ADRESL   | FC3h    | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |

| ADCON0   | FC2h    | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |  |

| ADCON1   | FC1h    | 0000                               | 0000                                                             | uuuu                            |  |  |

| ADCON2   | FC0h    | 0-00 0000                          | 0-00 0000                                                        | u-uu uuuu                       |  |  |

| CCPR1H   | FBFh    | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |

| CCPR1L   | FBEh    | xxxx xxxx                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |

| CCP1CON  | FBDh    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| VREFCON2 | FBCh    | 0 0000                             | 0 0000                                                           | u uuuu                          |  |  |

| VREFCON1 | FBBh    | 000-00-0                           | 000- 00-0                                                        | uuu- uu-u                       |  |  |

| VREFCON0 | FBAh    | 0001                               | 0001                                                             | uuuu                            |  |  |

| PSTRCON  | FB9h    | 0 0001                             | 0 0001                                                           | u uuuu                          |  |  |

| BAUDCON  | FB8h    | 0100 0-00                          | 0100 0-00                                                        | uuuu u-uu                       |  |  |

| PWM1CON  | FB7h    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| ECCP1AS  | FB6h    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| TMR3H    | FB3h    | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |

| TMR3L    | FB2h    | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |  |

| T3CON    | FB1h    | 0-00 0000                          | u-uu uuuu                                                        | u-uu uuuu                       |  |  |

| SPBRGH   | FB0h    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| SPBRG    | FAFh    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| RCREG    | FAEh    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| TXREG    | FADh    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| TXSTA    | FACh    | 0000 0010                          | 0000 0010                                                        | uuuu uuuu                       |  |  |

| RCSTA    | FABh    | 0000 000x                          | x000 0000x                                                       | uuuu uuuu                       |  |  |

| EEADR    | FAAh    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| EEDATA   | FA8h    | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |  |

| EECON2   | FA7h    | 0000 0000                          | 0000 0000                                                        | 0000 0000                       |  |  |

| EECON1   | FA6h    | xx-0 x000                          | uu-0 u000                                                        | uu-0 u000                       |  |  |

#### TABLE 22-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 22-3 for Reset value for specific condition.

# PIC18(L)F1XK22

| RRM              | RNCF Rotate Right f (No Carry)                   |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |            |     |   |                       |  |

|------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|---|-----------------------|--|

| Synt             | ax:                                              | RF                                                                                              | RNCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f { | ,d {,a}}   |     |   |                       |  |

| Ope              | rands:                                           | d e                                                                                             | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |            |     |   |                       |  |

| Ope              | ration:                                          | •                                                                                               | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow dest < 7 >$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |            |     |   |                       |  |

| Statu            | us Affected:                                     | N,                                                                                              | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |            |     |   |                       |  |

| Enco             | oding:                                           |                                                                                                 | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 00da       | fff | f | ffff                  |  |

| Desc             | cription:                                        | on<br>is  <br>pla<br>If 'i<br>sei<br>is '<br>pe<br>If 'i<br>sei<br>in<br>mo<br><b>Se</b><br>Bit | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected, overriding the BSR value. If 'a'<br>is '1', then the bank will be selected as<br>per the BSR value (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |     |            |     |   |                       |  |

| 14/              |                                                  |                                                                                                 | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |            |     |   | <b></b>               |  |

| Word             |                                                  | 1<br>1                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |            |     |   |                       |  |

| Cycl             | es.<br>Sycle Activity:                           | I                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |            |     |   |                       |  |

| QU               | Q1                                               |                                                                                                 | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | Q3         |     |   | Q4                    |  |

|                  | Decode                                           |                                                                                                 | Read<br>lister 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | Proc       | ess | - | Vrite to<br>stination |  |

| <u>Exar</u>      | <u>mple 1</u> :                                  | RR                                                                                              | NCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RI  | EG, 1      | , 0 |   |                       |  |

|                  | Before Instruc<br>REG<br>After Instructio<br>REG | =                                                                                               | 1101<br>1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | .11<br>)11 |     |   |                       |  |

| Example 2: RRNCF |                                                  |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | EG, 0      | , 0 |   |                       |  |

|                  | Before Instruc                                   | ruction                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |            |     |   |                       |  |

|                  | W                                                | =                                                                                               | ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |            |     |   |                       |  |

|                  | REG<br>After Instructio                          | =<br>on                                                                                         | 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 01  | .11        |     |   |                       |  |

|                  | W                                                | =                                                                                               | 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |            |     |   |                       |  |

|                  | REG                                              | =                                                                                               | 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 01  | .11        |     |   |                       |  |

| SETF                     | Set f                                                                                                                                                                             |                                                                                                                                     |                                                                                                          |                                                                                         |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| Syntax:                  | SETF f{                                                                                                                                                                           | ,a}                                                                                                                                 |                                                                                                          |                                                                                         |  |  |  |

| Operands:                | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                          | $\begin{array}{l} 0 \leq f \leq 255 \\ a  \in  [0,1] \end{array}$                                                                   |                                                                                                          |                                                                                         |  |  |  |

| Operation:               | $FFh\tof$                                                                                                                                                                         | $FFh \rightarrow f$                                                                                                                 |                                                                                                          |                                                                                         |  |  |  |

| Status Affected:         | None                                                                                                                                                                              | None                                                                                                                                |                                                                                                          |                                                                                         |  |  |  |

| Encoding:                | 0110                                                                                                                                                                              | 100a                                                                                                                                | ffff                                                                                                     | ffff                                                                                    |  |  |  |

| Description:             | The conter<br>are set to I<br>If 'a' is '0',<br>If 'a' is '1',<br>GPR bank<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode whe<br>Section 24<br>Bit-Orient<br>Literal Off | Fh.<br>the Access<br>the BSR i<br>(default).<br>and the e><br>oled, this in<br>Literal Of<br>never f ≤ 9<br>4.2.3 "Byt<br>ed Instru | es Bank is<br>s used to<br>attended ir<br>nstruction<br>fset Addr<br>95 (5Fh).<br>te-Orient<br>ctions in | selected.<br>select the<br>astruction<br>operates<br>essing<br>See<br>ed and<br>Indexed |  |  |  |

| Words:                   | 1                                                                                                                                                                                 |                                                                                                                                     |                                                                                                          |                                                                                         |  |  |  |

| Cycles:                  | 1                                                                                                                                                                                 |                                                                                                                                     |                                                                                                          |                                                                                         |  |  |  |

| Q Cycle Activity         | :                                                                                                                                                                                 |                                                                                                                                     |                                                                                                          |                                                                                         |  |  |  |

| Q1                       | Q2                                                                                                                                                                                | Q3                                                                                                                                  |                                                                                                          | Q4                                                                                      |  |  |  |

| Decode                   | Read<br>register 'f'                                                                                                                                                              | Proce<br>Data                                                                                                                       |                                                                                                          | Write<br>egister 'f'                                                                    |  |  |  |

| Example:<br>Before Instr | SETF                                                                                                                                                                              | REG                                                                                                                                 | , 1                                                                                                      |                                                                                         |  |  |  |

| Before Instruction |   |     |  |

|--------------------|---|-----|--|

| REG                | = | 5Ah |  |

| After Instruction  |   |     |  |

| REG                | = | FFh |  |

| SUBFSR                                                                                       | Subtract             | Subtract Literal from FSR |      |                         |  |  |  |

|----------------------------------------------------------------------------------------------|----------------------|---------------------------|------|-------------------------|--|--|--|

| Syntax:                                                                                      | SUBFSR               | f, k                      |      |                         |  |  |  |

| Operands:                                                                                    | $0 \le k \le 63$     |                           |      |                         |  |  |  |

|                                                                                              | f ∈ [ 0, 1,          | f ∈ [ 0, 1, 2 ]           |      |                         |  |  |  |

| Operation:                                                                                   | FSR(f) – k           | $s \rightarrow FSRf$      |      |                         |  |  |  |

| Status Affected:                                                                             | None                 |                           |      |                         |  |  |  |

| Encoding:                                                                                    | 1110                 | 1001                      | ffkk | kkkk                    |  |  |  |

| Description: The 6-bit literal 'k' is subtracted from the contents of the FSR specified 'f'. |                      |                           |      |                         |  |  |  |

| Words:                                                                                       | 1                    |                           |      |                         |  |  |  |

| Cycles:                                                                                      | 1                    |                           |      |                         |  |  |  |

| Q Cycle Activity:                                                                            |                      |                           |      |                         |  |  |  |

| Q1                                                                                           | Q2                   | Q3                        |      | Q4                      |  |  |  |

| Decode                                                                                       | Read<br>register 'f' | Proce<br>Data             |      | Write to<br>destination |  |  |  |

| Example: SUBFSR 2, 23h                                                                       |                      |                           |      |                         |  |  |  |

Example: Before Instruction

| Delote institu |     |       |

|----------------|-----|-------|

| FSR2           | =   | 03FFh |

| After Instruct | ion |       |

| FSR2           | =   | 03DCh |

| Syntax                    | :                  | SUE                            | BULNK                            | k                |            |                                    |       |                             |

|---------------------------|--------------------|--------------------------------|----------------------------------|------------------|------------|------------------------------------|-------|-----------------------------|

| Operar                    | nds:               | $0 \leq l$                     | <b>∢</b> ≤ 63                    |                  |            |                                    |       |                             |

| Operat                    | tion:              | FSR                            | 2 – k –                          | → FSF            | <b>R</b> 2 |                                    |       |                             |

|                           |                    | (TOS                           | $S) \rightarrow P$               | С                |            |                                    |       |                             |

| Status                    | Affected:          | Non                            | e                                |                  |            |                                    |       |                             |