Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

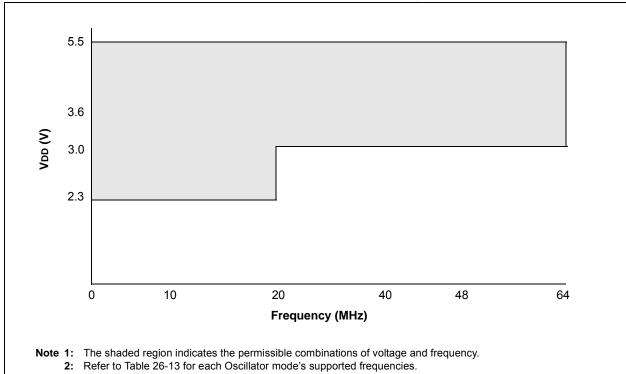

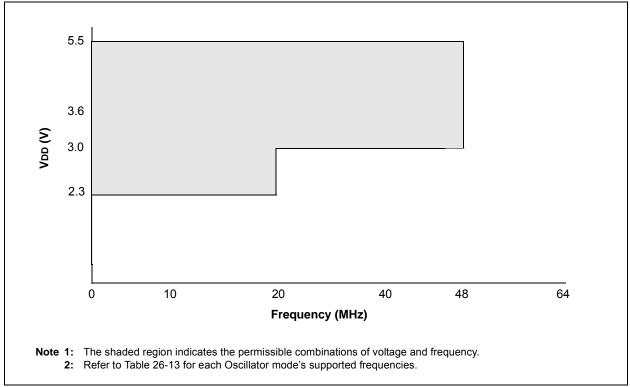

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

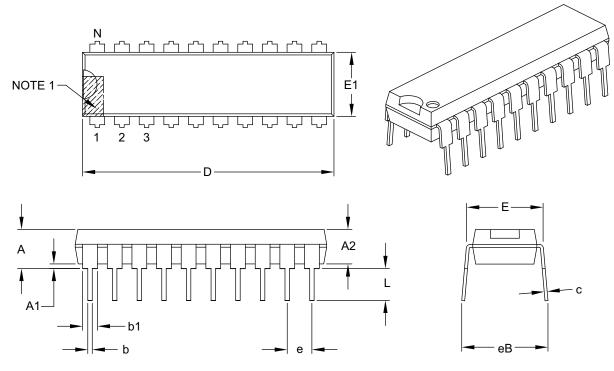

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f14k22-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.1.2.4 Stack Overflow and Underflow Resets

Device Resets on Stack Overflow and Stack Underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKOVF or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKOVF or STKUNF bit but not cause a device Reset. The STKOVF or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 3.1.3 FAST REGISTER STACK

A fast register stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high priority interrupts are enabled, the stack registers cannot be used reliably to return from low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten. In these cases, users must save the key registers by software during a low priority interrupt.

If interrupt priority is not used, all interrupts may use the fast register stack for returns from interrupt. If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the fast register stack. A RETURN, FAST instruction is then executed to restore these registers from the fast register stack.

Example 3-1 shows a source code example that uses the fast register stack during a subroutine call and return.

#### EXAMPLE 3-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR       |

|-----------------|--------------------------|

|                 | ;SAVED IN FAST REGISTER  |

|                 | ; STACK                  |

| •               |                          |

| •               |                          |

|                 |                          |

| SUB1 •          |                          |

| •               |                          |

| RETURN, FAST    | ;RESTORE VALUES SAVED    |

|                 | ; IN FAST REGISTER STACK |

|                 |                          |

# 3.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 3.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 3-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 3-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, W |

|-------|-------|-----------|

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       |       |           |

|       |       |           |

|       |       |           |

|       |       |           |

#### 3.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 4.1 "Table Reads and Table Writes".

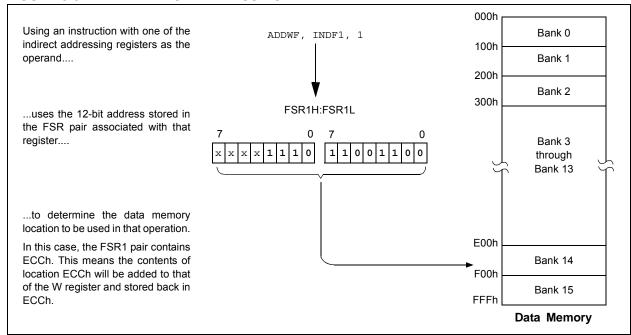

#### 3.4.3.1 FSR Registers and the INDF Operand

At the core of indirect addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. Each FSR pair holds a 12-bit value, therefore the four upper bits of the FSRnH register are not used. The 12-bit FSR value can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because indirect addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

#### 3.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers which cannot be directly read or written. Accessing these registers actually accesses the location to which the associated FSR register pair points, and also performs a specific action on the FSR value. They are:

- POSTDEC: accesses the location to which the FSR points, then automatically decrements the FSR by 1 afterwards

- POSTINC: accesses the location to which the FSR points, then automatically increments the FSR by 1 afterwards

- PREINC: automatically increments the FSR by 1, then uses the location to which the FSR points in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the location to which the result points in the operation.

In this context, accessing an INDF register uses the value in the associated FSR register without changing it. Similarly, accessing a PLUSW register gives the FSR value an offset by that in the W register; however, neither W nor the FSR is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR register.

#### FIGURE 3-8: INDIRECT ADDRESSING

| R/W-x      | K R/W-x              | U-0                                 | R/W-0           | R/W-x                         | R/W-0           | R/S-0                                  | R/S-0          |

|------------|----------------------|-------------------------------------|-----------------|-------------------------------|-----------------|----------------------------------------|----------------|

| EEPGI      | D CFGS               | —                                   | FREE            | WRERR                         | WREN            | WR                                     | RD             |

| bit 7      |                      |                                     |                 |                               |                 |                                        | bit 0          |

|            |                      |                                     |                 |                               |                 |                                        |                |

| Legend:    |                      |                                     |                 |                               |                 |                                        |                |

| R = Read   |                      | W = Writable                        |                 |                               |                 |                                        |                |

|            | n be set by software |                                     |                 | -                             | nented bit, rea |                                        |                |

| -n = Value | e at POR             | '1' = Bit is set                    |                 | '0' = Bit is cle              | ared            | x = Bit is unkr                        | IOWN           |

| bit 7      | <b>EEPGD:</b> Flas   | h Program or [                      | Data EEPROM     | 1 Memory Selec                | ct bit          |                                        |                |

|            |                      | lash program r                      |                 | 2                             |                 |                                        |                |

|            | 0 = Access d         | ata EEPROM                          | memory          |                               |                 |                                        |                |

| bit 6      | CFGS: Flash          | Program/Data                        | EEPROM or       | Configuration S               | elect bit       |                                        |                |

|            |                      | onfiguration re                     |                 | 214                           |                 |                                        |                |

|            |                      | lash program o                      |                 |                               |                 |                                        |                |

| bit 5      | •                    | ted: Read as '                      |                 | .,                            |                 |                                        |                |

| bit 4      |                      | Row (Block) E                       |                 |                               |                 |                                        |                |

|            |                      | e program men                       |                 |                               | PIR on the ne   | ext WR comman                          | IC             |

|            | 0 = Perform  v       |                                     |                 |                               |                 |                                        |                |

| bit 3      | WRERR: Flas          | sh Program/Da                       | ta EEPROM B     | Error Flag bit <sup>(1)</sup> |                 |                                        |                |

|            |                      |                                     |                 |                               | et during self- | timed programn                         | ning in normal |

|            |                      | , or an improp                      |                 | pt)                           |                 |                                        |                |

|            | 0 = 1 he write       | operation con                       | npleted         |                               |                 |                                        |                |

| bit 2      |                      | Program/Data                        |                 |                               |                 |                                        |                |

|            |                      |                                     |                 |                               |                 |                                        |                |

| 1.11.4     |                      | -                                   | lasn program    | data EEPROM                   |                 |                                        |                |

| bit 1      | WR: Write Co         |                                     | 1 orooo/write a | volo or o progra              |                 | ana avala ar writ                      |                |

|            |                      |                                     |                 |                               |                 | ase cycle or writ<br>e write is comple |                |

|            |                      |                                     |                 | ed) by software               |                 |                                        | 010.           |

|            | 0 = Write cyc        | le to the EEPR                      | ROM is comple   | ete                           |                 |                                        |                |

| bit 0      | RD: Read Co          | ntrol bit                           |                 |                               |                 |                                        |                |

|            |                      |                                     |                 |                               |                 | hardware. The R                        |                |

|            | •                    | ot cleared) by s<br>initiate an EEF |                 | it cannot be set              | when EEPGD      | = 1 or CFGS =                          | 1.)            |

| Note 1:    | When a WRERR c       | occurs, the FF                      | PGD and CFG     | S bits are not c              | leared. This a  | llows tracing of                       | the            |

|            | error condition.     | ,                                   |                 |                               |                 |                                        |                |

#### REGISTER 4-1: EECON1: DATA EEPROM CONTROL 1 REGISTER

## 5.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, which is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Four SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- EECON1

- EECON2

- EEDATA

- EEADR

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADR register holds the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer; it will vary with voltage and temperature as well as from chip-to-chip. Please refer to parameter US122 (Table 26-24) for exact limits.

#### 5.1 EEADR Register

The EEADR register is used to address the data EEPROM for read and write operations. The 8-bit range of the register can address a memory range of 256 bytes (00h to FFh).

#### 5.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 5-1) is the control register for data and program memory access. Control bit EEPGD determines if the access will be to program or data EEPROM memory. When the EEPGD bit is clear, operations will access the data EEPROM memory. When the EEPGD bit is set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When the CFGS bit is set, subsequent operations access Configuration registers. When the CFGS bit is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR        |

|-------|-------------------------------------------|

|       | may read as '1'. This can indicate that a |

|       | write operation was prematurely           |

|       | terminated by a Reset, or a write         |

|       | operation was attempted improperly.       |

The WR control bit initiates write operations. The bit can be set but not cleared by software. It is cleared only by hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit of the PIR2 register is set when the write is complete. It must be cleared by software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 4.1 "Table Reads and Table Writes"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

### 7.6 **PIE Registers**

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1 and PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 7-6: PIE1: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 1

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|-------|--------|--------|--------|

| —     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |       |       |       |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                 |

|-------|------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter Interrupt Enable bit                   |

|       | 1 = Enables the A/D interrupt                              |

|       | 0 = Disables the A/D interrupt                             |

| bit 5 | RCIE: EUSART Receive Interrupt Enable bit                  |

|       | <ol> <li>Enables the EUSART receive interrupt</li> </ol>   |

|       | 0 = Disables the EUSART receive interrupt                  |

| bit 4 | TXIE: EUSART Transmit Interrupt Enable bit                 |

|       | 1 = Enables the EUSART transmit interrupt                  |

|       | 0 = Disables the EUSART transmit interrupt                 |

| bit 3 | SSPIE: Master Synchronous Serial Port Interrupt Enable bit |

|       | 1 = Enables the MSSP interrupt                             |

|       | 0 = Disables the MSSP interrupt                            |

| bit 2 | CCP1IE: CCP1 Interrupt Enable bit                          |

|       | 1 = Enables the CCP1 interrupt                             |

|       | 0 = Disables the CCP1 interrupt                            |

| bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit             |

|       | 1 = Enables the TMR2 to PR2 match interrupt                |

|       | 0 = Disables the TMR2 to PR2 match interrupt               |

| bit 0 | TMR1IE: TMR1 Overflow Interrupt Enable bit                 |

|       | 1 = Enables the TMR1 overflow interrupt                    |

|       | 0 = Disables the TMR1 overflow interrupt                   |

|       |                                                            |

### 12.0 TIMER3 MODULE

The Timer3 module timer/counter incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- · Interrupt-on-overflow

- · Module Reset on CCP Special Event Trigger

A simplified block diagram of the Timer3 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The Timer3 module is controlled through the T3CON register (Register 12-1). It also selects the clock source options for the CCP modules (see **Section 13.1.1** "**CCP Module and Timer Resources**" for more information).

#### REGISTER 12-1: T3CON: TIMER3 CONTROL REGISTER

| Legend: |     |         |         |        |        |        |        |

|---------|-----|---------|---------|--------|--------|--------|--------|

| bit 7   |     |         |         |        |        |        | bit 0  |

| RD16    |     | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| R/W-0   | U-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>RD16:</b> 16-bit Read/Write Mode Enable bit<br>1 = Enables register read/write of Timer3 in one 16-bit operation<br>0 = Enables register read/write of Timer3 in two 8-bit operations                                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 5-4 | T3CKPS<1:0>: Timer3 Input Clock Prescale Select bits                                                                                                                                                                                                                                                                                                               |

|         | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                                                                                                                                                                           |

| bit 3   | T3CCP1: Timer3 and Timer1 to CCP1 Enable bits                                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>1 = Timer3 is the clock source for compare/capture of ECCP1</li> <li>0 = Timer1 is the clock source for compare/capture of ECCP1</li> </ul>                                                                                                                                                                                                               |

| bit 2   | T3SYNC: Timer3 External Clock Input Synchronization Control bit         (Not usable if the device clock comes from Timer1/Timer3.)         When TMR3CS = 1:         1 = Do not synchronize external clock input         0 = Synchronize external clock input         When TMR3CS = 0:         This bit is ignored. Timer3 uses the internal clock when TMR3CS = 0. |

| bit 1   | <ul> <li>TMR3CS: Timer3 Clock Source Select bit</li> <li>1 = External clock input from Timer1 oscillator or T13CKI (on the rising edge after the first falling edge)</li> <li>0 = Internal clock (Fosc/4)</li> </ul>                                                                                                                                               |

| bit 0   | TMR3ON: Timer3 On bit<br>1 = Enables Timer3<br>0 = Stops Timer3                                                                                                                                                                                                                                                                                                    |

#### 14.3.2 OPERATION

The MSSP module functions are enabled by setting SSPEN bit of the SSPCON1 register.

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits of the SSPCON1 register allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = (Fosc/(4\*(SSPADD + 1))

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRIS bits

Note: To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 14.3.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs. The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge  $(\overline{ACK})$ pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this  $\overline{ACK}$  pulse:

- The Buffer Full bit, BF bit of the SSPSTAT register, is set before the transfer is received.

- The overflow bit, SSPOV bit of the SSPCON1 register, is set before the transfer is received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in **Section 26.0 "Electrical Specifications"**.

#### 14.3.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the eight bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- MSSP Interrupt Flag bit, SSPIF of the PIR1 register, is set (interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W of the SSPSTAT register must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and UA of the SSPSTAT register are set).

- 2. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 3. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- Receive second (low) byte of address (bits SSPIF, BF and UA are set). If the address matches then the SCL is held until the next step. Otherwise the SCL line is not held.

- 5. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 6. Update the SSPADD register with the first (high) byte of address. (This will clear bit UA and release a held SCL line.)

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address with R/W bit set (bits SSPIF, BF, R/W are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 10. Load SSPBUF with byte the slave is to transmit, sets the BF bit.

- 11. Set the CKP bit to release SCL.

#### 15.1.2.4 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting the following bits:

- · RCIE interrupt enable bit of the PIE1 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 15.1.2.5 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 15.1.2.6 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated If a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 15.1.2.7 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set, the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 15.1.2.8 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

| Name    | Bit 7                                          | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|------------------------------------------------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| BAUDCON | ABDOVF                                         | RCIDL     | DTRXP  | CKTXP  | BRG16  | —      | WUE    | ABDEN  | 247                        |

| INTCON  | GIE/GIEH                                       | PEIE/GIEL | TMR0IE | INT0IE | RABIE  | TMR0IF | INT0IF | RABIF  | 245                        |

| IPR1    | —                                              | ADIP      | RCIP   | TXIP   | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 248                        |

| PIE1    | —                                              | ADIE      | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 248                        |

| PIR1    | —                                              | ADIF      | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 248                        |

| RCSTA   | SPEN                                           | RX9       | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 247                        |

| SPBRG   | EUSART Baud Rate Generator Register, Low Byte  |           |        |        |        |        |        | 247    |                            |

| SPBRGH  | EUSART Baud Rate Generator Register, High Byte |           |        |        |        |        |        | 247    |                            |

| TRISC   | TRISC7                                         | TRISC6    | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 248                        |

| TXREG   | TXREG EUSART Transmit Register                 |           |        |        |        |        |        |        | 247                        |

| TXSTA   | CSRC                                           | TX9       | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 247                        |

TABLE 15-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

#### 15.4.1.6 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver must be disabled by setting the corresponding TRIS bits when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

#### 15.4.1.7 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver must be disabled by setting the associated TRIS bit when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 15.4.1.8 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| R-0             | R-0           | R/W-0                                  | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0  |  |  |  |

|-----------------|---------------|----------------------------------------|------------------|------------------|-----------------|-----------------|--------|--|--|--|

| MC1OUT          | MC2OUT        | C1RSEL                                 | C2RSEL           | C1HYS            | C2HYS           | C1SYNC          | C2SYNC |  |  |  |

| bit 7           |               |                                        |                  |                  |                 |                 | bit 0  |  |  |  |

| Legend:         |               |                                        |                  |                  |                 |                 |        |  |  |  |

| R = Readable    | bit           | W = Writable                           | bit              | U = Unimplei     | mented bit, rea | d as '0'        |        |  |  |  |

| -n = Value at I | POR           | '1' = Bit is set                       |                  | '0' = Bit is cle |                 | x = Bit is unkr | nown   |  |  |  |

|                 |               |                                        |                  |                  |                 |                 |        |  |  |  |

| bit 7           | MC1OUT: Mi    | rror Copy of C                         | IOUT bit         |                  |                 |                 |        |  |  |  |

| bit 6           | MC2OUT: Mi    | rror Copy of C2                        | 2OUT bit         |                  |                 |                 |        |  |  |  |

| bit 5           | C1RSEL: Co    | mparator C1 R                          | eference Sele    | ct bit           |                 |                 |        |  |  |  |

|                 | 1 = FVR route | ed to C1VREF i                         | nput             |                  |                 |                 |        |  |  |  |

|                 | 0 = CVREF/D   | AC1OUT route                           | d to C1VREF in   | nput             |                 |                 |        |  |  |  |

| bit 4           | C2RSEL: Co    | mparator C2 R                          | eference Sele    | ct bit           |                 |                 |        |  |  |  |

|                 | 1 = FVR rout  | ed to C2VREF i                         | nput             |                  |                 |                 |        |  |  |  |

|                 | 0 = CVREF/D   | AC1OUT route                           | d to C2VREF in   | nput             |                 |                 |        |  |  |  |

| bit 3           | C1HYS: Corr   | parator C1 Hy                          | steresis Enabl   | e bit            |                 |                 |        |  |  |  |

|                 |               |                                        |                  |                  |                 |                 |        |  |  |  |

|                 | 0 = Compar    | ator C1 hystere                        | esis disabled    |                  |                 |                 |        |  |  |  |

| bit 2           |               | parator C2 Hy                          |                  | e bit            |                 |                 |        |  |  |  |

|                 |               | ator C2 hyster                         |                  |                  |                 |                 |        |  |  |  |

|                 | -             | ator C2 hystere                        |                  |                  |                 |                 |        |  |  |  |

| bit 1           |               | Output Synch                           |                  |                  |                 |                 |        |  |  |  |

|                 |               | ut is synchrono<br>ut is asynchror     |                  | lge to TMR1 cl   | lock            |                 |        |  |  |  |

| bit 0           | C2SYNC: C2    | C2SYNC: C2 Output Synchronous Mode bit |                  |                  |                 |                 |        |  |  |  |

|                 | 1 = C2 outp   | ut is synchrono                        | ous to rising ec | dge to TMR1 cl   | lock            |                 |        |  |  |  |

|                 | 0 = C2 outp   | ut is asynchror                        | nous             |                  |                 |                 |        |  |  |  |

#### REGISTER 17-3: CMCON0: COMPARATOR 2 CONTROL REGISTER 1

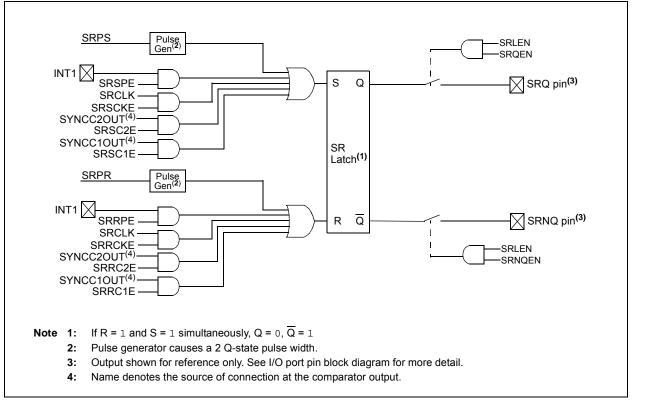

## 19.0 SR LATCH

The module consists of a single SR latch with multiple Set and Reset inputs as well as selectable latch output. The SR latch module includes the following features:

- · Programmable input selection

- SR latch output is available internally/externally

- Selectable Q and  $\overline{Q}$  output

- Firmware Set and Reset

- SR Latch

#### 19.1 Latch Operation

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be Set or Reset by CxOUT, INT1 pin, or variable clock. Additionally the SRPS and the SRPR bits of the SRCON0 register may be used to Set or Reset the SR latch, respectively. The latch is reset-dominant, therefore, if both Set and Reset inputs are high the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

#### 19.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the latch output selection. Both of the SR latch's outputs may be directly output to an independent I/O pin. Control is determined by the state of bits SRQEN and SRNQEN in registers SRCON0.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

#### 19.3 Effects of a Reset

Upon any device Reset, the SR latch is not initialized. The user's firmware is responsible to initialize the latch output before enabling it to the output pins.

#### FIGURE 19-1: SR LATCH SIMPLIFIED BLOCK DIAGRAM

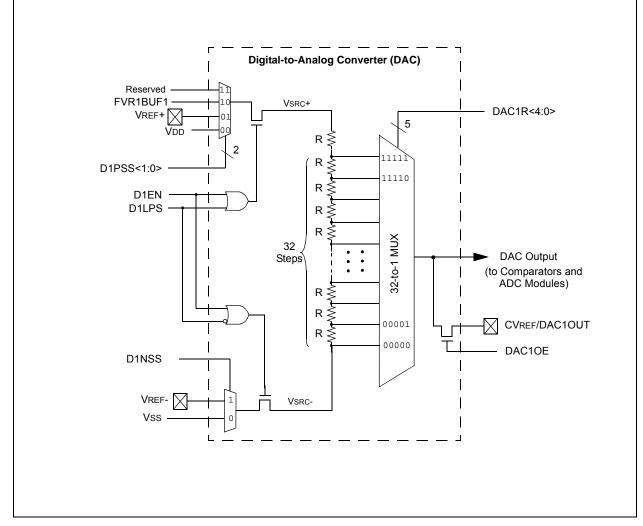

#### FIGURE 21-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

#### TABLE 24-2: PIC18FXXXX INSTRUCTION SET

| Mnemo     | onic,                           | Description                              | Civalac    | 16-Bit Instruction Word |      |      |      | Status                   | Notes      |

|-----------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|------|--------------------------|------------|

| Opera     | nds                             | Description                              | Cycles     | MSb                     |      |      | LSb  | Affected                 | Notes      |

| BYTE-ORIE | ENTED O                         | OPERATIONS                               |            |                         |      |      |      |                          |            |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da | ffff | ffff | C, DC, Z, OV, N          | 1, 2       |

| ADDWFC    | f, d, a                         | Add WREG and CARRY bit to f              | 1          | 0010                    | 00da | ffff | ffff | C, DC, Z, OV, N          | 1, 2       |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da | ffff | ffff | Z, N                     | 1, 2       |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110                    | 101a | ffff | ffff | Z                        | 2          |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001                    | 11da | ffff | ffff | Z, N                     | 1, 2       |

| CPFSEQ    | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110                    | 001a | ffff | ffff | None                     | 4          |

| CPFSGT    | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110                    | 010a | ffff | ffff | None                     | 4          |

| CPFSLT    | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110                    | 000a | ffff | ffff | None                     | 1, 2       |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da | ffff | ffff | C, DC, Z, OV, N          | 1, 2, 3, 4 |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da | ffff | ffff | None                     | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da | ffff | ffff | None                     | 1, 2       |

| INCF      | f, d, a                         | Increment f                              | 1 ΄        | 0010                    | 10da | ffff | ffff | C, DC, Z, OV, N          | 1, 2, 3, 4 |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da | ffff | ffff | None                     | 4          |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da | ffff | ffff | None                     | 1, 2       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1 ΄        | 0001                    | 00da | ffff | ffff | Z, N                     | 1, 2       |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101                    | 00da | ffff | ffff | Z, N                     | 1          |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff | ffff | ffff | None                     |            |

|           | 0 u                             | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff | ffff | ffff |                          |            |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a | ffff | ffff | None                     |            |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a | ffff | ffff | None                     | 1, 2       |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110                    | 110a | ffff | ffff | C, DC, Z, OV, N          |            |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da | ffff | ffff | C, Z, N                  | 1, 2       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da | ffff | ffff | Z, N                     |            |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da | ffff | ffff | C, Z, N                  |            |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da | ffff | ffff | Z, N                     |            |

| SETF      | f, a                            | Set f                                    | 1          | 0110                    | 100a | ffff | ffff | None                     | 1, 2       |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>borrow      | 1          | 0101                    | 01da | ffff | ffff | C, DC, Z, OV, N          |            |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da | ffff | ffff | C, DC, Z, OV, N          | 1, 2       |

| SUBWFB    | f, d, a                         | Subtract WREG from f with                | 1          | 0101                    | 10da | ffff | ffff | C, DC, Z, OV, N          | .,_        |

|           | ., ., .                         | borrow                                   | 1          | 0101                    | 2000 |      |      | -, -, -, -, -, , , , , , |            |

| SWAPF     | f, d, a                         | Swap nibbles in f                        | 1          | 0011                    | 10da | ffff | ffff | None                     | 4          |

| TSTFSZ    | f, a                            | Test f, skip if 0                        | 1 (2 or 3) | 0110                    | 011a | ffff | ffff | None                     | 1, 2       |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da | ffff | ffff | Z, N                     | ., _       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| BTG                                        | Bit Toggle f                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BOV                                                    | Branch if Overflow                                                                                                                                                                                                                                                                                    |  |  |  |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                    | BTG f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Syntax:                                                | BOV n                                                                                                                                                                                                                                                                                                 |  |  |  |

| Operands:                                  | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Operands:                                              | $-128 \le n \le 127$                                                                                                                                                                                                                                                                                  |  |  |  |

|                                            | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operation:                                             | if OVERFLOW bit is '1' (PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                                 |  |  |  |

| Operation:                                 | $(\overline{f} < b >) \to f < b >$                                                                                                                                                                                                                                                                                                                                                                                                                                | Status Affected:                                       | None                                                                                                                                                                                                                                                                                                  |  |  |  |

| Status Affected:                           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Encoding:                                              | 1110 0100 nnnn nnnn                                                                                                                                                                                                                                                                                   |  |  |  |

| Encoding:<br>Description:                  | Bit 'b' in data memory location 'f' is<br>inverted.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. | Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | If the OVERFLOW bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction.<br>1<br>1(2) |  |  |  |

| Words:                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | lf Jump:<br>Q1                                         | Q2 Q3 Q4                                                                                                                                                                                                                                                                                              |  |  |  |

| Cycles:                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Decode                                                 | Read literal Process Write to PC<br>'n' Data                                                                                                                                                                                                                                                          |  |  |  |

| Q Cycle Activity:<br>Q1                    | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No                                                     | No No No                                                                                                                                                                                                                                                                                              |  |  |  |

| Example:<br>Before Instruct                | Read<br>register 'f'Process<br>DataWrite<br>register 'f'BTGPORTC , 4 , 0                                                                                                                                                                                                                                                                                                                                                                                          | operation<br>If No Jump:<br>Q1<br>Decode               | operationoperationoperationQ2Q3Q4Read literalProcessNo'n'Dataoperation                                                                                                                                                                                                                                |  |  |  |

| PORTC<br>PORTC<br>After Instructi<br>PORTC | = 0111 0101 [75h]<br>on:                                                                                                                                                                                                                                                                                                                                                                                                                                          | PC                                                     | = address (HERE)<br>on<br>FLOW = 1;<br>= address (Jump)<br>FLOW = 0;                                                                                                                                                                                                                                  |  |  |  |

| MO\      | /LW                   | Move lite           | Move literal to W                       |      |           |  |  |  |  |

|----------|-----------------------|---------------------|-----------------------------------------|------|-----------|--|--|--|--|

| Synta    | ax:                   | MOVLW               | MOVLW k                                 |      |           |  |  |  |  |

| Oper     | ands:                 | $0 \le k \le 25$    | 5                                       |      |           |  |  |  |  |

| Oper     | ation:                | $k\toW$             |                                         |      |           |  |  |  |  |

| Statu    | s Affected:           | None                |                                         |      |           |  |  |  |  |

| Enco     | ding:                 | 0000                | 1110                                    | kkkk | kkkk      |  |  |  |  |

| Desc     | ription:              | The 8-bit I         | The 8-bit literal 'k' is loaded into W. |      |           |  |  |  |  |

| Word     | ls:                   | 1                   | 1                                       |      |           |  |  |  |  |

| Cycle    | es:                   | 1                   | 1                                       |      |           |  |  |  |  |

| QC       | ycle Activity:        |                     |                                         |      |           |  |  |  |  |

|          | Q1                    | Q2                  | Q3                                      | -    | Q4        |  |  |  |  |

|          | Decode                | Read<br>literal 'k' | Proce<br>Dat                            |      | rite to W |  |  |  |  |

| Example: |                       | MOVLW               | 5Ah                                     |      |           |  |  |  |  |

|          | After Instructio<br>W | on<br>= 5Ah         |                                         |      |           |  |  |  |  |

|          | vv                    | - 5AN               |                                         |      |           |  |  |  |  |

| MOVWF              | Move W t                                                                                                                                          | Move W to f                                                                                                                                                                                                                                                                                                                                                                                                   |                       |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|

| Syntax:            | MOVWF                                                                                                                                             | MOVWF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                  |                       |  |  |  |  |  |

| Operands:          | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                               |                       |  |  |  |  |  |

| Operation:         | $(W) \to f$                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                               |                       |  |  |  |  |  |

| Status Affected:   | None                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                               |                       |  |  |  |  |  |

| Encoding:          | 0110                                                                                                                                              | 111a ff                                                                                                                                                                                                                                                                                                                                                                                                       | ff ffff               |  |  |  |  |  |

|                    | 256-byte ba<br>If 'a' is '0', tl<br>If 'a' is '1', tl<br>GPR bank i<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 24 | Location 'f' can be anywhere in the 256-byte bank.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the GPR bank (default).<br>If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed |                       |  |  |  |  |  |

| Words:             | 1                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                             |                       |  |  |  |  |  |

| Cycles:            | 1                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                             |                       |  |  |  |  |  |

| Q Cycle Activity:  |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                               |                       |  |  |  |  |  |

| Q1                 | Q2                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                                                                            | Q4                    |  |  |  |  |  |