Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-QFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f14k22t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the Microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The write initiate sequence for EECON2, shown as steps 4 through 6 in **Section 4.4.1** "**Flash Program Memory Erase Sequence**", is used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing the internal Flash. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

#### 4.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory is:

- 1. Load Table Pointer register with address of block being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- · clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the block erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

|          | MOVLW | CODE_ADDR_UPPER | ; load TBLPTR with the base     |

|----------|-------|-----------------|---------------------------------|

|          | MOVWF | TBLPTRU         | ; address of the memory block   |

|          | MOVLW | CODE_ADDR_HIGH  |                                 |

|          | MOVWF | TBLPTRH         |                                 |

|          | MOVLW | CODE_ADDR_LOW   |                                 |

|          | MOVWF | TBLPTRL         |                                 |

| ERASE_BL | OCK   |                 |                                 |

|          | BSF   | EECON1, EEPGD   | ; point to Flash program memory |

|          | BCF   | EECON1, CFGS    | ; access Flash program memory   |

|          | BSF   | EECON1, WREN    | ; enable write to memory        |

|          | BSF   | EECON1, FREE    | ; enable block Erase operation  |

|          | BCF   | INTCON, GIE     | ; disable interrupts            |

| Required | MOVLW | 55h             |                                 |

| Sequence | MOVWF | EECON2          | ; write 55h                     |

|          | MOVLW | 0AAh            |                                 |

|          | MOVWF | EECON2          | ; write OAAh                    |

|          | BSF   | EECON1, WR      | ; start erase (CPU stall)       |

|          | BSF   | INTCON, GIE     | ; re-enable interrupts          |

#### EXAMPLE 4-2: ERASING A FLASH PROGRAM MEMORY BLOCK

#### 8.4 **Port Analog Control**

Some port pins are multiplexed with analog functions such as the Analog-to-Digital Converter and comparators. When these I/O pins are to be used as analog inputs it is necessary to disable the digital input buffer to avoid excessive current caused by improper biasing of the digital input. Individual control of the digital input buffers on pins which share analog functions is provided by the ANSEL and ANSELH registers. Setting an ANSx bit high will disable the associated digital input buffer and cause all reads of that pin to return '0' while allowing analog functions of that pin to operate correctly.

The state of the ANSx bits has no affect on digital output functions. A pin with the associated TRISx bit clear and ANSx bit set will still operate as a digital output but the Input mode will be analog.

| R/W-1        | R/W-1          | R/W-1                                  | R/W-1        | R/W-1            | R/W-1          | R/W-1           | R/W-1 |

|--------------|----------------|----------------------------------------|--------------|------------------|----------------|-----------------|-------|

| ANS7         | ANS6           | ANS5                                   | ANS4         | ANS3             | ANS2           | ANS1            | ANS0  |

| bit 7        | ·              |                                        |              |                  |                |                 | bit   |

|              |                |                                        |              |                  |                |                 |       |

| Legend:      |                |                                        |              |                  |                |                 |       |

| R = Readal   |                | W = Writable                           |              | •                | mented bit, re |                 |       |

| -n = Value a | at POR         | '1' = Bit is set                       |              | '0' = Bit is cle | ared           | x = Bit is unki | nown  |

| bit 7        | ANS7: RC3      | Analog Select (                        | Control bit  |                  |                |                 |       |

|              |                | nput buffer of RC                      |              |                  |                |                 |       |

|              | 0              | nput buffer of RC                      |              |                  |                |                 |       |

| bit 6        | ANS6: RC2      | Analog Select C                        | Control bit  |                  |                |                 |       |

|              |                | nput buffer of RC                      |              |                  |                |                 |       |

|              | 0 = Digital ii | nput buffer of RC                      | 2 is enabled |                  |                |                 |       |

| bit 5        | ANS5: RC1      | Analog Select C                        | Control bit  |                  |                |                 |       |

|              |                | nput buffer of RC                      |              |                  |                |                 |       |

|              | 0 = Digital ii | nput buffer of RC                      | 1 is enabled |                  |                |                 |       |

| bit 4        |                | Analog Select C                        |              |                  |                |                 |       |

|              | •              | nput buffer of RC                      |              |                  |                |                 |       |

|              | •              | nput buffer of RC                      |              |                  |                |                 |       |

| bit 3        |                | Analog Select C                        |              |                  |                |                 |       |

|              |                | nput buffer of RA                      |              |                  |                |                 |       |

| 1.1.0        | 0              | nput buffer of RA                      |              |                  |                |                 |       |

| bit 2        |                | Analog Select C                        |              |                  |                |                 |       |

|              |                | nput buffer of RA<br>nput buffer of RA |              |                  |                |                 |       |

| bit 1        | •              | Analog Select C                        |              |                  |                |                 |       |

|              |                | nput buffer of RA                      |              |                  |                |                 |       |

|              | 0              | nput buffer of RA                      |              |                  |                |                 |       |

| bit 0        | •              | Analog Select C                        |              |                  |                |                 |       |

|              |                | nput buffer of RA                      |              |                  |                |                 |       |

|              | 0              |                                        |              |                  |                |                 |       |

|  | REGISTER 8-14: | ANSEL: ANALOG SELECT REGISTER |

|--|----------------|-------------------------------|

|--|----------------|-------------------------------|

0 = Digital input buffer of RA0 is enabled

#### 13.4.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCP pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HFINTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

### 13.4.8.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the RC\_RUN Power-Managed mode and the OSCFIF bit of the PIR2 register will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

#### 13.4.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the enhanced CCP module to reset to a state compatible with the standard CCP module.

| Name    | Bit 7                                  | Bit 6                                             | Bit 5          | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |  |

|---------|----------------------------------------|---------------------------------------------------|----------------|----------|----------|--------|---------|---------|----------------------------|--|

| CCPR1H  | Capture/Co                             | mpare/PWM                                         | Register 1, H  | igh Byte |          |        |         |         | 247                        |  |

| CCPR1L  | Capture/Co                             | mpare/PWM                                         | Register 1, Lo | ow Byte  |          |        |         |         | 247                        |  |

| CCP1CON | P1M1                                   | P1M1 P1M0 DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 |                |          |          |        |         |         | 247                        |  |

| ECCP1AS | ECCPASE                                | ECCPAS2                                           | ECCPAS1        | ECCPAS0  | PSSAC1   | PSSAC0 | PSSBD1  | PSSBD0  | 247                        |  |

| INTCON  | GIE/GIEH                               | PEIE/GIEL                                         | TMR0IE         | INT0IE   | RABIE    | TMR0IF | INT0IF  | RABIF   | 245                        |  |

| IPR1    | _                                      | ADIP                                              | RCIP           | TXIP     | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 248                        |  |

| IPR2    | OSCFIP                                 | OSCFIP C1IP C2IP EEIP BCLIP _ TMR3IP _            |                |          |          |        |         |         | 248                        |  |

| PIE1    | _                                      | ADIE                                              | RCIE           | TXIE     | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 248                        |  |

| PIE2    | OSCFIE                                 | C1IE                                              | C2IE           | EEIE     | BCLIE    |        | TMR3IE  | _       | 248                        |  |

| PIR1    | _                                      | ADIF                                              | RCIF           | TXIF     | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 248                        |  |

| PIR2    | OSCFIF C1IF C2IF EEIF BCLIF — TMR3IF — |                                                   |                |          |          |        |         |         |                            |  |

| PR2     | Timer2 Peri                            | Timer2 Period Register                            |                |          |          |        |         |         |                            |  |

| PWM1CON | PRSEN                                  | PDC6                                              | PDC5           | PDC4     | PDC3     | PDC2   | PDC1    | PDC0    | 247                        |  |

| RCON    | IPEN                                   | SBOREN                                            | -              | RI       | TO       | PD     | POR     | BOR     | 246                        |  |

| TMR1H   | Timer1 Reg                             | ister, High By                                    | rte            |          |          |        |         |         | 246                        |  |

| TMR1L   | Timer1 Reg                             | ister, Low By                                     | te             |          |          |        |         |         | 246                        |  |

| TMR2    | Timer2 Reg                             | ister                                             |                |          |          |        |         |         | 246                        |  |

| TMR3H   | Timer3 Reg                             | ister, High By                                    | rte            |          |          |        |         |         | 247                        |  |

| TMR3L   | Timer3 Reg                             | Timer3 Register, Low Byte                         |                |          |          |        |         |         |                            |  |

| TRISC   | TRISC7                                 | TRISC6                                            | TRISC5         | TRISC4   | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 248                        |  |

| T1CON   | RD16                                   | T1RUN                                             | T1CKPS1        | T1CKPS0  | T1OSCEN  | T1SYNC | TMR1CS  | TMR10N  | 246                        |  |

| T2CON   |                                        | T2OUTPS3                                          | T2OUTPS2       | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 246                        |  |

| T3CON   | RD16                                   | _                                                 | T3CKPS1        | T3CKPS0  | T3CCP1   | T3SYNC | TMR3CS  | TMR3ON  | 247                        |  |

#### TABLE 13-3: REGISTERS ASSOCIATED WITH ECCP1 MODULE AND TIMER1 TO TIMER3

Legend: — = unimplemented, read as '0'. Shaded cells are not used during ECCP operation.

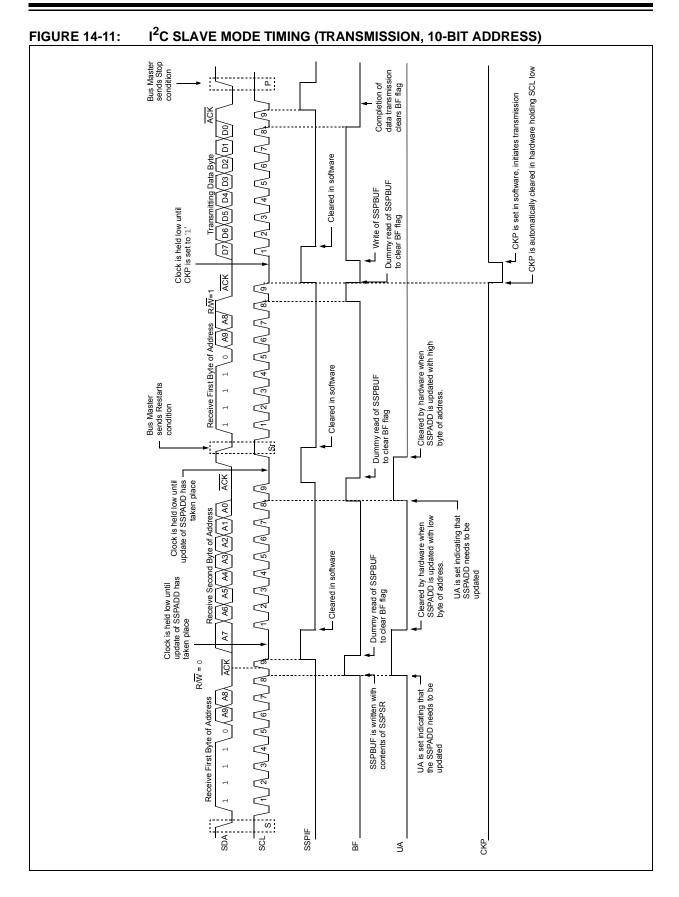

#### 14.2.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- SSPCON1 Control Register

- SSPSTAT STATUS register

- SSPBUF Serial Receive/Transmit Buffer

- SSPSR Shift Register (Not directly accessible)

SSPCON1 and SSPSTAT are the control and STATUS registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in and out. SSPBUF provides indirect access to the SSPSR register. SSPBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 14-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| R/W-0        | R/W-0                    | R-0                              | R-0            | R-0                | R-0             | R-0             | R-0         |

|--------------|--------------------------|----------------------------------|----------------|--------------------|-----------------|-----------------|-------------|

| SMP          | CKE                      | D/A                              | Р              | S                  | R/W             | UA              | BF          |

| bit 7        | ·                        | •                                |                | •                  |                 |                 | bit         |

|              |                          |                                  |                |                    |                 |                 |             |

| Legend:      |                          |                                  |                |                    |                 |                 |             |

| R = Reada    |                          | W = Writable                     |                | •                  | mented bit, rea |                 |             |

| -n = Value   | at POR                   | '1' = Bit is set                 |                | '0' = Bit is cle   | eared           | x = Bit is unki | nown        |

| bit 7        | SMP: Samp                | le bit                           |                |                    |                 |                 |             |

|              | SPI Master r             |                                  |                |                    |                 |                 |             |

|              | 1 = Input da             | ta sampled at er                 |                |                    |                 |                 |             |

|              | •                        | ta sampled at m                  | iddle of data  | output time        |                 |                 |             |

|              | SPI Slave m              | iode:<br>e cleared when          |                |                    |                 |                 |             |

| <b>h</b> # C |                          | lock Select bit <sup>(1)</sup>   |                | n Slave mode.      |                 |                 |             |

| bit 6        |                          | t occurs on trans                |                | tive to Idle clock | k state         |                 |             |

|              |                          | t occurs on trans                |                |                    |                 |                 |             |

| bit 5        | D/A: Data/A              | ddress bit                       |                |                    |                 |                 |             |

|              | Used in I <sup>2</sup> C | mode only.                       |                |                    |                 |                 |             |

| bit 4        | P: Stop bit              |                                  |                |                    |                 |                 |             |

|              | Used in I <sup>2</sup> C | mode only. This                  | bit is cleared | I when the MSS     | P module is di  | sabled, SSPEN   | is cleared. |

| bit 3        | S: Start bit             |                                  |                |                    |                 |                 |             |

|              | Used in I <sup>2</sup> C |                                  |                |                    |                 |                 |             |

| bit 2        |                          | Write Information                | n bit          |                    |                 |                 |             |

|              | Used in I <sup>2</sup> C | ,                                |                |                    |                 |                 |             |

| bit 1        | UA: Update               |                                  |                |                    |                 |                 |             |

|              | Used in I <sup>2</sup> C | ,                                |                |                    |                 |                 |             |

| bit 0        |                          | ull Status bit (Re               |                | only)              |                 |                 |             |

|              |                          | complete, SSP<br>not complete, S |                | notv               |                 |                 |             |

|              |                          | •                                |                |                    |                 |                 |             |

| Note 1:      | Polarity of clock s      | state is set by th               | e CKP bit of   | the SSPCON1 r      | register.       |                 |             |

#### 15.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART. If the RX/DT or TX/CK pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

RX/DT and TX/CK pin output drivers must be disabled by setting the corresponding TRIS bits.

#### 15.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 15.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 15.4.2.2 Synchronous Slave Transmission Set-up

- 1. Set the SYNC and SPEN bits and clear the CSRC bit. Set the TRIS bits corresponding to the RX/DT and TX/CK I/O pins.

- 2. Clear the CREN and SREN bits.

- If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the TXIE bit.

- 4. If 9-bit transmission is desired, set the TX9 bit.

- 5. Enable transmission by setting the TXEN bit.

- 6. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 7. Start transmission by writing the Least Significant eight bits to the TXREG register.

| TABLE 13-3. REGISTERS ASSOCIATED WITTSTRETIKONOOG SERVE TRANSMISSION |                                                         |                                        |             |              |       |        |        |        |                            |

|----------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| Name                                                                 | Bit 7                                                   | Bit 6                                  | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

| BAUDCON                                                              | ABDOVF                                                  | RCIDL                                  | DTRXP       | CKTXP        | BRG16 | —      | WUE    | ABDEN  | 247                        |

| INTCON                                                               | GIE/GIEH                                                | PEIE/GIEL                              | TMR0IE      | INT0IE       | RABIE | TMR0IF | INT0IF | RABIF  | 245                        |

| IPR1                                                                 | —                                                       | ADIP                                   | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 248                        |

| PIE1                                                                 |                                                         | ADIE                                   | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 248                        |

| PIR1                                                                 |                                                         | ADIF                                   | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 248                        |

| RCSTA                                                                | SPEN                                                    | PEN RX9 SREN CREN ADDEN FERR OERR RX9D |             |              |       |        |        | 247    |                            |

| SPBRG                                                                | EUSART B                                                | aud Rate Ge                            | enerator Re | gister, Low  | Byte  |        |        |        | 247                        |

| SPBRGH                                                               | EUSART B                                                | aud Rate Ge                            | enerator Re | gister, High | Byte  |        |        |        | 247                        |

| TRISC                                                                | TRISC7 TRISC6 TRISC5 TRISC4 TRISC3 TRISC2 TRISC1 TRISC0 |                                        |             |              |       |        | 248    |        |                            |

| TXREG                                                                | EUSART T                                                | ransmit Reg                            | ister       |              |       |        |        |        | 247                        |

| TXSTA                                                                | CSRC                                                    | TX9                                    | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 247                        |

|                                                                      | • • •                                                   |                                        | (-1.0)      |              |       |        | •      |        |                            |

#### TABLE 15-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

### 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

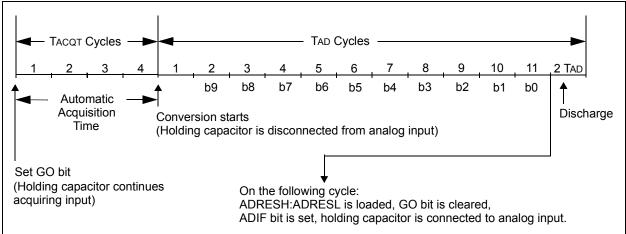

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will, depending on the ACQT bits of the ADCON2 register, either immediately start the Analog-to-Digital conversion or start an acquisition delay followed by the Analog-to-Digital conversion. Figure 16-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into SLEEP mode before the conversion begins.

Figure 16-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT<2:0> bits are set to '010' which selects a 4 TAD acquisition time before the conversion starts.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 16.2.9 "A/D Conversion Procedure".

### FIGURE 16-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

| T <u>cy - Tai</u> | D TAD1                                                                 | TAD2     | TAD3   | TAD4   | TAD5   | TAD6     | TAD7         | TAD8     | TAD9    | TAD10   | TAD11 | 2 TAD                           |

|-------------------|------------------------------------------------------------------------|----------|--------|--------|--------|----------|--------------|----------|---------|---------|-------|---------------------------------|

| <b>≜</b> ↑        | <b>∱</b>                                                               | b9       | b8     | b7     | b6     | b5       | b4           | b3       | b2      | b1      | b0    | ↑ '                             |

|                   | Conver                                                                 | sion sta | arts   |        |        |          |              |          |         |         |       | Discharge                       |

| Holdin            | ig capao                                                               | citor is | discon | nected | from a | analog i | input (t     | ypically | / 100 n | is)     |       |                                 |

| l<br>Set GO       | bit                                                                    |          |        |        |        |          | $\mathbf{I}$ |          |         |         |       | Į                               |

|                   | On the following cycle:<br>ADRESH:ADRESL is loaded, GO bit is cleared, |          |        |        |        |          |              |          |         |         |       |                                 |

|                   |                                                                        |          |        |        |        |          |              |          |         |         |       | eared,<br>cted to analog input. |

|                   |                                                                        |          |        |        |        |          |              |          | 9 00.00 | 0.10.10 |       | eter te analog inpati           |

#### FIGURE 16-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

#### 16.2.10 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

| Note: | Analog pin control is performed by the |

|-------|----------------------------------------|

|       | ANSEL and ANSELH registers. For        |

|       | ANSEL and ANSELH registers, see        |

|       | Register 8-14 and Register 8-15,       |

|       | respectively.                          |

#### REGISTER 16-1: ADCON0: A/D CONTROL REGISTER 0

| U-0                                | U-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0   | R/W-0 |  |  |

|------------------------------------|-----|-------|-----------------------------------------|-------|-------|---------|-------|--|--|

| —                                  |     | CHS3  | CHS2                                    | CHS1  | CHS0  | GO/DONE | ADON  |  |  |

| bit 7                              |     |       | •                                       | •     |       |         | bit 0 |  |  |

|                                    |     |       |                                         |       |       |         |       |  |  |

| Legend:                            |     |       |                                         |       |       |         |       |  |  |

| R = Readable bit W = Writable bit  |     |       | U = Unimplemented bit, read as '0'      |       |       |         |       |  |  |

| -n = Value at POR '1' = Bit is set |     |       | '0' = Bit is cleared x = Bit is unknown |       |       |         |       |  |  |

#### bit 7-6 Unimplemented: Read as '0'

| bit 5-2 | CHS<3:0>: Analog Channel Select bits                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|

|         | 0000 <b>= ANO</b>                                                                                                                    |

|         | 0001 <b>= AN1</b>                                                                                                                    |

|         | 0010 <b>= AN2</b>                                                                                                                    |

|         | 0011 <b>= AN3</b>                                                                                                                    |

|         | 0100 <b>= AN4</b>                                                                                                                    |

|         | 0101 <b>= AN5</b>                                                                                                                    |

|         | 0110 <b>= AN6</b>                                                                                                                    |

|         | 0111 <b>= AN7</b>                                                                                                                    |

|         | 1000 <b>= AN8</b>                                                                                                                    |

|         | 1001 = AN9                                                                                                                           |

|         | 1010 = AN10                                                                                                                          |

|         | 1011 = AN11                                                                                                                          |

|         | 1100 = Reserved                                                                                                                      |

|         | 1101 = Reserved                                                                                                                      |

|         | $1110 = DAC^{(2)}$                                                                                                                   |

|         | $1111 = FVR^{(2)}$                                                                                                                   |

| bit 1   | GO/DONE: A/D Conversion Status bit                                                                                                   |

|         | 1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.                                               |

|         | This bit is automatically cleared by hardware when the A/D conversion has completed.<br>0 = A/D conversion completed/not in progress |

| bit 0   | ADON: ADC Enable bit                                                                                                                 |

|         | 1 = ADC is enabled                                                                                                                   |

|         | 0 = ADC is disabled and consumes no operating current                                                                                |

| Note 1: | Selecting reserved channels will yield unpredictable results as unimplemented input channels are left floating.                      |

| 2:      | See Section 20.0 "Fixed Voltage Reference (FVR)" for more information.                                                               |

## 17.8 Additional Comparator Features

There are four additional comparator features:

- Simultaneous read of comparator outputs

- Internal reference selection

- · Hysteresis selection

- Output Synchronization

#### 17.8.1 SIMULTANEOUS COMPARATOR OUTPUT READ

The MC1OUT and MC2OUT bits of the CM2CON1 register are mirror copies of both comparator outputs. The ability to read both outputs simultaneously from a single register eliminates the timing skew of reading separate registers.

| Note 1: | Obtaining    | the   | status    | of    | C1    | IOUT  | or   |

|---------|--------------|-------|-----------|-------|-------|-------|------|

|         | C2OUT by     | read  | ling CM   | 2CO   | N1    | does  | not  |

|         | affect the o | compa | arator in | terru | ıpt ı | misma | atch |

|         | registers.   |       |           |       |       |       |      |

#### 17.8.2 INTERNAL REFERENCE SELECTION

There are two internal voltage references available to the noninverting input of each comparator. One of these is the Fixed Voltage Reference (FVR) and the other is the variable Digital-to-Analog Converter (CVREF/DAC). The CxRSEL bit of the CM2CON register determines which of these references is routed to the Digital-to-Analog Converter output (CVREF/DAC). Further routing to the comparator is accomplished by the CxR bit of the CMxCON0 register. See **20.0** "**Fixed Voltage Reference (FVR)**" and Figure 17-2 and Figure 17-3 for more detail.

#### 17.8.3 COMPARATOR HYSTERESIS

The Comparator Cx have selectable hysteresis. The hysteresis can be enabled by setting the CxHYS bit of the CM2CON1 register. See **Section 26.0** "**Electrical Specifications**" for more details.

#### 17.8.4 SYNCHRONIZING COMPARATOR OUTPUT TO TIMER 1

The Comparator Cx output can be synchronized with Timer1 by setting the CxSYNC bit of the CM2CON1 register. When enabled, the Cx output is latched on the rising edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the rising edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 17-2 and Figure 17-3) and the Timer1 Block Diagram (Figure 17-2) for more information.

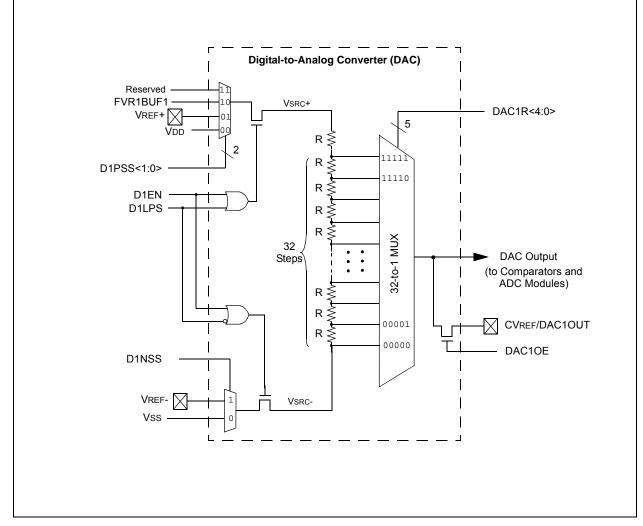

## FIGURE 21-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

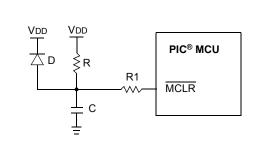

## 22.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In PIC18(L)F1XK22 devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. See **Section 8.1 "PORTA, TRISA and LATA Registers"** for more information.

## 22.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the POR bit of the RCON register. The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event. POR is not reset to '1' by any hardware event. To capture multiple events, the user must manually set the bit to '1' by software following any POR.

#### FIGURE 22-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3:  $\underline{R1 \ge 1} \ k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C, in the event of  $\overline{MCLR}/VPP$  pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

|                                        |                                                                                         |               |                                    | <b>REGISTER 2</b> |        |        |       |  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------|---------------|------------------------------------|-------------------|--------|--------|-------|--|--|--|

| U-0                                    | U-0                                                                                     | U-0           | R/P-1                              | R/P-1             | R/P-1  | R/P-1  | R/P-1 |  |  |  |

| —                                      | —                                                                                       | _             | WDTPS3                             | WDTPS2            | WDTPS1 | WDTPS0 | WDTEN |  |  |  |

| bit 7                                  |                                                                                         |               |                                    |                   |        |        | bit   |  |  |  |

| Legend:                                |                                                                                         |               |                                    |                   |        |        |       |  |  |  |

| R = Readable bit P = Programmable bit  |                                                                                         |               | U = Unimplemented bit, read as '0' |                   |        |        |       |  |  |  |

| -n = Value when device is unprogrammed |                                                                                         |               | x = Bit is unkr                    | nown              |        |        |       |  |  |  |

|                                        |                                                                                         | 0             |                                    |                   |        |        |       |  |  |  |

| bit 7-5                                | Unimplement                                                                             | ted: Read as  | ʻ0'                                |                   |        |        |       |  |  |  |

| bit 4-1                                | WDTPS<3:0>: Watchdog Timer Postscale Select bits                                        |               |                                    |                   |        |        |       |  |  |  |

|                                        | 1111 <b>= 1:32,7</b>                                                                    | 68            |                                    |                   |        |        |       |  |  |  |

|                                        | 1110 = 1:16,3                                                                           | 384           |                                    |                   |        |        |       |  |  |  |

|                                        | 1101 <b>= 1:8,1</b> 9                                                                   |               |                                    |                   |        |        |       |  |  |  |

|                                        | 1100 <b>= 1:4,0</b> 9                                                                   |               |                                    |                   |        |        |       |  |  |  |

|                                        | 1011 <b>= 1:2,0</b> 4                                                                   |               |                                    |                   |        |        |       |  |  |  |

|                                        | 1010 = 1:1,024                                                                          |               |                                    |                   |        |        |       |  |  |  |

|                                        | 1001 = 1:512                                                                            |               |                                    |                   |        |        |       |  |  |  |

|                                        | 1000 = 1:256                                                                            |               |                                    |                   |        |        |       |  |  |  |

|                                        | 0111 = 1:128                                                                            |               |                                    |                   |        |        |       |  |  |  |

|                                        | 0110 = 1:64<br>0101 = 1:32                                                              |               |                                    |                   |        |        |       |  |  |  |

|                                        | 0101 = 1.32<br>0100 = 1.16                                                              |               |                                    |                   |        |        |       |  |  |  |

|                                        | 0100 = 1.10<br>0011 = 1.8                                                               |               |                                    |                   |        |        |       |  |  |  |

|                                        | 0011 = 1.8<br>0010 = 1.4                                                                |               |                                    |                   |        |        |       |  |  |  |

|                                        | 0010 = 1.4<br>0001 = 1.2                                                                |               |                                    |                   |        |        |       |  |  |  |

|                                        | 0000 = 1:1                                                                              |               |                                    |                   |        |        |       |  |  |  |

| bit 0                                  |                                                                                         | obdog Timor I | Enable bit                         |                   |        |        |       |  |  |  |

|                                        | WDTEN: Watchdog Timer Enable bit<br>1 = WDT is always enabled. SWDTEN bit has no effect |               |                                    |                   |        |        |       |  |  |  |

|                                        | 0 = WDT is controlled by SWDTEN bit of the WDTCON register                              |               |                                    |                   |        |        |       |  |  |  |

| РОР                                                                                |             | Рор Тор о                                                                                              | Pop Top of Return Stack                                       |                                                 |                                         |                                                      |  |  |

|------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------|-----------------------------------------|------------------------------------------------------|--|--|

| Syntax                                                                             | :           | POP                                                                                                    |                                                               |                                                 |                                         |                                                      |  |  |

| Operands:                                                                          |             | None                                                                                                   | None                                                          |                                                 |                                         |                                                      |  |  |

| Operat                                                                             | ion:        | $(TOS) \rightarrow bi$                                                                                 | $(TOS) \rightarrow bit bucket$                                |                                                 |                                         |                                                      |  |  |

| Status                                                                             | Affected:   | None                                                                                                   | None                                                          |                                                 |                                         |                                                      |  |  |

| Encodi                                                                             | ing:        | 0000                                                                                                   | 0000                                                          | 000                                             | 0                                       | 0110                                                 |  |  |

| Description:                                                                       |             | The TOS va<br>stack and is<br>then becom<br>was pushed<br>This instruc-<br>the user to<br>stack to inc | s discard<br>nes the p<br>d onto th<br>ction is p<br>properly | led. Th<br>previou<br>e retui<br>rovide<br>mana | ne To<br>is va<br>n st<br>d to<br>ge tl | OS value<br>Ilue that<br>ack.<br>enable<br>he return |  |  |

| Words:                                                                             |             | 1                                                                                                      |                                                               |                                                 |                                         |                                                      |  |  |

| Cycles:                                                                            |             | 1                                                                                                      |                                                               |                                                 |                                         |                                                      |  |  |

| Q Cycle Activity:                                                                  |             |                                                                                                        |                                                               |                                                 |                                         |                                                      |  |  |

|                                                                                    | Q1          | Q2                                                                                                     | Q                                                             | 3                                               |                                         | Q4                                                   |  |  |

|                                                                                    | Decode      | No<br>operation                                                                                        | POP <sup>-</sup><br>valu                                      |                                                 | op                                      | No<br>peration                                       |  |  |

| <u>Examp</u>                                                                       | <u>le</u> : | POP<br>GOTO                                                                                            | NEW                                                           |                                                 |                                         |                                                      |  |  |

| Before Instruction<br>TOS<br>Stack (1 level down<br>After Instruction<br>TOS<br>PC |             | level down)                                                                                            | = (                                                           | 0031A:<br>014332<br>014332<br>NEW               | 2h                                      |                                                      |  |  |

| PUSH              |                             | Push Top                                                     | Push Top of Return Stack                                                                                                                                                                                                                    |                |    |                |  |  |

|-------------------|-----------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----|----------------|--|--|

| Syntax:           |                             | PUSH                                                         |                                                                                                                                                                                                                                             |                |    |                |  |  |

| Operands:         |                             | None                                                         |                                                                                                                                                                                                                                             |                |    |                |  |  |

| Oper              | ation:                      | $(PC + 2) \rightarrow$                                       | $(PC + 2) \rightarrow TOS$                                                                                                                                                                                                                  |                |    |                |  |  |

| Statu             | s Affected:                 | None                                                         |                                                                                                                                                                                                                                             |                |    |                |  |  |

| Enco              | oding:                      | 0000                                                         | 0000                                                                                                                                                                                                                                        | 000            | 0  | 0101           |  |  |

| Description:      |                             | the return s<br>value is pus<br>This instruc<br>software sta | The PC + 2 is pushed onto the top of<br>the return stack. The previous TOS<br>value is pushed down on the stack.<br>This instruction allows implementing a<br>software stack by modifying TOS and<br>then pushing it onto the return stack. |                |    |                |  |  |

| Word              | ls:                         | 1                                                            |                                                                                                                                                                                                                                             |                |    |                |  |  |

| Cycles:           |                             | 1                                                            |                                                                                                                                                                                                                                             |                |    |                |  |  |

| Q Cycle Activity: |                             |                                                              |                                                                                                                                                                                                                                             |                |    |                |  |  |

|                   | Q1                          | Q2                                                           | G                                                                                                                                                                                                                                           | 3              |    | Q4             |  |  |

|                   | Decode                      | PUSH<br>PC + 2 onto<br>return stack                          |                                                                                                                                                                                                                                             | lo<br>ation    | op | No<br>peration |  |  |

| Exan              | nple:                       | PUSH                                                         |                                                                                                                                                                                                                                             |                |    |                |  |  |

|                   | Before Instruc<br>TOS<br>PC | ction                                                        | =<br>=                                                                                                                                                                                                                                      | 345Ah<br>0124h |    |                |  |  |

|                   | After Instruction           | on                                                           | =                                                                                                                                                                                                                                           | 0126h          |    |                |  |  |

## 25.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 25.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 25.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 25.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 26.0 ELECTRICAL SPECIFICATIONS

## 26.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias             | 40°C to +125°C       |

|--------------------------------------------|----------------------|

| Storage temperature                        | 65°C to +150°C       |

| Voltage on pins with respect to Vss        |                      |

| on VDD pin                                 |                      |

| PIC18F1XK22                                | 0.3V to +6.5V        |

| PIC18LF1XK22                               | -0.3V to +4.0V       |

| on MCLR pin                                | -0.3V to +9.0V       |

| on all other pins                          | 0.3V to (VDD + 0.3V) |

| Maximum current <sup>(1)</sup>             |                      |

| on Vss pin                                 |                      |

| -40°C $\leq$ TA $\leq$ +85°C, Industrial   | 250 mA               |

| -40°C $\leq$ TA $\leq$ +125°C, Extended    |                      |

| on VDD pin                                 |                      |

| -40°C $\leq$ TA $\leq$ +85°C,Industrial    | 250 mA               |

| -40°C $\leq$ TA $\leq$ +125°C, Extended    |                      |

| sunk by all ports                          |                      |

| sourced by all ports                       |                      |

| Maximum output current                     |                      |

| sunk by any I/O pin                        | ±50 mA               |

| sourced by any I/O pin                     |                      |

| Clamp current, Ik (VPIN < 0 or VPIN > VDD) |                      |

| Total power dissipation <sup>(2)</sup>     |                      |

| ···· F · · · · · · · · · · · · · · · ·     |                      |

**Note 1:** Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 26-8 to calculate device specifications.

2: Power dissipation is calculated as follows: PDIS = VDD x {IDD -  $\Sigma$ IOH} +  $\Sigma$ {VDD - VOH) x IOH} +  $\Sigma$ (VOL x IOI).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

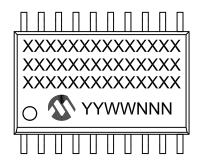

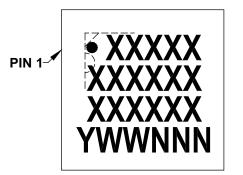

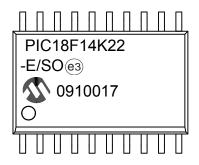

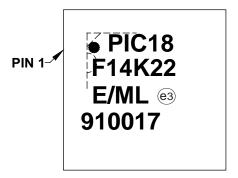

## Package Marking Information (Continued)

20-Lead SOIC (7.50 mm)

20-Lead QFN (4x4x0.9 mm)

Example

Example

| Legend | 4: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                     | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

## APPENDIX A: REVISION HISTORY

## **Revision A (February 2009)**

Original data sheet for PIC18(L)F1XK22 devices.

## Revision B (04/2009)

Revised data sheet title; Revised Peripheral Features section; Revised Table 3-1, Table 3-2; Revised Example 15-1; Revised Table 21-4.

## **Revision C (10/2009)**

Updated Table 1-1; Updated the "Electrical Specifications" section (Figures 25-1 to 25-4; subsections 25.1, 25.2, 25.3, 25.4, 25.5, 25.6, 25.7, 25.8, Added Param No. OS09 to Table 25-2; Added Param No. D003A and Note 1 to Table 25-12); Added graphs to the "DC and AC Characteristics Graphs and Charts" section; Other minor corrections.

## Revision D (05/2010)

Revised Section 1.3 (deleted #2); Revised Figure 1-1; Added Table 2-4; Removed register EEADRH from Tables 3-1 and 3-2; Revised Section 5 (Data EEPROM Memory); Updated Example 5-2 and Table 5-1; Revised Section 13.4.4 (Enhanced PWM Auto-Shutdown Mode); Added Note 4 below Register 13-2; Revised Figure 16-1; Revised Equation 20-1; Removed sub-section 20.1.3 (Output Clamped to Vss); Updated Figure 20-1; Revised Tables 21-4 and Table 22-1; Updated Register 22-5, Figure 25-5, Table 25-2, Table 25-8, Table 25-10 and Table 25-12; Updated the Electrical Specification section; Other minor corrections.

## **Revision E (10/2011)**

Updated data sheet to new format; Updated the Pin Diagrams; Updated the Electrical Specifications section; Updated the Packaging Information section; Updated Table B-1; Updated the Product Identification System section; Other minor corrections.

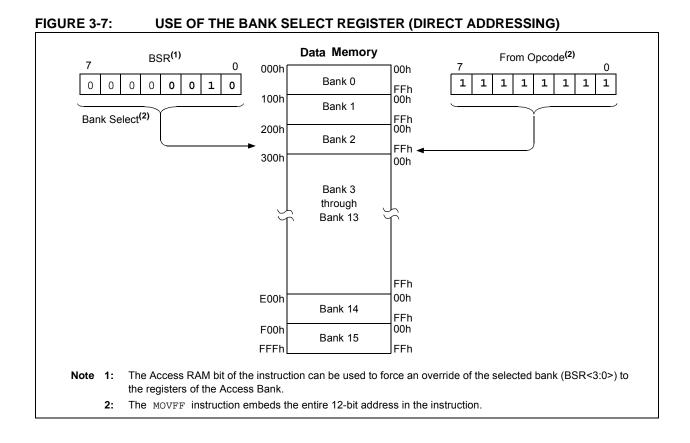

## Revision F (04/2016)

Updated Analog Features section on page 1; Updated Tables 1-2, 3-2, 8-5, 8-6, 16-2 and 22-4; Added Note 3 to Tables 3-2, 8-1 and 8-2; Added Note 1 to Tables 9-1, 10-2, 12-1 and 17-2, and Register 8-4; Updated Figures 3-7, 9-1 and 9-2; Updated Registers 13-2, 16-2, 19-1; Updated Section 1.1.2, 7.9 and 8.1; Replaced chapter 20.0 (Voltage References) with chapter 20.0 (Fixed Voltage Reference) and 21.0 (Digital-to-Analog Converter (DAC) Module); Updated Chapter 26.0 (Electrical Specifications); Other minor corrections.