Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| _                          |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Details                    |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

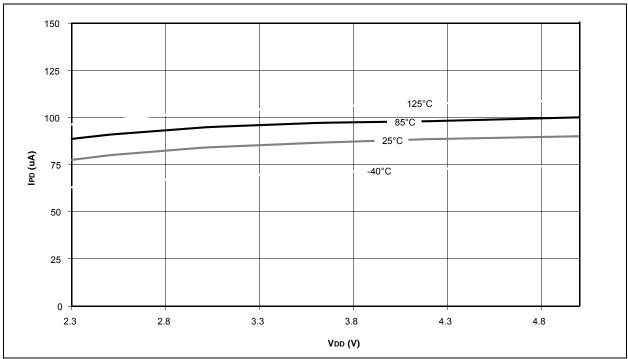

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f14k22t-i-ss |

### PIC18(L)F1XK22 Family Types

|                | dex           | Program Memory |       | Data Memory     |                           |      |                    |                        | S          |                        |      |             |        |          |

|----------------|---------------|----------------|-------|-----------------|---------------------------|------|--------------------|------------------------|------------|------------------------|------|-------------|--------|----------|

| Device         | Data Sheet In | Bytes          | Words | SRAM<br>(bytes) | Data<br>EEPROM<br>(bytes) | Pins | I/O <sup>(1)</sup> | 10-bit A/D<br>Channels | Comparator | Timers<br>8-bit/16-bit | ECCP | <b>MSSP</b> | EUSART | SR Latch |

| PIC18(L)F13K22 | (1)           | 8K             | 4K    | 256             | 256                       | 20   | 18                 | 12-ch                  | 2          | 1/3                    | 1    | 1           | 1      | Yes      |

| PIC18(L)F14K22 | (1)           | 16K            | 8K    | 512             | 256                       | 20   | 18                 | 12-ch                  | 2          | 1/3                    | 1    | 1           | 1      | Yes      |

Note 1: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document)

**1.** DS40001365 PIC18(L)F1XK22 20-Pin Flash Microcontrollers with XLP Technology

Note: For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

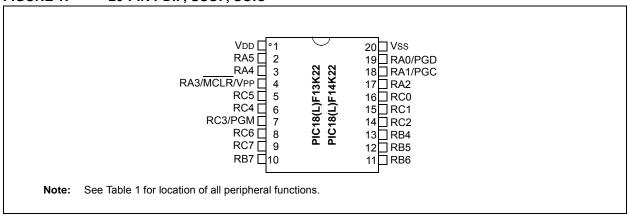

### **Pin Diagrams**

#### FIGURE 1: 20-PIN PDIP, SSOP, SOIC

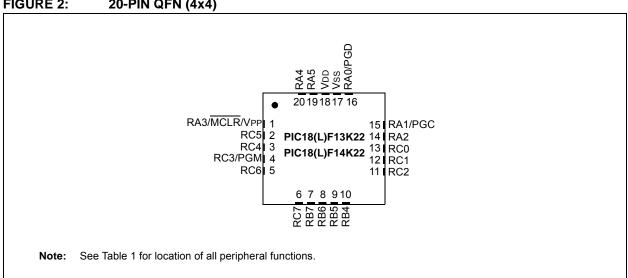

#### FIGURE 2: 20-PIN QFN (4x4)

Primary Oscillator, PIC18(L)F1XK22 External and Secondary Timer1/Timer3 OSC1/T13CKI Oscillator Sleep PCLKEN IDLEN LP, XT, HS, RC, EC, 4 x PLL Secondary Osc. OSC2 Sleep 0x FOSC<3:0> Peripherals T10SCEN PLL\_EN PLLEN Internal Osc. System ×Σ Clock CPU IRCF<2:0> Sleep 16 MHz 8 MHz Internal 110 4 MHz Oscillator 101 Block 2 MHz Postscaler FOSC<3:0> 100 X 16 MHz Clock 1 MHz **HFINTOSC** SCS<1:0> Control 500 kHz 010 250 kHz LFINTOSC 001 31 kHz 000 INTSRC Fail-Safe Clock Watchdog Timer Two-Speed Start-up

FIGURE 2-1: PIC® MCU CLOCK SOURCE BLOCK DIAGRAM

Note: If using a low-frequency external oscillator and want to multiple it by 4 via PLL, the ideal input frequency is from 4 MHz to 16 MHz.

### 2.4.1 PRIMARY EXTERNAL OSCILLATOR SHUTDOWN

The Primary External Oscillator can be enabled or disabled via software. To enable software control of the Primary External Oscillator, the PCLKEN bit of the CONFIG1H Configuration register must be set. With the PCLKEN bit set, the Primary External Oscillator is controlled by the PRI\_SD bit of the OSCCON2 register. The Primary External Oscillator will be enabled when the PRI\_SD bit is set, and disabled when the PRI\_SD bit is clear.

Note:

The Primary External Oscillator cannot be shut down when it is selected as the System Clock. To shut down the oscillator, the system clock source must be either the Secondary Oscillator or the Internal Oscillator.

### 2.4.2 LP, XT AND HS OSCILLATOR MODES

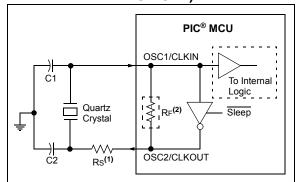

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 2-2). The mode selects a low, medium or high gain setting of the internal inverteramplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 2-2 and Figure 2-3 show typical circuits for quartz crystal and ceramic resonators, respectively.

# FIGURE 2-2: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: A series resistor (Rs) may be required for quartz crystals with low drive level.

- 2: The value of RF varies with the Oscillator mode selected (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PICmicro<sup>®</sup> Devices (DS00826)

- AN849, Basic PICmicro<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PICmicro<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949)

#### REGISTER 7-3: INTCON3: INTERRUPT CONTROL 3 REGISTER

| R/W-1  | R/W-1  | U-0 | R/W-0    | R/W-0 | U-0 | R/W-0  | R/W-0  |

|--------|--------|-----|----------|-------|-----|--------|--------|

| INT2IP | INT1IP | _   | — INT2IE |       | _   | INT2IF | INT1IF |

| bit 7  |        |     |          |       |     |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 INT2IP: INT2 External Interrupt Priority bit

1 = High priority0 = Low priority

bit 6 INT1IP: INT1 External Interrupt Priority bit

1 = High priority0 = Low priority

bit 5 **Unimplemented:** Read as '0'

bit 4 INT2IE: INT2 External Interrupt Enable bit

1 = Enables the INT2 external interrupt0 = Disables the INT2 external interrupt

bit 3 INT1IE: INT1 External Interrupt Enable bit

1 = Enables the INT1 external interrupt0 = Disables the INT1 external interrupt

bit 2 Unimplemented: Read as '0'

bit 1 INT2IF: INT2 External Interrupt Flag bit

1 = The INT2 external interrupt occurred (must be cleared by software)

0 = The INT2 external interrupt did not occur

bit 0 INT1IF: INT1 External Interrupt Flag bit

1 = The INT1 external interrupt occurred (must be cleared by software)

0 = The INT1 external interrupt did not occur

Note:

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software might ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

x = Bit is unknown

### 7.7 IPR Registers

Legend:

R = Readable bit

-n = Value at POR

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1 and IPR2). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

### REGISTER 7-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

W = Writable bit

'1' = Bit is set

| U-0   | R/W-1            | R/W-1 R/W-1 |       | R/W-1  | R/W-1  | R/W-1  | R/W-1 |

|-------|------------------|-------------|-------|--------|--------|--------|-------|

| _     | — ADIP RCIP TXIP |             | SSPIP | CCP1IP | TMR2IP | TMR1IP |       |

| bit 7 |                  |             |       |        |        |        | bit 0 |

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

| bit 7 | Unimplemented: Read as '0'                                   |

|-------|--------------------------------------------------------------|

| bit 6 | ADIP: A/D Converter Interrupt Priority bit                   |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

| bit 5 | RCIP: EUSART Receive Interrupt Priority bit                  |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

| bit 4 | TXIP: EUSART Transmit Interrupt Priority bit                 |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

| bit 3 | SSPIP: Master Synchronous Serial Port Interrupt Priority bit |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

| bit 2 | CCP1IP: CCP1 Interrupt Priority bit                          |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

| bit 1 | TMR2IP: TMR2 to PR2 Match Interrupt Priority bit             |

|       | 1 = High priority                                            |

|       | 0 = Low priority                                             |

| bit 0 | TMR1IP: TMR1 Overflow Interrupt Priority bit                 |

1 = High priority0 = Low priority

### 7.8 RCON Register

Legend:

The RCON register contains flag bits which are used to determine the cause of the last Reset or wake-up from Idle or Sleep modes. RCON also contains the IPEN bit which enables interrupt priorities.

The operation of the SBOREN bit and the Reset flag bits is discussed in more detail in **Section 22.1 "RCON Register"**.

### REGISTER 7-10: RCON: RESET CONTROL REGISTER

| R/W-0 | R/W-1                 | U-0 | R/W-1 | R-1 | R-1   | R/W-0 | R/W-0              |

|-------|-----------------------|-----|-------|-----|-------|-------|--------------------|

| IPEN  | SBOREN <sup>(1)</sup> | _   | — RI  |     | TO PD |       | BOR <sup>(3)</sup> |

| bit 7 |                       |     |       |     |       |       | bit 0              |

| R = Readable b  | oit W                                | = Writable bit                                          | U = Unimplemented bit, read    | d as '0'                       |

|-----------------|--------------------------------------|---------------------------------------------------------|--------------------------------|--------------------------------|

| -n = Value at P | OR '1'                               | = Bit is set                                            | '0' = Bit is cleared           | x = Bit is unknown             |

|                 |                                      |                                                         |                                |                                |

| bit 7           | IPEN: Interrupt P                    | riority Enable bit                                      |                                |                                |

|                 | •                                    | ty levels on interrupts                                 |                                |                                |

|                 | =                                    | •                                                       | C16CXXX Compatibility mode     | e)                             |

| bit 6           | SBOREN: BOR                          | Software Enable bit <sup>(1)</sup>                      |                                |                                |

|                 | If BOREN<1:0> =                      |                                                         |                                |                                |

|                 | 1 = BOR is enabl<br>0 = BOR is disab |                                                         |                                |                                |

|                 |                                      |                                                         |                                |                                |

|                 | If BOREN<1:0> = Bit is disabled an   |                                                         |                                |                                |

| bit 5           | Unimplemented                        | : Read as '0'                                           |                                |                                |

| bit 4           | RI: RESET Instruc                    | ction Flag bit                                          |                                |                                |

|                 | 1 = The RESET i                      | nstruction was not execu                                | ted (set by firmware or Power  | -on Reset)                     |

|                 |                                      |                                                         | I causing a device Reset (mu   | ust be set in firmware after a |

|                 |                                      | ed Reset occurs)                                        |                                |                                |

| bit 3           | TO: Watchdog Ti                      | •                                                       |                                |                                |

|                 | • •                                  | r-up, CLRWDT instruction                                | or SLEEP instruction           |                                |

| 1.11.0          | 0 = A WDT Time                       |                                                         |                                |                                |

| bit 2           |                                      | Detection Flag bit                                      | . ( (                          |                                |

|                 |                                      | r-up or by the CLRWDT in:<br>ution of the SLEEP instruc |                                |                                |

| bit 1           |                                      | Reset Status bit <sup>(2)</sup>                         | MOH                            |                                |

| DIL I           | 1 = No Power-on                      |                                                         |                                |                                |

|                 |                                      |                                                         | set in software after a Power- | on Reset occurs)               |

| bit 0           |                                      | Reset Status bit <sup>(3)</sup>                         | oot in contrare and a r oner   |                                |

| DIL O           |                                      | Reset has not occurred                                  | (set by firmware only)         |                                |

|                 |                                      |                                                         | e set by firmware after a POR  | or Brown-out Reset occurs)     |

|                 |                                      | (                                                       |                                | ,                              |

- Note 1: If SBOREN is enabled, its Reset state is '1'; otherwise, it is '0'.

- 2: The actual Reset value of POR is determined by the type of device Reset. See the notes following this register and **Section 22.6 "Reset State of Registers"** for additional information.

- 3: See Table 22-3.

TABLE 8-5: PORTC I/O SUMMARY

| Pin            | Function | TRIS<br>Setting                                                  | I/O | I/O<br>Type | Description                                                                                                       |  |  |  |  |  |

|----------------|----------|------------------------------------------------------------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RC0/AN4/C2IN+  | RC0      | 0                                                                | 0   | DIG         | LATC<0> data output.                                                                                              |  |  |  |  |  |

|                |          | 1                                                                | ı   | ST          | PORTC<0> data input.                                                                                              |  |  |  |  |  |

|                | AN4      | 1                                                                | ı   | ANA         | A/D input channel 4.                                                                                              |  |  |  |  |  |

|                | C2IN+    | 1                                                                |     | ANA         | Comparators C2 noninverting input.                                                                                |  |  |  |  |  |

| RC1/AN5/       | RC1      | 0                                                                | 0   | DIG         | LATC<1> data output.                                                                                              |  |  |  |  |  |

| C12IN1-        |          | 1                                                                | ı   | ST          | PORTC<1> data input.                                                                                              |  |  |  |  |  |

|                | AN5      | 1                                                                |     | ANA         | A/D input channel 5.                                                                                              |  |  |  |  |  |

|                | C12IN1-  | 1                                                                | ı   | ANA         | Comparators C1 and C2 inverting input, channel 1.                                                                 |  |  |  |  |  |

| RC2/AN6/       | RC2      | 0                                                                | 0   | DIG         | LATC<2> data output.                                                                                              |  |  |  |  |  |

| C12IN2-/P1D    |          | 1                                                                | ı   | ST          | PORTC<2> data input.                                                                                              |  |  |  |  |  |

|                | AN6      | 1                                                                | ı   | ANA         | A/D input channel 6.                                                                                              |  |  |  |  |  |

|                | C12IN2-  | 1                                                                | ı   | ANA         | Comparators C1 and C2 inverting input, channel 2.                                                                 |  |  |  |  |  |

|                | P1D      | 0                                                                | 0   | DIG         | ECCP1 Enhanced PWM output, channel D.                                                                             |  |  |  |  |  |

| RC3/AN7/       | RC3      | 0                                                                | 0   | DIG         | LATC<3> data output.                                                                                              |  |  |  |  |  |

| C12IN3-/P1C/   |          | 1                                                                | ı   | ST          | PORTC<3> data input.                                                                                              |  |  |  |  |  |

| PGM            | AN7      | 1                                                                | I   | ANA         | A/D input channel 7.                                                                                              |  |  |  |  |  |

|                | C12IN3-  | 12IN3- 1 I ANA Comparators C1 and C2 inverting input, channel 3. |     |             |                                                                                                                   |  |  |  |  |  |

|                | P1C      | 0                                                                | 0   | DIG         | ECCP1 Enhanced PWM output, channel C.                                                                             |  |  |  |  |  |

|                | PGM      | х                                                                | I   | ST          | Single-Supply Programming mode entry (ICSP™). Enabled by LVP Configuration bit; all other pin functions disabled. |  |  |  |  |  |

| RC4/C2OUT/P1B/ | RC4      | 0                                                                | 0   | DIG         | LATC<4> data output.                                                                                              |  |  |  |  |  |

| SRNQ           |          | 1                                                                | I   | ST          | PORTC<4> data input.                                                                                              |  |  |  |  |  |

|                | C2OUT    | 0                                                                | 0   | DIG         | Comparator 2 output.                                                                                              |  |  |  |  |  |

|                | P1B      | 0                                                                | 0   | DIG         | ECCP1 Enhanced PWM output, channel B.                                                                             |  |  |  |  |  |

|                | SRNQ     | 0                                                                | 0   | DIG         | SR Latch inverted output                                                                                          |  |  |  |  |  |

| RC5/CCP1/P1A   | RC5      | 0                                                                | 0   | DIG         | LATC<5> data output.                                                                                              |  |  |  |  |  |

|                |          | 1                                                                | ı   | ST          | PORTC<5> data input.                                                                                              |  |  |  |  |  |

|                | CCP1     | 0                                                                | 0   | DIG         | ECCP1 compare or PWM output.                                                                                      |  |  |  |  |  |

|                |          | 1                                                                | I   | ST          | ECCP1 capture input.                                                                                              |  |  |  |  |  |

|                | P1A      | 0                                                                | 0   | DIG         | ECCP1 Enhanced PWM output, channel A.                                                                             |  |  |  |  |  |

| RC6/AN8/SS     | RC6      | 0                                                                | 0   | DIG         | LATC<6> data output.                                                                                              |  |  |  |  |  |

|                |          | 1                                                                | ı   | ST          | PORTC<6> data input.                                                                                              |  |  |  |  |  |

|                | AN8      | 1                                                                | I   | ANA         | A/D input channel 8.                                                                                              |  |  |  |  |  |

|                | SS       | 1                                                                | ı   | TTL         | Slave select input for SSP (MSSP module)                                                                          |  |  |  |  |  |

| RC7/AN9/SDO    | RC7      | 0                                                                | 0   | DIG         | LATC<7> data output.                                                                                              |  |  |  |  |  |

|                |          | 1                                                                | I   | ST          | PORTC<7> data input.                                                                                              |  |  |  |  |  |

|                | AN9      | 1                                                                | I   | ANA         | A/D input channel 9.                                                                                              |  |  |  |  |  |

|                | SDO      | 0                                                                | 0   | DIG         | SPI data output (MSSP module).                                                                                    |  |  |  |  |  |

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

### 10.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates the following features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable internal or external clock source and Timer1 oscillator options

- · Interrupt-on-overflow

- · Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 10-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 10-2.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 10-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON of the T1CON register.

#### REGISTER 10-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0 | R-0                  | R-0 R/W-0 |         | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|----------------------|-----------|---------|---------|--------|--------|--------|

| RD16  | T1RUN T1CKPS1 T1CKPS |           | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |                      |           |         |         |        |        | bit 0  |

| Legend | • |

|--------|---|

| Legena | • |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 RD16: 16-bit Read/Write Mode Enable bit

1 = Enables register read/write of TImer1 in one 16-bit operation0 = Enables register read/write of Timer1 in two 8-bit operations

bit 6 T1RUN: Timer1 System Clock Status bit

1 = Main system clock is derived from Timer1 oscillator0 = Main system clock is derived from another source

bit 5-4 T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value

bit 3 T10SCEN: Timer1 Oscillator Enable bit

1 = Timer1 oscillator is enabled0 = Timer1 oscillator is shut off

The oscillator inverter and feedback resistor are turned off to eliminate power drain.

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Select bit

When TMR1CS = 1:

1 = Do not synchronize external clock input

0 = Synchronize external clock input

When TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from the T13CKI pin (on the rising edge)

0 = Internal clock (Fosc/4)

bit 0 TMR1ON: Timer1 On bit

1 = Enables Timer1

0 = Stops Timer1

#### 14.2.3 **ENABLING SPI I/O**

To enable the serial port, SSP Enable bit, SSPEN of the SSPCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI is automatically controlled by the SPI module

- · SDO must have corresponding TRIS bit cleared

- · SCK (Master mode) must have corresponding TRIS bit cleared

- · SCK (Slave mode) must have corresponding TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

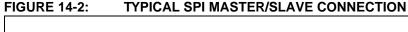

#### 14.2.4 TYPICAL CONNECTION

Figure 14-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- · Master sends dummy data Slave sends data

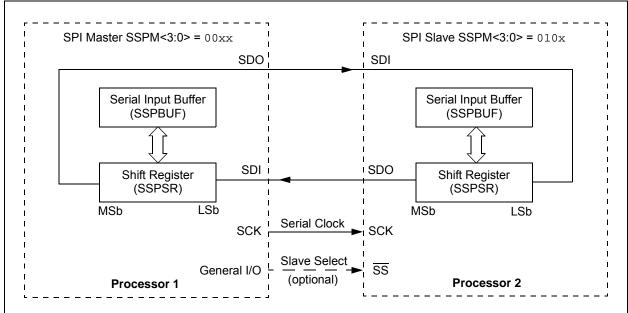

### 14.3.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the SSPADD register (Figure 14-17). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting.

Once the given operation is complete (i.e., transmission of the last data bit is followed by  $\overline{ACK}$ ), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 14-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

### **EQUATION 14-1: CLOCK RATES**

$$FSCL = \frac{FOSC}{(SSPADD + 1)(4)}$$

FIGURE 14-17: BAUD RATE GENERATOR BLOCK DIAGRAM

TABLE 14-3: I<sup>2</sup>C CLOCK RATE W/BRG

| Fosc   | FcY    | BRG Value | FSCL<br>(2 Rollovers of BRG) |

|--------|--------|-----------|------------------------------|

| 48 MHz | 12 MHz | 0Bh       | 1 MHz <sup>(1)</sup>         |

| 48 MHz | 12 MHz | 1Dh       | 400 kHz                      |

| 48 MHz | 12 MHz | 77h       | 100 kHz                      |

| 40 MHz | 10 MHz | 18h       | 400 kHz <sup>(1)</sup>       |

| 40 MHz | 10 MHz | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 09h       | 400 kHz <sup>(1)</sup>       |

| 16 MHz | 4 MHz  | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 02h       | 333 kHz <sup>(1)</sup>       |

| 4 MHz  | 1 MHz  | 09h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 00h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

### 15.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a Vol Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is 8 bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 15-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

### 15.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 15-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 15.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

- Note 1: When the SPEN bit is set the RX/DT I/O pin is automatically configured as an input, regardless of the state of the corresponding TRIS bit and whether or not the EUSART receiver is enabled. The RX/DT pin data can be read via a normal PORT read but PORT latch data output is precluded.

- 2: The TXIF transmitter interrupt flag is set when the TXEN enable bit is set.

### 15.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one Tcy immediately following the Stop bit transmission. The transmission of the Start bit, data bits and Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

### 15.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the CKTXP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the CKTXP bit to '1' will invert the transmit data resulting in low true idle and data bits. The CKTXP bit controls transmit data polarity only in Asynchronous mode. In Synchronous mode the CKTXP bit has a different function.

### 15.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

TABLE 15-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                |                  |                             |                | SYNC             | C = 0, BRGH                 | l = 1, BR0     | <b>316 =</b> 0    |                             |                |                  |                             |  |

|--------|----------------|------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos            | Fosc = 8.000 MHz |                             |                | Fosc = 4.000 MHz |                             |                | Fosc = 3.6864 MHz |                             |                | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | _              | _                | _                           | _              | _                | _                           | _              | _                 | _                           | 300            | 0.16             | 207                         |  |

| 1200   | _              | _                | _                           | 1202           | 0.16             | 207                         | 1200           | 0.00              | 191                         | 1202           | 0.16             | 51                          |  |

| 2400   | 2404           | 0.16             | 207                         | 2404           | 0.16             | 103                         | 2400           | 0.00              | 95                          | 2404           | 0.16             | 25                          |  |

| 9600   | 9615           | 0.16             | 51                          | 9615           | 0.16             | 25                          | 9600           | 0.00              | 23                          | _              | _                | _                           |  |

| 10417  | 10417          | 0.00             | 47                          | 10417          | 0.00             | 23                          | 10473          | 0.53              | 21                          | 10417          | 0.00             | 5                           |  |

| 19.2k  | 19231          | 0.16             | 25                          | 19.23k         | 0.16             | 12                          | 19.2k          | 0.00              | 11                          | _              | _                | _                           |  |

| 57.6k  | 55556          | -3.55            | 8                           | _              | _                | _                           | 57.60k         | 0.00              | 3                           | _              | _                | _                           |  |

| 115.2k | _              | _                | _                           | _              | _                | _                           | 115.2k         | 0.00              | 1                           | _              | _                | _                           |  |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                               |                |                   |                               |                   |            |                               |                |            |                               |

|--------|-------------------------------|------------|-------------------------------|----------------|-------------------|-------------------------------|-------------------|------------|-------------------------------|----------------|------------|-------------------------------|

| BAUD   | Fosc                          | = 48.00    | 0 MHz                         | Fosc           | Fosc = 18.432 MHz |                               | Fosc = 12.000 MHz |            | Fosc = 11.0592 MHz            |                |            |                               |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) |

| 300    | 300.0                         | 0.00       | 9999                          | 300.0          | 0.00              | 3839                          | 300               | 0.00       | 2499                          | 300.0          | 0.00       | 2303                          |

| 1200   | 1200.1                        | 0.00       | 2499                          | 1200           | 0.00              | 959                           | 1200              | 0.00       | 624                           | 1200           | 0.00       | 575                           |

| 2400   | 2400                          | 0.00       | 1249                          | 2400           | 0.00              | 479                           | 2404              | 0.16       | 311                           | 2400           | 0.00       | 287                           |

| 9600   | 9615                          | 0.16       | 311                           | 9600           | 0.00              | 119                           | 9615              | 0.16       | 77                            | 9600           | 0.00       | 71                            |

| 10417  | 10417                         | 0.00       | 287                           | 10378          | -0.37             | 110                           | 10417             | 0.00       | 71                            | 10473          | 0.53       | 65                            |

| 19.2k  | 19.23k                        | 0.16       | 155                           | 19.20k         | 0.00              | 59                            | 19.23k            | 0.16       | 38                            | 19.20k         | 0.00       | 35                            |

| 57.6k  | 57.69k                        | 0.16       | 51                            | 57.60k         | 0.00              | 19                            | 57.69k            | 0.16       | 12                            | 57.60k         | 0.00       | 11                            |

| 115.2k | 115.38k                       | 0.16       | 25                            | 115.2k         | 0.00              | 9                             | _                 | _          | _                             | 115.2k         | 0.00       | 5                             |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                               |                |            |                               |                |            |                               |                  |            |                               |

|--------|-------------------------------|------------|-------------------------------|----------------|------------|-------------------------------|----------------|------------|-------------------------------|------------------|------------|-------------------------------|

| BAUD   | Fos                           | c = 8.000  | ) MHz                         | Fos            | c = 4.000  | ) MHz                         | Fosc           | = 3.686    | 4 MHz                         | Fosc = 1.000 MHz |            |                               |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRGH<br>:SPBRG<br>(decimal) |

| 300    | 299.9                         | -0.02      | 1666                          | 300.1          | 0.04       | 832                           | 300.0          | 0.00       | 767                           | 300.5            | 0.16       | 207                           |

| 1200   | 1199                          | -0.08      | 416                           | 1202           | 0.16       | 207                           | 1200           | 0.00       | 191                           | 1202             | 0.16       | 51                            |

| 2400   | 2404                          | 0.16       | 207                           | 2404           | 0.16       | 103                           | 2400           | 0.00       | 95                            | 2404             | 0.16       | 25                            |

| 9600   | 9615                          | 0.16       | 51                            | 9615           | 0.16       | 25                            | 9600           | 0.00       | 23                            | _                | _          | _                             |

| 10417  | 10417                         | 0.00       | 47                            | 10417          | 0.00       | 23                            | 10473          | 0.53       | 21                            | 10417            | 0.00       | 5                             |

| 19.2k  | 19.23k                        | 0.16       | 25                            | 19.23k         | 0.16       | 12                            | 19.20k         | 0.00       | 11                            | _                | _          | _                             |

| 57.6k  | 55556                         | -3.55      | 8                             | _              | _          | _                             | 57.60k         | 0.00       | 3                             | _                | _          | _                             |

| 115.2k | _                             |            | _                             | _              | _          | _                             | 115.2k         | 0.00       | 1                             | _                | _          | _                             |

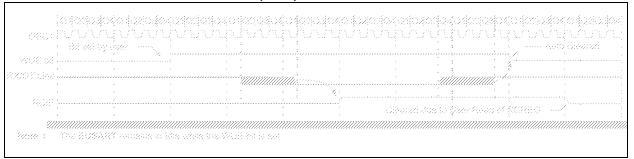

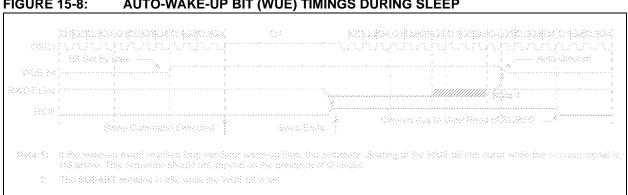

#### **AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION FIGURE 15-7:**

#### **FIGURE 15-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP**

TABLE 22-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Address | Power-on Reset,<br>Brown-out Reset | MCLR Resets, WDT Reset, RESET Instruction, Stack Resets | Wake-up via WDT<br>or Interrupt |

|----------|---------|------------------------------------|---------------------------------------------------------|---------------------------------|

| IPR2     | FA2h    | 1111 1-1-                          | 1111 1-1-                                               | uuuu u-u-                       |

| PIR2     | FA1h    | 0000 0-0-                          | 0000 0-0-                                               | uuuu u-u-(1)                    |

| PIE2     | FA0h    | 0000 0-0-                          | 0000 0-0-                                               | uuuu u-u-                       |

| IPR1     | F9Fh    | -111 1111                          | -111 1111                                               | -uuu uuuu                       |

| PIR1     | F9Eh    | -000 0000                          | -000 0000                                               | -uuu uuuu <b>(1)</b>            |

| PIE1     | F9Dh    | -000 0000                          | -000 0000                                               | -uuu uuuu                       |

| OSCTUNE  | F9Bh    | 0000 0000                          | 0000 0000                                               | uuuu uuuu                       |

| TRISC    | F95h    | 1111 1111                          | 1111 1111                                               | uuuu uuuu                       |

| TRISB    | F94h    | 1111                               | 1111                                                    | uuuu                            |

| TRISA    | F93h    | 11 1111                            | 11 1111                                                 | uu uuuu                         |

| LATC     | F8Bh    | xxxx xxxx                          | uuuu uuuu                                               | uuuu uuuu                       |

| LATB     | F8Ah    | xxxx                               | uuuu                                                    | uuuu                            |

| LATA     | F89h    | xx xxxx                            | uu uuuu                                                 | uu uuuu                         |

| PORTC    | F82h    | xxxx xxxx                          | uuuu uuuu                                               | uuuu uuuu                       |

| PORTB    | F81h    | xxxx                               | uuuu                                                    | uuuu                            |

| PORTA    | F80h    | xx xxxx                            | xx xxxx                                                 | uu uuuu                         |

| ANSELH   | F7Fh    | 1111                               | 1111                                                    | uuuu                            |

| ANSEL    | F7Eh    | 1111 1111                          | 1111 1111                                               | uuuu uuuu                       |

| IOCB     | F7Ah    | 0000                               | 0000                                                    | uuuu                            |

| IOCA     | F79h    | 00 0000                            | 00 0000                                                 | uu uuuu                         |

| WPUB     | F78h    | 1111                               | 1111                                                    | uuuu                            |

| WPUA     | F77h    | 11 1111                            | 11 1111                                                 | uu uuuu                         |

| SLRCON   | F76h    | 111                                | 111                                                     | uuu                             |

| SSPMSK   | F6Fh    | 1111 1111                          | 1111 1111                                               | uuuu uuuu                       |

| CM1CON0  | F6Dh    | 0000 0000                          | 0000 0000                                               | uuuu uuuu                       |

| CM2CON1  | F6Ch    | 0000 0000                          | 0000 0000                                               | uuuu uuuu                       |

| CM2CON0  | F6Bh    | 0000 0000                          | 0000 0000                                               | uuuu uuuu                       |

| SRCON1   | F69h    | 0000 0000                          | 0000 0000                                               | uuuu uuuu                       |

| SRCON0   | F68h    | 0000 0000                          | 0000 0000                                               | uuuu uuuu                       |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 22-3 for Reset value for specific condition.

| COMF              | Compler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nent f    |      |      |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|--|--|

| Syntax:           | COMF f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | {,d {,a}} |      |      |  |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5         |      |      |  |  |

| Operation:        | $(\overline{f}) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t         |      |      |  |  |

| Status Affected:  | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |      |      |  |  |

| Encoding:         | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11da      | ffff | ffff |  |  |

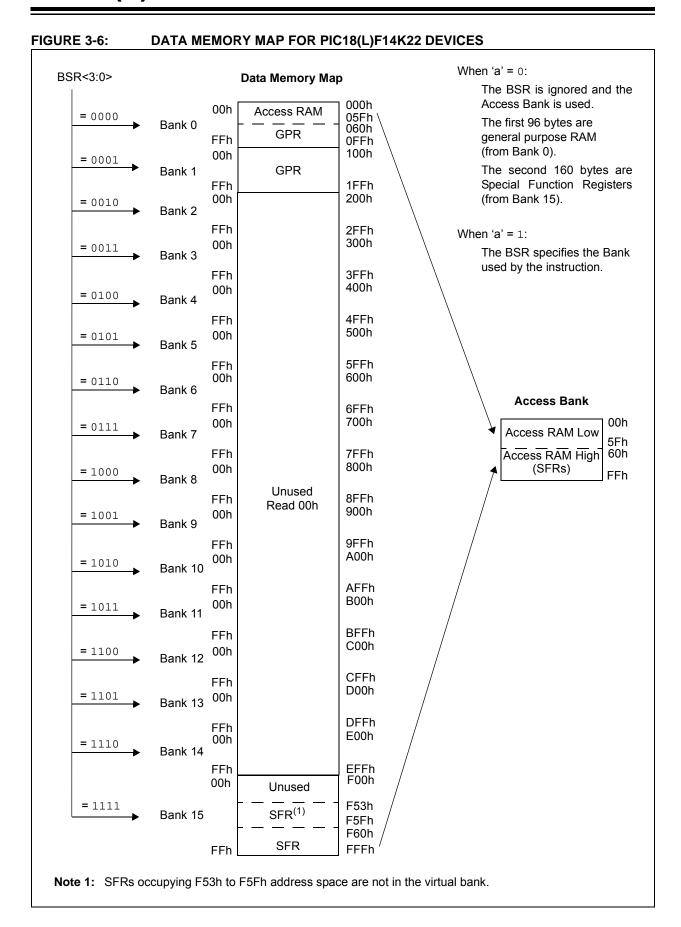

| Description:      | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f' (default). If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |           |      |      |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |      |      |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |      |      |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |      |      |  |  |

| Ω1                | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ω3        | 3    | Ω4   |  |  |

|                    |     | register 'f' | Da   | ata | destination |

|--------------------|-----|--------------|------|-----|-------------|

|                    |     |              |      |     |             |

| Example:           |     | COMF         | REG, | 0,0 |             |

| Before Instruction |     |              |      |     |             |

|                    | RFG | = 13h        |      |     |             |

Read

Process

Write to

After Instruction REG 13h ECh

Decode

| CPFSEQ Compare f with W, skip if f = W |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |           |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| Syntax:                                | CPFSEQ                                                                                                                                                                                                                               | f {,a}                                                                                                                                                                                                                   |           |  |  |  |

| Operands:                              | $0 \le f \le 255$                                                                                                                                                                                                                    |                                                                                                                                                                                                                          |           |  |  |  |

|                                        | $a \in [0,1]$                                                                                                                                                                                                                        |                                                                                                                                                                                                                          |           |  |  |  |

| Operation:                             | (f) - (W),                                                                                                                                                                                                                           | 0.4.0                                                                                                                                                                                                                    |           |  |  |  |

|                                        | skip if (f) = (<br>(unsigned o                                                                                                                                                                                                       |                                                                                                                                                                                                                          |           |  |  |  |

| Status Affected:                       | None                                                                                                                                                                                                                                 |                                                                                                                                                                                                                          |           |  |  |  |

| Encoding:                              | 0110                                                                                                                                                                                                                                 | 001a fff                                                                                                                                                                                                                 | f ffff    |  |  |  |

| Description:                           | location 'f' to<br>performing<br>If 'f' = W, th<br>discarded a<br>instead, ma<br>instruction.<br>If 'a' is '0', th<br>If 'a' is '1', th<br>GPR bank (<br>If 'a' is '0' an<br>set is enabl<br>in Indexed I<br>mode when<br>Section 24 | Compares the contents of data memory location 'f' to the contents of W by performing an unsigned subtraction. If 'f' = W, then the fetched instruction is discarded and a NOP is executed instead, making this a 2-cycle |           |  |  |  |

| Words:                                 | 1                                                                                                                                                                                                                                    |                                                                                                                                                                                                                          |           |  |  |  |

| Cycles:                                |                                                                                                                                                                                                                                      | ycles if skip an<br>a 2-word instru                                                                                                                                                                                      |           |  |  |  |

| Q Cycle Activity:                      |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |           |  |  |  |

| Q1                                     | Q2                                                                                                                                                                                                                                   | Q3                                                                                                                                                                                                                       | Q4        |  |  |  |

| Decode                                 | Read                                                                                                                                                                                                                                 | Process                                                                                                                                                                                                                  | No        |  |  |  |

|                                        | register 'f'                                                                                                                                                                                                                         | Data                                                                                                                                                                                                                     | operation |  |  |  |

| If skip:                               |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |           |  |  |  |

| Q1                                     | Q2                                                                                                                                                                                                                                   | Q3                                                                                                                                                                                                                       | Q4        |  |  |  |

| No                                     | No                                                                                                                                                                                                                                   | No                                                                                                                                                                                                                       | No        |  |  |  |

| operation                              | operation                                                                                                                                                                                                                            | operation                                                                                                                                                                                                                | operation |  |  |  |

| If skip and followe                    | d by 2-word in:                                                                                                                                                                                                                      | struction:                                                                                                                                                                                                               | 04        |  |  |  |

| IT SK                                       | ıp:       |           |           |           |  |  |

|---------------------------------------------|-----------|-----------|-----------|-----------|--|--|

|                                             | Q1        | Q2        | Q3        | Q4        |  |  |

|                                             | No        | No        | No        | No        |  |  |

|                                             | operation | operation | operation | operation |  |  |

| If skip and followed by 2-word instruction: |           |           |           |           |  |  |

|                                             | Q1        | Q2        | Q3        | Q4        |  |  |

|                                             | No        | No        | No        | No        |  |  |

|                                             |           |           |           |           |  |  |

| <u> </u>  | QZ        | ŲS        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

| No        | No        | No        | No        |

| operation | operation | operation | operation |

Example: CPFSEQ REG, 0 NEQUAL EQUAL

Before Instruction

PC Address HERE W ? REG

After Instruction

If REG W;

Address (EQUAL)

If REG

Address (NEQUAL)

**MOVLW** Move literal to W

Syntax: MOVLW k Operands:  $0 \le k \le 255$

Operation:  $\mathsf{k}\to\mathsf{W}$ Status Affected: None

Encoding: 0000 1110 kkkk kkkk

Description: The 8-bit literal 'k' is loaded into W.

Words: Cycles: 1

Q Cycle Activity:

| Q1     | Q2          | Q3      | Q4         |

|--------|-------------|---------|------------|

| Decode | Read        | Process | Write to W |

|        | literal 'k' | Data    |            |

Example: MOVLW 5Ah

After Instruction

W 5Ah

| MOVWF            | Move W to f                        |

|------------------|------------------------------------|

| Syntax:          | MOVWF f {,a}                       |

| Operands:        | $0 \le f \le 255$<br>$a \in [0,1]$ |

| Operation:       | $(W) \rightarrow f$                |

| Status Affected: | None                               |

| Encoding:        | 0110 llla ffff ffff                |

| Description:     | Move data from W to register 'f'.  |

Location 'f' can be anywhere in the 256-byte bank.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

If 'a' is '0' and the extended instruction

GPR bank (default).

set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 24.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed**

Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: MOVWF REG, 0

Before Instruction

4Fh REG FFh

After Instruction

W 4Fh REG 4Fh

| POP | Pop Top | of Return Stack |

|-----|---------|-----------------|

|-----|---------|-----------------|

Syntax: POP

Operands: None

Operation:  $(TOS) \rightarrow bit bucket$

Status Affected: None

Encoding: 0000 0000 0000 0110

Description:

The TOS value is pulled off the return stack and is discarded. The TOS value then becomes the previous value that was pushed onto the return stack.