Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf13k22-e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Example 6-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 6-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES<3:0>).

#### EQUATION 6-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L                |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | (ARG1L • ARG2L)                          |

|           |   |                                          |

#### EXAMPLE 6-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ;                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| L |        |             |                   |

Example 6-4 shows the sequence to do a 16 x 16 signed multiply. Equation 6-2 shows the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 6-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L                                        |

|-----------|---|------------------------------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$                         |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$                            |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$                            |

|           |   | $(ARG1L \bullet ARG2L) +$                                        |

|           |   | $(-1 \bullet ARG2H < 7 > \bullet ARG1H: ARG1L \bullet 2^{16}) +$ |

|           |   | $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$    |

|           |   |                                                                  |

## EXAMPLE 6-4:

#### 16 x 16 SIGNED MULTIPLY ROUTINE

| MOVF           | ARG1L, W          |                    |

|----------------|-------------------|--------------------|

| MULWF          | ARG2L             | ; ARG1L * ARG2L -> |

|                |                   | ; PRODH:PRODL      |

| MOVFF          | PRODH, RES1       | ;                  |

| MOVFF          | PRODL, RESO       | ;                  |

| ;              |                   |                    |

| MOVF           | ARG1H, W          |                    |

| MULWF          | ARG2H             | ; ARG1H * ARG2H -> |

|                |                   | ; PRODH:PRODL      |

| MOVEE          | PRODH, RES3       |                    |

| MOVFF          |                   |                    |

| ;              | FRODE, RESZ       | 1                  |

| MOVF           | ADC11 W           |                    |

|                | ARG1L, W<br>ARG2H |                    |

| MOTME          | ARGZH             | ; ARG1L * ARG2H -> |

|                |                   | ; PRODH:PRODL      |

|                | PRODL, W          | ;                  |

| ADDWF          | RES1, F           | ; Add cross        |

| MOVF           |                   | ; products         |

|                | RES2, F           | ;                  |

| CLRF           | WREG              | ;                  |

| ADDWFC         | RES3, F           | ;                  |

| ;              |                   |                    |

| MOVF           | ARG1H, W          | ;                  |

| MULWF          | ARG2L             | ; ARG1H * ARG2L -> |

|                |                   | ; PRODH:PRODL      |

| MOVF           | PRODL, W          | ;                  |

| ADDWF          | RES1, F           | ; Add cross        |

| MOVF           | PRODH, W          | ; products         |

|                | RES2, F           | ;                  |

| CLRF           | WREG              | ;                  |

| ADDWFC         | RES3, F           | ;                  |

| ;              |                   |                    |

| BTFSS          | ARG2H, 7          | ; ARG2H:ARG2L neg? |

| BRA            | ,<br>SIGN ARG1    | ; no, check ARG1   |

| MOVF           | ARG1L, W          | ;                  |

| SUBWF          | RES2              | ;                  |

| MOVF           | ARG1H, W          | i                  |

| SUBWFB         |                   |                    |

| ;              | 1.000             |                    |

| ,<br>SIGN ARG1 |                   |                    |

| BTFSS          | ARG1H, 7          | ; ARG1H:ARG1L neg? |

| BIF55<br>BRA   |                   |                    |

|                | CONT_CODE         | ; no, done<br>;    |

| MOVF           | ARG2L, W          |                    |

| SUBWF          | RES2              | ;                  |

| MOVF           | ARG2H, W          | ;                  |

| SUBWFB         | RES3              |                    |

| ;              |                   |                    |

| CONT_CODE      |                   |                    |

| :              |                   |                    |

|                |                   |                    |

## 9.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 9-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 9-1. Figure 9-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

#### **REGISTER 9-1:** TOCON: TIMERO CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR0ON | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:      |                                                      |                                                                              |                              |                    |  |  |  |

|--------------|------------------------------------------------------|------------------------------------------------------------------------------|------------------------------|--------------------|--|--|--|

| R = Readal   | ole bit                                              | W = Writable bit                                                             | U = Unimplemented bit,       | read as '0'        |  |  |  |

| -n = Value a | at POR                                               | '1' = Bit is set                                                             | '0' = Bit is cleared         | x = Bit is unknown |  |  |  |

|              |                                                      |                                                                              |                              |                    |  |  |  |

| bit 7        | TMR0ON                                               | : Timer0 On/Off Control bit                                                  |                              |                    |  |  |  |

|              |                                                      | es Timer0                                                                    |                              |                    |  |  |  |

|              | 0 = Stops                                            | Timer0                                                                       |                              |                    |  |  |  |

| bit 6        | <b>T08BIT</b> : ⊤                                    | imer0 8-bit/16-bit Control bi                                                | t                            |                    |  |  |  |

|              |                                                      | 0 is configured as an 8-bit ti                                               |                              |                    |  |  |  |

|              | 0 = Timer                                            | 0 is configured as a 16-bit ti                                               | mer/counter                  |                    |  |  |  |

| bit 5        | TOCS: Tin                                            | ner0 Clock Source Select bi                                                  | t                            |                    |  |  |  |

|              | 1 = Trans                                            | ition on T0CKI pin                                                           |                              |                    |  |  |  |

|              | 0 = Intern                                           | al instruction cycle clock (C                                                | LKOUT)                       |                    |  |  |  |

| bit 4        | TOSE: Timer0 Source Edge Select bit                  |                                                                              |                              |                    |  |  |  |

|              | 1 = Increment on high-to-low transition on TOCKI pin |                                                                              |                              |                    |  |  |  |

|              | 0 = Increr                                           | ment on low-to-high transitio                                                | n on T0CKI pin               |                    |  |  |  |

| bit 3        | PSA: Timer0 Prescaler Assignment bit                 |                                                                              |                              |                    |  |  |  |

|              |                                                      | 1 = TImer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler. |                              |                    |  |  |  |

|              | 0 = Timer                                            | 0 prescaler is assigned. Tim                                                 | er0 clock input comes from p | rescaler output.   |  |  |  |

| bit 2-0      | T0PS<2:0                                             | )>: Timer0 Prescaler Select                                                  | bits                         |                    |  |  |  |

|              |                                                      | 56 prescale value                                                            |                              |                    |  |  |  |

|              |                                                      | 28 prescale value                                                            |                              |                    |  |  |  |

|              |                                                      | 4 prescale value                                                             |                              |                    |  |  |  |

|              |                                                      | 2 prescale value                                                             |                              |                    |  |  |  |

|              |                                                      | 6 prescale value<br>prescale value                                           |                              |                    |  |  |  |

|              |                                                      | prescale value                                                               |                              |                    |  |  |  |

|              |                                                      | prescale value                                                               |                              |                    |  |  |  |

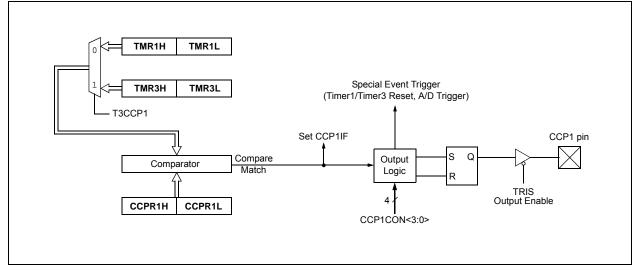

## 13.3 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCP1 pin can be:

- Driven high

- Driven low

- Toggled (high-to-low or low-to-high)

- Remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP1M<3:0>). At the same time, the interrupt flag bit, CCP1IF, is set.

#### 13.3.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRIS bit.

| Note: | Clea                                       | ring the C | CCP1CON r | egister wil | II force |

|-------|--------------------------------------------|------------|-----------|-------------|----------|

|       | the                                        | CCP1       | compare   | output      | latch    |

|       | (depending on device configuration) to the |            |           |             |          |

|       | default low level. This is not the PORTC   |            |           |             | ORTC     |

|       | 1/0 E                                      | DATA late  | ch.       |             |          |

#### 13.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation will not work reliably.

#### 13.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the CCP1 pin is not affected. Only the CCP1IF interrupt flag is affected.

#### 13.3.4 SPECIAL EVENT TRIGGER

The CCP module is equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP1M<3:0> = 1011).

The Special Event Trigger resets the timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPR1 registers to serve as a programmable period register for either timer.

The Special Event Trigger can also start an A/D conversion. In order to do this, the A/D converter must already be enabled.

#### FIGURE 13-2: COMPARE MODE OPERATION BLOCK DIAGRAM

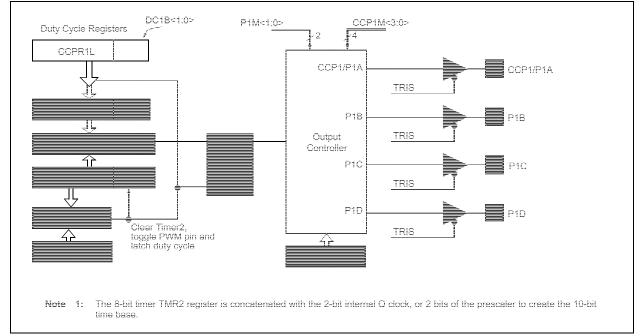

## 13.4 PWM (Enhanced Mode)

The Enhanced PWM mode can generate a PWM signal on up to four different output pins with up to 10-bits of resolution. It can do this through four different PWM output modes:

- Single PWM

- · Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 13-1 shows the pin assignments for each Enhanced PWM mode.

Figure 13-3 shows an example of a simplified block diagram of the Enhanced PWM module.

**Note:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 13-3: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

**Note 1:** The TRIS register value for each PWM output must be configured appropriately.

2: Any pin not used by an Enhanced PWM mode is available for alternate pin functions.

#### TABLE 13-2: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode            | P1M<1:0> | CCP1/P1A           | P1B                | P1C                | P1D                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

Note 1: Outputs are enabled by pulse steering in Single mode. See Register 13-4.

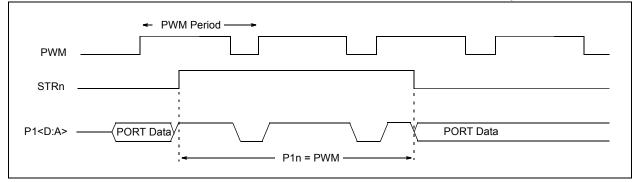

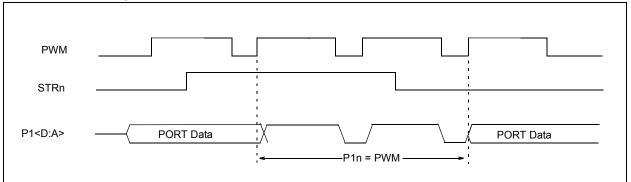

#### 13.4.7.1 Steering Synchronization

The STRSYNC bit of the PSTRCON register gives the user two selections of when the steering event will happen. When the STRSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRCON register. In this case, the output signal at the P1<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STRSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 13-17 and 13-18 illustrate the timing diagrams of the PWM steering depending on the STRSYNC setting.

#### FIGURE 13-17: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRSYNC = 0)

#### FIGURE 13-18: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRSYNC = 1)

#### 14.2.3 ENABLING SPI I/O

To enable the serial port, SSP Enable bit, SSPEN of the SSPCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the <u>SSPEN</u> bit. This configures the SDI, SDO, SCK and <u>SS</u> pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDI is automatically controlled by the SPI module

- · SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding

TRIS bit cleared

- SCK (Slave mode) must have corresponding

TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

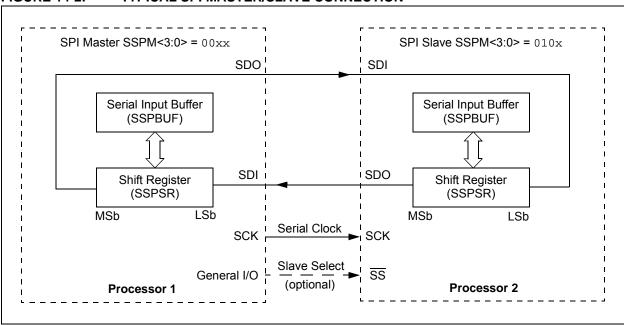

## 14.2.4 TYPICAL CONNECTION

Figure 14-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 14-2: TYPICAL SPI MASTER/SLAVE CONNECTION

#### 14.2.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 14-2) is to broadcast data by the software protocol.

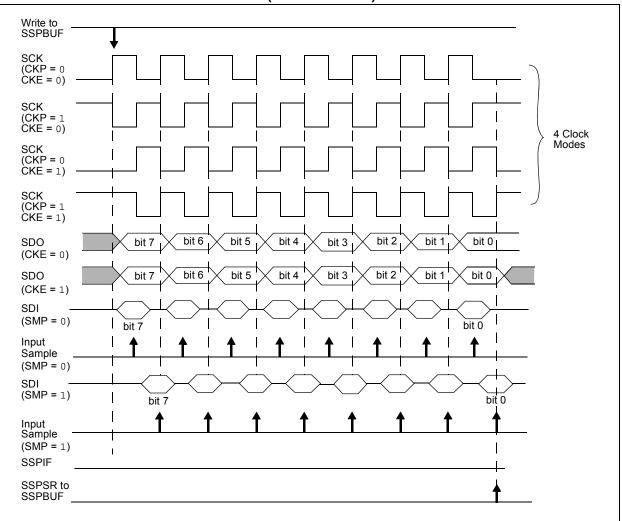

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register. This then, would give waveforms for SPI communication as shown in Figure 14-3, Figure 14-5 and Figure 14-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- · Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 64 MHz) of 16.00 Mbps.

Figure 14-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 14-3: SPI MODE WAVEFORM (MASTER MODE)

## 15.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRG register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF Interrupt Flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 15.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 15-7), and asynchronously if the device is in Sleep mode (Figure 15-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 15.3.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared by hardware by a rising edge on RX/DT. The interrupt condition is then cleared by software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

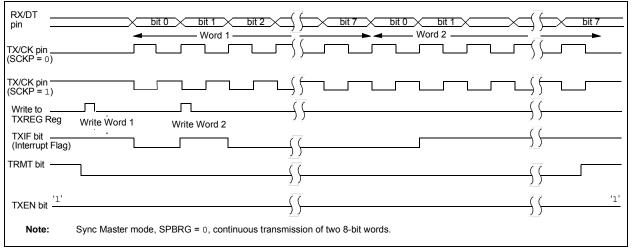

## 15.4.1.5 Synchronous Master Transmission Set-up

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 15.3 "EUSART Baud Rate Generator (BRG)").

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RX/DT and TX/CK I/O pins.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE, GIE and PEIE interrupt enable bits.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

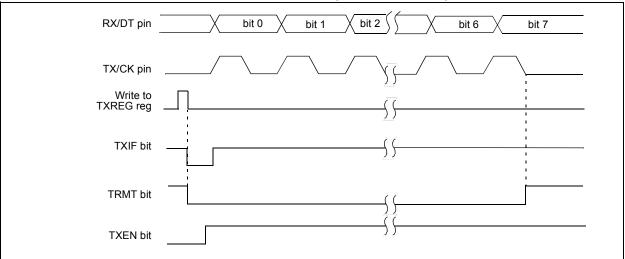

#### FIGURE 15-10: SYNCHRONOUS TRANSMISSION

#### FIGURE 15-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

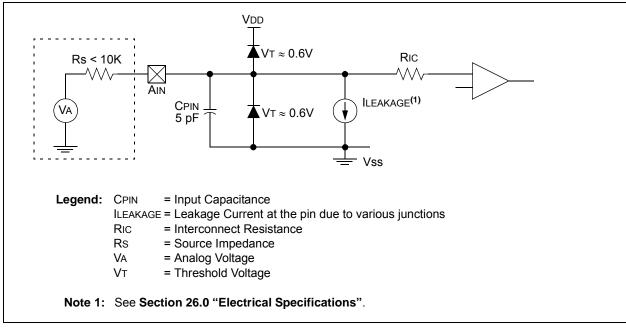

## 17.7 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 17-6. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### FIGURE 17-6: ANALOG INPUT MODEL

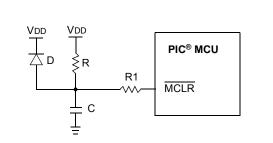

## 22.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In PIC18(L)F1XK22 devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. See **Section 8.1 "PORTA, TRISA and LATA Registers"** for more information.

## 22.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the POR bit of the RCON register. The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event. POR is not reset to '1' by any hardware event. To capture multiple events, the user must manually set the bit to '1' by software following any POR.

#### FIGURE 22-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3:  $\underline{R1 \ge 1} \ k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C, in the event of  $\overline{MCLR}/VPP$  pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

| Parts and starts of file and states of the                                                                                                                                                                                                                    |                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Byte-oriented file register operations                                                                                                                                                                                                                        | Example Instruction  |

| 15 10 9 8 7 0<br>OPCODE d a f(FILE #)                                                                                                                                                                                                                         |                      |

| OPCODE     d     a     f (FILE #)       d = 0 for result destination to be WREG register       d = 1 for result destination to be file register (f)       a = 0 to force Access Bank       a = 1 for BSR to select bank       f = 8-bit file register address | ADDWF MYREG, W, B    |

| -                                                                                                                                                                                                                                                             |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                         |                      |

| 15 12 11 0<br>OPCODE f (Source FILE #)                                                                                                                                                                                                                        |                      |

|                                                                                                                                                                                                                                                               | MOVFF MYREG1, MYREG2 |

| 15 12 11 0<br>1111 f (Destination FILE #)                                                                                                                                                                                                                     |                      |

|                                                                                                                                                                                                                                                               |                      |

| f = 12-bit file register address                                                                                                                                                                                                                              |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                         |                      |

| 15 12 11 9 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                                 | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                         |                      |

| Literal operations                                                                                                                                                                                                                                            |                      |

| 15 8 7 0                                                                                                                                                                                                                                                      |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                            | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                                     |                      |

|                                                                                                                                                                                                                                                               |                      |

| Control operations                                                                                                                                                                                                                                            |                      |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                              |                      |

| 15 8 7 0                                                                                                                                                                                                                                                      |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                                       | GOTO Label           |

| 15 12 11 0<br>1111 n<19:8> (literal)                                                                                                                                                                                                                          |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                        |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                                    |                      |

| <u>15 8 7 0</u>                                                                                                                                                                                                                                               |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                                     | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                                    |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                        |                      |

| S = Fast bit                                                                                                                                                                                                                                                  |                      |

| 15 11 10 0                                                                                                                                                                                                                                                    |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                                      | BRA MYFUNC           |

|                                                                                                                                                                                                                                                               |                      |

|                                                                                                                                                                                                                                                               |                      |

| <u>15 8 7 0</u>                                                                                                                                                                                                                                               |                      |

# PIC18(L)F1XK22

| COMF                 | Complement f                                                 |             | CPFSEQ              | Compare                        | f with W, sk                      | tip if f = W    |

|----------------------|--------------------------------------------------------------|-------------|---------------------|--------------------------------|-----------------------------------|-----------------|

| Syntax:              | COMF f {,d {,a}}                                             |             | Syntax:             | CPFSEQ                         | f {,a}                            |                 |

| Operands:            | 0 ≤ f ≤ 255                                                  |             | Operands:           | $0 \leq f \leq 255$            |                                   |                 |

|                      | $d \in [0,1]$                                                |             |                     | <b>a</b> ∈ [0,1]               |                                   |                 |

|                      | <b>a</b> ∈ [0,1]                                             |             | Operation:          | (f) – (W),                     |                                   |                 |

| Operation:           | $(f) \rightarrow dest$                                       |             |                     | skip if (f) = (<br>(unsigned c | (W)<br>comparison)                |                 |

| Status Affected:     | N, Z                                                         |             | Status Affected:    | None                           | ,ompaneon)                        |                 |

| Encoding:            | 0001 11da ff:                                                | f ffff      | Encoding:           | 0110                           | 001a ffi                          | ff ffff         |

| Description:         | The contents of register '                                   | ' are       | Description:        |                                |                                   | f data memory   |

|                      | complemented. If 'd' is '0'                                  |             | Description         |                                | o the contents                    |                 |

|                      | stored in W. If 'd' is '1', th                               |             |                     |                                | an unsigned s                     |                 |

|                      | stored back in register 'f'<br>If 'a' is '0', the Access Ba  |             |                     | -                              | en the fetched                    |                 |

|                      | If 'a' is '1', the BSR is use                                |             |                     |                                | nd a NOP is ex<br>king this a 2-c |                 |

|                      | GPR bank (default).                                          |             |                     | instruction.                   |                                   | ycie            |

|                      | If 'a' is '0' and the extend                                 |             |                     | lf 'a' is '0', t               | he Access Bar                     | nk is selected. |

|                      | set is enabled, this instruction in Indexed Literal Offset A | •           |                     | , -                            |                                   | d to select the |

|                      | mode whenever $f \le 95$ (5)                                 | -           |                     | GPR bank                       | (default).                        | ed instruction  |

|                      | Section 24.2.3 "Byte-Or                                      |             |                     |                                | ed, this instruc                  |                 |

|                      | Bit-Oriented Instruction<br>Literal Offset Mode" for         |             |                     | in Indexed                     | Literal Offset A                  | Addressing      |

|                      |                                                              | details.    |                     |                                | ever $f \le 95$ (5)               |                 |

| Words:               | 1                                                            |             |                     |                                | .2.3 "Byte-Ori<br>d Instruction   |                 |

| Cycles:              | 1                                                            |             |                     |                                | set Mode" for                     |                 |

| Q Cycle Activity:    |                                                              |             | Words:              | 1                              |                                   |                 |

| Q1                   | Q2 Q3                                                        | Q4          | Cycles:             | 1(2)                           |                                   |                 |

| Decode               | Read Process                                                 | Write to    |                     |                                | ycles if skip an                  |                 |

|                      | register 'f' Data                                            | destination |                     | by a                           | a 2-word instru                   | uction.         |

| Evenale              |                                                              |             | Q Cycle Activity:   |                                |                                   |                 |

| Example:             | COMF REG, 0, 0                                               |             | Q1                  | Q2                             | Q3                                | Q4              |

| Before Instru<br>REG | = 13h                                                        |             | Decode              | Read<br>register 'f'           | Process<br>Data                   | No<br>operation |

| After Instruct       |                                                              |             | lf skip:            |                                | Data                              | operation       |

| REG                  | = 13h                                                        |             | Q1                  | Q2                             | Q3                                | Q4              |

| W                    | = ECh                                                        |             | No                  | No                             | No                                | No              |

|                      |                                                              |             | operation           | operation                      | operation                         | operation       |

|                      |                                                              |             | If skip and followe | ,                              |                                   | 04              |

|                      |                                                              |             | Q1<br>No            | Q2<br>No                       | Q3<br>No                          | Q4<br>No        |

|                      |                                                              |             | operation           | operation                      | operation                         | operation       |

|                      |                                                              |             | No                  | No                             | No                                | No              |

|                      |                                                              |             | operation           | operation                      | operation                         | operation       |

|                      |                                                              |             | Example:            | HERE                           | CPFSEQ REG                        | B, 0            |

|                      |                                                              |             |                     | NEQUAL                         | : ~                               |                 |

|                      |                                                              |             |                     | EQUAL                          | :                                 |                 |

|                      |                                                              |             | Before Instruc      |                                |                                   |                 |

|                      |                                                              |             | PC Addr             |                                | RE                                |                 |

|                      |                                                              |             | W<br>REG            | = ?<br>= ?                     |                                   |                 |

|                      |                                                              |             | After Instruction   |                                |                                   |                 |

|                      |                                                              |             | If REG              | = W;                           |                                   |                 |

| If REG | = | W;      |          |

|--------|---|---------|----------|

| PC     | = | Address | (EQUAL)  |

| If REG | ≠ | W;      |          |

| PC     | = | Address | (NEQUAL) |

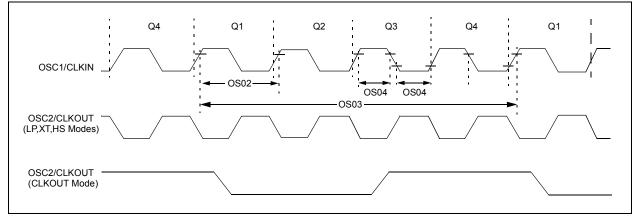

## 26.5 AC Characteristics: PIC18(L)F1XK22-I/E

#### FIGURE 26-8: CLOCK TIMING

| Param.<br>No. | Symbol  | Characteristic             |              | Min.          | Max.     | Units | Conditions                                                            |  |

|---------------|---------|----------------------------|--------------|---------------|----------|-------|-----------------------------------------------------------------------|--|

| SP100*        | Тнідн   | Clock high time            | 100 kHz mode | 4.0           | _        | μS    | Device must operate at a minimum of 1.5 MHz                           |  |

|               |         |                            | 400 kHz mode | 0.6           | _        | μS    | Device must operate at a minimum of 10 MHz                            |  |

|               |         |                            | SSP Module   | 1.5Tcy        | —        |       |                                                                       |  |

| SP101*        | TLOW    | Clock low time             | 100 kHz mode | 4.7           | _        | μS    | Device must operate at a minimum of 1.5 MHz                           |  |

|               |         |                            | 400 kHz mode | 1.3           | _        | μS    | Device must operate at a minimum of 10 MHz                            |  |

|               |         |                            | SSP Module   | 1.5Tcy        | —        |       |                                                                       |  |

| SP102*        | TR      | SDA and SCL rise time      | 100 kHz mode | —             | 1000     | ns    |                                                                       |  |

|               |         |                            | 400 kHz mode | 20 +<br>0.1Св | 300      | ns    | CB is specified to be from 10-400 pF                                  |  |

| SP103*        | TF      | SDA and SCL fall time      | 100 kHz mode | —             | 250      | ns    |                                                                       |  |

|               |         |                            | 400 kHz mode | 20 +<br>0.1Св | 250      | ns    | CB is specified to be from 10-400 pF                                  |  |

| SP90*         | Tsu:sta | Start condition setup time | 100 kHz mode | 4.7           | —        | μS    | Only relevant for                                                     |  |

|               |         |                            | 400 kHz mode | 0.6           | —        | μS    | Repeated Start condition                                              |  |

| SP91*         | THD:STA | Start condition hold time  | 100 kHz mode | 4.0           |          | μS    | After this period the first clock pulse is generated                  |  |

|               |         |                            | 400 kHz mode | 0.6           | —        | μS    |                                                                       |  |

| SP106*        | THD:DAT | Data input hold time       | 100 kHz mode | 0             | —        | ns    |                                                                       |  |

|               |         |                            | 400 kHz mode | 0             | 0.9      | μS    |                                                                       |  |

| SP107*        | TSU:DAT | Data input setup<br>time   | 100 kHz mode | 250           |          | ns    | (Note 2)                                                              |  |

|               |         |                            | 400 kHz mode | 100           |          | ns    |                                                                       |  |

| SP92*         | Tsu:sto | Stop condition setup time  | 100 kHz mode | 4.7           |          | μS    |                                                                       |  |

|               |         |                            | 400 kHz mode | 0.6           |          | μS    |                                                                       |  |

| SP109*        | ΤΑΑ     | Output valid from clock    | 100 kHz mode | —             | 3500     | ns    | (Note 1)                                                              |  |

|               |         |                            | 400 kHz mode | —             | <u> </u> | ns    |                                                                       |  |

| SP110*        | TBUF    | Bus free time              | 100 kHz mode | 4.7           | _        | μS    | Time the bus must be free<br>before a new transmis-<br>sion can start |  |

|               |         |                            | 400 kHz mode | 1.3           | _        | μS    |                                                                       |  |

| SP            | Св      | Bus capacitive loadi       | ng           | —             | 400      | pF    |                                                                       |  |

## TABLE 26-28: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

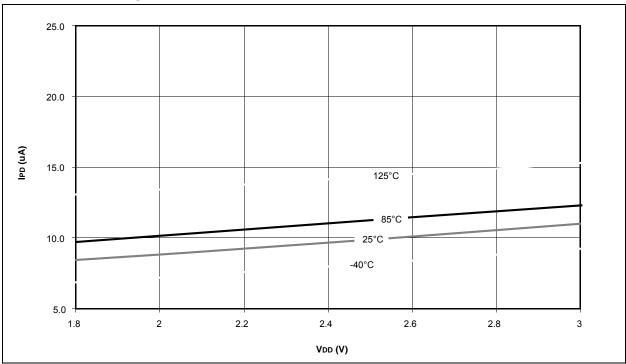

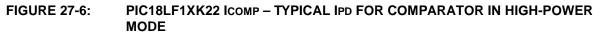

FIGURE 27-5: PIC18LF1XK22 ICOMP – TYPICAL IPD FOR COMPARATOR IN LOW-POWER MODE

# PIC18(L)F1XK22

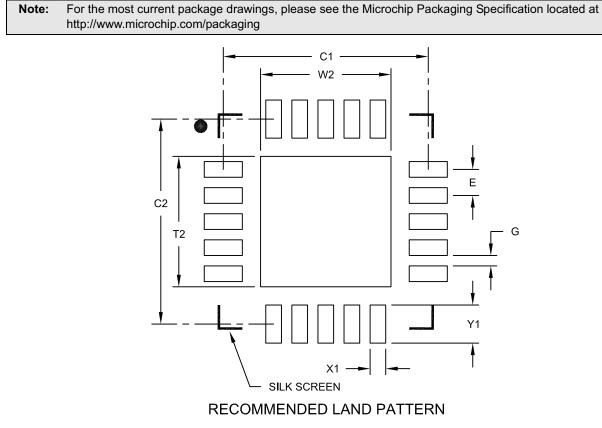

20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

|                            | MILLIMETERS |      |          |      |  |

|----------------------------|-------------|------|----------|------|--|

| Dimensio                   | MIN         | NOM  | MAX      |      |  |

| Contact Pitch              | E           |      | 0.50 BSC |      |  |

| Optional Center Pad Width  | W2          |      |          | 2.50 |  |

| Optional Center Pad Length | T2          |      |          | 2.50 |  |

| Contact Pad Spacing        | C1          |      | 3.93     |      |  |

| Contact Pad Spacing        | C2          |      | 3.93     |      |  |

| Contact Pad Width          | X1          |      |          | 0.30 |  |

| Contact Pad Length         | Y1          |      |          | 0.73 |  |

| Distance Between Pads      | G           | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

## APPENDIX A: REVISION HISTORY

## **Revision A (February 2009)**

Original data sheet for PIC18(L)F1XK22 devices.

## Revision B (04/2009)

Revised data sheet title; Revised Peripheral Features section; Revised Table 3-1, Table 3-2; Revised Example 15-1; Revised Table 21-4.

## **Revision C (10/2009)**

Updated Table 1-1; Updated the "Electrical Specifications" section (Figures 25-1 to 25-4; subsections 25.1, 25.2, 25.3, 25.4, 25.5, 25.6, 25.7, 25.8, Added Param No. OS09 to Table 25-2; Added Param No. D003A and Note 1 to Table 25-12); Added graphs to the "DC and AC Characteristics Graphs and Charts" section; Other minor corrections.

## Revision D (05/2010)

Revised Section 1.3 (deleted #2); Revised Figure 1-1; Added Table 2-4; Removed register EEADRH from Tables 3-1 and 3-2; Revised Section 5 (Data EEPROM Memory); Updated Example 5-2 and Table 5-1; Revised Section 13.4.4 (Enhanced PWM Auto-Shutdown Mode); Added Note 4 below Register 13-2; Revised Figure 16-1; Revised Equation 20-1; Removed sub-section 20.1.3 (Output Clamped to Vss); Updated Figure 20-1; Revised Tables 21-4 and Table 22-1; Updated Register 22-5, Figure 25-5, Table 25-2, Table 25-8, Table 25-10 and Table 25-12; Updated the Electrical Specification section; Other minor corrections.

## **Revision E (10/2011)**

Updated data sheet to new format; Updated the Pin Diagrams; Updated the Electrical Specifications section; Updated the Packaging Information section; Updated Table B-1; Updated the Product Identification System section; Other minor corrections.

## **Revision F (04/2016)**

Updated Analog Features section on page 1; Updated Tables 1-2, 3-2, 8-5, 8-6, 16-2 and 22-4; Added Note 3 to Tables 3-2, 8-1 and 8-2; Added Note 1 to Tables 9-1, 10-2, 12-1 and 17-2, and Register 8-4; Updated Figures 3-7, 9-1 and 9-2; Updated Registers 13-2, 16-2, 19-1; Updated Section 1.1.2, 7.9 and 8.1; Replaced chapter 20.0 (Voltage References) with chapter 20.0 (Fixed Voltage Reference) and 21.0 (Digital-to-Analog Converter (DAC) Module); Updated Chapter 26.0 (Electrical Specifications); Other minor corrections.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2009-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0464-4

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.