Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 17                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 20-QFN (4x4)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf14k22t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.8 Oscillator Start-up Timer

The Primary External Oscillator, when configured for LP, XT or HS modes, incorporates an Oscillator Start-up Timer (OST). The OST ensures that the oscillator starts and provides a stable clock to the oscillator module. The OST times out when 1024 oscillations on OSC1 have occurred. During the OST period, with the system clock set to the Primary External Oscillator, the program counter does not increment suspending program execution. The OST period will occur following:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Wake-up from Sleep

- · Oscillator being enabled

- Expiration of Power-up Timer (PWRT)

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Start-up mode can be selected. See **Section 2.11** "**Two-Speed Start-up Mode**" for more information.

#### 2.9 Clock Switching

The device contains circuitry to prevent clock "glitches" due to a change of the system clock source. To accomplish this, a short pause in the system clock occurs during the clock switch. If the new clock source is not stable (e.g., OST is active), the device will continue to execute from the old clock source until the new clock source becomes stable. The timing of a clock switch is as follows:

- 1. SCS<1:0> bits of the OSCCON register are modified.

- 2. The system clock will continue to operate from the old clock until the new clock is ready.

- Clock switch circuitry waits for two consecutive rising edges of the old clock after the new clock is ready.

- 4. The system clock is held low, starting at the next falling edge of the old clock.

- 5. Clock switch circuitry waits for an additional two rising edges of the new clock.

- On the next falling edge of the new clock, the low hold on the system clock is release and the new clock is switched in as the system clock.

- 7. Clock switch is complete.

Refer to Figure 2-5 for more details.

| Old Clock                  | li liiii liiii liiii liiii liiii | - Elinear Alassa (Carasta A | <br> | Republica |

|----------------------------|----------------------------------|-----------------------------|------|-----------|

| New Clock                  |                                  |                             |      |           |

| New Cit Peacy              |                                  |                             | <br> |           |

| IRCF <2:0>                 | inci Chi 🗴 Sainci Naw            |                             |      |           |

| System Clock               |                                  |                             |      |           |

|                            |                                  |                             |      |           |

| Low Space Nig<br>Old Clark | 93 <b>8338</b> 893<br>           | Clock Sync                  | <br> | Running   |

|                            |                                  | Cieck Syne                  |      | Running   |

| ORI ORICE                  |                                  | Clock Byne                  |      |           |

| OKI OKAX                   |                                  | Clock Gyne                  |      | 9         |

### FIGURE 2-5: CLOCK SWITCH TIMING

#### 3.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 3-5 and Figure 3-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 3.5.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 3.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

#### 3.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top portion of Bank 15 (F60h to FFFh). A list of these registers is given in Table 3-1 and Table 3-2.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

#### 5.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit of the EECON1 register and then set control bit, RD. The data is available on the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 5-1.

#### 5.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADR register and the data written to the EEDATA register. The sequence in Example 5-2 must be followed to initiate the write cycle.

The write will not begin if this sequence is not exactly followed (write 55h to EECON2, write 0AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, EECON1, EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared by hardware and the EEPROM Interrupt Flag bit, EEIF, is set. The user may either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### 5.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

EXAMPLE 5-1: DATA EEPROM READ

|   | MOVLW | DATA EE A | ADDR  | ; |                             |

|---|-------|-----------|-------|---|-----------------------------|

|   | MOVWF |           |       |   | Data Memory Address to read |

|   | BCF   | EECON1, E | EEPGD | ; | Point to DATA memory        |

|   | BCF   | EECON1, C | CFGS  | ; | Access EEPROM               |

| I | BSF   | EECON1, F | RD    | ; | EEPROM Read                 |

|   | MOVF  | EEDATA, W | N     | ; | W = EEDATA                  |

|   |       |           |       |   |                             |

#### EXAMPLE 5-2: DATA EEPROM WRITE

| Required<br>Sequence | MOVLW<br>MOVWF<br>BCF<br>BCF<br>BCF<br>BCF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF | DATA_EE_ADDR_LOW<br>EEADR<br>DATA_EE_DATA<br>EEDATA<br>EECON1, EEPGD<br>EECON1, CFGS<br>EECON1, WREN<br>INTCON, GIE<br>55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1, WR | <pre>; Data Memory Address to write<br/>;<br/>; Data Memory Value to write<br/>; Point to DATA memory<br/>; Access EEPROM<br/>; Enable writes<br/>; Disable Interrupts<br/>;<br/>; Write 55h<br/>;<br/>; Write 0AAh<br/>; Set WR bit to begin write</pre> |

|----------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | BSF<br>BSF                                                                            | EECON1, WR<br>INTCON, GIE                                                                                                                                            | ; Set WR bit to begin write<br>; Enable Interrupts                                                                                                                                                                                                        |

|                      | BCF                                                                                   | EECON1, WREN                                                                                                                                                         | ; User code execution<br>; Disable writes on write complete (EEIF set)                                                                                                                                                                                    |

| R/W-1        | R/W-1                         | R/W-1                                                        | R/W-1                             | U-0             | R/W-1             | U-0             | R/W-1         |

|--------------|-------------------------------|--------------------------------------------------------------|-----------------------------------|-----------------|-------------------|-----------------|---------------|

| RABPU        | INTEDG0                       | INTEDG1                                                      | INTEDG2                           | —               | TMR0IP            | _               | RABIP         |

| bit 7        | ÷                             |                                                              |                                   |                 |                   |                 | bit 0         |

|              |                               |                                                              |                                   |                 |                   |                 |               |

| Legend:      |                               |                                                              |                                   |                 |                   |                 |               |

| R = Readab   | le bit                        | W = Writable                                                 | bit                               | U = Unimple     | emented bit, read | d as '0'        |               |

| -n = Value a | t POR                         | '1' = Bit is set                                             |                                   | '0' = Bit is cl | eared             | x = Bit is unk  | nown          |

| bit 7        | 1 = PORTA a<br>0 = PORTA a    | RTA and PORT<br>and PORTB pu<br>and PORTB pu<br>nd WPUB bits | ll-ups are disa<br>ll-ups are ena | bled            | that the pin is a | n input and the | corresponding |

| bit 6        | 1 = Interrupt                 | kternal Interrup<br>on rising edge<br>on falling edge        | ·                                 | ct bit          |                   |                 |               |

| bit 5        | 1 = Interrupt                 | kternal Interrup<br>on rising edge<br>on falling edge        | ·                                 | ct bit          |                   |                 |               |

| bit 4        | 1 = Interrupt                 | kternal Interrup<br>on rising edge<br>on falling edge        | ·                                 | ct bit          |                   |                 |               |

| bit 3        | Unimplemen                    | ted: Read as '                                               | 0'                                |                 |                   |                 |               |

| bit 2        | TMROIP: TM                    | R0 Overflow In                                               | terrupt Priority                  | / bit           |                   |                 |               |

|              | 1 = High pric<br>0 = Low prio | ,                                                            |                                   |                 |                   |                 |               |

| bit 1        | Unimplemen                    | ted: Read as '                                               | 0'                                |                 |                   |                 |               |

| bit 0        |                               | Ind RB Port Ch                                               | ange Interrup                     | t Priority bit  |                   |                 |               |

|              | 1 = High pric<br>0 = Low prio |                                                              |                                   |                 |                   |                 |               |

| Note: Ir     | 0 = Low prio                  | -                                                            | interrupt                         |                 |                   |                 |               |

#### REGISTER 7-2: INTCON2: INTERRUPT CONTROL 2 REGISTER

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the global    |

|       | enable bit. User software might ensure the    |

|       | appropriate interrupt flag bits are clear     |

|       | prior to enabling an interrupt. This feature  |

|       | allows for software polling.                  |

| REGISTER 7-3     | <b>5. PIKZ</b> . |                                      |                 | FIREQUES         | I (FLAG) KEU     |                 |             |

|------------------|------------------|--------------------------------------|-----------------|------------------|------------------|-----------------|-------------|

| R/W-0            | R/W-0            | R/W-0                                | R/W-0           | R/W-0            | U-0              | R/W-0           | U-0         |

| OSCFIF           | C1IF             | C2IF                                 | EEIF            | BCLIF            | _                | TMR3IF          | —           |

| bit 7            |                  |                                      |                 |                  |                  |                 | bit (       |

|                  |                  |                                      |                 |                  |                  |                 |             |

| Legend:          |                  |                                      |                 |                  |                  |                 |             |

| R = Readable b   | it               | W = Writable                         | bit             | U = Unimple      | mented bit, read | as '0'          |             |

| -n = Value at PC | )R               | '1' = Bit is set                     |                 | '0' = Bit is cle | eared            | x = Bit is unkr | Iown        |

| bit 7            |                  | illator Fail Inte                    | rupt Elag bit   |                  |                  |                 |             |

|                  |                  |                                      | 1 0             | e changed to     | HFINTOSC (mu     | st he cleared b | v software) |

|                  |                  | lock operating                       | CIOCK INPUL NA  | is changed to    |                  |                 | y soliware) |

| bit 6            | C1IF: Compa      | rator C1 Interro                     | upt Flag bit    |                  |                  |                 |             |

|                  | 1 = Compara      | ator C1 output I                     | nas changed (   | must be cleare   | ed by software)  |                 |             |

|                  | 0 = Compara      | ator C1 output h                     | nas not chang   | ed               |                  |                 |             |

| bit 5            | C2IF: Compa      | rator C2 Interro                     | upt Flag bit    |                  |                  |                 |             |

|                  |                  |                                      |                 |                  | ed by software)  |                 |             |

|                  |                  | ator C2 output l                     | •               |                  |                  |                 |             |

|                  |                  | EPROM/Flash                          | •               | •                | •                |                 |             |

|                  |                  | e operation is c<br>e operation is n |                 |                  | , ,              |                 |             |

|                  |                  | Collision Interru                    | •               | i nas not been   | i starteu        |                 |             |

|                  |                  | llision occurred                     |                 | ared by softwa   | ure)             |                 |             |

|                  |                  | ollision occurre                     |                 | area by soltwa   |                  |                 |             |

| bit 2            | Unimplemen       | ted: Read as '                       | 0'              |                  |                  |                 |             |

| bit 1            | TMR3IF: TMF      | R3 Overflow Int                      | terrupt Flag bi | t                |                  |                 |             |

|                  |                  | gister overflow<br>gister did not o  | ·               | leared by softw  | ware)            |                 |             |

|                  |                  | •                                    |                 |                  |                  |                 |             |

|                  | ommpiemen        | ted: Read as '                       | U               |                  |                  |                 |             |

|                  |                  |                                      |                 |                  |                  |                 |             |

### REGISTER 7-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| U-0                                               | U-0             | R/W-x            | R/W-x                                      | R-x                               | R/W-x | R/W-x | R/W-x |  |

|---------------------------------------------------|-----------------|------------------|--------------------------------------------|-----------------------------------|-------|-------|-------|--|

| _                                                 | —               | RA5              | RA4                                        | RA3                               | RA2   | RA1   | RA0   |  |

| bit 7                                             |                 |                  |                                            |                                   |       |       | bit ( |  |

|                                                   |                 |                  |                                            |                                   |       |       |       |  |

| Legend:                                           |                 |                  |                                            |                                   |       |       |       |  |

| R = Readable bit W = Writa                        |                 | W = Writable     | ble bit U = Unimplemented bit, read as '0' |                                   |       |       |       |  |

| -n = Value a                                      | at POR          | '1' = Bit is set |                                            | '0' = Bit is cleared x = Bit is u |       |       | nown  |  |

|                                                   |                 |                  |                                            |                                   |       |       |       |  |

| bit 7-6                                           | Unimplemen      | ted: Read as '0  | כי                                         |                                   |       |       |       |  |

| bit 5-0 RA<5:0>: PORTA I/O Pin bit <sup>(1)</sup> |                 |                  | (1)                                        |                                   |       |       |       |  |

|                                                   | 1 = Port pin is | s > Vih          |                                            |                                   |       |       |       |  |

|                                                   | 0 = Port pin is | s < Vil          |                                            |                                   |       |       |       |  |

#### **REGISTER 8-1: PORTA: PORTA REGISTER**

**Note 1:** The RA3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0). Otherwise, RA3 reads as '0'. This bit is read-only.

#### REGISTER 8-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | U-1 | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|-----|--------|--------|--------|

| —     | —   | TRISA5 | TRISA4 |     | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |        |        |     |        |        | bit 0  |

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit <sup>(1)</sup><br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                                        |

|         | •                                                                                                                                                                 |

**Note 1:** TRISA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

| EXAMPLE | 10-1: I | MPLEMENTING A | A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE |

|---------|---------|---------------|----------------------------------------------------|

| RTCinit |         |               |                                                    |

|         | MOVLW   | 80h           | ; Preload TMR1 register pair                       |

|         | MOVWF   | TMR1H         | ; for 1 second overflow                            |

|         | CLRF    | TMR1L         |                                                    |

|         | MOVLW   | b'00001111'   | ; Configure for external clock,                    |

|         | MOVWF   | TICON         | ; Asynchronous operation, external oscillator      |

|         | CLRF    | secs          | ; Initialize timekeeping registers                 |

|         | CLRF    | mins          | ;                                                  |

|         | MOVLW   | .12           |                                                    |

|         | MOVWF   | hours         |                                                    |

|         | BSF     | PIE1, TMR1IE  | ; Enable Timer1 interrupt                          |

|         | RETURN  |               |                                                    |

| RTCisr  |         |               |                                                    |

|         | BSF     | TMR1H, 7      | ; Preload for 1 sec overflow                       |

|         | BCF     | PIR1, TMR1IF  | ; Clear interrupt flag                             |

|         | INCF    | secs, F       | ; Increment seconds                                |

|         | MOVLW   | .59           | ; 60 seconds elapsed?                              |

|         | CPFSGT  | Secs          |                                                    |

|         | RETURN  |               | ; No, done                                         |

|         | CLRF    | secs          | ; Clear seconds                                    |

|         | INCF    | mins, F       | ; Increment minutes                                |

|         | MOVLW   | .59           | ; 60 minutes elapsed?                              |

|         | CPFSGT  | mins          |                                                    |

|         | RETURN  |               | ; No, done                                         |

|         | CLRF    | mins          | ; clear minutes                                    |

|         | INCF    | hours, F      | ; Increment hours                                  |

|         | MOVLW   | .23           | ; 24 hours elapsed?                                |

|         | CPFSGT  | hours         |                                                    |

|         | RETURN  |               | ; No, done                                         |

|         | CLRF    | hours         | ; Reset hours                                      |

|         | RETURN  |               | ; Done                                             |

### EXAMPLE 10-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

#### TABLE 10-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7                      | Bit 6                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|----------------------------|---------------------------------------------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | <b>GIE/GIEH</b>            | PEIE/GIEL                                   | TMR0IE  | INT0IE  | RABIE   | TMR0IF | INT0IF | RABIF  | 245                        |

| IPR1   | _                          | - ADIP RCIP TXIP SSPIP CCP1IP TMR2IP TMR1IP |         |         |         |        |        |        |                            |

| PIE1   | _                          | ADIE                                        | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 248                        |

| PIR1   | _                          | ADIF                                        | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 248                        |

| TMR1H  | Timer1 Register, High Byte |                                             |         |         |         |        |        |        |                            |

| TMR1L  | Timer1 Register, Low Byte  |                                             |         |         |         |        |        |        | 246                        |

| TRISA  | _                          |                                             | TRISA5  | TRISA4  | _(1)    | TRISA2 | TRISA1 | TRISA0 | 248                        |

| T1CON  | RD16                       | T1RUN                                       | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 246                        |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Unimplemented, read as'1'.

### 13.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

PIC18(L)F1XK22 devices have one ECCP (Capture/Compare/PWM) module. The module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register.

CCP1 is implemented as a standard CCP module with enhanced PWM capabilities. These include:

- · Provision for two or four output channels

- Output steering

- Programmable polarity

- Programmable dead-band control

- · Automatic shutdown and restart

The enhanced features are discussed in detail in **Section 13.4 "PWM (Enhanced Mode)"**.

#### REGISTER 13-1: CCP1CON: ENHANCED CAPTURE/COMPARE/PWM CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                               |                    |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as 'O'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

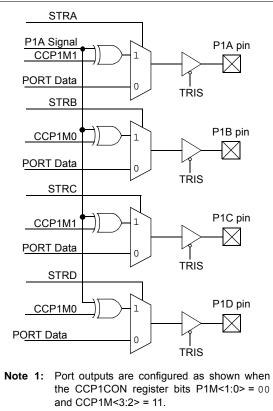

P1M<1:0>: Enhanced PWM Output Configuration bits

|         | <ul> <li><u>If CCP1M&lt;3:2&gt; = 00, 01, 10:</u></li> <li>xx = P1A assigned as Capture/Compare input/output; P1B, P1C, P1D assigned as port pins</li> <li><u>If CCP1M&lt;3:2&gt; = 11:</u></li> <li>00 = Single output: P1A, P1B, P1C and P1D controlled by steering (See Section 13.4.7 "Pulse Steering Mode").</li> <li>01 = Full-bridge output forward: P1D modulated; P1A active; P1B, P1C inactive</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 10 = Half-bridge output: P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins<br>11 = Full-bridge output reverse: P1B modulated; P1C active; P1A, P1D inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 5-4 | DC1B<1:0>: PWM Duty Cycle bit 1 and bit 0<br><u>Capture mode:</u><br>Unused.<br><u>Compare mode:</u><br>Unused.<br><u>PWM mode:</u><br>These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in<br>CCPR1L.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 3-0 | <pre>CCP1M&lt;3:0&gt;: Enhanced CCP Mode Select bits<br/>0000 = Capture/Compare/PWM off (resets ECCP module)<br/>0001 = Reserved<br/>0010 = Compare mode, toggle output on match<br/>0011 = Reserved<br/>0100 = Capture mode, every falling edge<br/>0101 = Capture mode, every falling edge<br/>0110 = Capture mode, every 4th rising edge<br/>0111 = Capture mode, every 16th rising edge<br/>0111 = Capture mode, every 16th rising edge<br/>1000 = Compare mode, initialize CCP1 pin low, set output on compare match (set CCP1IF)<br/>1001 = Compare mode, initialize CCP1 pin high, clear output on compare match (set CCP1IF)<br/>1010 = Compare mode, generate software interrupt only, CCP1 pin reverts to I/O state<br/>1011 = Compare mode, trigger special event (ECCP resets TMR1 or TMR3, start A/D conversion, sets</pre> |

bit 7-6

FIGURE 13-16: SIMPLIFIED STEERING BLOCK DIAGRAM

**2:** Single PWM output requires setting at least one of the STRx bits.

# 14.2.8 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in Full Power mode; in the case of the Sleep mode, all clocks are halted.

In all Idle modes, a clock is provided to the peripherals. That clock could be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See **Section 18.0 "Power-Managed Modes"** for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

When MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller:

- From Sleep, in Slave mode

- From Idle, in Slave or Master mode

If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any Power-Managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

#### 14.2.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 14.2.10 BUS MODE COMPATIBILITY

Table 14-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| TABLE 14-1: | SPI BUS MODES |

|-------------|---------------|

|-------------|---------------|

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

There is also an SMP bit which controls when the data is sampled.

| TABLE 14-2. REGISTERS ASSOCIATED WITH SPTOPERATION |                                           |           |        |        |        |        |        |        |                            |

|----------------------------------------------------|-------------------------------------------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| Name                                               | Bit 7                                     | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

| INTCON                                             | GIE/GIEH                                  | PEIE/GIEL | TMR0IE | INT0IE | RABIE  | TMR0IF | INT0IF | RABIF  | 245                        |

| IPR1                                               | —                                         | ADIP      | RCIP   | TXIP   | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 248                        |

| PIE1                                               | —                                         | ADIE      | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 248                        |

| PIR1                                               | —                                         | ADIF      | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 248                        |

| TRISB                                              | TRISB7                                    | TRISB6    | TRISB5 | TRISB4 | —      | _      | _      | _      | 248                        |

| TRISC                                              | TRISC7                                    | TRISC6    | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 248                        |

| SSPBUF                                             | PBUF SSP Receive Buffer/Transmit Register |           |        |        |        |        |        |        | 246                        |

| SSPCON1                                            | WCOL                                      | SSPOV     | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 246                        |

| SSPSTAT                                            | SMP                                       | CKE       | D/A    | Р      | S      | R/W    | UA     | BF     | 246                        |

TABLE 14-2:

REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: Shaded cells are not used by the MSSP in SPI mode.

#### 14.3.4 CLOCK STRETCHING

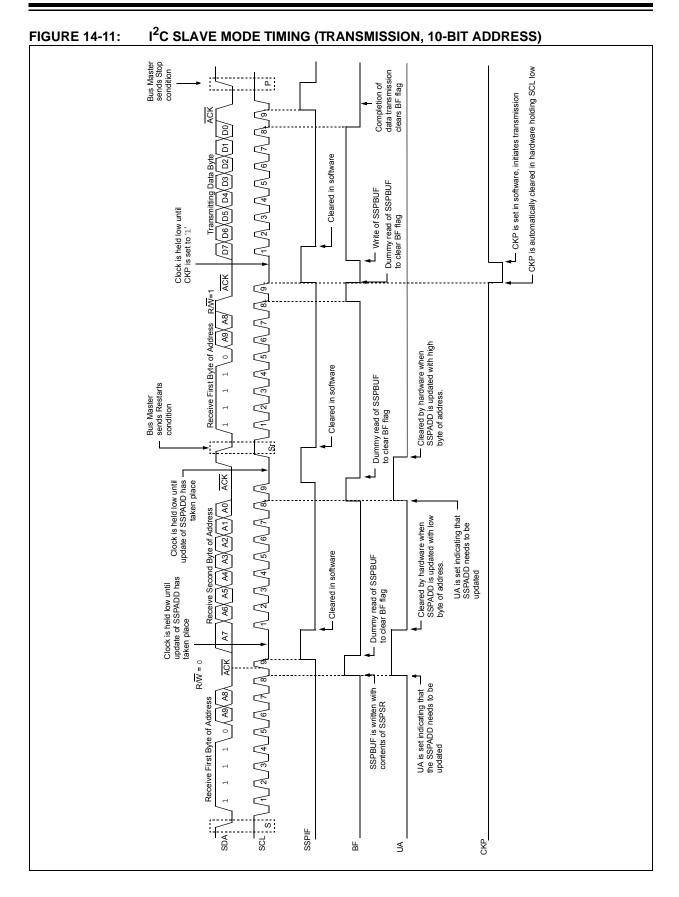

Both 7-bit and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit of the SSPCON2 register allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 14.3.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence if the BF bit is set, the CKP bit of the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another data transfer sequence. This will prevent buffer overruns from occurring (see Figure 14-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set by software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 14.3.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

#### 14.3.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another data transfer sequence (see Figure 14-9).

- Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- **2:** The CKP bit can be set by software regardless of the state of the BF bit.

#### 14.3.4.4 Clock Stretching for 10-bit Slave Transmit Mode

In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence which contains the high-order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is automatic with the hardware clearing CKP, as in 7-bit Slave Transmit mode (see Figure 14-11).

#### 14.3.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter SP106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter SP107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 14-21).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 14.3.10.1 BF Status Flag

In Transmit mode, the BF bit of the SSPSTAT register is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 14.3.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared by software before the next transmission.

#### 14.3.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 14.3.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN bit of the SSPCON2 register.

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPCON2 register.

#### 14.3.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 14.3.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 14.3.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

<sup>© 2009-2016</sup> Microchip Technology Inc.

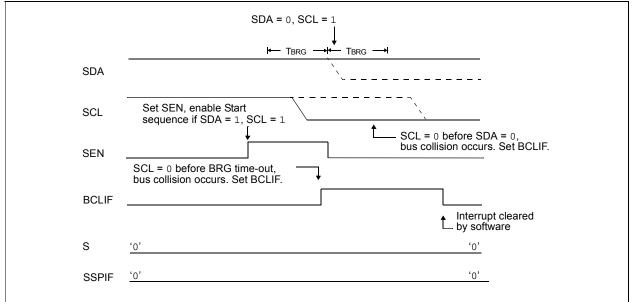

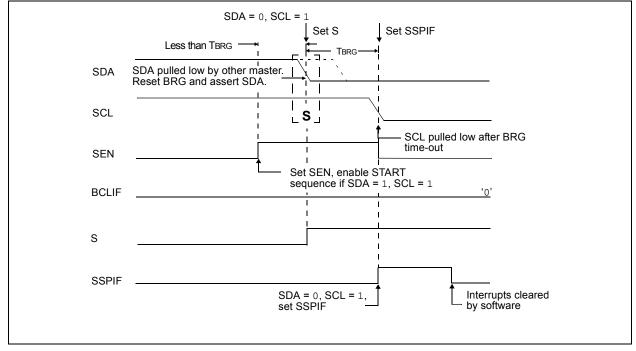

#### FIGURE 14-28: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

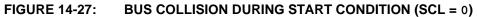

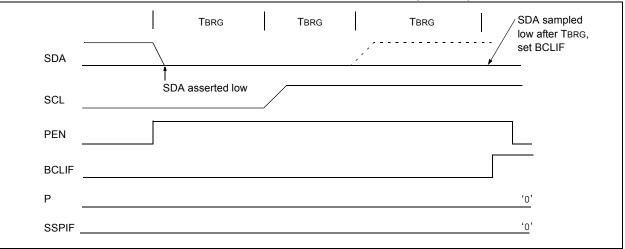

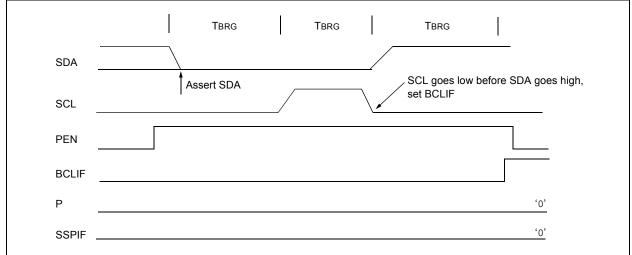

#### 14.3.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 14-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 14-32).

#### FIGURE 14-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 14-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

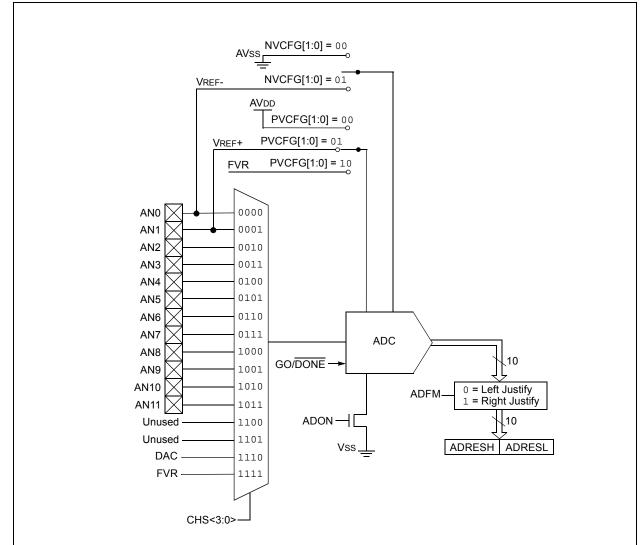

## 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

The ADC voltage reference is software selectable to either VDD, or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 16-1 shows the block diagram of the ADC.

#### FIGURE 16-1: ADC BLOCK DIAGRAM

© 2009-2016 Microchip Technology Inc.

| Name     | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| ANSEL    | ANS7     | ANS6      | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 248                        |

| CM1CON0  | C10N     | C10UT     | C10E   | C1POL  | C1SP   | C1R    | C1CH1  | C1CH0  | 248                        |

| CM2CON0  | C2ON     | C2OUT     | C2OE   | C2POL  | C2SP   | C2R    | C2CH1  | C2CH0  | 248                        |

| CM2CON1  | MC10UT   | MC2OUT    | C1RSEL | C2RSEL | C1HYS  | C2HYS  | C1SYNC | C2SYNC | 248                        |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RABIE  | TMR0IF | INT0IF | RABIF  | 245                        |

| IPR2     | OSCFIP   | C1IP      | C2IP   | EEIP   | BCLIP  | _      | TMR3IP | _      | 248                        |

| LATC     | LATC7    | LATC6     | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | 248                        |

| PIE2     | OSCFIE   | C1IE      | C2IE   | EEIE   | BCLIE  | —      | TMR3IE | _      | 248                        |

| PIR2     | OSCFIF   | C1IF      | C2IF   | EEIF   | BCLIF  | —      | TMR3IF | _      | 248                        |

| PORTC    | RC7      | RC6       | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | 248                        |

| VREFCON0 | FVR1EN   | FVR1ST    | FVR18  | 6<1:0> | —      | —      | —      | _      | 247                        |

| VREFCON1 | D1EN     | D1LPS     | DAC10E |        | D1PS   | S<1:0> | _      | D1NSS  | 247                        |

| TRISA    | _        | _         | TRISA5 | TRISA4 | _(1)   | TRISA2 | TRISA1 | TRISA0 | 248                        |

| TRISC    | TRISC7   | TRISC6    | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 248                        |

|  | <b>TABLE 17-2:</b> | REGISTERS ASSOCIATED WITH COMPARATOR MODULE |

|--|--------------------|---------------------------------------------|

|--|--------------------|---------------------------------------------|

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

Note 1: Unimplemented, read as '1'.

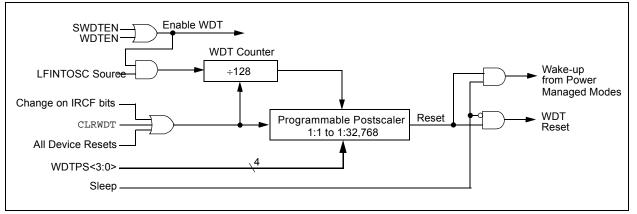

### 23.2 Watchdog Timer (WDT)

For PIC18(L)F1XK22 devices, the WDT is driven by the LFINTOSC source. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the LFINTOSC oscillator.

The 4-millisecond period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexer, controlled by bits in Configuration register 2H. Available periods range from 4 ms to 131.072 seconds (2.18 minutes). The WDT and postscaler are cleared when any of the following events occur: a SLEEP or CLRWDT instruction is executed, the IRCF bits of the OSCCON register are changed or a clock failure has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- 2: Changing the setting of the IRCF bits of the OSCCON register clears the WDT and postscaler counts.

#### FIGURE 23-1: WDT BLOCK DIAGRAM

| ADDWFC                                                                           | RY bit to                                                                                                                                                                                                 | o f                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                          | ADDWFC                                                                                                                                                                                                    | f {,d {,a                                                                                                                                                             | a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                               |

| Operands:                                                                        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                       |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

| Operation:                                                                       | (W) + (f) +                                                                                                                                                                                               | $(C) \rightarrow de$                                                                                                                                                  | st                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                               |

| Status Affected:                                                                 | N,OV, C, D                                                                                                                                                                                                | C, Z                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

| Encoding:                                                                        | 0010                                                                                                                                                                                                      | 00da                                                                                                                                                                  | ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ffff                                                                                                          |

|                                                                                  | ory location<br>placed in W<br>placed in d<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode when<br>Section 24<br>Bit-Oriente<br>Literal Offs | V. If 'd' is<br>ata memory<br>he Access<br>he BSR is<br>(default).<br>and the ex-<br>led, this in<br>Literal Off<br>never $f \leq 1$<br><b>4.2.3 "By</b><br>ed Instru | '1', the report locations and the second | sult is<br>on 'f'.<br>selected.<br>select the<br>astruction<br>operates<br>essing<br>See<br>ed and<br>Indexed |