Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 45MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 39                                                                         |

| Program Memory Size        | 96КВ (96К х 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-LQFP                                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1226fbd48-301-1 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3. Applications

- eMetering

- Lighting

- Industrial networking

- Alarm systems

- White goods

## 4. Ordering information

## Table 1. Ordering information

| Type number      | Package | Package                                                                                        |          |  |  |  |  |  |

|------------------|---------|------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

|                  | Name    | Description                                                                                    | Version  |  |  |  |  |  |

| LPC1227FBD64/301 | LQFP64  | LQFP64: plastic low profile quad flat package; 64 leads; body 10 $\times$ 10 $\times$ 1.4 mm   | SOT314-2 |  |  |  |  |  |

| LPC1226FBD64/301 | LQFP64  | LQFP64: plastic low profile quad flat package; 64 leads; body 10 $\times$ 10 $\times$ 1.4 mm   | SOT314-2 |  |  |  |  |  |

| LPC1225FBD64/321 | LQFP64  | LQFP64: plastic low profile quad flat package; 64 leads; body 10 $\times$ 10 $\times$ 1.4 mm   | SOT314-2 |  |  |  |  |  |

| LPC1225FBD64/301 | LQFP64  | LQFP64: plastic low profile quad flat package; 64 leads; body 10 $\times$ 10 $\times$ 1.4 mm   | SOT314-2 |  |  |  |  |  |

| LPC1224FBD64/121 | LQFP64  | LQFP64: plastic low profile quad flat package; 64 leads; body 10 $\times$ 10 $\times$ 1.4 mm   | SOT314-2 |  |  |  |  |  |

| LPC1224FBD64/101 | LQFP64  | LQFP64: plastic low profile quad flat package; 64 leads; body 10 $\times$ 10 $\times$ 1.4 mm   | SOT314-2 |  |  |  |  |  |

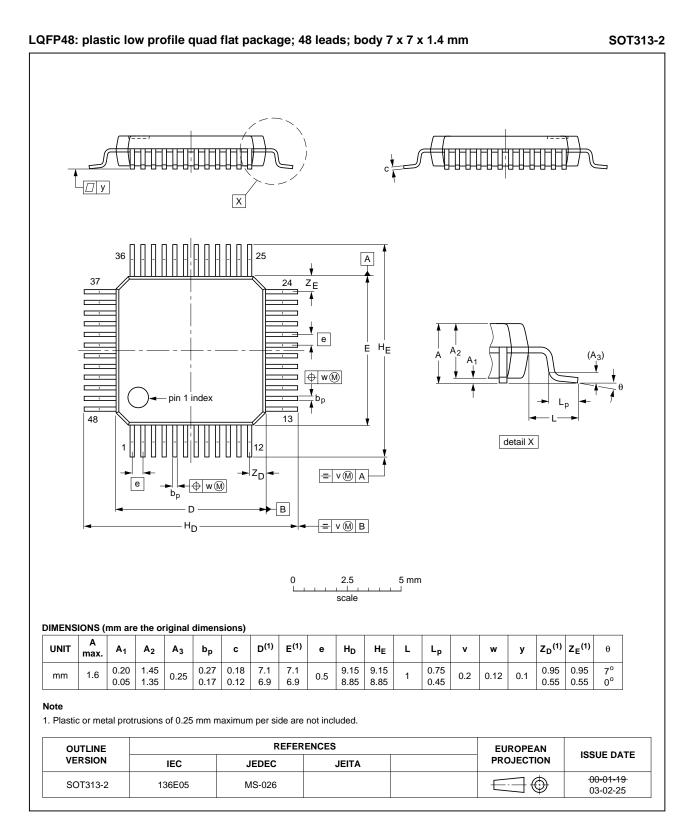

| LPC1227FBD48/301 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm       | SOT313-2 |  |  |  |  |  |

| LPC1226FBD48/301 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm       | SOT313-2 |  |  |  |  |  |

| LPC1225FBD48/321 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm       | SOT313-2 |  |  |  |  |  |

| LPC1225FBD48/301 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm       | SOT313-2 |  |  |  |  |  |

| LPC1224FBD48/121 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm       | SOT313-2 |  |  |  |  |  |

| LPC1224FBD48/101 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body 7 $\times$ 7 $\times$ 1.4 mm $-$ | SOT313-2 |  |  |  |  |  |

## 32-bit ARM Cortex-M0 microcontroller

| Symbol                      | Pin LQFP48 | Pin LQFP64 |            | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                       |

|-----------------------------|------------|------------|------------|-------------------------|------|-----------------------|-------------------------------------------------------------------|

| PIO0_17/MOSI                | 32         | 44         | [2]        | no                      | I/O  | I; PU                 | PIO0_17 — General purpose digital input/output pin.               |

|                             |            |            | [3]        |                         | I/O  | -                     | MOSI — Master Out Slave In for SSP/SPI.                           |

| PIO0_18/SWCLK/              | 33         | 45         | [2]        | no                      | I/O  | I; PU                 | PIO0_18 — General purpose digital input/output pin.               |

| CT32B0_CAP0/<br>CT32B0_MAT0 |            |            | [3]        |                         | I    | -                     | <b>SWCLK</b> — Serial wire clock, alternate location.             |

| 010200_100.000              |            |            |            |                         | I    | -                     | <b>CT32B0_CAP0</b> — Capture input, channel 0 for 32-bit timer 0. |

|                             |            |            |            |                         | 0    | -                     | CT32B0_MAT0 — Match output, channel 0 for 32-bit timer 0.         |

| PIO0_19/ACMP0_I0/           | 4          | 4          | [6]<br>[7] | no                      | I/O  | I; PU                 | PIO0_19 — General purpose digital input/output pin.               |

| CT32B0_CAP1/<br>CT32B0_MAT1 |            |            | [7]        |                         | I    | -                     | ACMP0_I0 — Input 0 for comparator 0.                              |

| 010200_100011               |            |            |            |                         | I    | -                     | <b>CT32B0_CAP1</b> — Capture input, channel 1 for 32-bit timer 0. |

|                             |            |            |            |                         | 0    | -                     | CT32B0_MAT1 — Match output, channel 1 for 32-bit timer 0          |

| PIO0_20/ACMP0_I1/           | 5          | 5          | [6]        | no                      | I/O  | I; PU                 | PIO0_20 — General purpose digital input/output pin.               |

| CT32B0_CAP2/<br>CT32B0_MAT2 |            |            | [7]        |                         | I    | -                     | ACMP0_I1 — Input 1 for comparator 0.                              |

|                             |            |            |            |                         | I    | -                     | <b>CT32B0_CAP2</b> — Capture input, channel 2 for 32-bit timer 0. |

|                             |            |            |            |                         | 0    | -                     | CT32B0_MAT2 — Match output, channel 2 for 32-bit timer 0.         |

| PIO0_21/ACMP0_I2/           | 6          | 6          | [6]        | no                      | I/O  | I; PU                 | PIO0_21 — General purpose digital input/output pin.               |

| CT32B0_CAP3/<br>CT32B0_MAT3 |            |            | [7]        |                         | I    | -                     | ACMP0_I2 — Input 2 for comparator 0.                              |

| 0152D0_INIA15               |            |            |            |                         | I    | -                     | <b>CT32B0_CAP3</b> — Capture input, channel 3 for 32-bit timer 0. |

|                             |            |            |            |                         | 0    | -                     | CT32B0_MAT3 — Match output, channel 3 for 32-bit timer 0.         |

| PIO0_22/ACMP0_I3            | 7          | 7          | [6]        | no                      | I/O  | I; PU                 | PIO0_22 — General purpose digital input/output pin.               |

|                             |            |            | [7]        |                         | I    | -                     | ACMP0_I3 — Input 3 for comparator 0.                              |

| PIO0_23/                    | 8          | 8          | [6]        | no                      | I/O  | I; PU                 | PIO0_23 — General purpose digital input/output pin.               |

| ACMP1_I0/<br>CT32B1_CAP0/   |            |            | [7]        |                         | I    | -                     | ACMP1_I0 — Input 0 for comparator 1.                              |

| CT32B1_MAT0                 |            |            |            |                         | I    | -                     | <b>CT32B1_CAP0</b> — Capture input, channel 0 for 32-bit timer 1. |

|                             |            |            |            |                         | 0    | -                     | CT32B1_MAT0 — Match output, channel 0 for 32-bit timer 1.         |

| PIO0_24/ACMP1_I1/           | 9          | 9          | [6]        | no                      | I/O  | I; PU                 | PIO0_24 — General purpose digital input/output pin.               |

| CT32B1_CAP1/<br>CT32B1_MAT1 |            |            | [7]        |                         | I    | -                     | ACMP1_I1 — Input 1 for comparator 1.                              |

| CT32DT_WATT                 |            |            |            |                         | I    | -                     | <b>CT32B1_CAP1</b> — Capture input, channel 1 for 32-bit timer 1. |

|                             |            |            |            |                         | 0    | -                     | CT32B1_MAT1 — Match output, channel 1 for 32-bit timer 1.         |

| SWDIO/ACMP1_I2/             | 10         | 10         | [6]        | no                      | I/O  | I; PU                 | <b>SWDIO</b> — Serial wire debug input/output, default location.  |

| CT32B1_CAP2/                |            |            | [7]        |                         | I    | -                     | ACMP1_I2 — Input 2 for comparator 1.                              |

| CT32B1_MAT2/<br>PIO0_25     |            |            |            |                         | I    | -                     | <b>CT32B1_CAP2</b> — Capture input, channel 2 for 32-bit timer 1. |

| _                           |            |            |            |                         | 0    | -                     | CT32B1_MAT2 — Match output, channel 2 for 32-bit timer 1.         |

|                             |            |            |            |                         | I/O  | -                     | PIO0_25 — General purpose digital input/output pin.               |

| SWCLK/ACMP1_I3/             | 11         | 11         | [6]        | no                      | I    | I; PU                 | SWCLK — Serial wire clock, default location.                      |

| CT32B1_CAP3/                |            |            | [7]        |                         | I    | -                     | ACMP1_I3 — Input 3 for comparator 1.                              |

| CT32B1_MAT3/<br>PIO0_26     |            |            |            |                         | I    | -                     | CT32B1_CAP3 — Capture input, channel 3 or 32-bit timer 1.         |

|                             |            |            |            |                         | 0    | -                     | CT32B1_MAT3 — Match output, channel 3 for 32-bit timer 1.         |

|                             |            |            |            |                         |      |                       |                                                                   |

## Table 3. LPC122x pin description ...continued

LPC122X Product data sheet

## 32-bit ARM Cortex-M0 microcontroller

| Table 3. LPC122x p<br>Symbol     |            |            |            |                |               | Reset            | Description                                                                                                                                                                                                                                                 |

|----------------------------------|------------|------------|------------|----------------|---------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                           | Pin LQFP48 | Pin LQFP64 |            | logic<br>input | туре          | state<br>[1]     | Description                                                                                                                                                                                                                                                 |

| PIO0_27/ACMP0_O                  | 12         | 12         | <u>[9]</u> | no             | I/O           | I; PU            | <b>PIO0_27</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                                     |

|                                  |            |            |            |                | 0             | -                | <b>ACMP0_O</b> — Output for comparator 0.                                                                                                                                                                                                                   |

| PIO0_28/ACMP1_O/<br>CT16B0_CAP0/ | 13         | 17         | [9]        | no             | I/O           | I; PU            | <b>PIO0_28</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                                     |

| CT16B0_MAT0                      |            |            |            |                | 0             | -                | ACMP1_O — Output for comparator 1.                                                                                                                                                                                                                          |

|                                  |            |            |            |                | I             | -                | CT16B0_CAP0 — Capture input, channel 0 for 16-bit timer 0.                                                                                                                                                                                                  |

|                                  |            |            |            |                | 0             | -                | CT16B0_MAT0 — Match output, channel 0 for 16-bit timer 0.                                                                                                                                                                                                   |

| PIO0_29/ROSC/<br>CT16B0_CAP1/    | 14         | 18         | [9]        | no             | I/O           | I; PU            | <b>PIO0_29</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                                     |

| CT16B0_MAT1                      |            |            |            |                | I/O           | -                | <b>ROSC</b> — Relaxation oscillator for 555 timer applications.                                                                                                                                                                                             |

|                                  |            |            |            |                | I             | -                | CT16B0_CAP1 — Capture input, channel 1 for 16-bit timer 0.                                                                                                                                                                                                  |

|                                  |            |            |            |                | 0             | -                | CT16B0_MAT1 — Match output, channel 1 for 16-bit timer 0.                                                                                                                                                                                                   |

| R/PIO0_30/AD0                    | 34         | 46         | [6]<br>[3] | no             | I             | I; PU            | R — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                    |

|                                  |            |            |            |                | I/O           | -                | PIO0_30 — General purpose digital input/output pin.                                                                                                                                                                                                         |

|                                  |            |            |            |                | Ι             | -                | AD0 — A/D converter, input 0.                                                                                                                                                                                                                               |

| R/PIO0_31/AD1                    | 35         | 47         | [6]<br>[3] | no             | I             | I; PU            | <ul> <li>R — Reserved. Configure for an alternate function in the IOCONFIG block.</li> </ul>                                                                                                                                                                |

|                                  |            |            |            |                | I/O           | -                | PIO0_31 — General purpose digital input/output pin.                                                                                                                                                                                                         |

|                                  |            |            |            |                | Ι             | -                | AD1 — A/D converter, input 1.                                                                                                                                                                                                                               |

| PIO1_0 to PIO1_6                 |            |            |            |                | I/O           |                  | <b>Port 1</b> — Port 1 is a 32-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block. Pins PIO1_7 through PIO1_31 are not available. |

| R/PIO1_0/AD2                     | 36         | 48         | [6]<br>[3] | no             | 0             | I; PU            | R — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                                    |

|                                  |            |            |            |                | I/O           | -                | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                  |            |            |            |                | I             | -                | AD2 — A/D converter, input 2.                                                                                                                                                                                                                               |

| R/PIO1_1/AD3                     | 37         | 49         | [6]<br>[3] | no             | I             | I; PU            | R — Reserved. Configure for an alternate function in the IOCONFIG block.Do not pull this pin LOW at reset.                                                                                                                                                  |

|                                  |            |            |            |                | I/O           | -                | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                  |            |            |            |                | I             | -                | AD3 — A/D converter, input 3.                                                                                                                                                                                                                               |

| PIO1_2/SWDIO/AD4                 | 38         | 50         | [6]        | no             | I/O           | I; PU            | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                  |            |            | [3]        |                | I/O           | -                | <b>SWDIO</b> — Serial wire debug input/output, alternate location.                                                                                                                                                                                          |

|                                  |            |            |            |                | I             | -                | AD4 — A/D converter, input 4.                                                                                                                                                                                                                               |

| PIO1_3/AD5/WAKEUP                | 39         | 51         | [8]        | no             | I/O           | I; PU            | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                  |            |            | [3]        |                | <u> </u>      | -                | AD5 — A/D converter, input 5.                                                                                                                                                                                                                               |

|                                  |            |            |            |                | I             | -                | WAKEUP — Deep power-down mode wake-up pin.                                                                                                                                                                                                                  |

| PIO1_4/AD6                       | 40         | 52         | [6]<br>[3] | no             | I/O           | I; PU            | PIO1_4 — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                  |            |            | [3]        |                | I             | -                | <b>AD6</b> — A/D converter, input 6.                                                                                                                                                                                                                        |

| LPC122X                          |            |            |            | All int        | formation pro | ovided in this o | document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved                                                                                                                                                                              |

## Table 3. LPC122x pin description ...continued

Product data sheet

## 32-bit ARM Cortex-M0 microcontroller

| Symbol                           | Pin LQFP48 | Pin LQFP64 |            | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                   |

|----------------------------------|------------|------------|------------|-------------------------|------|-----------------------|-------------------------------------------------------------------------------|

| PIO2_6/                          | -          | 35         | [2]        | no                      | I/O  | I; PU                 | PIO2_6 — General purpose digital input/output pin.                            |

| CT32B0_CAP2/<br>CT32B0_MAT2/DCD0 |            |            | [3]        |                         | I    | -                     | CT32B0_CAP2 — Capture input, channel 2 for 32-bit timer 0.                    |

| C132B0_IMA12/DCD0                |            |            |            |                         | 0    | -                     | CT32B0_MAT2 — Match output, channel 2 for 32-bit timer 0.                     |

|                                  |            |            |            |                         | I    | -                     | <b>DCD0</b> — Data Carrier Detect input for UART0.                            |

| PIO2_7/                          | -          | 36         | [2]        | no                      | I/O  | I; PU                 | PIO2_7 — General purpose digital input/output pin.                            |

| CT32B0_CAP3/                     |            |            | [3]        |                         | I    | -                     | CT32B0_CAP3 — Capture input, channel 3 for 32-bit timer 0.                    |

| CT32B0_MAT3/DSR0                 |            |            |            |                         | 0    | -                     | CT32B0_MAT3 — Match output, channel 3 for 32-bit timer 0.                     |

|                                  |            |            |            |                         | I    | -                     | <b>DSR0</b> — Data Set Ready input for UART0.                                 |

| PIO2_8/                          | -          | 59         | [2]        | no                      | I/O  | I; PU                 | PIO2_8 — General purpose digital input/output pin.                            |

| CT32B1_CAP0/                     |            |            | [3]        |                         | I    | -                     | CT32B1_CAP0 — Capture input, channel 0 for 32-bit timer 1.                    |

| CT32B1_MAT0                      |            |            |            |                         | 0    | -                     | CT32B1_MAT0 — Match output, channel 0 for 32-bit timer 1.                     |

| PIO2_9/                          | -          | 60         | [2]        | no                      | I/O  | I; PU                 | PIO2_9 — General purpose digital input/output pin.                            |

| CT32B1_CAP1/                     |            |            | [3]        |                         | I    | -                     | CT32B1_CAP1 — Capture input, channel 1 for 32-bit timer 1.                    |

| CT32B1_MAT1                      |            |            |            |                         | 0    | -                     | CT32B1_MAT1 — Match output, channel 1 for 32-bit timer 1.                     |

| PIO2_10/                         | -          | 61         | [2]        | no                      | I/O  | I; PU                 | PIO2_10 — General purpose digital input/output pin.                           |

| CT32B1_CAP2/                     |            |            | [3]        |                         | I    | -                     | CT32B1_CAP2 — Capture input, channel 2 for 32-bit timer 1.                    |

| CT32B1_MAT2/TXD1                 |            |            |            |                         | 0    | -                     | CT32B1_MAT2 — Match output, channel 2 for 32-bit timer 1.                     |

|                                  |            |            |            |                         | 0    | -                     | <b>TXD1</b> — Transmitter output for UART1.                                   |

| PIO2_11/                         | -          | 62         | [2]        | no                      | I/O  | I; PU                 | PIO2_11 — General purpose digital input/output pin.                           |

| CT32B1_CAP3/                     |            |            | [3]        |                         | I    | -                     | CT32B1_CAP3 — Capture input, channel 3 for 32-bit timer 1.                    |

| CT32B1_MAT3/RXD1                 |            |            |            |                         | 0    | -                     | CT32B1_MAT3 — Match output, channel 3 for 32-bit timer 1.                     |

|                                  |            |            |            |                         | I    | -                     | <b>RXD1</b> — Receiver input for UART1.                                       |

| PIO2_12/RXD1                     | -          | 13         | [2]        | no                      | I/O  | I; PU                 | PIO2_12 — General purpose digital input/output pin.                           |

|                                  |            |            | [3]        |                         | I    | -                     | <b>RXD1</b> — Receiver input for UART1.                                       |

| PIO2_13/TXD1                     | -          | 14         | [2]        | no                      | I/O  | I; PU                 | PIO2_13 — General purpose digital input/output pin.                           |

|                                  |            |            | [3]        |                         | 0    | -                     | <b>TXD1</b> — Transmitter output for UART1.                                   |

| PIO2_14                          | -          | 15         | [2]<br>[3] | no                      | I/O  | I; PU                 | PIO2_14 — General purpose digital input/output pin.                           |

| PIO2_15                          | -          | 16         | [2]<br>[3] | no                      | I/O  | I; PU                 | PIO2_15 — General purpose digital input/output pin.                           |

| RTCXIN                           | 46         | 58         | [10]       | -                       | I    | -                     | Input to the 32 kHz oscillator circuit.                                       |

| RTCXOUT                          | 45         | 57         | [10]       | -                       | 0    | -                     | Output from the 32 kHz oscillator amplifier.                                  |

| XTALIN                           | 1          | 1          |            | -                       | I    | -                     | Input to the system oscillator circuit and internal clock generator circuits. |

| XTALOUT                          | 2          | 2          |            | -                       | 0    | -                     | Output from the system oscillator amplifier.                                  |

| VREF_CMP                         | 3          | 3          |            | -                       | I    | -                     | Reference voltage for comparator.                                             |

## Table 3. LPC122x pin description ...continued

## 32-bit ARM Cortex-M0 microcontroller

| Table 4. Pin mult | iplexing    |      |              |           |         |

|-------------------|-------------|------|--------------|-----------|---------|

| Peripheral        | Function    | Туре | Available of | on ports: |         |

| ADC               | AD0         | I    | PIO0_30      | -         | -       |

|                   | AD1         | I    | PIO0_31      | -         | -       |

|                   | AD2         | I    | PIO1_0       | -         | -       |

|                   | AD3         | I    | PIO1_1       | -         | -       |

|                   | AD4         | I    | PIO1_2       | -         | -       |

|                   | AD5         | I    | PIO1_3       | -         | -       |

|                   | AD6         | I    | PIO1_4       | -         | -       |

|                   | AD7         | I    | PIO1_5       | -         | -       |

| CT16B0            | CT16B0_CAP0 | I    | PIO0_11      | PIO0_28   | PIO2_0  |

|                   | CT16B0_CAP1 | I    | PIO0_12      | PIO0_29   | PIO2_1  |

|                   | CT16B0_MAT0 | 0    | PIO0_11      | PIO0_28   | PIO2_0  |

|                   | CT16B0_MAT1 | 0    | PIO0_12      | PIO0_29   | PIO2_1  |

| CT16B1            | CT16B1_CAP0 | I    | PIO0_15      | PIO1_5    | PIO2_2  |

|                   | CT16B1_CAP1 | I    | PIO0_16      | PIO1_6    | PIO2_3  |

|                   | CT16B1_MAT0 | 0    | PIO0_15      | PIO1_5    | PIO2_2  |

|                   | CT16B1_MAT1 | 0    | PIO0_16      | PIO1_6    | PIO2_3  |

| CT32B0            | CT32B0_CAP0 | I    | PIO0_1       | PIO0_18   | PIO2_4  |

|                   | CT32B0_CAP1 | I    | PIO0_2       | PIO0_19   | PIO2_5  |

|                   | CT32B0_CAP2 | I    | PIO0_3       | PIO0_20   | PIO2_6  |

|                   | CT32B0_CAP3 | I    | PIO0_4       | PIO0_21   | PIO2_7  |

|                   | CT32B0_MAT0 | 0    | PIO0_1       | PIO0_18   | PIO2_4  |

|                   | CT32B0_MAT1 | 0    | PIO0_2       | PIO0_19   | PIO2_5  |

|                   | CT32B0_MAT2 | 0    | PIO0_3       | PIO0_20   | PIO2_6  |

|                   | CT32B0_MAT3 | 0    | PIO0_4       | PIO0_21   | PIO2_7  |

| CT32B1            | CT32B1_CAP0 | I    | PIO0_6       | PIO0_23   | PIO2_8  |

|                   | CT32B1_CAP1 | I    | PIO0_7       | PIO0_24   | PIO2_9  |

|                   | CT32B1_CAP2 | I    | PIO0_8       | PIO0_25   | PIO2_10 |

|                   | CT32B1_CAP3 | I    | PIO0_9       | PIO0_26   | PIO2_11 |

|                   | CT32B1_MAT0 | 0    | PIO0_6       | PIO0_23   | PIO2_8  |

|                   | CT32B1_MAT1 | 0    | PIO0_7       | PIO0_24   | PIO2_9  |

|                   | CT32B1_MAT2 | 0    | PIO0_8       | PIO0_25   | PIO2_10 |

|                   | CT32B1_MAT3 | 0    | PIO0_9       | PIO0_26   | PIO2_11 |

| UART0             | RXD0        | I    | PIO0_1       | PIO2_1    | -       |

|                   | TXD0        | 0    | PIO0_2       | PIO2_2    | -       |

|                   | CTS0        | I    | PIO0_7       | PIO2_4    | -       |

|                   | DCD0        | I    | PIO0_5       | PIO2_6    | -       |

|                   | DSR0        | I    | PIO0_4       | PIO2_7    | -       |

|                   | DTR0        | 0    | PIO0_3       | PIO2_3    | -       |

|                   | RIO         | I    | PIO0_6       | PIO2_5    | -       |

|                   | RTS0        | 0    | PIO0_0       | PIO2_0    | -       |

|                   |             |      |              |           |         |

LPC122X Product data sheet

| Table 4. Pin mul | tiplexing            |      |              |           |         |

|------------------|----------------------|------|--------------|-----------|---------|

| Peripheral       | Function             | Туре | Available of | on ports: |         |

| UART1            | RXD1                 | Ι    | PIO0_8       | PIO2_11   | PIO2_12 |

|                  | TXD1                 | 0    | PIO0_9       | PIO2_10   | PIO2_13 |

| SSP/SPI          | SCK                  | I/O  | PIO0_14      | -         | -       |

|                  | MISO                 | I/O  | PIO0_16      | -         | -       |

|                  | MOSI                 | I/O  | PIO0_17      | -         | -       |

|                  | SSEL                 | I/O  | PIO0_15      | -         | -       |

| I2C              | SCL                  | I/O  | PIO0_10      | -         | -       |

|                  | SDA                  | I/O  | PIO0_11      | -         | -       |

| SWD              | SWCLK <sup>[1]</sup> | I    | PIO0_18      | PIO0_26   | -       |

|                  | SWDIO[1]             | I/O  | PIO0_25      | PIO1_2    | -       |

| Reset            | RESET                | Ι    | PIO0_13      | -         | -       |

| Clockout pin     | CLKOUT               | 0    | PIO0_12      | -         | -       |

|                  |                      |      |              |           |         |

Table 4. Pin multiplexing

[1] After reset, the SWD functions are selected by default on pins PIO0\_26 and PIO0\_25.

## 7. Functional description

## 7.1 ARM Cortex-M0 processor

The ARM Cortex-M0 is a general purpose, 32-bit microprocessor, which offers high performance and very low power consumption.

## 7.1.1 System tick timer

The ARM Cortex-M0 includes a System Tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a 10 ms interval.

## 7.2 On-chip flash program memory

The LPC122x contain up to 128 kB of on-chip flash memory.

## 7.3 On-chip SRAM

The LPC122x contain a total of up to 8 kB on-chip static RAM memory.

## 7.4 Memory map

The LPC122x incorporates several distinct memory regions, shown in the following figures. <u>Figure 4</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The AHB peripheral area is 2 megabyte in size, and is divided to allow for up to 128 peripherals. The APB peripheral area is 512 kB in size and is divided to allow for up to 32 peripherals. Each peripheral of either type is allocated 16 kilobytes of space. This allows simplifying the address decoding for each peripheral.

- In the LPC122x, the NVIC supports 32 vectored interrupts. In addition, up to 12 of the individual GPIO inputs are NVIC-vector capable.

- Four programmable interrupt priority levels with hardware priority level masking.

- Software interrupt generation.

- Non-maskable Interrupt (NMI) can be programmed to use any of the peripheral interrupts. The NMI is not available on an external pin.

## 7.5.2 Interrupt sources

Each peripheral device has one interrupt line connected to the NVIC but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

Any GPIO pin (total of up to 55 pins) regardless of the selected function, can be programmed to generate an interrupt on a level, a rising edge or falling edge, or both.

## 7.6 IOCONFIG block

The IOCONFIG block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on-chip peripherals.

Peripherals should be connected to the appropriate pins prior to being activated and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined.

## 7.6.1 Features

- Programmable pull-up resistor.

- Programmable digital glitch filter.

- Programmable input inverter.

- Programmable drive current.

- Programmable open-drain mode.

## 7.7 Micro DMA controller

The micro DMA controller enables memory-to-memory, memory-to-peripheral, and peripheral-to-memory data transfers. The supported peripherals are: UART0 (transmit and receive), UART1 (transmit and receive), SSP/SPI (transmit and receive), ADC, RTC, 32-bit counter/timer 0 (match output channels 0 and 1), 32-bit counter/timer 1 (match output channels 0 and 1), 16-bit counter/timer 0 (match output channel 0), 16-bit counter/timer 1 (match output channel 0), comparator 0, comparator 1, GPIO0 to GPIO2.

## 7.7.1 Features

- Single AHB-Lite master for transferring data using a 32-bit address bus and 32-bit data bus.

- 21 DMA channels.

- Handshake signals and priority level programmable for each channel.

- Each priority level arbitrates using a fixed priority that is determined by the DMA channel number.

- Supports memory-to-memory, memory-to-peripheral, and peripheral-to-memory transfers.

- Supports multiple DMA cycle types and multiple DMA transfer widths.

- Performs all DMA transfers using the single AHB-Lite burst type.

## 7.8 CRC engine

The Cyclic Redundancy Check (CRC) engine with programmable polynomial settings supports several CRC standards commonly used. To save system power and bus bandwidth, the CRC engine supports DMA transfers.

## 7.8.1 Features

- Supports three common polynomials CRC-CCITT, CRC-16, and CRC-32.

- CRC-CCITT: x<sup>16</sup> + x<sup>12</sup> + x<sup>5</sup> + 1

- CRC-16:  $x^{16} + x^{15} + x^2 + 1$

- CRC-32:  $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$

- Bit order reverse and 1's complement programmable setting for input data and CRC sum.

- Programmable seed number setting.

- Supports CPU programmed I/O or DMA back-to-back transfer.

- Accept any size of data width per write: 8, 16 or 32-bit.

- 8-bit write: 1-cycle operation

- 16-bit write: 2-cycle operation (8-bit × 2-cycle)

- 32-bit write: 4-cycle operation (8-bit × 4-cycle)

## 7.9 Fast general purpose parallel I/O

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Separate registers allow setting or clearing any number of outputs simultaneously. The value of the output register may be read back as well as the current state of the port pins.

## 7.9.1 Features

- Bit level set and clear registers allow a single instruction to set or clear any number of bits in one port.

- Direction control of individual bits.

- All I/O default to inputs after reset.

## 7.10 UARTs

The LPC122x contains two UARTs. UART0 supports full modem control and RS-485/9-bit mode and allows both software address detection and automatic hardware address detection using 9-bit mode.

The UARTs include a fractional baud rate generator. Standard baud rates such as 115200 Bd can be achieved with any crystal frequency above 2 MHz.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- The I<sup>2</sup>C-bus controller supports multiple address recognition and a bus monitor mode.

## 7.13 10-bit ADC

The LPC122x contains one ADC. It is a single 10-bit successive approximation ADC with eight channels.

## 7.13.1 Features

- 10-bit successive approximation ADC.

- Input multiplexing among 8 pins.

- Power-down mode.

- Measurement range 0 V to V<sub>DD(3V3)</sub>.

- 10-bit conversion time of 257 kHz.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or counter/timer match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

## 7.14 Comparator block

The comparator block consists of two analog comparators.

## 7.14.1 Features

- Up to six selectable external sources per comparator; fully configurable on either positive or negative comparator input channels.

- BOD 0.9 V internal reference voltage selectable on both comparators; configurable on either positive or negative comparator input channels.

- 32-stage voltage ladder internal reference voltage selectable on both comparators; configurable on either positive or negative comparator input channels.

- Voltage ladder source voltage is selectable from an external pin or an internal 3.3 V voltage rail if external power source is not available.

- Voltage ladder can be separately powered down for applications only requiring the comparator function.

- Relaxation oscillator circuitry output for a feedback 555-style timer application.

- Common interrupt connected to NVIC.

- Comparator outputs selectable as synchronous or asynchronous.

## **NXP Semiconductors**

## 32-bit ARM Cortex-M0 microcontroller

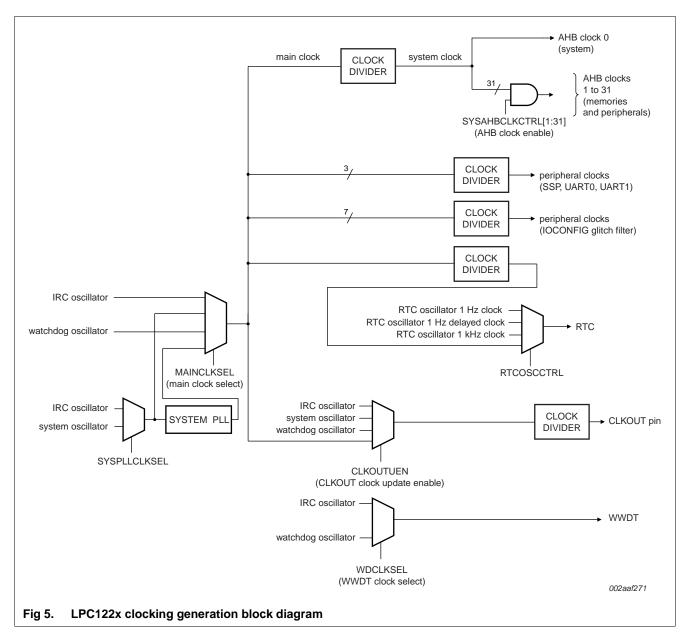

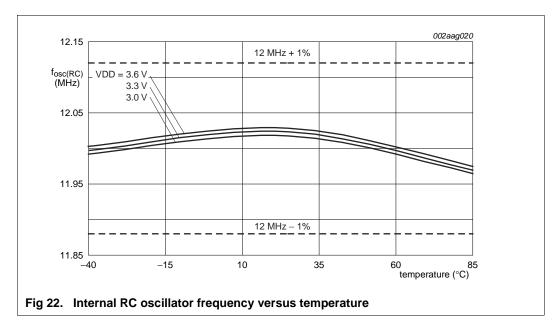

### 7.18.1.1 Internal RC oscillator

The IRC may be used as the clock source for the WDT, and/or as the clock that drives the PLL and subsequently the CPU. The nominal IRC frequency is 12 MHz. The IRC is trimmed to 1 % accuracy over the entire voltage and temperature range.

Upon power-up or any chip reset, the LPC122x use the IRC as the clock source. Software may later switch to one of the other available clock sources.

### 7.18.1.2 System oscillator

The system oscillator can be used as the clock source for the CPU, with or without using the PLL.

In Sleep mode, execution of instructions is suspended until either a reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and may generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

#### 7.18.5.2 Deep-sleep mode

In Deep-sleep mode, the chip is in Sleep mode, and in addition all analog blocks are shut down. As an exception, the user has the option to keep the watchdog oscillator and the BOD circuit running for self-timed wake-up and BOD protection. Deep-sleep mode allows for additional power savings.

The GPIO pins PIO0\_0 to PIO0\_11 (up to 12 pins total) and the RTC match interrupt can serve as a wake-up input to the start logic to wake up the chip from Deep-sleep mode.

Unless the watchdog oscillator is selected to run in Deep-sleep mode, the clock source should be switched to IRC before entering Deep-sleep mode, because the IRC can be switched on and off glitch-free.

### 7.18.5.3 Deep power-down mode

In Deep power-down mode, power is shut off to the entire chip with the exception of the Real Time Clock, the four general-purpose registers, and the WAKEUP pin. The LPC122x can wake up from Deep power-down mode via the WAKEUP pin or the RTC match interrupt.

When entering Deep power-down mode, an external pull-up resistor is required on the WAKEUP pin to hold it HIGH. The RESET pin must also be held HIGH to prevent it from floating while in Deep power-down mode.

## 7.19 System control

## 7.19.1 Start logic

The start logic connects external pins to corresponding interrupts in the NVIC. Each pin shown in <u>Table 3</u> as input to the start logic has an individual interrupt in the NVIC interrupt vector table. The start logic pins can serve as external interrupt pins when the chip is running. In addition, an input signal on the start logic pins can wake up the chip from Deep-sleep mode when all clocks are shut down.

The start logic must be configured in the system configuration block and in the NVIC before being used.

## 7.19.2 Reset

Reset has four sources on the LPC122x: the RESET pin, the Watchdog reset, power-on reset (POR), and the BrownOut Detection (BOD) circuit. The RESET pin is a Schmitt trigger input pin. Assertion of chip reset by any source, once the operating voltage attains a usable level, starts the IRC and initializes the flash controller.

When the internal Reset is removed, the processor begins executing at address 0, which is initially the Reset vector mapped from the boot block. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

An external pull-up resistor is required on the RESET pin if Deep power-down mode is used.

## 7.19.3 Brownout detection

The LPC122x includes four levels for monitoring the voltage on the  $V_{DD(3V3)}$  pin. If this voltage falls below one of the four selected levels, the BOD asserts an interrupt signal to the NVIC. This signal can be enabled for interrupt in the Interrupt Enable Register in the NVIC in order to cause a CPU interrupt; if not, software can monitor the signal by reading a dedicated status register. An additional threshold level can be selected to cause a forced reset of the chip.

## 7.19.4 Code security (Code Read Protection - CRP)

This feature of the LPC122x allows user to enable different levels of security in the system so that access to the on-chip flash and use of the SWD and ISP can be restricted. When needed, CRP is invoked by programming a specific pattern into a dedicated flash location. IAP commands are not affected by the CRP.

There are three levels of Code Read Protection:

- 1. CRP1 disables access to chip via the SWD and allows partial flash update (excluding flash sector 0) using a limited set of the ISP commands. This mode is useful when CRP is required and flash field updates are needed but all sectors can not be erased.

- CRP2 disables access to chip via the SWD and only allows full flash erase and update using a reduced set of the ISP commands.

- 3. Running an application with level CRP3 selected fully disables any access to chip via the SWD pins and the ISP. This mode effectively disables ISP override using PIO0\_12 pin, too. It is up to the user's application to provide (if needed) flash update mechanism using IAP calls or call reinvoke ISP command to enable flash update via UART0.

### CAUTION

If level three Code Read Protection (CRP3) is selected, no future factory testing can be performed on the device.

In addition to the three CRP levels, sampling of pin PIO0\_12 for valid user code can be disabled.

### 7.19.5 APB interface

The APB peripherals are located on one APB bus.

### 7.19.6 AHB-Lite

The AHB-Lite connects the CPU bus of the ARM Cortex-M0 to the flash memory, the main static RAM, and the Boot ROM.

## 7.19.7 External interrupt inputs

All GPIO pins can be level or edge sensitive interrupt inputs.

## 7.20 Emulation and debugging

Debug functions are integrated into the ARM Cortex-M0. Serial wire debug is supported.

## 7.21 Integer division routines

The LPC122x contain performance-optimized integer division routines with support for up to 32-bit width in the numerator and denominator. Routines for signed and unsigned division and division with remainder are available. The integer division routines are ROM-based to reduce code-size.

## 32-bit ARM Cortex-M0 microcontroller

## 10. Static characteristics

| Table 7.        | Static characteristics                                           |

|-----------------|------------------------------------------------------------------|

| $T_{amb} = -40$ | $^{\circ}\!C$ to +85 $^{\circ}\!C$ , unless otherwise specified. |

| Symbol               | Parameter                   | Conditions                                                                              |           | Min             | Тур <u>[1]</u> | Max                 | Unit |

|----------------------|-----------------------------|-----------------------------------------------------------------------------------------|-----------|-----------------|----------------|---------------------|------|

| V <sub>DD(IO)</sub>  | input/output supply voltage | on pin $V_{DD(IO)}$                                                                     |           | 3.0             | 3.3            | 3.6                 | V    |

| V <sub>DD(3V3)</sub> | supply voltage (3.3 V)      |                                                                                         |           | 3.0             | 3.3            | 3.6                 | V    |

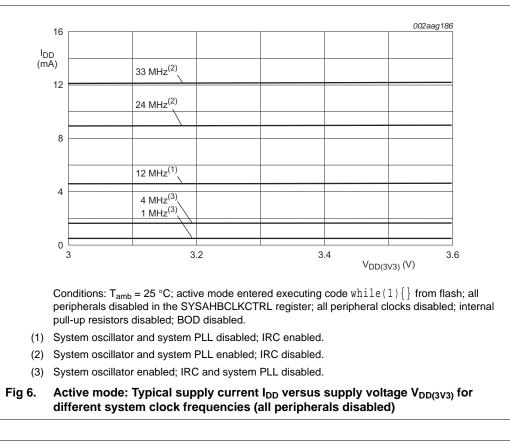

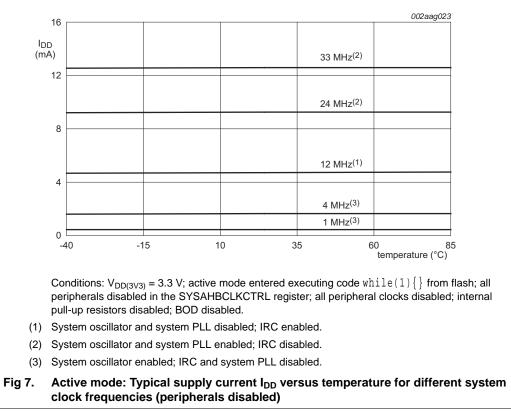

| DD                   | supply current              | Active mode;<br>$V_{DD(3V3)} = 3.3 V;$<br>$T_{amb} = 25 °C; code$                       |           |                 |                |                     |      |

|                      |                             | while(1){}                                                                              |           |                 |                |                     |      |

|                      |                             | executed from flash                                                                     |           |                 |                |                     |      |

|                      |                             | all peripherals disabled:                                                               |           |                 |                |                     |      |

|                      |                             | CCLK = 12 MHz                                                                           |           | -               | 4.6            | -                   | mA   |

|                      |                             | CCLK = 24 MHz                                                                           |           | -               | 9              | -                   | mA   |

|                      |                             | CCLK = 33 MHz                                                                           |           | -               | 12.2           | -                   | mA   |

|                      |                             | all peripherals enabled:                                                                |           |                 |                |                     |      |

|                      |                             | CCLK = 12 MHz                                                                           |           | -               | 6.6            | -                   | mA   |

|                      |                             | CCLK = 24 MHz                                                                           |           | -               | 10.9           | -                   | mA   |

|                      |                             | CCLK = 33 MHz                                                                           |           | -               | 14.1           | -                   | mA   |

|                      |                             | Sleep mode;<br>$V_{DD(3V3)} = 3.3 V;$<br>$T_{amb} = 25 °C;$<br>all peripherals disabled |           |                 |                |                     |      |

|                      |                             | CCLK = 12 MHz                                                                           |           | -               | 1.8            | -                   | mA   |

|                      |                             | CCLK = 24 MHz                                                                           |           | -               | 3.3            | -                   | mA   |

|                      |                             | CCLK = 33 MHz                                                                           |           | -               | 4.4            | -                   | mA   |

|                      |                             | Deep-sleep mode;<br>$V_{DD(3V3)} = 3.3 V;$<br>$T_{amb} = 25 °C$                         |           | -               | 30             | -                   | μA   |

|                      |                             | Deep power-down mode;<br>$V_{DD(3V3)} = 3.3 V;$<br>$T_{amb} = 25 °C$                    |           | -               | 720            | -                   | nA   |

| Normal-driv          | e output pins (Standard p   | ort pins, RESET)                                                                        |           |                 |                |                     |      |

| IIL                  | LOW-level input<br>current  | $V_1 = 0 V;$                                                                            |           | -               | -              | 100                 | nA   |

| Ін                   | HIGH-level input<br>current | $V_{I} = V_{DD(IO)};$                                                                   |           | -               | -              | 100                 | nA   |

| loz                  | OFF-state output<br>current | $V_O = 0 \ V; \ V_O = V_{DD(IO)};$                                                      |           | -               | -              | 100                 | nA   |

| VI                   | input voltage               | pin configured to provide a digital function                                            | [2][3][4] | 0               | -              | $V_{\text{DD(IO)}}$ | V    |

| Vo                   | output voltage              | output active                                                                           |           | 0               | -              | V <sub>DD(IO)</sub> | V    |

| V <sub>IH</sub>      | HIGH-level input<br>voltage |                                                                                         |           | $0.7V_{DD(IO)}$ | -              | -                   | V    |

## 32-bit ARM Cortex-M0 microcontroller

| Symbol           | Parameter                                     | Conditions                                   |                      | Min                          | Typ <u>[1]</u>  | Max                                   | Unit |

|------------------|-----------------------------------------------|----------------------------------------------|----------------------|------------------------------|-----------------|---------------------------------------|------|

| V <sub>IL</sub>  | LOW-level input voltage                       |                                              |                      | -                            | -               | 0.3V <sub>DD(I</sub><br><sub>O)</sub> | V    |

| V <sub>hys</sub> | hysteresis voltage                            |                                              |                      | -                            | 0.4             | -                                     | V    |

| V <sub>OH</sub>  | HIGH-level output voltage                     | low mode; $I_{OH} = -2 \text{ mA}$           |                      | V <sub>DD(IO)</sub> –<br>0.4 | -               | -                                     | V    |

|                  |                                               | high mode; $I_{OH} = -4 \text{ mA}$          |                      | V <sub>DD(IO)</sub> –<br>0.4 | -               | -                                     | V    |

| V <sub>OL</sub>  | LOW-level output                              | low mode; I <sub>OL</sub> = 2 mA             |                      | -                            | -               | 0.4                                   | V    |

|                  | voltage                                       | high mode; $I_{OL} = 4 \text{ mA}$           |                      |                              |                 | 0.4                                   |      |

| I <sub>OH</sub>  | HIGH-level output<br>current                  | low mode; $V_{OH} = V_{DD(IO)} - 0.4 V$      |                      | -2                           | -               | -                                     | mA   |

|                  |                                               | high mode; $V_{OH} = V_{DD(IO)} - 0.4 V$     |                      | -4                           | -               | -                                     | mA   |

| I <sub>OL</sub>  | LOW-level output                              | low mode; $V_{OL}$ = 0.4 V                   |                      | 2                            | -               | -                                     | mA   |

|                  | current                                       | high mode; $V_{OL}$ = 0.4 V                  |                      | 4                            | -               | -                                     | mA   |

| I <sub>OHS</sub> | HIGH-level<br>short-circuit output<br>current | V <sub>OH</sub> = 0 V                        | <u>[5]</u>           | -                            | -               | -45                                   | mA   |

| I <sub>OLS</sub> | LOW-level<br>short-circuit output<br>current  | $V_{OL} = V_{DDA}$                           | <u>[5]</u>           | -                            | -               | 50                                    | mA   |

| I <sub>pu</sub>  | pull-up current                               | $V_{I} = 0 V$                                |                      | -50                          | -80             | -100                                  | μΑ   |

| High-drive o     | output pins (PIO0_27, PIC                     | 0_28, PIO0_29, PIO0_12)                      |                      |                              |                 |                                       |      |

| I <sub>IL</sub>  | LOW-level input<br>current                    | $V_1 = 0 V;$                                 |                      | -                            | -               | 100                                   | nA   |

| I <sub>IH</sub>  | HIGH-level input<br>current                   | $V_{I} = V_{DD(IO)};$                        |                      | -                            | -               | 100                                   | nA   |

| I <sub>OZ</sub>  | OFF-state output<br>current                   | $V_O = 0 V; V_O = V_{DD(IO)};$               |                      | -                            | -               | 100                                   | nA   |

| VI               | input voltage                                 | pin configured to provide a digital function | <u>[2][3]</u><br>[4] | 0                            | -               | V <sub>DD(IO)</sub>                   | V    |

| Vo               | output voltage                                | output active                                |                      | 0                            | -               | V <sub>DD(IO)</sub>                   | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                      |                                              |                      | $0.7V_{DD(IO)}$              | -               | -                                     | V    |

| V <sub>IL</sub>  | LOW-level input voltage                       |                                              | -                    | -                            | $0.3V_{DD(IO)}$ | -                                     | -    |

| V <sub>hys</sub> | hysteresis voltage                            |                                              |                      |                              | -               | -                                     | V    |

| V <sub>OH</sub>  | HIGH-level output voltage                     | low mode; $I_{OH} = -20 \text{ mA}$          |                      | V <sub>DD(IO)</sub> -<br>0.7 | -               | -                                     | V    |

|                  |                                               | high mode; $I_{OH} = -28 \text{ mA}$         |                      | V <sub>DD(IO)</sub> -<br>0.7 | -               | -                                     | V    |

| V <sub>OL</sub>  | LOW-level output                              | low mode; I <sub>OL</sub> = 12 mA            |                      | -                            | -               | 0.4                                   | V    |

|                  | voltage                                       | high mode; I <sub>OL</sub> = 18 mA           |                      | -                            | -               | 0.4                                   | V    |

## Table 7.Static characteristics ... continued $T_{amb} = -40$ °C to +85 °C, unless otherwise specified.

32 of 61

## 10.1 Peripheral power consumption

The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled in the SYSAHBCLKCFG and PDRUNCFG (for analog blocks) registers. All other blocks are disabled in both registers and no code is executed. Measured on a typical sample at  $T_{amb} = 25$  °C and  $V_{DD(3V3)} = 3.3$  V.

| Table 8. | Peripheral power consumption |

|----------|------------------------------|

|----------|------------------------------|

| Peripheral                                  | Typical current consumption I <sub>DD</sub> in mA |                            |           |                      |      |  |  |  |  |

|---------------------------------------------|---------------------------------------------------|----------------------------|-----------|----------------------|------|--|--|--|--|

|                                             | Frequency<br>independent                          | 24 MHz                     |           | 12 MHz               |      |  |  |  |  |

|                                             |                                                   | system<br>oscillator + PLL | IRC + PLL | system<br>oscillator | IRC  |  |  |  |  |

| IRC                                         | 0.29                                              | -                          | -         | -                    | -    |  |  |  |  |

| PLL (PLL output<br>frequency = 24 MHz)      | 1.87                                              | -                          | -         | -                    | -    |  |  |  |  |

| WDosc (WDosc output<br>frequency = 500 kHz) | 0.25                                              | -                          | -         | -                    | -    |  |  |  |  |

| BOD                                         | 0.06                                              | -                          | -         | -                    | -    |  |  |  |  |

| Analog comparator 0/1                       | -                                                 | 0.05                       | 0.05      | 0.03                 | 0.02 |  |  |  |  |

| ADC                                         | -                                                 | 1.86                       | 1.85      | 1.61                 | 1.61 |  |  |  |  |

| CRC engine                                  | -                                                 | 0.04                       | 0.04      | 0.02                 | 0.02 |  |  |  |  |

| 16-bit timer 0 (CT16B0)                     | -                                                 | 0.09                       | 0.09      | 0.04                 | 0.04 |  |  |  |  |

| 16-bit timer 1 (CT16B1)                     | -                                                 | 0.09                       | 0.09      | 0.04                 | 0.04 |  |  |  |  |

| 32-bit timer 0 (CT32B0)                     | -                                                 | 0.08                       | 0.08      | 0.04                 | 0.04 |  |  |  |  |

| 32-bit timer 1 (CT32B1)                     | -                                                 | 0.08                       | 0.08      | 0.04                 | 0.04 |  |  |  |  |

| GPIO0                                       | -                                                 | 0.34                       | 0.34      | 0.17                 | 0.17 |  |  |  |  |

| GPIO1                                       | -                                                 | 0.34                       | 0.34      | 0.17                 | 0.17 |  |  |  |  |

| GPIO2                                       | -                                                 | 0.36                       | 0.37      | 0.18                 | 0.18 |  |  |  |  |

| 12C                                         | -                                                 | 0.09                       | 0.09      | 0.05                 | 0.05 |  |  |  |  |

| IOCON                                       | -                                                 | 0.09                       | 0.10      | 0.05                 | 0.05 |  |  |  |  |

| RTC                                         | -                                                 | 0.10                       | 0.10      | 0.05                 | 0.05 |  |  |  |  |

| SSP                                         | -                                                 | 0.30                       | 0.29      | 0.15                 | 0.15 |  |  |  |  |

| UART0                                       | -                                                 | 0.52                       | 0.51      | 0.26                 | 0.26 |  |  |  |  |

| UART1                                       | -                                                 | 0.52                       | 0.51      | 0.26                 | 0.26 |  |  |  |  |

| DMA                                         | -                                                 | 0.18                       | 0.18      | 0.09                 | 0.09 |  |  |  |  |

| WWDT                                        | -                                                 | 0.06                       | 0.06      | 0.03                 | 0.03 |  |  |  |  |

## **10.2** Power consumption

Power measurements in Active, Sleep, and Deep-sleep modes were performed under the following conditions (see *LPC122x user manual*):

- Active mode: all GPIO pins set to input with external pull-up resistors.

- Sleep and Deep-sleep modes: all GPIO pins set to output driving LOW.

- Deep power-down mode: all GPIO pins set to input with external pull-up resistors.

## 32-bit ARM Cortex-M0 microcontroller

All information provided in this document is subject to legal disclaimers

## 11.4 Internal oscillators

## Table 14. Dynamic characteristic: internal oscillators

| $T_{amb} = -40^{-1}$ C to +65 <sup>-1</sup> C, $v_{DD(3V3)}$ over specified ranges. |                                  |            |       |                |       |      |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------|------------|-------|----------------|-------|------|--|--|--|--|

| Symbol                                                                              | Parameter                        | Conditions | Min   | Typ <u>[2]</u> | Мах   | Unit |  |  |  |  |

| $f_{osc(RC)}$                                                                       | internal RC oscillator frequency | -          | 11.88 | 12             | 12.12 | MHz  |  |  |  |  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at nominal supply voltages.

#### Table 15. Dynamic characteristics: Watchdog oscillator

| Symbol    | Parameter                        | Conditions                                                  |        | Min | Typ <u>[1]</u> | Мах | Unit |

|-----------|----------------------------------|-------------------------------------------------------------|--------|-----|----------------|-----|------|

| fosc(int) | internal oscillator<br>frequency | DIVSEL = 0x1F, FREQSEL = 0x1<br>in the WDTOSCCTRL register; | [2][3] | -   | 7.8            | -   | kHz  |

|           |                                  | DIVSEL = 0x00, FREQSEL = 0xF<br>in the WDTOSCCTRL register  | [2][3] | -   | 1700           | -   | kHz  |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] The typical frequency spread over processing and temperature (T<sub>amb</sub> =  $-40 \degree C$  to +85  $\degree C$ ) is ±40 %.

[3] See the LPC122x user manual.

Fig 26. Package outline SOT313-2 (LQFP48)

32-bit ARM Cortex-M0 microcontroller

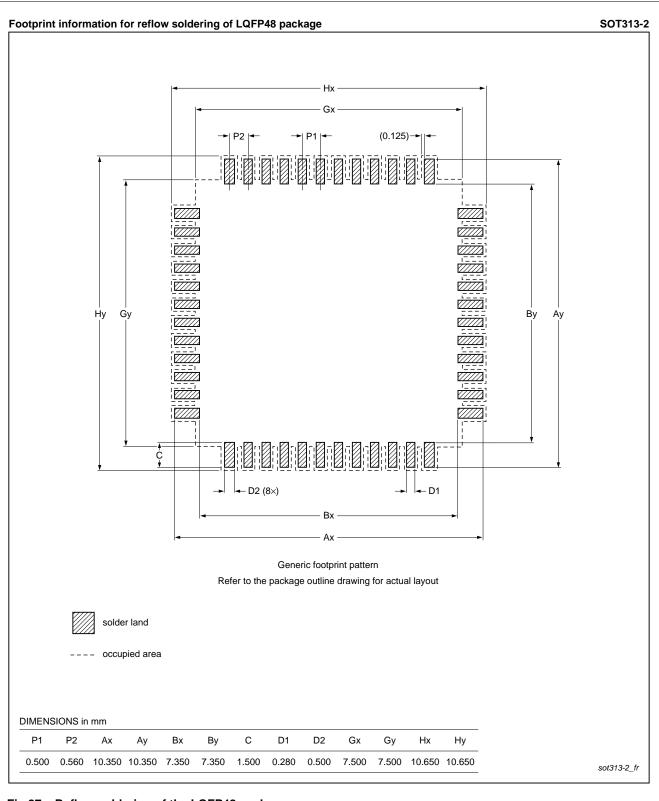

## 14. Soldering

Fig 27. Reflow soldering of the LQFP48 package