# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 4                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 4x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 8-VDFN Exposed Pad                                                     |

| Supplier Device Package    | 8-DFN-EP (4x4)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qa4cfqer |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

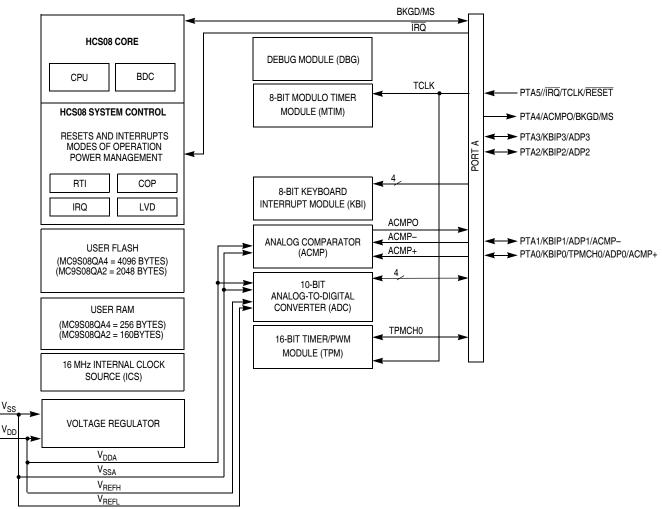

## 1 MCU Block Diagram

The block diagram, Figure 1, shows the structure of the MC9S08QA4 MCU.

NOTES:

- <sup>1</sup> Port pins are software configurable with pullup device if input port.

- <sup>2</sup> Port pins are software configurable for output drive strength.

- <sup>3</sup> Port pins are software configurable for output slew rate control.

- <sup>4</sup> IRQ contains a software configurable (IRQPDD) pullup device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>5</sup> RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>6</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>7</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

### Figure 1. MC9S08QA4 Series Block Diagram

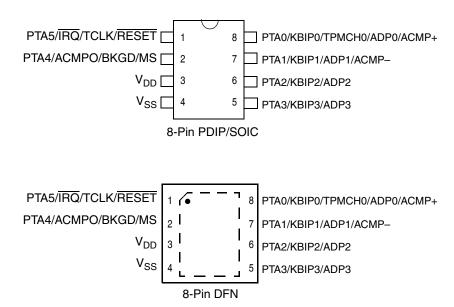

# 2 Pin Assignments

This section shows the pin assignments in the packages available for the MC9S08QA4 series.

**Pin Assignments**

| DIN   | _                 |       | Priority |                   |                    |

|-------|-------------------|-------|----------|-------------------|--------------------|

| PIN   | Lowest            |       |          |                   | Highest            |

| 8-Pin | Port Pin          | Alt 1 | Alt 2    | Alt 3             | Alt 4              |

| 1     | PTA5 <sup>1</sup> | ĪRQ   | TCLK     |                   | RESET              |

| 2     | PTA4              |       | ACMPO    | BKGD              | MS                 |

| 3     |                   |       |          |                   | V <sub>DD</sub>    |

| 4     |                   |       |          |                   | V <sub>SS</sub>    |

| 5     | PTA3              | KBIP3 | ADP3     |                   |                    |

| 6     | PTA2              | KBIP2 | ADP2     |                   |                    |

| 7     | PTA1              | KBIP1 |          | ADP1 <sup>2</sup> | ACMP-2             |

| 8     | PTA0              | KBIP0 | TPMCH0   | ADP0 <sup>2</sup> | ACMP+ <sup>2</sup> |

### Table 1. Pin Sharing Priority

<sup>1</sup> Pin does not contain a clamp diode to  $V_{DD}$  and must not be driven above  $V_{DD}$ . The voltage measured on the internally pulled-up RESET pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ .

<sup>2</sup> If ACMP and ADC are both enabled, both will have access to the pin.

Figure 2. MC9S08QA4 Series in 8-Pin Packages

| Rating                                   | Symbol         | Value                                         | Unit |

|------------------------------------------|----------------|-----------------------------------------------|------|

| Operating temperature range (packaged)   | T <sub>A</sub> | T <sub>L</sub> to T <sub>H</sub><br>–40 to 85 | °C   |

| Thermal resistance<br>Single-layer board |                |                                               |      |

| 8-pin PDIP                               |                | 113                                           |      |

| 8-pin NB SOIC                            | $\theta_{JA}$  | 150                                           | °C/W |

| 8-pin DFN                                |                | 179                                           |      |

| Thermal resistance<br>Four-layer board   |                |                                               |      |

| 8-pin PDIP                               |                | 72                                            |      |

| 8-pin NB SOIC                            | $\theta_{JA}$  | 87                                            | °C/W |

| 8-pin DFN                                |                | 41                                            | 1    |

**Table 3. Thermal Characteristics**

The average chip-junction temperature  $(T_J)$  in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

—  $T_A =$  Ambient temperature, °C

—  $\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W

- P<sub>D</sub> = P<sub>int</sub> + P<sub>I/O</sub>

—  $P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

—  $P_{I/O}$  = Power dissipation on input and output pins — user-determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K \div (T_{J} + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2 \qquad \qquad Eqn. 3$$

where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

### 3.4 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM) and the charge device model (CDM).

| Parameter                                                                                                                                                                                                                                                                                                            | Symbol              | Min                   | Typical | Max                  | Unit     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|---------|----------------------|----------|

| (V <sub>DD</sub> rising)                                                                                                                                                                                                                                                                                             |                     | 2.16                  | 2.19    | 2.27                 |          |

| Power on reset (POR) re-arm voltage                                                                                                                                                                                                                                                                                  | V <sub>por</sub>    | —                     | 1.4     | —                    | V        |

| Bandgap voltage reference                                                                                                                                                                                                                                                                                            | V <sub>BG</sub>     | 1.18                  | 1.20    | 1.21                 | V        |

| Input high voltage ( $V_{DD} > 2.3 \text{ V}$ ) (all digital inputs)                                                                                                                                                                                                                                                 | M                   | $0.70 \times V_{DD}$  | _       | _                    | V        |

| Input high voltage (1.8 V $\leq$ V_{DD} $\leq$ 2.3 V) (all digital inputs)                                                                                                                                                                                                                                           | V <sub>IH</sub>     | $0.85 \times V_{DD}$  | _       | _                    | V        |

| Input low voltage (V <sub>DD</sub> > 2.3 V) (all digital inputs)                                                                                                                                                                                                                                                     |                     | —                     |         | $0.35 \times V_{DD}$ |          |

| Input low voltage (1.8 V $\leq$ V_{DD} $\leq$ 2.3 V) (all digital inputs)                                                                                                                                                                                                                                            | V <sub>IL</sub>     |                       |         | $0.30 \times V_{DD}$ | V        |

| Input hysteresis (all digital inputs)                                                                                                                                                                                                                                                                                | V <sub>hys</sub>    | $0.06 \times V_{DD}$  |         | _                    | V        |

| Input leakage current (per pin)<br>$V_{In} = V_{DD}$ or $V_{SS}$ , all input-only pins                                                                                                                                                                                                                               | <sub>In</sub>       | _                     | 0.025   | 1.0                  | μA       |

| High impedance (off-state) leakage current (per pin) $V_{ln} = V_{DD}$ or $V_{SS}$ , all input/output                                                                                                                                                                                                                | ll <sub>oz</sub> l  | _                     | 0.025   | 1.0                  | μA       |

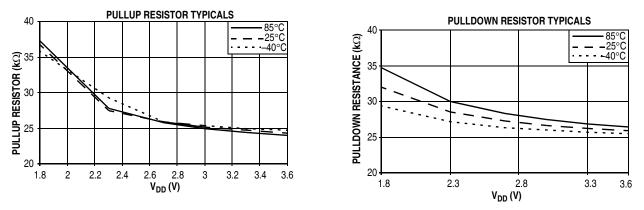

| Internal pullup resistors <sup>3,4</sup>                                                                                                                                                                                                                                                                             | R <sub>PU</sub>     | 17.5                  | _       | 52.5                 | kΩ       |

| Internal pulldown resistor (KBI)                                                                                                                                                                                                                                                                                     | R <sub>PD</sub>     | 17.5                  | _       | 52.5                 | kΩ       |

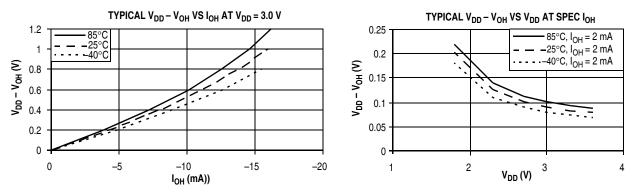

| Output high voltage — low drive (PTxDSn = 0) $I_{OH} = -2 \text{ mA} (V_{DD} \ge 1.8 \text{ V})$                                                                                                                                                                                                                     |                     | V <sub>DD</sub> – 0.5 | _       | _                    |          |

|                                                                                                                                                                                                                                                                                                                      | V <sub>OH</sub>     | V <sub>DD</sub> – 0.5 |         |                      | V        |

| Maximum total I <sub>OH</sub> for all port pins                                                                                                                                                                                                                                                                      | II <sub>OHT</sub> I | _                     | _       | 60                   | mA       |

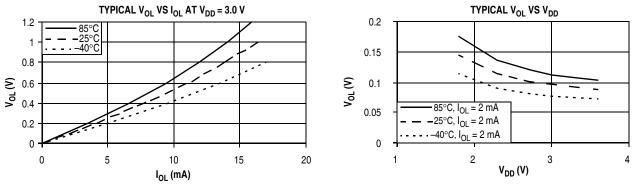

| Output low voltage — low drive (PTxDSn = 0) $I_{OL}$ = 2.0 mA (V <sub>DD</sub> $\ge$ 1.8 V)                                                                                                                                                                                                                          |                     | _                     | _       | 0.5                  | v        |

| $ \begin{array}{l} \text{Output low voltage } & \text{ high drive } (\text{PTxDSn} = 1) \\ \text{I}_{OL} = 10.0 \text{ mA } (\text{V}_{DD} \geq 2.7 \text{ V}) \\ \text{I}_{OL} = 6 \text{ mA } (\text{V}_{DD} \geq 2.3 \text{ V}) \\ \text{I}_{OL} = 3 \text{ mA } (\text{V}_{DD} \geq 1.8 \text{ V}) \end{array} $ | V <sub>OL</sub>     | <br>                  |         | 0.5<br>0.5<br>0.5    | v        |

| Maximum total I <sub>OL</sub> for all port pins                                                                                                                                                                                                                                                                      | I <sub>OLT</sub>    | —                     | —       | 60                   | mA       |

| DC injection current <sup>2, 5, 6, 7</sup><br>$V_{In} < V_{SS}, V_{In} > V_{DD}$<br>Single pin limit<br>Total MCU limit, includes sum of all stressed pins                                                                                                                                                           | I <sub>IC</sub>     | -0.2<br>-5            |         | 0.2<br>5             | mA<br>mA |

| Input capacitance (all non-supply pins)                                                                                                                                                                                                                                                                              | C <sub>In</sub>     | —                     | _       | 7                    | pF       |

Table 6. DC Characteristics (Temperature Range = -40 to 85°C Ambient) (continued)

<sup>1</sup> RAM will retain data down to POR voltage. RAM data not guaranteed to be valid following a POR.

<sup>2</sup> This parameter is characterized and not tested on each device.

$^3~$  Measurement condition for pull resistors:  $V_{In}$  =  $V_{SS}$  for pullup and  $V_{In}$  =  $V_{DD}$  for pulldown.

<sup>4</sup> PTA5/IRQ/TCLK/RESET pullup resistor may not pull up to the specified minimum V<sub>IH</sub>. However, all ports are functionally tested to guarantee that a logic 1 will be read on any port input when the pullup is enabled and no DC load is present on the pin.

$^5\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$

- <sup>6</sup> Input must be current-limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>7</sup> Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

Figure 3. Pullup and Pulldown Typical Resistor Values ( $V_{DD} = 3.0 \text{ V}$ )

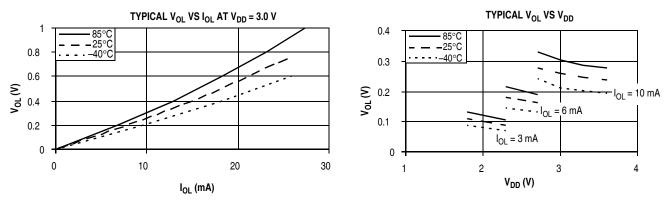

Figure 4. Typical Low-Side Driver (Sink) Characteristics — Low Drive (PTxDSn = 0)

Figure 5. Typical Low-Side Driver (Sink) Characteristics — High Drive (PTxDSn = 1)

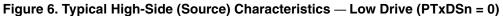

Figure 7. Typical High-Side (Source) Characteristics — High Drive (PTxDSn = 1)

### 3.6 Supply Current Characteristics

This section includes information about power supply current in various operating modes.

| Parameter                                                      | Symbol            | V <sub>DD</sub> (V) <sup>1</sup> | Typical <sup>2</sup> | Max    | T (°C) |

|----------------------------------------------------------------|-------------------|----------------------------------|----------------------|--------|--------|

| Run supply current <sup>3</sup> measured in FBE mode at        | RI <sub>DD</sub>  | 3                                | 3.5 mA               | 5 mA   | 85     |

| f <sub>Bus</sub> = 8 MHz                                       | DD                | 2                                | 2.6 mA               |        | 85     |

| Run supply current <sup>3</sup> measured in FBE mode at        | RI <sub>DD</sub>  | 3                                | 490 μA               | 1 mA   | 85     |

| f <sub>Bus</sub> = 1 MHz                                       | UUDD              | 2                                | 370 μA               | -      | 85     |

| Wait mode supply current <sup>4</sup> measured in FBE at 8 MHz | WI <sub>DD</sub>  | 3                                | 1 mA                 | 1.5 mA | 85     |

| Stop1 mode supply current                                      | S11               | 3                                | 475 nA               | 1.2 μA | 85     |

|                                                                | S1I <sub>DD</sub> | 2                                | 470 nA               | -      | 85     |

| Stop2 mode supply current                                      | 521               | 3                                | 600 nA               | 2 μΑ   | 85     |

|                                                                | S2I <sub>DD</sub> | 2                                | 550 nA               | _      | 85     |

| Stop3 mode supply current                                      | Sal               | 3                                | 750 nA               | 6 μΑ   | 85     |

|                                                                | S3I <sub>DD</sub> | 2                                | 680 nA               |        | 85     |

| RTI adder to stop1, stop2, or stop3 <sup>4</sup>               |                   | 3                                | 300 nA               | _      | 85     |

|                                                                |                   | 2                                | 300 nA               | _      | 85     |

| LVD adder to stop3 (LVDE = LVDSE = $1$ ) <sup>4</sup>          | _                 | 3                                | 70 μA                | _      | 85     |

|                                                                |                   | 2                                | 60 μ <b>Α</b>        | _      | 85     |

Table 7. Supply Current Characteristics

- <sup>1</sup> 3 V values are 100% tested; 2 V values are characterized but not tested.

- $^2~$  Typicals are measured at 25 °C.

- <sup>3</sup> Does not include any DC loads on port pins.

<sup>4</sup> Most customers are expected to find that auto-wakeup from a stop mode can be used instead of the higher current wait mode.

### 3.7 Internal Clock Source (ICS) Characteristics

### Table 8. ICS Specifications (Temperature Range = -40 to 85°C Ambient)

| Characteristic                                                                                                                                              | Symbol                   | Min   | Typical <sup>1</sup> | Max      | Unit              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|----------------------|----------|-------------------|

| Internal reference start-up time                                                                                                                            | t <sub>IRST</sub>        |       | 60                   | 100      | μS                |

| Average internal reference frequency — untrimmed                                                                                                            | f <sub>int_ut</sub>      | 25    | 32.7                 | 41.66    | kHz               |

| Average internal reference frequency — trimmed                                                                                                              | f <sub>int_t</sub>       | 31.25 | —                    | 39.06    | kHz               |

| DCO output frequency range — untrimmed                                                                                                                      | f <sub>dco_ut</sub>      | 12.8  | 16.8                 | 21.33    | MHz               |

| DCO output frequency range — trimmed                                                                                                                        | f <sub>dco_t</sub>       | 16    | _                    | 20       | MHz               |

| Resolution of trimmed DCO output frequency at fixed voltage and temperature <sup>2</sup>                                                                    | $\Delta f_{dco\_res\_t}$ | _     | ±0.1                 | ±0.2     | %f <sub>dco</sub> |

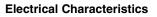

| Total deviation of DCO output from trimmed frequency <sup>2</sup><br>At 8 MHz over full voltage and temperature range<br>At 8 MHz and 3.6 V from 0 to 70 °C | $\Delta f_{dco_t}$       | _     | −1.0 to 0.5<br>±0.5  | ±2<br>±1 | %f <sub>dco</sub> |

| FLL acquisition time <sup>2,3</sup>                                                                                                                         | t <sub>Acquire</sub>     | _     | —                    | 1.5      | ms                |

| Long term jitter of DCO output clock (averaged over 2 ms interval)                                                                                          | C <sub>Jitter</sub>      | _     | 0.02                 | 0.2      | %f <sub>dco</sub> |

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25 °C, or is typical recommended value.

<sup>2</sup> This parameter is characterized and not tested on each device.

<sup>3</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value changed.

### 3.8 AC Characteristics

This section describes timing characteristics for each peripheral system.

### 3.8.1 Control Timing

| Parameter                                                                                                                              | Symbol                                | Min                         | Typical <sup>1</sup> | Мах  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|----------------------|------|------|

| Bus frequency $(t_{cyc} = 1/f_{Bus})$                                                                                                  | f <sub>Bus</sub>                      | 0                           |                      | 10   | MHz  |

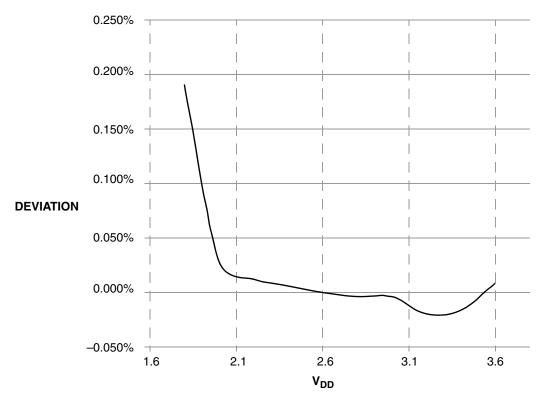

| Real-time interrupt internal oscillator period (see Table 9)                                                                           | t <sub>RTI</sub>                      | 700                         | 1000                 | 1300 | μs   |

| External reset pulse width <sup>2</sup>                                                                                                | t <sub>extrst</sub>                   | 100                         | —                    | —    | ns   |

| IRQ pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>3</sup>                                                     | tı∟ıн                                 | 100<br>1.5 t <sub>cyc</sub> | _                    | _    | ns   |

| KBIPx pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>3</sup>                                                   | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 t <sub>cyc</sub> | _                    | _    | ns   |

| Port rise and fall time (load = 50 pF) <sup>4</sup><br>Slew rate control disabled (PTxSE = 0)<br>Slew rate control enabled (PTxSE = 1) | t <sub>Rise</sub> , t <sub>Fall</sub> |                             | 3<br>30              |      | ns   |

| BKGD/MS setup time after issuing background debug force reset to enter user or BDM modes                                               | t <sub>MSSU</sub>                     | 500                         | —                    | —    | ns   |

| BKGD/MS hold time after issuing background debug force reset to enter user or BDM modes <sup>5</sup>                                   | t <sub>MSH</sub>                      | 100                         | _                    | _    | μs   |

### Table 9. Control Timing

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25°C.

$^2$  This is the shortest pulse that is guaranteed to be recognized.

<sup>3</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^4$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40°C to 85°C.

<sup>5</sup> To enter BDM mode following a POR, BKGD/MS should be held low during the power-up and for a hold time of t<sub>MSH</sub> after V<sub>DD</sub> rises above V<sub>LVD</sub>.

Figure 9. Typical RTI Clock Period vs. Temperature

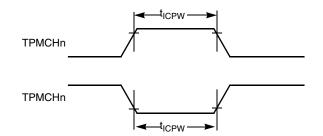

Figure 13. Timer Input Capture Pulse

### 3.9 Analog Comparator (ACMP) Electricals

| Characteristic                         | Symbol             | Min            | Typical | Max             | Unit |

|----------------------------------------|--------------------|----------------|---------|-----------------|------|

| Supply voltage                         | V <sub>DD</sub>    | 1.80           | _       | 3.60            | V    |

| Supply current (active)                | I <sub>DDAC</sub>  | _              | 20      | _               | μA   |

| Analog input voltage                   | V <sub>AIN</sub>   | $V_{SS} - 0.3$ | _       | V <sub>DD</sub> | V    |

| Analog input offset voltage            | V <sub>AIO</sub>   | _              | 20      | 40              | mV   |

| Analog comparator hysteresis           | V <sub>H</sub>     | 3.0            | 9.0     | 15.0            | mV   |

| Analog input leakage current           | I <sub>ALKG</sub>  | _              | _       | 1.0             | μA   |

| Analog comparator initialization delay | t <sub>AINIT</sub> | _              | _       | 1.0             | μS   |

### 3.10 ADC Characteristics

| Characteristic              | Conditions                                                            | Symbol            | Min             | Typical <sup>1</sup> | Мах             | Unit | Comment            |

|-----------------------------|-----------------------------------------------------------------------|-------------------|-----------------|----------------------|-----------------|------|--------------------|

| Supply voltage              | Absolute                                                              | V <sub>DD</sub>   | 1.8             | —                    | 3.6             | V    |                    |

| Input voltage               |                                                                       | V <sub>ADIN</sub> | V <sub>SS</sub> | —                    | V <sub>DD</sub> | V    |                    |

| Input capacitance           |                                                                       | C <sub>ADIN</sub> | —               | 4.5                  | 5.5             | pF   |                    |

| Input resistance            |                                                                       | R <sub>ADIN</sub> | _               | 5                    | 7               | kΩ   |                    |

| Analog source<br>resistance | 10 bit mode<br>f <sub>ADCK</sub> > 4 MHz<br>f <sub>ADCK</sub> < 4 MHz | R <sub>AS</sub>   | _               | _                    | 5<br>10         | kΩ   | External to<br>MCU |

|                             | 8 bit mode (all valid f <sub>ADCK</sub> )                             |                   |                 | —                    | 10              |      |                    |

| ADC conversion              | High Speed (ADLPC=0)                                                  | f                 | 0.4             | —                    | 8.0             | MHz  |                    |

| clock frequency             | Low Power (ADLPC=1)                                                   | f <sub>ADCK</sub> | 0.4             | —                    | 4.0             |      |                    |

Typical values assume  $V_{DD}$  = 3.0 V, Temp = 25°C,  $f_{ADCK}$  =1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

1

| Characteristic                | Conditions              | Symbol              | Min | Typical <sup>1</sup> | Мах  | Unit             | Comment                               |  |

|-------------------------------|-------------------------|---------------------|-----|----------------------|------|------------------|---------------------------------------|--|

| Conversion time               | Short sample (ADLSMP=0) |                     | _   | 20                   | _    | ADCK             | See                                   |  |

| (including sample time)       | Long sample (ADLSMP=1)  | t <sub>ADC</sub>    | _   | 40                   | _    | cycles           | MC9S08QA4<br>Series                   |  |

|                               | Short sample (ADLSMP=0) |                     |     | 3.5                  |      | ADCK             | <i>Reference</i><br><i>Manual</i> for |  |

| Sample time                   | Long sample (ADLSMP=1)  | t <sub>ADS</sub>    | _   | 23.5                 | _    | cycles           | conversion<br>time variances          |  |

| <b>- - - - - - - - - -</b>    | 10-bit mode             | _                   | _   | ±1.5                 | ±3.5 | 1.002            | Includes                              |  |

| Total unadjusted error        | 8-bit mode              | E <sub>TUE</sub>    | _   | ±0.7                 | ±1.5 | LSB <sup>2</sup> | quantization                          |  |

| <b>B</b>                      | 10-bit mode             |                     |     | ±0.5                 | ±1.0 |                  | Monotonicity                          |  |

| Differential<br>non-linearity | 8-bit mode              | DNL                 | _   | ±0.3                 | ±0.5 | LSB <sup>2</sup> | and no<br>missing codes<br>guaranteed |  |

| Integral non-linearity        | 10-bit mode             | - INL -             | _   | ±0.5                 | ±1.0 | LSB <sup>2</sup> |                                       |  |

| integral non-linearity        | 8-bit mode              |                     | _   | ±0.3                 | ±0.5 | LOD              |                                       |  |

| Zero-scale error              | 10-bit mode             | E <sub>ZS</sub>     | _   | ±1.5                 | ±2.1 | LSB <sup>2</sup> | V <sub>ADIN</sub> = V <sub>SS</sub>   |  |

| Zero-scale error              | 8-bit mode              | ►ZS                 |     | ±0.5                 | ±0.7 | LOD              |                                       |  |

| Full-scale error              | 10-bit mode             | E <sub>FS</sub>     | 0   | ±1.0                 | ±1.5 | LSB <sup>2</sup> | V <sub>ADIN</sub> = V <sub>DD</sub>   |  |

|                               | 8-bit mode              | ⊢FS                 | 0   | ±0.5                 | ±0.5 | LOD              | VADIN − VDD                           |  |

| Quantization error            | 10-bit mode             | E <sub>Q</sub>      |     | —                    | ±0.5 | LSB <sup>2</sup> |                                       |  |

| Quantization entri            | 8-bit mode              | LQ                  |     | —                    | ±0.5 | 100              |                                       |  |

| Input leakage error           | 10-bit mode             | Ε <sub>IL</sub>     | 0   | ±0.2                 | ±4   | LSB <sup>2</sup> | Pad leakage <sup>3 *</sup>            |  |

| Input leakage error           | 8-bit mode              |                     | 0   | ±0.1                 | ±1.2 | LOB              | R <sub>AS</sub>                       |  |

| Temp sensor                   | −40°C − 25°C            | m                   | —   | 1.646                | _    | mV/°C            |                                       |  |

| slope                         | 25°C – 85°C             |                     | _   | 1.769                |      |                  |                                       |  |

| Temp sensor<br>voltage        | 25°C                    | V <sub>TEMP25</sub> | _   | 701.2                | _    | mV               |                                       |  |

| Table 13. 3 V 10-Bit ADC Characteristics ( | (continued) |

|--------------------------------------------|-------------|

|--------------------------------------------|-------------|

<sup>1</sup> Typical values assume V<sub>DD</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> 1 LSB = (V<sub>REFH</sub> - V<sub>REFL</sub>)/2<sup>N</sup>

<sup>3</sup> Based on input pad leakage current. Refer to pad electricals.

#### 3.11 **Flash Specifications**

This section provides details about program/erase times and program-erase endurance for the flash memory.

Program and erase operations do not require any special power sources other than the normal V<sub>DD</sub> supply. For more detailed information about program/erase operations, see *MC9S08QA4 Series Reference Manual*.

| Characteristic                                                                                                   | Symbol                  | Min    | Typical | Мах  | Unit              |

|------------------------------------------------------------------------------------------------------------------|-------------------------|--------|---------|------|-------------------|

| Supply voltage for program/erase<br>-40°C to 85°C                                                                | V <sub>prog/erase</sub> | 1.8    | _       | 3.6  | V                 |

| Supply voltage for read operation                                                                                | V <sub>Read</sub>       | 1.8    | —       | 3.6  | V                 |

| Internal FCLK frequency <sup>1</sup>                                                                             | f <sub>FCLK</sub>       | 150    | —       | 200  | kHz               |

| Internal FCLK period (1/FCLK)                                                                                    | t <sub>Fcyc</sub>       | 5      | —       | 6.67 | μS                |

| Byte program time (random location) <sup>2</sup>                                                                 | t <sub>prog</sub>       |        | 9       |      | t <sub>Fcyc</sub> |

| Byte program time (burst mode) <sup>2</sup>                                                                      | t <sub>Burst</sub>      |        | 4       |      | t <sub>Fcyc</sub> |

| Page erase time <sup>2</sup>                                                                                     | t <sub>Page</sub>       | 4000   |         |      | t <sub>Fcyc</sub> |

| Mass erase time <sup>2</sup>                                                                                     | t <sub>Mass</sub>       |        | 20,000  |      | t <sub>Fcyc</sub> |

| Program/erase endurance <sup>3</sup><br>T <sub>L</sub> to T <sub>H</sub> = $-40^{\circ}$ C to + 85°C<br>T = 25°C |                         | 10,000 |         |      | cycles            |

| Data retention <sup>4</sup>                                                                                      | t <sub>D_ret</sub>      | 15     | 100     |      | years             |

Table 14. Flash Characteristics

<sup>1</sup> The frequency of this clock is controlled by a software setting.

<sup>2</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>3</sup> **Typical endurance for flash** was evaluated for this product family on the 9S12Dx64. For additional information on how Motorola defines typical endurance, please refer to Engineering Bulletin EB619/D, *Typical Endurance for Nonvolatile Memory*.

<sup>4</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines typical data retention, please refer to Engineering Bulletin EB618/D, *Typical Data Retention for Nonvolatile Memory.*

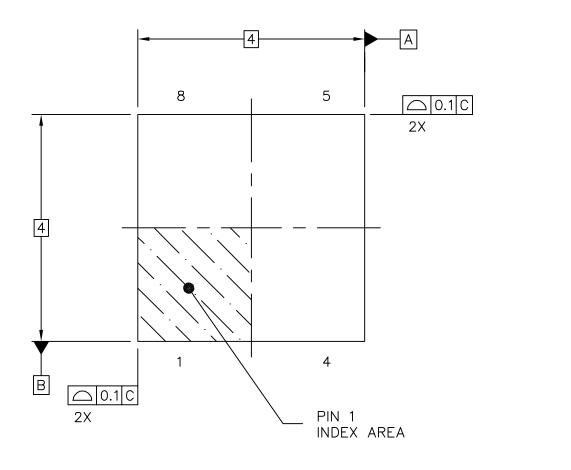

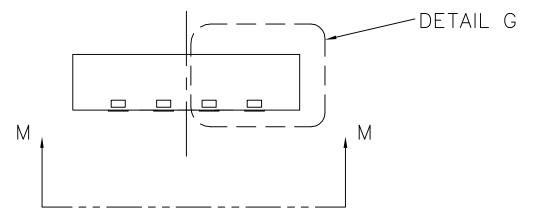

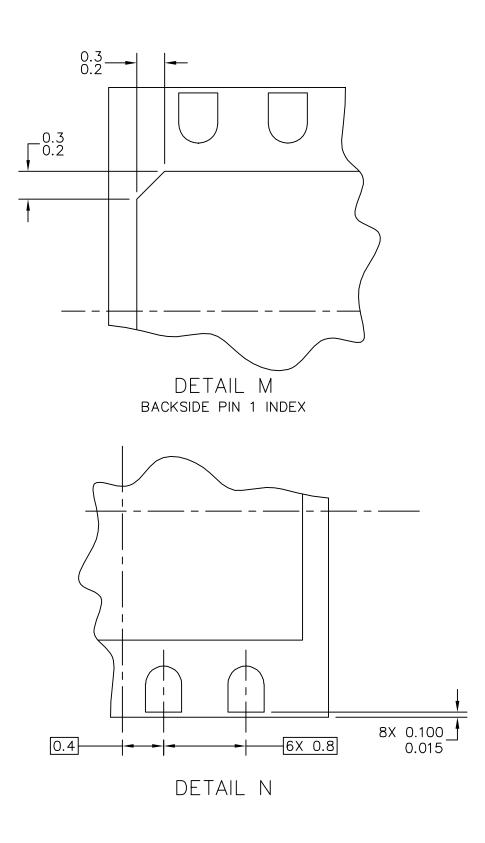

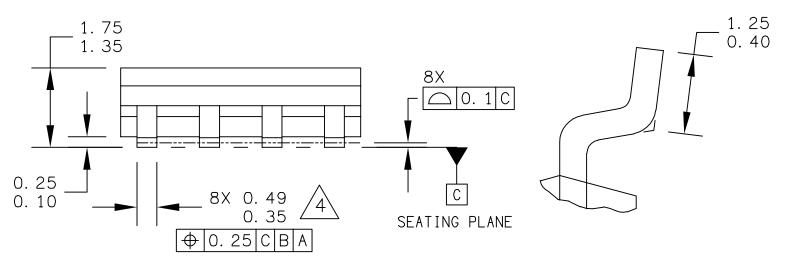

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA   | L OUTLINE    | PRINT VERSION NO | T TO SCALE |

|---------------------------------------------------------|-------------|--------------|------------------|------------|

| TITLE: THERMALLY ENHANCED                               | DUAL        | DOCUMENT NO  | ): 98ARL10557D   | REV: B     |

| FLAT NO LEAD PACKAGE                                    | CASE NUMBER | : 1452–02    | 28 DEC 2005      |            |

| 8 TERMINAL, 0.8 PITCH (4                                | X 4 X 1)    | STANDARD: NO | N-JEDEC          |            |

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED.         | MECHANICA | L OUTLINE    | PRINT VERSION NO | T TO SCALE  |

|-----------------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED                                       | DUAL      | DOCUMENT NO  | ): 98ARL10557D   | REV: B      |

| FLAT NO LEAD PACKAGE (DFN)<br>8 TERMINAL, 0.8 PITCH (4 X 4 X 1) |           | CASE NUMBER  | 8: 1452–02       | 28 DEC 2005 |

|                                                                 |           | STANDARD: NO | N-JEDEC          |             |

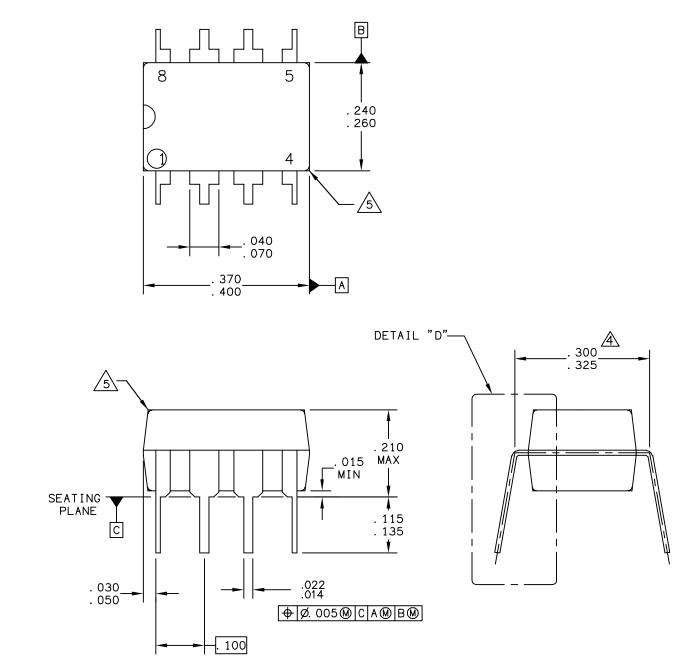

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. |  | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--|--------------|------------------|-------------|

| TITLE:                                                  |  | DOCUMENT NO  | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                               |  | CASE NUMBER  | 8: 626–06        | 19 MAY 2005 |

|                                                         |  | STANDARD: NO | N-JEDEC          |             |

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. ALL DIMENSIONS ARE IN INCHES.

- 3. 626-03 TO 626-06 OBSOLETE. NEW STANDARD 626-07.

- $\triangle$  DIMENSION TO CENTER OF LEAD WHEN FORMED PARALLEL.

- A PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CONERS). STYLE 1:

| PIN | 1. | AC | ΙN   |  |

|-----|----|----|------|--|

|     | 2. | DC | + IN |  |

|     | 3. | DC | — IN |  |

|     | 4. | AC | ΙN   |  |

- 5. GROUND

- OUTPUT

AUXILIARY

- 8. VCC

| © FREESCALE SEMICONDUCTOR, INC.<br>All Rights reserved. |  | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--|--------------|------------------|-------------|

| TITLE:                                                  |  | DOCUMENT NO  | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                               |  | CASE NUMBER  | 8: 626–06        | 19 MAY 2005 |

|                                                         |  | STANDARD: NO | N-JEDEC          |             |

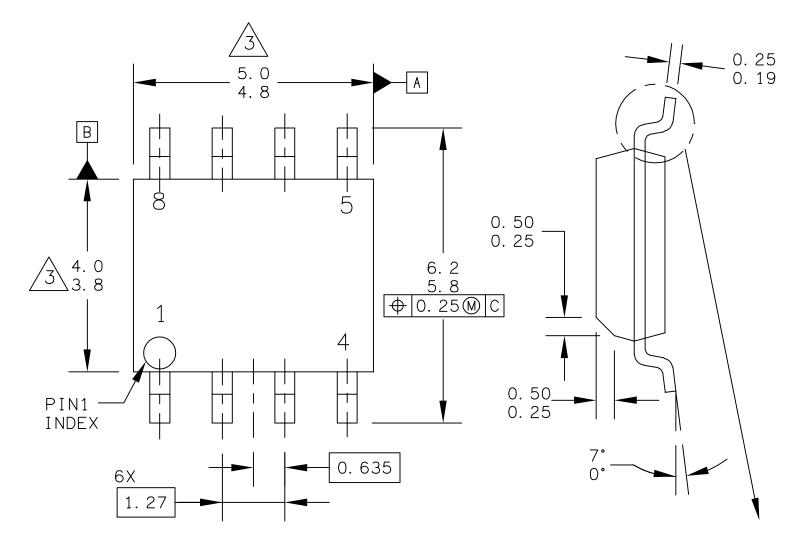

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO  | ): 98ASB42564B   | REV: U      |

| 8LD SOIC NARROW                                         | BODY      | CASE NUMBER  | 8: 751–07        | 07 APR 2005 |

|                                                         |           | STANDARD: JE | DEC MS-012AA     |             |

| STYLE 16:       |        | STYLE  | 17:   | STYLE 1 | 8:      |

|-----------------|--------|--------|-------|---------|---------|

| PIN 1. EMITTER, | DIE #1 | PIN 1. | VCC   | PIN 1.  | ANODE   |

| 2. BASE,        | DIE #1 | 2.     | V20UT | 2.      | ANODE   |

| 3. EMITTER,     | DIE #2 | 3.     | V10UT | 3.      | SOURCE  |

| 4. BASE,        | DIE #2 | 4.     | TXE   | 4.      | GATE    |

| 5. COLLECTOR,   | DIE #2 | 5.     | RXE   | 5.      | DRAIN   |

| 6. COLLECTOR,   | DIE #2 | 6.     | VEE   | 6.      | DRAIN   |

| 7. COLLECTOR,   | DIE #1 | 7.     | GND   | 7.      | CATHODE |

| 8. COLLECTOR,   | DIE #1 | 8.     | ACC   | 8.      | CATHODE |

|                 |        |        |       |         |         |

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO  | : 98ASB42564B    | REV: U      |

| 8LD SOIC NARROW                                         | BODY      | CASE NUMBER  | 2: 751–07        | 07 APR 2005 |

|                                                         |           | STANDARD: JE | DEC MS-012AA     |             |

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- A DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- A. DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE     | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO  | ): 98ASB42564B   | REV: U      |

| 8LD SOIC NARROW                                         | N BODY    | CASE NUMBER  | 8: 751–07        | 07 APR 2005 |

|                                                         |           | STANDARD: JE | DEC MS-012AA     |             |