# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | CANbus, LINbusSCI, SPI                                                 |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 48                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561ar6tae |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table of Contents —

\_\_\_\_\_

| 10 ON-CHIP PERIPHERALS                                        | 53  |

|---------------------------------------------------------------|-----|

| 10.1 WINDOW WATCHDOG (WWDG)                                   | 53  |

| 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK MCC/RTC       | 59  |

| 10.3 PWM AUTO-RELOAD TIMER (ART)                              |     |

| 10.4 16-BIT TIMER                                             | 72  |

| 10.5 8-BIT TIMER (TIM8)                                       | 91  |

| 10.6 SERIAL PERIPHERAL INTERFACE (SPI)                        | 109 |

| 10.7 LINSCI SERIAL COMMUNICATION INTERFACE (LIN MASTER/SLAVE) | 121 |

| 10.8 LINSCI SERIAL COMMUNICATION INTERFACE (LIN MASTER ONLY)  | 152 |

| 10.9 BECAN CONTROLLER (BECAN)                                 |     |

| 10.1010-BIT A/D CONVERTER (ADC)                               | 208 |

| 11 INSTRUCTION SET                                            |     |

| 11.1 CPU ADDRESSING MODES                                     | 212 |

| 11.2 INSTRUCTION GROUPS                                       | 215 |

| 12 ELECTRICAL CHARACTERISTICS                                 | 218 |

| 12.1 PARAMETER CONDITIONS                                     | 218 |

| 12.2 ABSOLUTE MAXIMUM RATINGS                                 |     |

| 12.3 OPERATING CONDITIONS                                     |     |

| 12.4 SUPPLY CURRENT CHARACTERISTICS                           |     |

| 12.5 CLOCK AND TIMING CHARACTERISTICS                         | 225 |

| 12.6 AUTO WAKEUP FROM HALT OSCILLATOR (AWU)                   |     |

| 12.7 MEMORY CHARACTERISTICS                                   | 229 |

| 12.8 EMC CHARACTERISTICS                                      | 230 |

| 12.9 I/O PORT PIN CHARACTERISTICS                             | 233 |

| 12.10CONTROL PIN CHARACTERISTICS                              | 238 |

| 12.11TIMER PERIPHERAL CHARACTERISTICS                         | 241 |

| 12.12COMMUNICATION INTERFACE CHARACTERISTICS                  | 242 |

| 12.1310-BIT ADC CHARACTERISTICS                               | 244 |

| 13 PACKAGE CHARACTERISTICS                                    | 248 |

| 13.1 PACKAGE MECHANICAL DATA                                  | 248 |

| 13.2 THERMAL CHARACTERISTICS                                  | 250 |

| 13.3 SOLDERING AND GLUEABILITY INFORMATION                    | 250 |

| 14 DEVICE CONFIGURATION AND ORDERING INFORMATION              | 251 |

| 14.1 FLASH OPTION BYTES                                       |     |

| 14.2 TRANSFER OF CUSTOMER CODE                                | 253 |

| 15 DEVELOPMENT TOOLS                                          |     |

| 16 IMPORTANT NOTES                                            |     |

| 16.1 ALL DEVICES                                              |     |

| 16.2 FLASH/FASTROM DEVICES ONLY                               |     |

| 16.3 ROM DEVICES ONLY                                         |     |

| 17 REVISION HISTORY                                           | 263 |

#### 4 FLASH PROGRAM MEMORY

#### **4.1 INTRODUCTION**

The ST7 dual voltage High Density Flash

(HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a Byte-by-Byte basis using an external V<sub>PP</sub> supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (In-Circuit Programming) or IAP (In-Application Programming).

The array matrix organisation allows each sector to be erased and reprogrammed without affecting other sectors.

#### **4.2 MAIN FEATURES**

- 3 Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (In-Circuit Programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (In-Application Programming) In this mode, all sectors except Sector 0, can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Read-out protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

#### 4.3 STRUCTURE

<u>ل ۲</u>

The Flash memory is organised in sectors and can be used for both code and data storage.

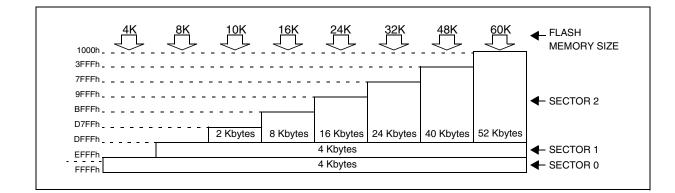

Figure 6. Memory Map and Sector Address

Depending on the overall Flash memory size in the microcontroller device, there are up to three user sectors (see Table 3). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

The first two sectors have a fixed size of 4 Kbytes (see Figure 6). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

| Table 4. Sectors available in Flash devices |

|---------------------------------------------|

|---------------------------------------------|

| Flash Size (bytes) | Available Sectors |

|--------------------|-------------------|

| 4K                 | Sector 0          |

| 8K                 | Sectors 0,1       |

| > 8K               | Sectors 0,1, 2    |

#### 4.3.1 Read-out Protection

Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

In Flash devices, this protection is removed by reprogramming the option. In this case, the entire program memory is first automatically erased and the device can be reprogrammed.

Read-out protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the Option List.

#### FLASH PROGRAM MEMORY (Cont'd)

#### 4.5 ICP (IN-CIRCUIT PROGRAMMING)

To perform ICP the microcontroller must be switched to ICC (In-Circuit Communication) mode by an external controller or programming tool.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations, or selection serial communication interface for downloading).

When using an STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user needs only to implement the ICP hardware interface on the application board (see Figure 7). For more details on the pin locations, refer to the device pinout description.

#### 4.6 IAP (IN-APPLICATION PROGRAMMING)

This mode uses a BootLoader program previously stored in Sector 0 by the user (in ICP mode or by plugging the device in a programming tool).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored, etc.). For example, it is possible to download code from the SPI, SCI or other type of serial interface and program it in the Flash. IAP mode can be used to program any of the Flash sectors except Sector 0, which is write/ erase protected to allow recovery in case errors occur during the programming operation.

<u>/</u>ک

#### **4.7 RELATED DOCUMENTATION**

For details on Flash programming and ICC protocol, refer to the *ST7 Flash Programming Reference Manual* and to the *ST7 ICC Protocol Reference Manual*.

#### **4.8 REGISTER DESCRIPTION**

#### FLASH CONTROL/STATUS REGISTER (FCSR)

Read/Write

| Reset Value: 0000 0000 (00h) |   |   |   |   |    |   |   |  |

|------------------------------|---|---|---|---|----|---|---|--|

| 7                            |   |   |   | 2 | 00 |   | 0 |  |

| 0                            | 0 | 0 | 0 | 0 | 0  | 0 | 0 |  |

This register is reserved for use by Programming Tool software. It controls the Flash programming and erasing operations.

#### Table 5. Flash Control/Status Register Address and Reset Value

| 0 | Address<br>(Hex.) | Register<br>Label   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|-------------------|---------------------|---|---|---|---|---|---|---|---|

|   | 0024h             | FCSR<br>Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### 6.3 RESET SEQUENCE MANAGER (RSM)

#### 6.3.1 Introduction

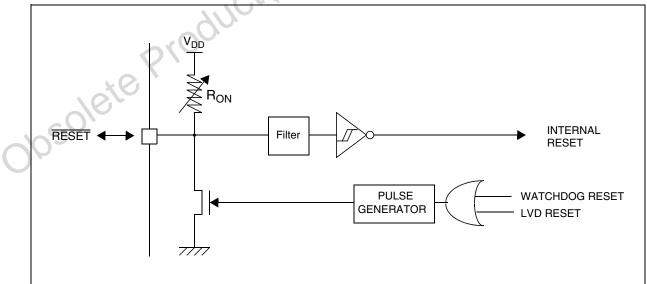

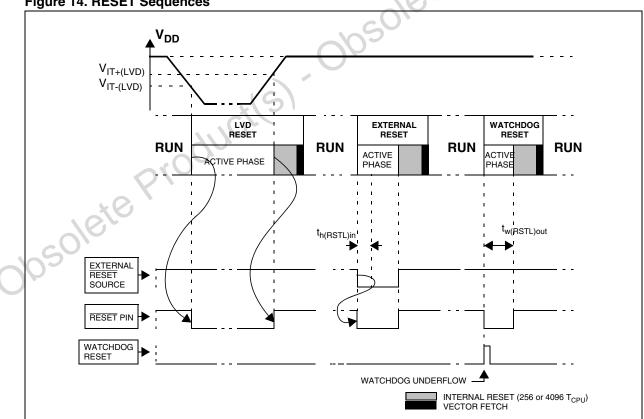

The reset sequence manager includes three RE-SET sources as shown in Figure 2:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

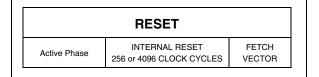

The basic RESET sequence consists of three phases as shown in Figure 1:

- Active Phase depending on the RESET source

- 256 or 4096 CPU clock cycle delay (selected by option byte)

- RESET vector fetch

<u>/</u>ک

The 256 or 4096 CPU clock cycle delay allows the oscillator to stabilize and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay should be selected by option byte to correspond to the stabilization time of the external oscillator used in the application.

The RESET vector fetch phase duration is two clock cycles.

#### Figure 12. RESET Sequence Phases

**Caution:** When the ST7 is unprogrammed or fully erased, the Flash is blank and the RESET vector is not programmed. For this reason, it is recommended to keep the RESET pin in low state until programming mode is entered, in order to avoid unwanted behavior.

#### 6.3.2 Asynchronous External RESET pin

The  $\overline{\text{RESET}}$  pin is both an input and an open-drain output with integrated  $R_{ON}$  weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See Electrical Characteristic section for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 3). This detection is asynchronous and therefore the MCU can enter reset state even in HALT mode.

#### **RESET SEQUENCE MANAGER** (Cont'd)

The **RESET** pin is an asynchronous signal which plays a major role in EMS performance. In a noisy environment, it is recommended to follow the guidelines mentioned in the electrical characteristics section.

#### 6.3.3 External Power-On RESET

If the LVD is disabled by option byte, to start up the microcontroller correctly, the user must ensure by means of an external reset circuit that the reset signal is held low until  $\ensuremath{\mathsf{V}_{\text{DD}}}$  is over the minimum level specified for the selected f<sub>OSC</sub> frequency.

A proper reset signal for a slow rising V<sub>DD</sub> supply can generally be provided by an external RC network connected to the RESET pin.

#### 6.3.4 Internal Low Voltage Detector (LVD) RESET

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

- Power-On RESET

- Voltage Drop RESET

The device  $\overline{\text{RESET}}$  pin acts as an output that is pulled low when  $V_{DD} < V_{IT+}$  (rising edge) or  $V_{DD} < V_{IT-}$  (falling edge) as shown in Figure 3.

The LVD filters spikes on  $V_{DD}$  larger than  $t_{q(VDD)}$  to avoid parasitic resets.

#### 6.3.5 Internal Watchdog RESET

The RESET sequence generated by a internal Watchdog counter overflow is shown in Figure 3.

Starting from the Watchdog counter underflow, the device RESET pin acts as an output that is pulled low during at least tw(RSTL)out.

**67/**

#### Figure 14. RESET Sequences

#### PWM AUTO-RELOAD TIMER (Cont'd)

57

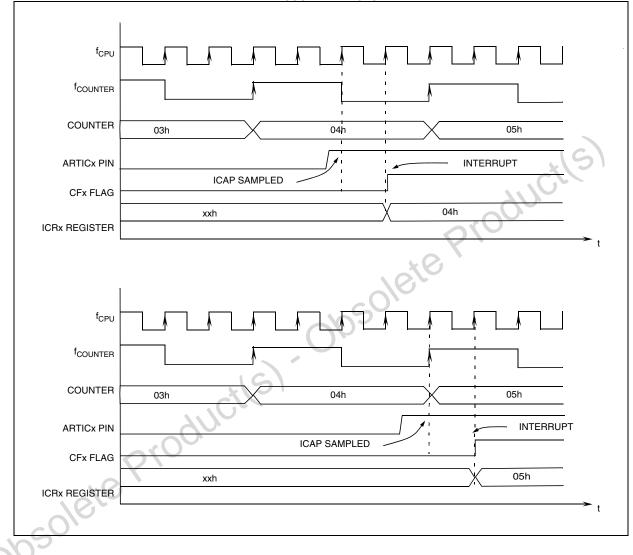

### Figure 46. input Capture Timing Diagram, $f_{COUNTER} = f_{CPU} / 4$

67/265

#### **External Interrupt Capability**

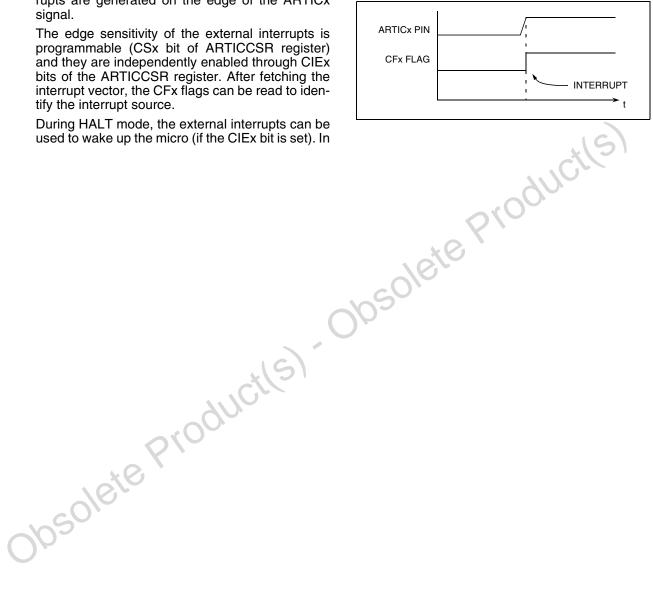

This mode allows the Input capture capabilities to be used as external interrupt sources. The interrupts are generated on the edge of the ARTICx signal.

The edge sensitivity of the external interrupts is programmable (CSx bit of ARTICCSR register) and they are independently enabled through CIEx bits of the ARTICCSR register. After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

this case, the interrupt synchronization is done directly on the ARTICx pin edge (Figure 47).

#### Figure 47. ART External Interrupt in Halt Mode

#### **ON-CHIP PERIPHERALS** (Cont'd)

#### **10.3.3 Register Description**

#### CONTROL / STATUS REGISTER (ARTCSR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |     |     |     |     |      |     | 0   |  |

|------|-----|-----|-----|-----|------|-----|-----|--|

| EXCL | CC2 | CC1 | CC0 | TCE | FCRL | OIE | OVF |  |

#### Bit 7 = **EXCL** External Clock

This bit is set and cleared by software. It selects the input clock for the 7-bit prescaler.

0: CPU clock. 1: External clock.

Bit 6:4 = **CC[2:0]** Counter Clock Control These bits are set and cleared by software. They determine the prescaler division ratio from  $f_{INPUT}$ .

| <b>f</b> COUNTER         | With f <sub>INPUT</sub> =8 MHz | CC2 | CC1 | CC0 |

|--------------------------|--------------------------------|-----|-----|-----|

| f <sub>INPUT</sub>       | 8 MHz                          | 0   | 0   | 0   |

| f <sub>INPUT</sub> / 2   | 4 MHz                          | 0   | 0   | 1   |

| f <sub>INPUT</sub> / 4   | 2 MHz                          | 0   | 1   | 0   |

| f <sub>INPUT</sub> / 8   | 1 MHz                          | 0   | 1   | 1   |

| f <sub>INPUT</sub> / 16  | 500 kHz                        | 1   | 0   | 0   |

| f <sub>INPUT</sub> / 32  | 250 kHz                        | 1   | 0   | 1   |

| f <sub>INPUT</sub> / 64  | 125 kHz                        | 1   | 1   | 0   |

| f <sub>INPUT</sub> / 128 | 62.5 kHz                       | 1   | 1   | 1   |

#### Bit 3 = **TCE** *Timer Counter Enable*

This bit is set and cleared by software. It puts the timer in the lowest power consumption mode. 0: Counter stopped (prescaler and counter frozen).

1: Counter running.

#### Bit 2 = **FCRL** Force Counter Re-Load

This bit is write-only and any attempt to read it will yield a logical zero. When set, it causes the contents of ARTARR register to be loaded into the counter, and the content of the prescaler register to be cleared in order to initialize the timer before starting to count.

#### Bit 1 = **OIE** Overflow Interrupt Enable

This bit is set and cleared by software. It allows to enable/disable the interrupt which is generated when the OVF bit is set.

0: Overflow Interrupt disable.

1: Overflow Interrupt enable.

#### Bit 0 = **OVF** Overflow Flag

This bit is set by hardware and cleared by software reading the ARTCSR register. It indicates the transition of the counter from FFh to the ARTARR value.

#### 0: New transition not yet reached 1: Transition reached

### COUNTER ACCESS REGISTER (ARTCAR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CA7 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 |

Bit 7:0 = CA[7:0] Counter Access Data

These bits can be set and cleared either by hardware or by software. The ARTCAR register is used to read or write the auto-reload counter "on the fly" (while it is counting).

### AUTO-RELOAD REGISTER (ARTARR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| AR7 | AR6 | AR5 | AR4 | AR3 | AR2 | AR1 | AR0 |

#### Bit 7:0 = AR[7:0] Counter Auto-Reload Data

These bits are set and cleared by software. They are used to hold the auto-reload value which is automatically loaded in the counter when an overflow occurs. At the same time, the PWM output levels are changed according to the corresponding OPx bit in the PWMCR register.

This register has two PWM management functions:

- Adjusting the PWM frequency

- Setting the PWM duty cycle resolution

#### PWM Frequency vs Resolution:

| ARTARR     | Resolution | f <sub>PWM</sub> |           |  |

|------------|------------|------------------|-----------|--|

| value      | Resolution | Min              | Max       |  |

| 0          | 8-bit      | ~0.244 kHz       | 31.25 kHz |  |

| [ 0127 ]   | > 7-bit    | ~0.244 kHz       | 62.5 kHz  |  |

| [ 128191 ] | > 6-bit    | ~0.488 kHz       | 125 kHz   |  |

| [ 192223 ] | > 5-bit    | ~0.977 kHz       | 250 kHz   |  |

| [ 224239 ] | > 4-bit    | ~1.953 kHz       | 500 kHz   |  |

#### 16-BIT TIMER (Cont'd)

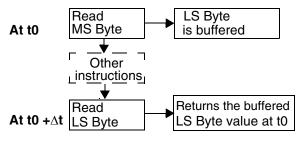

**16-bit read sequence:** (from either the Counter Register or the Alternate Counter Register).

Beginning of the sequence

Sequence completed

The user must read the MS Byte first, then the LS Byte value is buffered automatically.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MS Byte several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LS Byte of the count value at the time of the read.

Whatever the timer mode used (input capture, output compare, One Pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true.

1. Reading the SR register while the TOF bit is set. 2. An access (read or write) to the CLR register.

**Notes:** The TOF bit is not cleared by accesses to ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by WAIT mode.

In HALT mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a Reset).

#### 10.4.3.2 External Clock

The external clock (where available) is selected if CC0 = 1 and CC1 = 1 in the CR2 register.

The status of the EXEDG bit in the CR2 register determines the type of level transition on the external clock pin EXTCLK that will trigger the free running counter.

The counter is synchronized with the falling edge of the internal CPU clock.

A minimum of four falling edges of the CPU clock must occur between two consecutive active edges of the external clock; thus the external clock frequency must be less than a quarter of the CPU clock frequency.

<u>///</u>

#### 16-BIT TIMER (Cont'd)

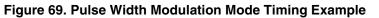

#### 10.4.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are two output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC*i*E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

#### Procedure:

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OC*i*R register and CR register:

OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \text{ OC} i R = \frac{\Delta t * f_{CPU}}{\text{PRESC}}$$

Where:

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 17 Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC}_{i} = \Delta t \star f_{EXT}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OCiLR register (enables the output compare function and clears the OCF*i* bit).

<u>(۲</u>/

#### 8-BIT TIMER (Cont'd)

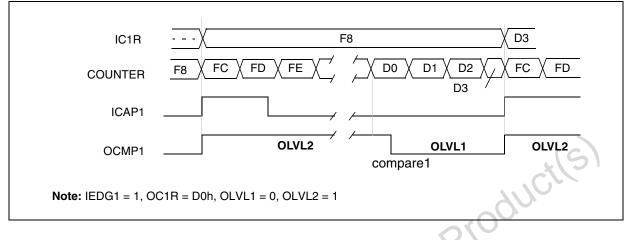

#### Figure 68. One Pulse Mode Timing Example

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.3.1 Functional Description

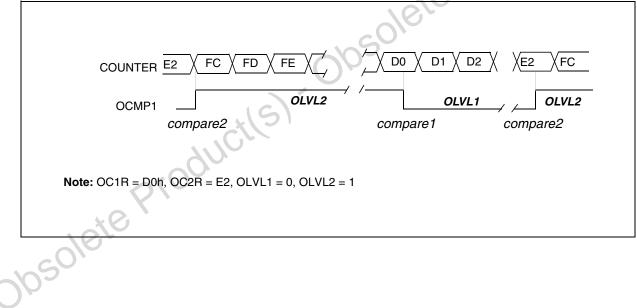

A basic example of interconnections between a single master and a single slave is illustrated in Figure 71.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 74 on page 114) but master and slave must be programmed with the same timing mode.

#### Figure 71. Single Master/ Single Slave Application

#### SERIAL PERIPHERAL INTERFACE (Cont'd)

#### Table 22. SPI Register Map and Reset Values

|   | Address<br>(Hex.) | Register<br>Label                    | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|---|-------------------|--------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| ľ | 21                | SPIDR<br>Reset Value                 | MSB<br>x  | x         | x         | x         | x         | x         | x         | LSB<br>x  |

|   | 22                | SPICR<br>Reset Value                 | SPIE<br>0 | SPE<br>0  | SPR2<br>0 | MSTR<br>0 | CPOL<br>x | CPHA<br>x | SPR1<br>x | SPR0<br>x |

| ľ | 23                | SPICSR<br>Reset Value                | SPIF<br>0 | WCOL<br>0 | OVR<br>0  | MODF<br>0 | 0         | SOD<br>0  | SSM<br>0  | SSI<br>O  |

| 0 | 05016             | Reset Value<br>SPICSR<br>Reset Value | odu       | cils      |           | 050       | ete       | Prof      | JUCE      |           |

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd) 10.7.6 Low Power Modes 10.7.7 Interrupts

| Mode | Description                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SCI.<br>SCI interrupts cause the device to exit from<br>Wait mode.                                 |

| HALT | SCI registers are frozen.<br>In Halt mode, the SCI stops transmitting/re-<br>ceiving until Halt mode is exited. |

| Interrupt Event                              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| Transmit Data Register<br>Empty              | TDRE          | TIE                      |                      |                      |

| Transmission Com-<br>plete                   | тс            | TCIE                     |                      |                      |

| Received Data Ready to be Read               | RDRF          | RIE                      | Yes                  | No                   |

| Overrun Error or LIN<br>Synch Error Detected | OR/<br>LHE    |                          | 19                   | $\mathbf{h}$         |

| Idle Line Detected                           | IDLE          | ILIE                     | 11                   |                      |

| Parity Error                                 | PE            | PIE                      |                      |                      |

| LIN Header Detection                         | LHDF          | LHIE                     |                      |                      |

The SCI interrupt events are connected to the same interrupt vector (see Interrupts chapter).

These events generate an interrupt if the corre-sponding Enable Control Bit is set and the inter-rupt mask in the CC register is reset (RIM instrucobsolete Product(s) - 0 tion).

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

#### **CONTROL REGISTER 2 (SCICR2)**

Read/Write Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |                   | 0                 |

|-----|------|-----|------|----|----|-------------------|-------------------|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU <sup>1)</sup> | SBK <sup>1)</sup> |

<sup>1)</sup>This bit has a different function in LIN mode, please refer to the LIN mode register description.

Bit 7 = **TIE** *Transmitter interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: In SCI interrupt is generated whenever TDRE = 1 in the SCISR register

Bit 6 = **TCIE** *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC = 1 in the SCISR register

Bit 5 = **RIE** *Receiver interrupt enable*

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR = 1 or RDRF = 1 in the SCISR register

Bit 4 = ILIE Idle line interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE = 1 in the SCISR register.

Bit 3 = **TE** Transmitter enable

This bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

#### Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

#### Bit 2 = **RE** *Receiver enable*

This bit enables the receiver. It is set and cleared by software.

0: Receiver is disabled in the SCISR register

1: Receiver is enabled and begins searching for a start bit

#### Bit 1 = RWU Receiver wake-up

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in active mode

- 1: Receiver in mute mode

#### Notes:

- Before selecting Mute mode (by setting the RWU bit) the SCI must first receive a data byte, otherwise it cannot function in Mute mode with wakeup by Idle line detection.

- In Address Mark Detection Wake-Up configuration (WAKE bit = 1) the RWU bit cannot be modified by software while the RDRF bit is set.

#### Bit 0 = SBK Send break

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter will send a BREAK word at the end of the current word.

#### **DATA REGISTER (SCIDR)**

Read/Write

7

Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

|-----|-----|-----|-----|-----|-----|-----|-----|

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 1).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 1).

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

SCICR2 register is set, the LHDM bit selects the Wake-Up method (replacing the WAKE bit). 0: LIN Synch Break Detection Method 1: LIN Identifier Field Detection Method

Bit 2 = LHIE LIN Header Interrupt Enable

This bit is set and cleared by software. It is only usable in LIN Slave mode.

0: LIN Header Interrupt is inhibited.

1: An SCI interrupt is generated whenever LHDF = 1.

Bit 1 = LHDF LIN Header Detection Flag

This bit is set by hardware when a LIN Header is detected and cleared by a software sequence (an access to the SCISR register followed by a read of the SCICR3 register). It is only usable in LIN Slave mode.

0: No LIN Header detected.

1: LIN Header detected.

**Notes:** The header detection method depends on the LHDM bit:

- If LHDM = 0, a header is detected as a LIN Synch Break.

- If LHDM = 1, a header is detected as a LIN Identifier, meaning that a LIN Synch Break Field + a LIN Synch Field + a LIN Identifier Field have been consecutively received.

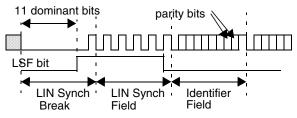

#### Bit 0 = LSF LIN Synch Field State

This bit indicates that the LIN Synch Field is being analyzed. It is only used in LIN Slave mode. In Auto Synchronization Mode (LASE bit = 1), when the SCI is in the LIN Synch Field State it waits or counts the falling edges on the RDI line.

It is set by hardware as soon as a LIN Synch Break is detected and cleared by hardware when the LIN Synch Field analysis is finished (see Figure 11). This bit can also be cleared by software to exit LIN Synch State and return to idle mode.

0: The current character is not the LIN Synch Field

1: LIN Synch Field State (LIN Synch Field undergoing analysis)

#### LIN DIVIDER REGISTERS

LDIV is coded using the two registers LPR and LP-FR. In LIN Slave mode, the LPR register is accessible at the address of the SCIBRR register and the LPFR register is accessible at the address of the SCIETPR register.

#### LIN PRESCALER REGISTER (LPR) Read/Write

Reset Value: 0000 0000 (00h)

| 70   | 0.   |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| LPR7 | LPR6 | LPR5 | LPR4 | LPR3 | LPR2 | LPR1 | LPR0 |

#### LPR[7:0] LIN Prescaler (mantissa of LDIV)

These 8 bits define the value of the mantissa of the LIN Divider (LDIV):

| LPR[7:0] | Rounded Mantissa (LDIV) |

|----------|-------------------------|

| 00h      | SCI clock disabled      |

| 01h      | 1                       |

|          |                         |

| FEh      | 254                     |

| FFh      | 255                     |

**Caution:** LPR and LPFR registers have different meanings when reading or writing to them. Consequently bit manipulation instructions (BRES or BSET) should never be used to modify the LPR[7:0] bits, or the LPFR[3:0] bits.

#### beCAN CONTROLLER (Cont'd)

#### 10.9.3 Operating Modes

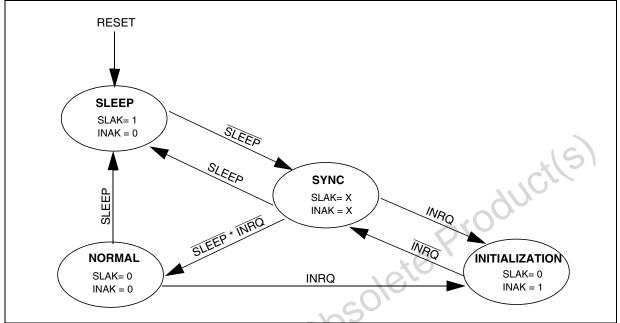

The beCAN has three main operating modes: Initialization, Normal and Sleep. After a hardware reset, beCAN is in Sleep mode to reduce power consumption. The software requests beCAN to enter Initialization or Sleep mode by setting the INRQ or SLEEP bits in the CMCR register. Once the mode has been entered, beCAN confirms it by setting the INAK or SLAK bits in the CMSR register. When neither INAK nor SLAK are set, beCAN is in Normal mode. Before entering Normal mode beCAN always has to **synchronize** on the CAN bus. To synchronize, beCAN waits until the CAN bus is idle, this means 11 consecutive recessive bits have been monitored on CANRX.

#### 10.9.3.1 Initialization Mode

The software initialization can be done while the hardware is in Initialization mode. To enter this mode the software sets the INRQ bit in the CMCR register and waits until the hardware has confirmed the request by setting the INAK bit in the CMSR register.

To leave Initialization mode, the software clears the INQR bit. beCAN has left Initialization mode once the INAK bit has been cleared by hardware.

While in Initialization mode, all message transfers to and from the CAN bus are stopped and the status of the CAN bus output CANTX is recessive (high).

Entering Initialization Mode does not change any of the configuration registers.

To initialize the CAN Controller, software has to set up the Bit Timing registers and the filter banks. If a filter bank is not used, it is recommended to leave it non active (leave the corresponding FACT bit cleared).

#### 10.9.3.2 Normal Mode

Once the initialization has been done, the software must request the hardware to enter Normal mode, to synchronize on the CAN bus and start reception and transmission. Entering Normal mode is done by clearing the INRQ bit in the CMCR register and waiting until the hardware has confirmed the request by clearing the INAK bit in the CMSR register. Afterwards, the beCAN synchronizes with the data transfer on the CAN bus by waiting for the occurrence of a sequence of 11 consecutive recessive bits (= Bus Idle) before it can take part in bus activities and start message transfer.

The initialization of the filter values is independent from Initialization mode but must be done while the filter bank is not active (corresponding FACTx bit cleared). The filter bank scale and mode configuration must be configured in initialization mode.

#### beCAN CONTROLLER (Cont'd) Filter Bank Scale and Mode Configuration

The filter banks are configured by means of the corresponding CFCRx register. To configure a filter bank this must be deactivated by clearing the FACT bit in the CFCR register. The filter scale is configured by means of the FSC[1:0] bits in the corresponding CFCR register, refer to Figure 9. Filter Bank Scale Configuration - Register Organisation. The **identifier list** or **identifier mask** mode for the corresponding Mask/Identifier registers is configured by means of the FMCLx and FMCHx bits in the CFMR register. The FMCLx bit defines the mode for the two least significant bytes, and the FMCHx bit the mode for the two most significant bytes of filter bank x. **Examples**:

- If filter bank 1 is configured as two 16-bit filters, then the FMCL1 bit defines the mode of the CF1R2 and CF1R3 registers and the FMCH1 bit defines the mode of the CF1R6 and CF1R7 registers.

- If filter bank 2 is configured as four 8-bit filters, then the FMCL2 bit defines the mode of the CF2R1 and CF2R3 registers and the FMCH2 bit defines the mode of the CF2R5 and CF2R7 registers.

**Note**: In 32-bit configuration, the FMCLx and FM-CHx bits must have the same value to ensure that the four Mask/Identifier registers are in the same mode.

To filter a group of identifiers, configure the Mask/ Identifier registers in mask mode.

To select single identifiers, configure the Mask/ Identifier registers in identifier list mode.

Filters not used by the application should be left deactivated.

#### Filter Match Index

Once a message has been received in the FIFO it is available to the application. Typically application

data are copied into RAM locations. To copy the data to the right location the application has to identify the data by means of the identifier. To avoid this and to ease the access to the RAM locations, the CAN controller provides a Filter Match Index.

This index is stored in the mailbox together with the message according to the filter priority rules. Thus each received message has its associated Filter Match Index.

The Filter Match Index can be used in two ways:

- Compare the Filter Match Index with a list of expected values.

- Use the Filter Match Index as an index on an array to access the data destination location.

For non-masked filters, the software no longer has to compare the identifier.

If the filter is masked the software reduces the comparison to the masked bits only.

#### **Filter Priority Rules**

Depending on the filter combination it may occur that an identifier passes successfully through several filters. In this case the filter match value stored in the receive mailbox is chosen according to the following rules:

- A filter in identifier list mode prevails on an filter in mask mode.

- A filter with full identifier coverage prevails over filters covering part of the identifier, e.g. 16-bit filters prevail over 8-bit filters.

- Filters configured in the same mode and with identical coverage are prioritized by filter number and register number. The lower the number the higher the priority.

| Address<br>(Hex.) | Register<br>Name | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|-------------------|------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| 7Eh               | MTSLR            | TIME7  | TIME6  | TIME5  | TIME4  | TIME3  | TIME2  | TIME1 | TIME0 |

|                   | Reset Value      | x      | x      | x      | x      | x      | x      | x     | x     |

| 7Fh               | MTSHR            | TIME15 | TIME14 | TIME13 | TIME12 | TIME11 | TIME10 | TIME9 | TIME8 |

|                   | Reset Value      | x      | x      | x      | x      | x      | x      | x     | x     |

Table 34. beCAN Filter Configuration Page - Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Name     | 7     | 6     | 5     | 4     | 3         | 2         | 1         | 50        |

|-------------------|----------------------|-------|-------|-------|-------|-----------|-----------|-----------|-----------|

| 701               | CESR                 |       | LEC2  | LEC1  | LEC0  |           | BOFF      | EPVF      | EWGF      |

| 70h               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

| 741               | CEIER                | ERRIE |       |       | LECIE |           | BOFIE     | EPVIE     | EWGIE     |

| 71h               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

| 70h               | TECR                 | TEC7  | TEC6  | TEC5  | TEC4  | TEC3      | TEC2      | TEC1      | TEC0      |

| 72h               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

| 73h               | RECR                 | REC7  | REC6  | REC5  | REC4  | REC3      | REC2      | REC1      | REC0      |

| 730               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

| 746               | CBTR0                | SJW1  | SJW0  | BRP5  | BRP4  | BRP3      | BRP2      | BRP1      | BRP0      |

| 74h               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

| 754               | CBTR1                |       | BS22  | BS21  | BS20  | BS13      | BS12      | BS11      | BS10      |

| 75h               | Reset Value          | 0     | 0     | 1     | 0     | 0         | 0         | 1         | 1         |

| 76h               | Reserved             | x CX  | ×     | x     | x     | x         | x         | x         | x         |

| 77h               | Reserved             | x     | x     | x     | x     | x         | x         | x         | x         |

|                   | CFMR0                | FMH3  | FML3  | FMH2  | FML2  | FMH1      | FML1      | FMH0      | FML0      |

| 78h               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

| 79h               | CFMR1<br>Reset Value | 0     | 0     | 0     | 0     | FMH5<br>0 | FML5<br>0 | FMH4<br>0 | FML4<br>0 |

| 746               | CFCR0                | FFA1  | FSC11 | FSC10 | FACT1 | FFA0      | FSC01     | FSC00     | FACT0     |

| 7Ah               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

| ZDh               | CFCR1                | FFA3  | FSC31 | FSC30 | FACT3 | FFA2      | FSC21     | FSC20     | FACT2     |

| 7Bh               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

| 7Ch               | CFCR2                | FFA5  | FSC51 | FSC50 | FACT5 | FFA4      | FSC41     | FSC40     | FACT4     |

| 701               | Reset Value          | 0     | 0     | 0     | 0     | 0         | 0         | 0         | 0         |

#### CLOCK CHARACTERISTICS (Cont'd)

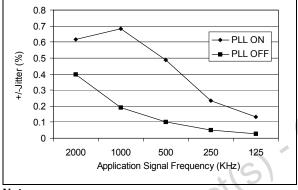

#### 12.5.4 PLL Characteristics

Operating conditions: V\_{DD} 3.8 to 5.5V @ T\_A 0 to 70°C<sup>1)</sup> or V\_{DD} 4.5 to 5.5V @ T\_A -40 to 125°C

| Symbol                   | Parameter                 | Conditions                                                       | Min | Тур    | Max | Unit |

|--------------------------|---------------------------|------------------------------------------------------------------|-----|--------|-----|------|

| V <sub>DD(PLL)</sub>     | PLL Voltage Range         | $T_A = 0$ to $+70^{\circ}C$                                      | 3.8 |        | 5.5 |      |

|                          |                           | $T_{A} = -40 \text{ to } +125^{\circ}\text{C}$                   | 4.5 | 5.5    |     |      |

| f <sub>OSC</sub>         | PLL input frequency range |                                                                  | 2   |        | 4   | MHz  |

| $\Delta f_{CPU}/f_{CPU}$ | PLL jitter <sup>1)</sup>  | $f_{OSC} = 4 \text{ MHz}, V_{DD} = 4.5 \text{ to } 5.5 \text{V}$ |     | Note 2 |     | %    |

|                          |                           | $f_{OSC}$ = 2 MHz, $V_{DD}$ = 4.5 to 5.5V                        |     |        |     | 70   |

Notes:

- 1. Data characterized but not tested.

- 2. Under characterization

The user must take the PLL jitter into account in the application (for example in serial communication or sampling of high frequency signals). The PLL jitter is a periodic effect, which is integrated over several CPU cycles. Therefore, the longer the period of the application signal, the less it is impacted by the PLL jitter.

Figure 123 shows the PLL jitter integrated on application signals in the range 125 kHz to 2 MHz. At frequencies of less than 125 kHz, the jitter is negligible.

#### Notes:

1. Measurement conditions:  $f_{CPU} = 4$  MHz,  $T_A = 25^{\circ}C$