Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | CANbus, LINbusSCI, SPI                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 11x10b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561j4tae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## INTERRUPTS (Cont'd)

| Instruction | New Description                 | Function/Example      | 11 | Н | 10 | Ν | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|---|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |   |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | 11 | Н | 10 | Ν | Z | С |

| JRM         | Jump if I1:0 = 11 (level 3)     | 11:0 = 11 ?           |    |   |    |   |   |   |

| JRNM        | Jump if I1:0 <> 11              | 1:0 <> 11 ?           |    |   |    |   |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | 11 | Н | 10 | Ν | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |   | 9 |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  | X |   | 1 |

| TRAP        | Software trap                   | Software NMI          | 1  |   | 1  | Ś | / |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  | 5 |   |   |

## **Table 8. Dedicated Interrupt Instruction Set**

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

57

## POWER SAVING MODES (Cont'd)

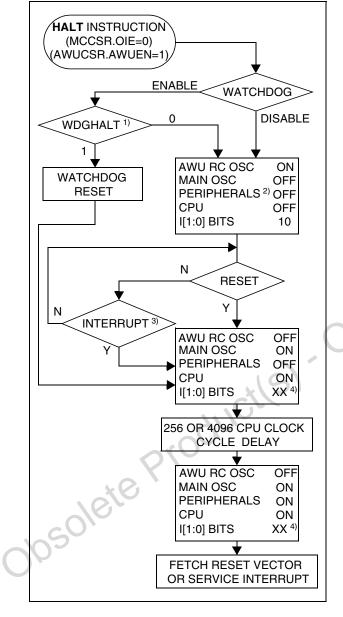

## Figure 31. AWUFH Mode Flow-chart

#### Notes:

**1.** WDGHALT is an option bit. See option byte section for more details.

**2.** Peripheral clocked with an external clock source can still be active.

**3.** Only an AWUFH interrupt and some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 34 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

#### I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

## 9.3 I/O PORT IMPLEMENTATION

<u>لرک</u>

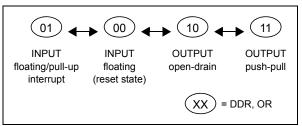

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 33 on page 49. Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

## Figure 33. Interrupt I/O Port State Transitions

## 9.4 LOW POWER MODES

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

## 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit |     | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|-----|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes |                      |

## PWM AUTO-RELOAD TIMER (Cont'd)

57

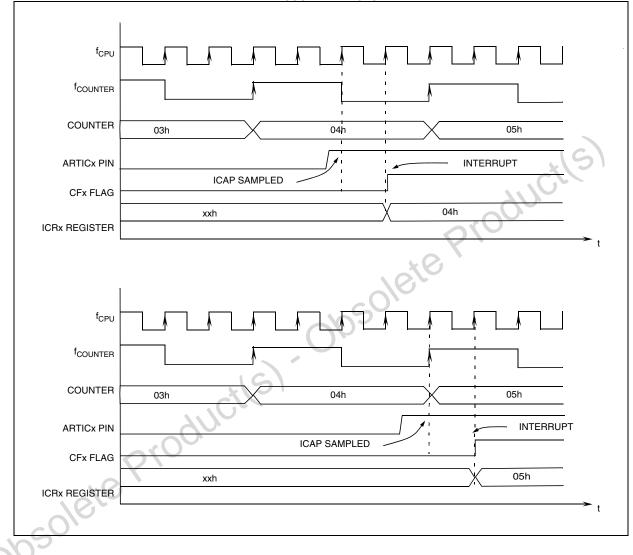

# Figure 46. input Capture Timing Diagram, $f_{COUNTER} = f_{CPU} / 4$

67/265

## 16-BIT TIMER (Cont'd)

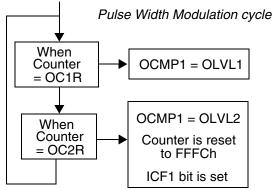

#### 10.4.3.6 Pulse Width Modulation Mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality can not be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

## Procedure

To use Pulse Width Modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula in the opposite column.

- 2. Load the OC1R register with the value corresponding to the period of the pulse if (OLVL1 = 0 and OLVL2 = 1) using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

If OLVL1 = 1 and OLVL2 = 0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$OC_{i}R Value = \frac{t \cdot t_{CPU}}{PRESC} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 17 Clock Control Bits)

If the timer clock is an external clock the formula is:

Where:

= Signal or pulse period (in seconds)

$f_{EXT}$  = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (See Figure 58)

## Notes:

- 1. After a write instruction to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- 3. The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4. In PWM mode the ICAP1 pin can not be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and ICF1 can also generates interrupt if ICIE is set.

- 5. When the Pulse Width Modulation (PWM) and One Pulse mode (OPM) bits are both set, the PWM mode is the only active one.

## 16-BIT TIMER (Cont'd) 10.4.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 16-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                      |

|      | 16-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                           |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                             |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequently, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

## 10.4.5 Interrupts

| Interrupt Event                                    | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |    |

|----------------------------------------------------|---------------|--------------------------|----------------------|----------------------|----|

| Input Capture 1 event/Counter reset in PWM mode    |               | ICF1                     | ICIE                 |                      |    |

| Input Capture 2 event                              |               | ICF2                     | ICIE                 |                      |    |

| Output Compare 1 event (not available in PWM mode) |               | OCF1                     | OCIE                 | Yes                  | No |

| Output Compare 2 event (not available in PWM mode) |               | OCF2                     | OULE                 |                      |    |

| Timer Overflow event                               | S             | TOF                      | TOIE                 |                      |    |

**Note:** The 16-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

## 10.4.6 Summary of Timer Modes

| MODES                       | TIMER RESOURCES |                               |                  |                         |  |  |  |  |

|-----------------------------|-----------------|-------------------------------|------------------|-------------------------|--|--|--|--|

| MODES                       | Input Capture 1 | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |  |  |  |

| Input Capture (1 and/or 2)  | Yes             | Yes                           | Yes              | Yes                     |  |  |  |  |

| Output Compare (1 and/or 2) | 165             | 165                           | 165              | 165                     |  |  |  |  |

| One Pulse Mode              | No              | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |  |  |  |

| PWM Mode                    | NO              | Not Recommended <sup>3)</sup> | NO               | No                      |  |  |  |  |

1) See note 4 in Section 10.4.3.5 "One Pulse Mode"

2) See note 5 in Section 10.4.3.5 "One Pulse Mode"

3) See note 4 in Section 10.4.3.6 "Pulse Width Modulation Mode"

<u>ل</u>رک

## 8-BIT TIMER (Cont'd)

57

## 8-BIT TIMER (Cont'd) CONTROL/STATUS REGISTER (CSR)

Read Only (except bit 2 R/W)

Reset Value: 0000 0000 (00h)

| 1    |      |     |      |      |      |   |   |  |  |

|------|------|-----|------|------|------|---|---|--|--|

| ICF1 | OCF1 | TOF | ICF2 | OCF2 | TIMD | 0 | 0 |  |  |

#### Bit 7 = **ICF1** Input Capture Flag 1.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP1 pin or the counter has reached the OC2R value in PWM mode. To clear this bit, first read the SR register, then read or write the the IC1R register.

## Bit 6 = **OCF1** *Output Compare Flag 1.*

0: No match (reset value).

1: The content of the free running counter has matched the content of the OC1R register. To clear this bit, first read the SR register, then read or write the OC1R register.

Bit 5 = **TOF** *Timer Overflow Flag.*

0: No timer overflow (reset value).

1: The free running counter rolled over from FFh to 00h. To clear this bit, first read the SR register, then read or write the CTR register. **Note:** Reading or writing the ACTR register does not clear TOF.

#### Bit 4 = ICF2 Input Capture Flag 2.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP2 pin. To clear this bit, first read the SR register, then read or write the IC2R register.

Bit 3 = OCF2 Output Compare Flag 2.

- 0: No match (reset value).

- 1: The content of the free running counter has matched the content of the OC2R register. To clear this bit, first read the SR register, then read or write the OC2R register.

#### Bit 2 = TIMD Timer disable.

This bit is set and cleared by software. When set, it freezes the timer prescaler and counter and disabled the output functions (OCMP1 and OCMP2 pins) to reduce power consumption. Access to the timer registers is still available, allowing the timer configuration to be changed, or the counter reset, while it is disabled.

0: Timer enabled

1: Timer prescaler, counter and outputs disabled

Bits 1:0 = Reserved, must be kept cleared.

## SERIAL PERIPHERAL INTERFACE (cont'd)

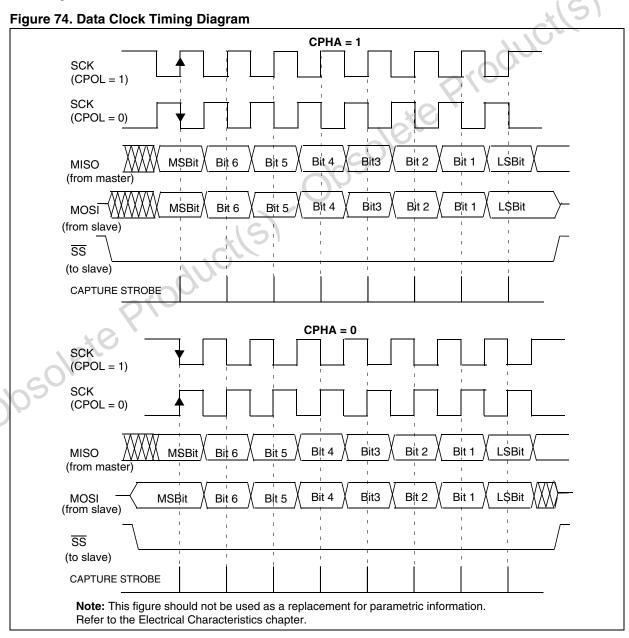

#### 10.6.4 Clock Phase and Clock Polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (See Figure 74).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge.

Figure 74 shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin and the MOSI pin are directly connected between the master and the slave device.

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

## **/**

## SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.5 Error Flags

## 10.6.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device's SS pin is pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the  $\overline{SS}$  pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

In a slave device, the MODF bit can not be set, but in a multimaster configuration the device can be in slave mode with the MODF bit set.

The MODF bit indicates that there might have been a multimaster conflict and allows software to handle this using an interrupt routine and either perform a reset or return to an application default state.

## 10.6.5.2 Overrun Condition (OVR)

An overrun condition occurs when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

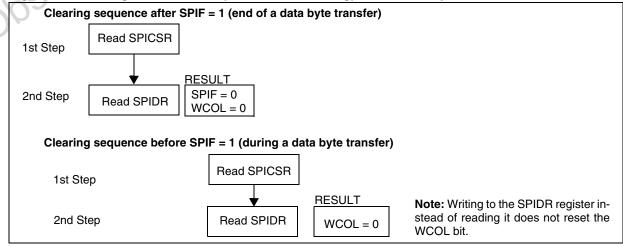

## 10.6.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 10.6.3.2 "Slave Select Management".

**Note:** A "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the CPU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

Clearing the WCOL bit is done through a software sequence (see Figure 75).

#### Figure 75. Clearing the WCOL Bit (Write Collision Flag) Software Sequence

#### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Mode)

#### 10.7.9 LIN Mode - Functional Description.

The block diagram of the Serial Control Interface, in LIN slave mode is shown in Figure 5.

It uses six registers:

- 3 control registers: SCICR1, SCICR2 and SCICR3

- 2 status registers: the SCISR register and the LHLR register mapped at the SCIERPR address

- A baud rate register: LPR mapped at the SCI-BRR address and an associated fraction register LPFR mapped at the SCIETPR address

The bits dedicated to LIN are located in the SCICR3. Refer to the register descriptions in Section 0.1.10 for the definitions of each bit.

#### 10.7.9.1 Entering LIN Mode

To use the LINSCI in LIN mode the following configuration must be set in SCICR3 register:

- Clear the M bit to configure 8-bit word length.

- Set the LINE bit.

#### Master

To enter master mode the LSLV bit must be reset In this case, setting the SBK bit will send 13 low bits.

Then the baud rate can programmed using the SCIBRR, SCIERPR and SCIETPR registers.

In LIN master mode, the Conventional and / or Extended Prescaler define the baud rate (as in standard SCI mode)

## Slave

Set the LSLV bit in the SCICR3 register to enter LIN slave mode. In this case, setting the SBK bit will have no effect.

In LIN Slave mode the LIN baud rate generator is selected instead of the Conventional or Extended Prescaler. The LIN baud rate generator is common to the transmitter and the receiver.

Then the baud rate can be programmed using LPR and LPRF registers.

**Note:** It is mandatory to set the LIN configuration first before programming LPR and LPRF, because the LIN configuration uses a different baud rate generator from the standard one.

#### 10.7.9.2 LIN Transmission

In LIN mode the same procedure as in SCI mode has to be applied for a LIN transmission.

To transmit the LIN Header the proceed as follows:

- First set the SBK bit in the SCICR2 register to start transmitting a 13-bit LIN Synch Break

- reset the SBK bit

- Load the LIN Synch Field (0x55) in the SCIDR register to request Synch Field transmission

- Wait until the SCIDR is empty (TDRE bit set in the SCISR register)

- Load the LIN message Identifier in the SCIDR register to request Identifier transmission.

<u>ل ۲</u>۲

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### 10.7.9.7 LINSCI Clock Tolerance

#### LINSCI Clock Tolerance when unsynchronized

When LIN slaves are unsynchronized (meaning no characters have been transmitted for a relatively long time), the maximum tolerated deviation of the LINSCI clock is +/-15%.

If the deviation is within this range then the LIN Synch Break is detected properly when a new reception occurs.

This is made possible by the fact that masters send 13 low bits for the LIN Synch Break, which can be interpreted as 11 low bits (13 bits -15% = 11.05) by a "fast" slave and then considered as a LIN Synch Break. According to the LIN specification, a LIN Synch Break is valid when its duration is greater than t<sub>SBRKTS</sub> = 10. This means that the LIN Synch Break must last at least 11 low bits.

**Note:** If the period desynchronization of the slave is +15% (slave too slow), the character "00h" which represents a sequence of 9 low bits must not be interpreted as a break character (9 bits + 15% = 10.35). Consequently, a valid LIN Synch break must last at least 11 low bits.

#### LINSCI Clock Tolerance when Synchronized

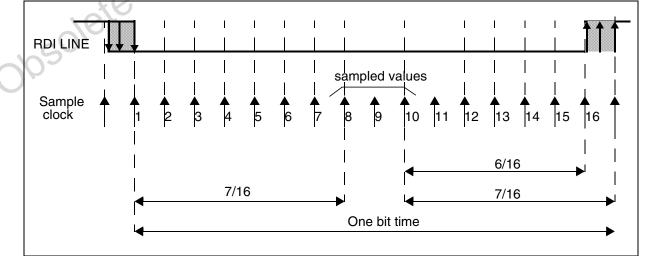

When synchronization has been performed, following reception of a LIN Synch Break, the LINS-CI, in LIN mode, has the same clock deviation tolerance as in SCI mode, which is explained below:

During reception, each bit is oversampled 16 times. The mean of the 8th, 9th and 10th samples is considered as the bit value.

Figure 86.Bit Sampling in Reception Mode

67/

Consequently, the clock frequency should not vary more than 6/16 (37.5%) within one bit.

The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation should not exceed 3.75%.

#### 10.7.9.8 Clock Deviation Causes

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error.

Note: The transmitter can be either a master or a slave (in case of a slave listening to the response of another slave).

- D<sub>MEAS</sub>: Error due to the LIN Synch measurement performed by the receiver.

- D<sub>QUANT</sub>: Error due to the baud rate quantization of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete LIN message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the LINSCI clock tolerance:

$D_{TRA} + D_{MEAS} + D_{QUANT} + D_{REC} + D_{TCL} < 3.75\%$

## LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### 10.7.9.9 Error due to LIN Synch measurement

The LIN Synch Field is measured over eight bit times.

This measurement is performed using a counter clocked by the CPU clock. The edge detections are performed using the CPU clock cycle.

This leads to a precision of 2 CPU clock cycles for the measurement which lasts 16\*8\*LDIV clock cycles.

Consequently, this error (D<sub>MEAS</sub>) is equal to:

2 / (128\*LDIV<sub>MIN</sub>).

$LDIV_{MIN}$  corresponds to the minimum LIN prescaler content, leading to the maximum baud rate, taking into account the maximum deviation of +/-15%.

#### 10.7.9.10 Error due to Baud Rate Quantization

The baud rate can be adjusted in steps of 1 / (16 \* LDIV). The worst case occurs when the "real" baud rate is in the middle of the step.

This leads to a quantization error ( $D_{QUANT}$ ) equal to 1 / (2\*16\*LDIV<sub>MIN</sub>).

#### 10.7.9.11 Impact of Clock Deviation on Maximum Baud Rate

The choice of the nominal baud rate (LDIV<sub>NOM</sub>) will influence both the quantization error ( $D_{QUANT}$ ) and the measurement error ( $D_{MEAS}$ ). The worst case occurs for LDIV<sub>MIN</sub>.

Consequently, at a given CPU frequency, the maximum possible nominal baud rate (LPR<sub>MIN</sub>) should be chosen with respect to the maximum tolerated deviation given by the equation:

D<sub>TRA</sub> + 2 / (128\*LDIV<sub>MIN</sub>) + 1 / (2\*16\*LDIV<sub>MIN</sub>)

$+ D_{REC} + D_{TCL} < 3.75\%$

#### Example:

A nominal baud rate of 20Kbits/s at  $T_{CPU}$  = 125ns (8 MHz) leads to LDIV<sub>NOM</sub> = 25d.

LDIV<sub>MIN</sub> = 25 - 0.15\*25 = 21.25

D<sub>MEAS</sub> = 2 / (128\*LDIV<sub>MIN</sub>) \* 100 = 0.00073%

D<sub>QUANT</sub> = 1 / (2\*16\*LDIV<sub>MIN</sub>) \* 100 = 0.0015%

## LIN Slave systems

For LIN Slave systems (the LINE and LSLV bits are set), receivers wake up by LIN Synch Break or LIN Identifier detection (depending on the LHDM bit).

## Hot Plugging Feature for LIN Slave Nodes

In LIN Slave Mute Mode (the LINE, LSLV and RWU bits are set) it is possible to hot plug to a network during an ongoing communication flow. In this case the SCI monitors the bus on the RDI line until 11 consecutive dominant bits have been detected and discards all the other bits received.

## **beCAN CONTROLLER** (Cont'd)

- The FIFO interrupt can be generated by the following events:

- Reception of a new message, FMP bits in the CRFR0 register incremented.

- FIFO0 full condition, FULL bit in the CRFR0 register set.

- FIFO0 overrun condition, FOVR bit in the CRFR0 register set.

- The transmit, error and status change interrupt can be generated by the following events:

- Transmit mailbox 0 becomes empty, RQCP0 bit in the CTSR register set.

- Transmit mailbox 1 becomes empty, RQCP1 bit in the CTSR register set.

- Error condition, for more details on error conditions please refer to the CAN Error Status register (CESR).

- Wake-up condition, SOF monitored on the done by s

CAN Rx signal.

#### **10.9.6 Register Access Protection**

Erroneous access to certain configuration registers can cause the hardware to temporarily disturb the whole CAN network. Therefore the following registers can be modified by software only while the hardware is in initialization mode:

CBTR0, CBTR1, CFCR0, CFCR1, CFMR and CDGR registers.

Although the transmission of incorrect data will not cause problems at the CAN network level, it can severely disturb the application. A transmit mailbox can be only modified by software while it is in empty state (refer to Figure 7. Transmit Mailbox States).

The filters must be deactivated before their value can be modified by software. The modification of the filter configuration (scale or mode) can be done by software only in initialization mode.

## beCAN CONTROLLER (Cont'd)

Bits 3:0 **BS1[3:0]** *Time Segment 1* These bits define the number of time quanta in Time Segment 1

Time Segment 1 = (BS1+1)

For more information on bit timing, please refer to Section 0.1.4.6 Bit Timing.

## CAN FILTER PAGE SELECT REGISTER

## (CPSR)

All bits of this register are set and cleared by software.

Read / Write

Reset Value: 0000 0000 (00h)

|   | 7  |     |    |    |    |      |      | 0    |   | 4     | Acceptance  |

|---|----|-----|----|----|----|------|------|------|---|-------|-------------|

|   | ,  |     |    |    |    | 1    |      | Ű    | 1 | 5     | Reserved    |

|   | 0  | 0   | 0  | 0  | 0  | FPS2 | FPS1 | FPS0 |   | 6     | Configurati |

|   |    | -   | -  |    |    |      |      |      | J | 7     | Receive FI  |

| 0 | 05 | 016 | ţO | Р( | 00 |      | 19   |      | 0 | psolf | ste '       |

Bits 7:3 = Reserved. Forced to 0 by hardware.

## Bits 2:0 = **PS[2:0]** *Page Select* - Read/Write

This register contains the page number.

## Table 31. Filter Page Selection

| PS[2:0] | Page Selected           |  |  |  |  |  |  |  |

|---------|-------------------------|--|--|--|--|--|--|--|

| 0       | Tx Mailbox 0            |  |  |  |  |  |  |  |

| 1       | Tx Mailbox 1            |  |  |  |  |  |  |  |

| 2       | Acceptance Filter 0:1   |  |  |  |  |  |  |  |

| 3       | Acceptance Filter 2:3   |  |  |  |  |  |  |  |

| 4       | Acceptance Filter 4:5   |  |  |  |  |  |  |  |

| 5       | Reserved                |  |  |  |  |  |  |  |

| 6       | Configuration/Diagnosis |  |  |  |  |  |  |  |

| 7       | Receive FIFO            |  |  |  |  |  |  |  |

## beCAN CONTROLLER (Cont'd)

## CAN FILTER MODE REGISTER (CFMR1)

All bits of this register are set and cleared by software.

Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |      |      |      | 0    |

|---|---|---|---|------|------|------|------|

| 0 | 0 | 0 | 0 | FMH5 | FML5 | FMH4 | FML4 |

Bits 7:4 = Reserved. Forced to 0 by hardware.

#### Bit 3 = FMH5 Filter Mode High

Mode of the high registers of Filter 5. 0: High registers are in mask mode 1: High registers are in identifier list mode

Bit 2 = **FML5** *Filter Mode Low* Mode of the low registers of filter 5. 0: Low registers are in mask mode 1: Low registers are in identifier list mode

Bit 1 = FMH4 Filter Mode High

Mode of the high registers of filter 4.

0: High registers are in mask mode

1: High registers are in identifier list mode

Bit 0 = **FML4** *Filter Mode Low* Mode of the low registers of filter 4. 0: Low registers are in mask mode 1: Low registers are in identifier list mode

## FILTER x REGISTER[7:0] (CFxR[7:0])

Read / Write

Reset Value: Undefined

| 1   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| FB7 | FB6 | FB5 | FB4 | FB3 | FB2 | FB1 | FB0 |

#### In all configurations:

Bits 7:0 = FB[7:0] Filter Bits

#### Identifier

Each bit of the register specifies the level of the corresponding bit of the expected identifier.

0: Dominant bit is expected

1: Recessive bit is expected

#### Mask

Each bit of the register specifies whether the bit of the associated identifier register must match with the corresponding bit of the expected identifier or not.

0: Don't care, the bit is not used for the comparison

1: Must match, the bit of the incoming identifier must have the same level has specified in the corresponding identifier register of the filter.

**Note:** Each filter x is composed of 8 registers, CFxR[7:0]. Depending on the scale and mode configuration of the filter the function of each register can differ. For the filter mapping, functions description and mask registers association, refer to Section 0.1.4.3 Identifier Filtering.

A Mask/Identifier register in **mask mode** has the same bit mapping as in **identifier list** mode.

**Note**: To modify these registers, the corresponding FACT bit in the CFCR register must be cleared.

)psolete

## 10.10 10-BIT A/D CONVERTER (ADC)

#### 10.10.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

#### 10.10.2 Main Features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

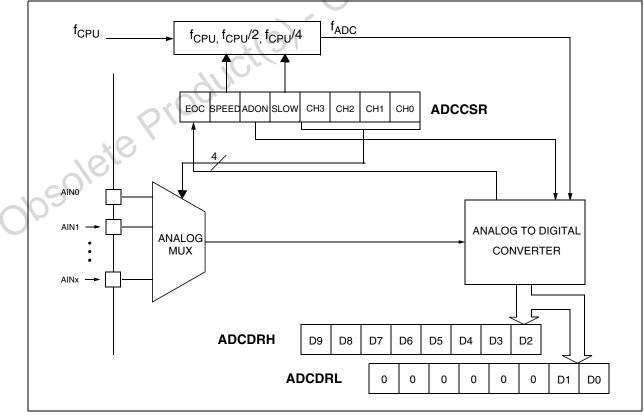

The block diagram is shown in Figure 116.

## Figure 116. ADC Block Diagram

#### 10.10.3 Functional Description

#### 10.10.3.1 Digital A/D Conversion Result

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{DDA}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and AD-CDRL registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the allotted time.

## **12.4 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode for which the clock is stopped).

| Cumbal          | Deveneter                                          | Conditions                                                                                                                                                                                                                                                     | Flash Devices              |                        | <b>ROM Devices</b>           |                          |      |

|-----------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|------------------------------|--------------------------|------|

| Symbol          | Parameter                                          | Conditions                                                                                                                                                                                                                                                     | Typ <sup>1)</sup>          | Max <sup>2)</sup>      | Typ <sup>1</sup>             | Max <sup>2)</sup>        | Unit |

| I <sub>DD</sub> | Supply current in RUN mode <sup>3)</sup>           | $ \begin{array}{l} f_{OSC} = 2 \ \text{MHz}, \ f_{CPU} = 1 \ \text{MHz} \\ f_{OSC} = 4 \ \text{MHz}, \ f_{CPU} = 2 \ \text{MHz} \\ f_{OSC} = 8 \ \text{MHz}, \ f_{CPU} = 4 \ \text{MHz} \\ f_{OSC} = 16 \ \text{MHz}, \ f_{CPU} = 8 \ \text{MHz} \end{array} $ | 1.8<br>3.2<br>6<br>10      | 3<br>5<br>8<br>15      | 1.1<br>2.2<br>4.4<br>8.9     | 2<br>3.5<br>6<br>12      |      |

|                 | Supply current in SLOW mode <sup>3)</sup>          |                                                                                                                                                                                                                                                                | 0.5<br>0.6<br>0.85<br>1.25 | 2.7<br>3<br>3.6<br>4   | 0.1<br>0.2<br>0.4<br>0.8     | 0.2<br>0.4<br>0.8<br>1.5 | mA   |

|                 | Supply current in WAIT mode <sup>3)</sup>          | $ \begin{array}{l} f_{OSC} = 2 \ \text{MHz}, f_{CPU} = 1 \ \text{MHz} \\ f_{OSC} = 4 \ \text{MHz}, f_{CPU} = 2 \ \text{MHz} \\ f_{OSC} = 8 \ \text{MHz}, f_{CPU} = 4 \ \text{MHz} \\ f_{OSC} = 16 \ \text{MHz}, f_{CPU} = 8 \ \text{MHz} \end{array} $         | 1<br>1.8<br>3.4<br>6.4     | 3<br>4<br>5<br>7       | 0.7<br>1.4<br>2.9<br>5.7     | 3<br>4<br>5<br>7         |      |

|                 | Supply current in SLOW WAIT mode <sup>2)</sup>     |                                                                                                                                                                                                                                                                | 0.4<br>0.5<br>0.6<br>0.8   | 1.2<br>1.3<br>1.8<br>2 | 0.07<br>0.14<br>0.28<br>0.56 | 0.12<br>0.25<br>0.5<br>1 |      |

|                 | Supply current in HALT mode <sup>4)</sup>          | $V_{DD} = 5.5V \frac{-40^{\circ}C \le T_A \le +85^{\circ}C}{-40^{\circ}C \le T_A \le +125^{\circ}C}$                                                                                                                                                           | <1                         | 10<br>50               | <1                           | 10<br>50                 | μA   |

|                 | Supply current in ACTIVE HALT mode <sup>4)5)</sup> |                                                                                                                                                                                                                                                                | 0.5                        | 1.2                    | 0.18                         | 0.25                     | mA   |

|                 | Supply current in AWUFH mode <sup>4)5)</sup>       | $V_{DD} = 5.5V \frac{-40^{\circ}C \le T_A \le +85^{\circ}C}{-40^{\circ}C \le T_A \le +125^{\circ}C}$                                                                                                                                                           | 25                         | 30<br>70               | 25                           | 30<br>70                 | μA   |

Notes:

1. Typical data are based on  $T_A$  = 25°C,  $V_{DD}$  = 5V (4.5V  $\leq V_{DD} \leq$  5.5V range).

2. Data based on characterization results, tested in production at  $V_{DD}$  max.,  $f_{CPU}$  max. and  $T_A$  max.

3. Measurements are done in the following conditions:

- Program executed from Flash, CPU running with Flash (for flash devices).

- All I/O pins in input mode with a static value at  $V_{DD} \, \text{or} \, V_{SS}$  (no load)

- All peripherals in reset state.

- Clock input (OSC1) driven by external square wave.

- In SLOW and SLOW WAIT mode, f<sub>CPU</sub> is based on f<sub>OSC</sub> divided by 32.

To obtain the total current consumption of the device, add the clock source (Section 12.5.3) and the peripheral power consumption (Section 12.4.2).

4. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load). Data based on characterization results, tested in production at  $V_{DD}$  max.,  $f_{CPU}$  max. and  $T_A$  max.

5. This consumption refers to the Halt period only and not the associated run period which is software dependent.

<u>/</u>ک

5

## 12.4.2 On-Chip Peripherals

$T_A = 25^{\circ}C$ ,  $f_{CPU} = 8$  MHz.

| Symbol                | Parameter                                        | Condi | tions                  | Тур | Unit |

|-----------------------|--------------------------------------------------|-------|------------------------|-----|------|

| I <sub>DD(TIM)</sub>  | 16-bit Timer supply current <sup>1)</sup>        |       |                        | 50  |      |

| I <sub>DD(TIM8)</sub> | 8-bit Timer supply current <sup>1)</sup>         |       | V <sub>DD</sub> = 5.0V | 50  | μA   |

| I <sub>DD(ART)</sub>  | ART PWM supply current <sup>2)</sup>             |       |                        | 75  |      |

| I <sub>DD(SPI)</sub>  | SPI supply current <sup>3)</sup>                 |       |                        | 400 |      |

| I <sub>DD(SCI)</sub>  | SCI supply current <sup>4)</sup>                 |       |                        |     |      |

| I <sub>DD(ADC)</sub>  | ADC supply current when converting <sup>5)</sup> |       |                        |     |      |

| I <sub>DD(CAN)</sub>  | CAN supply current <sup>6)</sup>                 |       |                        | 800 |      |

#### Notes:

- 1. Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer counter running at f<sub>CPU</sub>/4) and timer counter stopped (only TIMD bit set). Data valid for one timer.

- Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer stopped) and timer counter enabled (only TCE bit set).

- 3. Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to 55h). This measurement includes the pad toggling consumption.

4. Data based on a differential I<sub>DD</sub> measurement between SCI low power state (SCID = 1) and a permanent SCI data transmit sequence. Data valid for one SCI.

- 5. Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions.

- 6. Data based on a differential I<sub>DD</sub> measurement between reset configuration (CAN disabled) and a permanent CAN data transmit sequence with RX and TX connected together. This measurement include the pad toggling consumption.

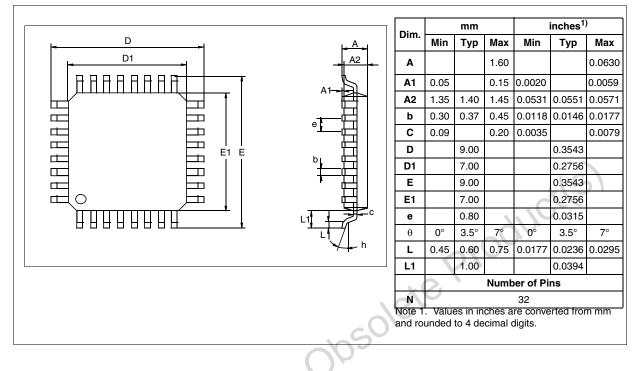

## Figure 149. 32-Pin Low Profile Quad Flat Package (7x7)

## 13.2 THERMAL CHARACTERISTICS

| Symbol            | Ratings                                                                        | Value          | Unit |

|-------------------|--------------------------------------------------------------------------------|----------------|------|

| R <sub>thJA</sub> | Package thermal resistance (junction to ambient)<br>LQFP64<br>LQFP44<br>LQFP32 | 60<br>52<br>70 | °C/W |

| PD                | Power dissipation <sup>1)</sup>                                                | 500            | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>                                     | 150            | °C   |

#### Notes:

1. The maximum power dissipation is obtained from the formula  $P_D = (T_J - T_A) / R_{thJA}$ . The power dissipation of an application can be defined by the user with the formula:  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD} \times V_{DD}$ ) and  $P_{PORT}$  is the port power dissipation depending on the ports used in the application. 2. The maximum chip-junction temperature is based on technology characteristics.

## **13.3 SOLDERING AND GLUEABILITY INFORMATION**

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard

JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK® specifications are available at www.st.com.

57