Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | CANbus, LINbusSCI, SPI                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 6x10b                                                             |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561k4tae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

# 6.4.4 Register Description

# SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

Read/Write

Reset Value: 000x 000x (00h)

| 7 |           |          |           |   |   |   | 0         |

|---|-----------|----------|-----------|---|---|---|-----------|

| 0 | AVD<br>IE | AVD<br>F | LVD<br>RF | 0 | 0 | 0 | WDG<br>RF |

Bit 7 = Reserved, must be kept cleared.

Bit 6 = **AVDIE** Voltage Detector interrupt enable This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag changes (toggles). The pending interrupt information is automatically cleared when software enters the AVD interrupt routine. 0: AVD interrupt disabled

1: AVD interrupt enabled

#### Bit 5 = **AVDF** Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 16 and to Section 6.4.2.1 for additional details.

0:  $V_{DD}$  over  $V_{IT+(AVD)}$  threshold 1:  $V_{DD}$  under  $V_{IT-(AVD)}$  threshold

#### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined. Bits 3:1 = Reserved, must be kept cleared.

#### Bit 0 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

|                    |       |       |

#### Application notes

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

**CAUTION:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

# **7 INTERRUPTS**

# 7.1 INTRODUCTION

The ST7 enhanced interrupt management provides the following features:

- Hardware interrupts

- Software interrupt (TRAP)

- Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 2 non maskable events: RESET, TRAP

- 1 maskable Top Level Event: TLI

- This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) ST7 interrupt controller.

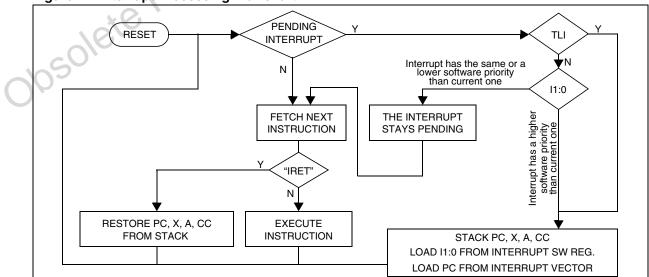

# 7.2 MASKING AND PROCESSING FLOW

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of

each interrupt vector (see Table 6). The processing flow is shown in Figure 17.

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to "Interrupt Mapping" table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note**: As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.

# Table 7. Interrupt Software Priority Levels

| Interrupt software priority   | Level | 11 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | •     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

# Figure 17. Interrupt Processing Flowchart

57

### INTERRUPTS (Cont'd)

# 7.3 INTERRUPTS AND LOW POWER MODES

All interrupts allow the processor to exit the WAIT low power mode. On the contrary, only external and other specified interrupts allow the processor to exit from the HALT modes (see column "Exit from HALT" in "Interrupt Mapping" table). When several pending interrupts are present while exiting HALT mode, the first one serviced can only be an interrupt with exit from HALT mode capability and it is selected through the same decision process shown in Figure 18.

**Note:** If an interrupt, that is not able to Exit from HALT mode, is pending with the highest priority when exiting HALT mode, this interrupt is serviced after the first one serviced.

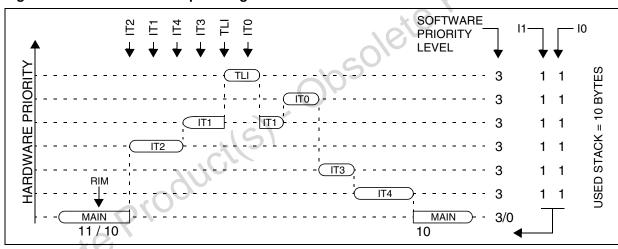

Figure 19. Concurrent Interrupt Management

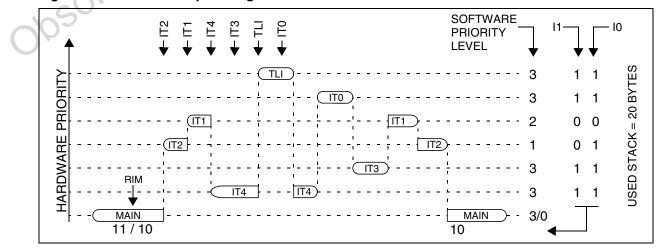

# 7.4 CONCURRENT & NESTED MANAGEMENT

The following Figure 19 and Figure 20 show two different interrupt management modes. The first is called concurrent mode and does not allow an interrupt to be interrupted, unlike the nested mode in Figure 20. The interrupt hardware priority is given in this order from the lowest to the highest: MAIN, IT4, IT3, IT2, IT1, IT0, TLI. The software priority is given for each interrupt.

**Warning**: A stack overflow may occur without notifying the software of the failure.

Figure 20. Nested Interrupt Management

<u>ل</u>رک

### **POWER SAVING MODES** (Cont'd)

#### Halt Mode Recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

<u>لرک</u>

# 8.5 ACTIVE HALT MODE

ACTIVE HALT mode is the lowest power consumption mode of the MCU with a real time clock available. It is entered by executing the 'HALT' instruction when MCC/RTC interrupt enable flag (OIE bit in MCCSR register) is set and when the AWUEN bit in the AWUCSR register is cleared (See "Register Description" on page 45.)

| MCCSR<br>OIE bit | Power Saving Mode entered when HALT<br>instruction is executed |  |  |  |  |

|------------------|----------------------------------------------------------------|--|--|--|--|

| 0                | HALT mode                                                      |  |  |  |  |

| 1                | ACTIVE HALT mode                                               |  |  |  |  |

|                  |                                                                |  |  |  |  |

The MCU can exit ACTIVE HALT mode on reception of the RTC interrupt and some specific interrupts (see Table 9, "Interrupt Mapping," on page 34) or a RESET. When exiting ACTIVE HALT mode by means of a RESET a 4096 or 256 CPU cycle delay occurs (depending on the option byte). After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 28).

When entering ACTIVE HALT mode, the I[1:0] bits in the CC register are are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In ACTIVE HALT mode, only the main oscillator and its associated counter (MCC/RTC) are running to keep a wake-up time base. All other peripherals are not clocked except those which get their clock supply from another clock generator (such as external or auxiliary oscillator).

The safeguard against staying locked in ACTIVE HALT mode is provided by the oscillator interrupt.

**Note:** As soon as active halt is enabled, executing a HALT instruction while the Watchdog is active does not generate a RESET.

This means that the device cannot spend more than a defined delay in this power saving mode.

# POWER SAVING MODES (Cont'd)

### 8.6 AUTO WAKE-UP FROM HALT MODE

Auto Wake-Up From Halt (AWUFH) mode is similar to Halt mode with the addition of an internal RC oscillator for wake-up. Compared to ACTIVE HALT mode, AWUFH has lower power consumption because the main clock is not kept running, but there is no accurate realtime clock available.

It is entered by executing the HALT instruction when the AWUEN bit in the AWUCSR register has been set and the OIE bit in the MCCSR register is cleared (see Section 10.2 on page 59 for more details).

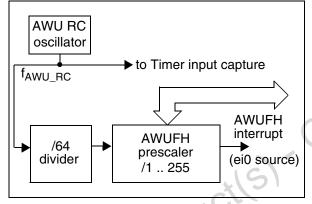

#### Figure 29. AWUFH Mode Block Diagram

As soon as HALT mode is entered, and if the AWUEN bit has been set in the AWUCSR register, the AWU RC oscillator provides a clock signal ( $f_{AWU_RC}$ ). Its frequency is divided by a fixed divider and a programmable prescaler controlled by the AWUPR register. The output of this prescaler provides the delay time. When the delay has elapsed the AWUF flag is set by hardware and an interrupt wakes up the MCU from Halt mode. At the same time the main oscillator is immediately turned on

Figure 30. AWUF Halt Timing Diagram

<u>ل</u>حک

and a 256 or 4096 cycle delay is used to stabilize it. After this start-up delay, the CPU resumes operation by servicing the AWUFH interrupt. The AWU flag and its associated interrupt are cleared by software reading the AWUCSR register.

To compensate for any frequency dispersion of the AWU RC oscillator, it can be calibrated by measuring the clock frequency  $f_{AWU}$  RC and then calculating the right prescaler value. Measurement mode is enabled by setting the AWUM bit in the AWUCSR register in Run mode. This connects  $f_{AWU}$  RC to the ICAP1 input of the 16-bit timer, allowing the  $f_{AWU}$  RC to be measured using the main oscillator clock as a reference timebase.

#### Similarities with Halt mode

The following AWUFH mode behavior is the same as normal Halt mode:

- The MCU can exit AWUFH mode by means of any interrupt with exit from Halt capability or a reset (see Section 8.4 "HALT MODE").

- When entering AWUFH mode, the I[1:0] bits in the CC register are forced to 10b to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

- In AWUFH mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. None of the peripherals are clocked except those which get their clock supply from another clock generator (such as an external or auxiliary oscillator like the AWU oscillator).

- The compatibility of Watchdog operation with AWUFH mode is configured by the WDGHALT option bit in the option byte. Depending on this setting, the HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET.

|                     |           | • t <sub>AWU</sub> | ļ                            |                      |

|---------------------|-----------|--------------------|------------------------------|----------------------|

|                     | RUN MODE  | HALT MODE          | 256 or 4096 t <sub>CPU</sub> | RUN MODE             |

| f <sub>CPU</sub>    |           |                    |                              |                      |

| f <sub>AWU_RC</sub> |           |                    |                              |                      |

| AWUFH               | interrupt |                    |                              | Clear<br>by software |

43/265

# 9 I/O PORTS

# 9.1 INTRODUCTION

The I/O ports offer different functional modes: - transfer of data through digital inputs and outputs

and for specific pins:

- external interrupt generation

- alternate signal input/output for the on-chip peripherals.

An I/O port contains up to 8 pins. Each pin can be programmed independently as digital input (with or without interrupt generation) or digital output.

# 9.2 FUNCTIONAL DESCRIPTION

Each port has two main registers:

- Data Register (DR)

- Data Direction Register (DDR)

and one optional register:

- Option Register (OR)

Each I/O pin may be programmed using the corresponding register bits in the DDR and OR registers: Bit X corresponding to pin X of the port. The same correspondence is used for the DR register.

The following description takes into account the OR register, (for specific ports which do not provide this register refer to the I/O Port Implementation section). The generic I/O block diagram is shown in Figure 32

# 9.2.1 Input Modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

# Notes:

1. Writing the DR register modifies the latch value but does not affect the pin status.

2. When switching from input to output mode, the DR register has to be written first to drive the correct level on the pin as soon as the port is configured as an output.

3. Do not use read/modify/write instructions (BSET or BRES) to modify the DR register as this might corrupt the DR content for I/Os configured as input.

#### **External interrupt function**

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an external interrupt request to the CPU.

Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout description and interrupt section). If several input pins are selected simultaneously as interrupt sources, these are first detected according to the sensitivity bits in the EICR register and then logically ORed.

The external interrupts are hardware interrupts, which means that the request latch (not accessible directly by the application) is automatically cleared when the corresponding interrupt vector is fetched. To clear an unwanted pending interrupt by software, the sensitivity bits in the EICR register must be modified.

# 9.2.2 Output Modes

The output configuration is selected by setting the corresponding DDR register bit. In this case, writing the DR register applies this digital value to the I/O pin through the latch. Then reading the DR register returns the previously stored value.

Two different output modes can be selected by software through the OR register: Output push-pull and open-drain.

DR register value and output pin status:

| DR | Push-pull       | Open-drain |

|----|-----------------|------------|

| 0  | V <sub>SS</sub> | Vss        |

| 1  | V <sub>DD</sub> | Floating   |

# 9.2.3 Alternate Functions

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over the standard I/O programming.

When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

When the signal is going to an on-chip peripheral, the I/O pin must be configured in input mode. In this case, the pin state is also digitally readable by addressing the DR register.

**Note:** Input pull-up configuration can cause unexpected value at the input of the alternate peripheral input. When an on-chip peripheral use a pin as input and output, this pin has to be configured in input floating mode.

# 16-BIT TIMER (Cont'd) 10.4.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 16-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                      |

|      | 16-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                           |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                             |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequently, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

# 10.4.5 Interrupts

| Interrupt Event                                    | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |    |

|----------------------------------------------------|---------------|--------------------------|----------------------|----------------------|----|

| Input Capture 1 event/Counter reset in PWM mode    | ICF1          | ICIE                     |                      |                      |    |

| Input Capture 2 event                              |               |                          |                      |                      |    |

| Output Compare 1 event (not available in PWM mode) |               | OCF1                     | OCIE                 | Yes                  | No |

| Output Compare 2 event (not available in PWM mode) |               | OCF2                     | OCIE                 |                      |    |

| Timer Overflow event                               | S             | TOF                      | TOIE                 |                      |    |

**Note:** The 16-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# 10.4.6 Summary of Timer Modes

| MODES                       | TIMER RESOURCES |                               |                  |                         |  |  |

|-----------------------------|-----------------|-------------------------------|------------------|-------------------------|--|--|

| MODES                       | Input Capture 1 | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |  |

| Input Capture (1 and/or 2)  | Yes             | Yes                           | Yes              | Yes                     |  |  |

| Output Compare (1 and/or 2) | 165             | 165                           | 165              | 165                     |  |  |

| One Pulse Mode              | No              | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |  |

| PWM Mode                    | NO              | Not Recommended <sup>3)</sup> | NO               | No                      |  |  |

1) See note 4 in Section 10.4.3.5 "One Pulse Mode"

2) See note 5 in Section 10.4.3.5 "One Pulse Mode"

3) See note 4 in Section 10.4.3.6 "Pulse Width Modulation Mode"

**لركم**

# 8-BIT TIMER (Cont'd)

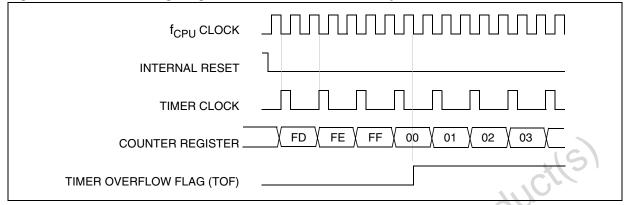

# Figure 60. Counter Timing Diagram, Internal Clock Divided by 2

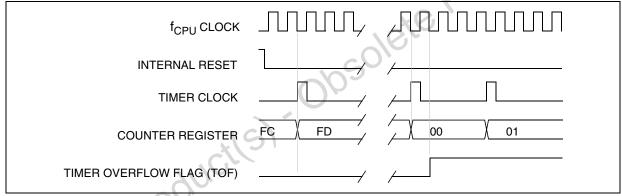

# Figure 61. Counter Timing Diagram, Internal Clock Divided by 4

# Figure 62. Counter Timing Diagram, Internal Clock Divided by 8

|   | f <sub>CPU</sub> CLOCK    |          |

|---|---------------------------|----------|

| 1 | INTERNAL RESET            | 1        |

|   | TIMER CLOCK               |          |

|   | COUNTER REGISTER          | FC FD 00 |

|   | TIMER OVERFLOW FLAG (TOF) |          |

Note: The MCU is in reset state when the internal reset signal is high, when it is low the MCU is running.

# 8-BIT TIMER (Cont'd) CONTROL REGISTER 2 (CR2)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |     |     |     |       | 0 |

|------|------|-----|-----|-----|-----|-------|---|

| OC1E | OC2E | OPM | PWM | CC1 | CC0 | IEDG2 | 0 |

# Bit 7 = **OC1E** *Output Compare 1 Pin Enable.*

This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode). Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.

- 0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP1 pin alternate function enabled.

#### Bit 6 = **OC2E** Output Compare 2 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.

- 0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP2 pin alternate function enabled.

Bit 5 = **OPM** One Pulse Mode.

- 0: One Pulse Mode is not active.

- 1: One Pulse Mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.

Bit 4 = **PWM** Pulse Width Modulation.

- 0: PWM mode is not active.

- 1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.

# Bit 3, 2 = **CC[1:0]** *Clock Control.*

The timer clock mode depends on these bits:

#### Table 20. Clock Control Bits

| Timer Clock               | CC1 | CC0 |

|---------------------------|-----|-----|

| f <sub>CPU</sub> / 4      | 0   | 0   |

| f <sub>CPU</sub> / 2      | 0   | 1   |

| f <sub>CPU</sub> / 8      | KU1 | 0   |

| f <sub>OSC2</sub> / 8000* | 1   | 1   |

16

\* Not available in Slow mode in ST72F561.

Bit 1 = IEDG2 Input Edge 2.

This bit determines which type of level transition on the ICAP2 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

Bit 0 = Reserved, must be kept at 0.

# SERIAL PERIPHERAL INTERFACE (cont'd)

# 10.6.3.1 Functional Description

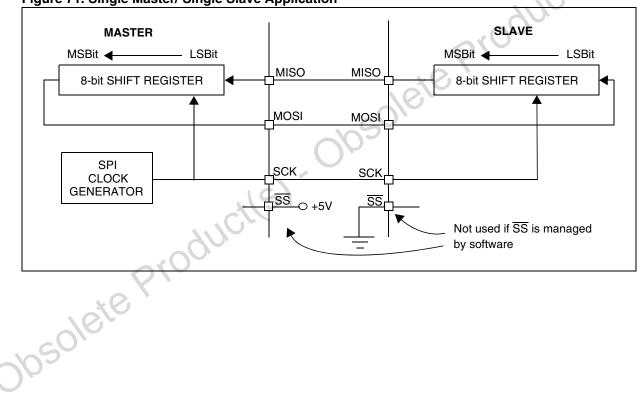

A basic example of interconnections between a single master and a single slave is illustrated in Figure 71.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 74 on page 114) but master and slave must be programmed with the same timing mode.

#### Figure 71. Single Master/ Single Slave Application

### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### 10.7.9.7 LINSCI Clock Tolerance

#### LINSCI Clock Tolerance when unsynchronized

When LIN slaves are unsynchronized (meaning no characters have been transmitted for a relatively long time), the maximum tolerated deviation of the LINSCI clock is +/-15%.

If the deviation is within this range then the LIN Synch Break is detected properly when a new reception occurs.

This is made possible by the fact that masters send 13 low bits for the LIN Synch Break, which can be interpreted as 11 low bits (13 bits -15% = 11.05) by a "fast" slave and then considered as a LIN Synch Break. According to the LIN specification, a LIN Synch Break is valid when its duration is greater than t<sub>SBRKTS</sub> = 10. This means that the LIN Synch Break must last at least 11 low bits.

**Note:** If the period desynchronization of the slave is +15% (slave too slow), the character "00h" which represents a sequence of 9 low bits must not be interpreted as a break character (9 bits + 15% = 10.35). Consequently, a valid LIN Synch break must last at least 11 low bits.

#### LINSCI Clock Tolerance when Synchronized

When synchronization has been performed, following reception of a LIN Synch Break, the LINS-CI, in LIN mode, has the same clock deviation tolerance as in SCI mode, which is explained below:

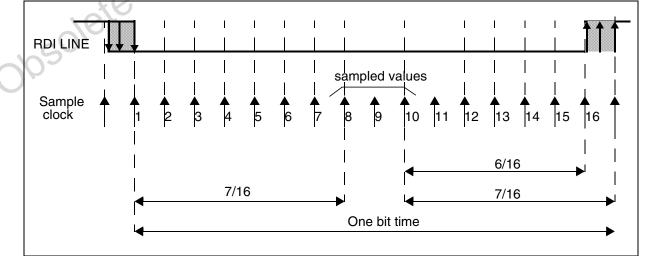

During reception, each bit is oversampled 16 times. The mean of the 8th, 9th and 10th samples is considered as the bit value.

Figure 86.Bit Sampling in Reception Mode

67/

Consequently, the clock frequency should not vary more than 6/16 (37.5%) within one bit.

The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation should not exceed 3.75%.

#### 10.7.9.8 Clock Deviation Causes

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error.

Note: The transmitter can be either a master or a slave (in case of a slave listening to the response of another slave).

- D<sub>MEAS</sub>: Error due to the LIN Synch measurement performed by the receiver.

- D<sub>QUANT</sub>: Error due to the baud rate quantization of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete LIN message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the LINSCI clock tolerance:

$D_{TRA} + D_{MEAS} + D_{QUANT} + D_{REC} + D_{TCL} < 3.75\%$

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

# **CONTROL REGISTER 3 (SCICR3)**

### Read/Write

Reset Value: 0000 0000 (00h)

Bit 7 = Reserved, must be kept cleared.

#### Bit 6 = LINE LIN Mode Enable.

This bit is set and cleared by software. 0: LIN Mode disabled 1: LIN Master mode enabled

The LIN Master mode enables the capability to send LIN Synch Breaks (13 low bits) using the SBK bit in the SCICR2 register

.In transmission, the LIN Synch Break low phase duration is shown as below:

| LINE | М   | Number of low bits sent<br>during a LIN Synch Break<br>10<br>11<br>13 |  |  |  |

|------|-----|-----------------------------------------------------------------------|--|--|--|

| 0    | 0   | 10                                                                    |  |  |  |

| 0    | 0 1 | 11                                                                    |  |  |  |

| 4    | 0   | 13                                                                    |  |  |  |

| I    | 1   | 14                                                                    |  |  |  |

|      |     |                                                                       |  |  |  |

Bits 5:4 = Reserved, forced by hardware to 0. These bits are not used.

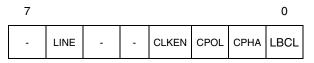

Bit 3 = CLKEN Clock Enable.

This bit allows the user to enable the SCLK pin. 0: SLK pin disabled

1: SLK pin enabled

# Bit 2 = **CPOL** Clock Polarity.

This bit allows the user to select the polarity of the clock output on the SCLK pin. It works in conjunction with the CPHA bit to produce the desired clock/data relationship (see Figure 92 and Figure 93).

- 0: Steady low value on SCLK pin outside transmission window.

- 1: Steady high value on SCLK pin outside transmission window.

# Bit 1 = CPHA Clock Phase.

This bit allows the user to select the phase of the clock output on the SCLK pin. It works in conjunction with the CPOL bit to produce the desired clock/data relationship (see Figure 92 and Figure 93)

0: SCLK clock line activated in middle of data bit.

1: SCLK clock line activated at beginning of data bit.

# Bit 0 = LBCL Last bit clock pulse.

This bit allows the user to select whether the clock pulse associated with the last data bit transmitted (MSB) has to be output on the SCLK pin.

- 0: The clock pulse of the last data bit is not output to the SCLK pin.

- 1: The clock pulse of the last data bit is output to the SCLK pin.

**Note:** The last bit is the 8th or 9th data bit transmitted depending on the 8 or 9 bit format selected by the M bit in the SCICR1 register.

# Table 26. SCI clock on SCLK pin

| Data<br>format | M bit | LBCL bit | Number of clock<br>pulses on SCLK |

|----------------|-------|----------|-----------------------------------|

| 8 bit          | 0     | 0        | 7                                 |

| 0 Dit          |       | 1        | 8                                 |

| 9 bit          | 1     | 0        | 8                                 |

| 9 Dit          | I     | 1        | 9                                 |

**Note:** These 3 bits (**CPOL**, **CPHA**, **LBCL**) should not be written while the transmitter is enabled.

#### **10.9.8 Register Description**

10.9.8.1 Control and Status Registers

CAN MASTER CONTROL REGISTER (CMCR) Reset Value: 0000 0010 (02h)

| 7 |      |      |      |      |      |       | 0    |

|---|------|------|------|------|------|-------|------|

| 0 | ABOM | AWUM | NART | RFLM | TXFP | SLEEP | INRQ |

Bit 7 = Reserved, must be kept cleared.

#### Bit 6 = **ABOM** Automatic Bus-Off Management - Read/Set/Clear

This bit controls the behaviour of the CAN hardware on leaving the Bus-Off state.

- 0: The Bus-Off state is left on software request. Refer to Section 0.1.4.5 Error Management, Bus-Off recovery.

- 1: The Bus-Off state is left automatically by hardware once 128 x 11 recessive bits have been monitored.

For detailed information on the Bus-Off state please refer to Section 0.1.4.5 Error Management.

#### Bit 5 = **AWUM** Automatic Wake-Up Mode - Read/Set/Clear

This bit controls the behaviour of the CAN hardware on message reception during sleep mode. 0: The sleep mode is left on software request by

- clearing the SLEEP bit of the CMCR register.

- 1: The sleep mode is left automatically by hardware on CAN message detection. The SLEEP bit of the CMCR register and the SLAK bit of the CMSR register are cleared by hardware.

#### Bit 4 = **NART** No Automatic Retransmission - Read/Set/Clear

- 0: The CAN hardware will automatically retransmit the message until it has been successfully transmitted according to the CAN standard.

- 1: A message will be transmitted only once, independently of the transmission result (successful, error or arbitration lost).

# Bit 3 = **RFLM** Receive FIFO Locked Mode

- Read/Set/Clear

- 0: Receive FIFO not locked on overrun. Once a receive FIFO is full the next incoming message will overwrite the previous one.

- 1: Receive FIFO locked against overrun. Once a receive FIFO is full the next incoming message will be discarded.

# Bit 2 = **TXFP** Transmit FIFO Priority

- Read/Set/Clear

This bit controls the transmission order when several mailboxes are pending at the same time.

- 0: Priority driven by the identifier of the message

- 1: Priority driven by the request order (chronologically)

#### Bit 1 = **SLEEP** Sleep Mode Request - Read/Set/Clear

This bit is set by software to request the CAN hardware to enter the sleep mode. Sleep mode will be entered as soon as the current CAN activity (transmission or reception of a CAN frame) has been completed.

This bit is cleared by software to exit sleep mode.

This bit is cleared by hardware when the AWUM bit is set and a SOF bit is detected on the CAN Rx signal.

# Bit 0 = INRQ Initialization Request

### - Read/Set/Clear

The software clears this bit to switch the hardware into normal mode. Once 11 consecutive recessive bits have been monitored on the Rx signal the CAN hardware is synchronized and ready for transmission and reception. Hardware signals this event by clearing the INAK bit if the CMSR register.

Software sets this bit to request the CAN hardware to enter initialization mode. Once software has set the INRQ bit, the CAN hardware waits until the current CAN activity (transmission or reception) is completed before entering the initialization mode. Hardware signals this event by setting the INAK bit in the CMSR register.

# MAILBOX DATA LENGTH CONTROL REGIS-TER (MDLC)

All bits of this register is write protected when the mailbox is not in empty state.

Read / Write

Reset Value: xxxx xxxx (xxh)

| 7 |   |   |   |      |      |      | 0    |

|---|---|---|---|------|------|------|------|

| 0 | 0 | 0 | 0 | DLC3 | DLC2 | DLC1 | DLC0 |

Bit 7 = Reserved, must be kept cleared.

s. A mes s. obsolete Product(s) - Obsolete(s) - Obsolete(s) - Obsolete(s) - Obsolete(s)

# MAILBOX DATA REGISTERS (MDAR[7:0])

All bits of this register are write protected when the mailbox is not in empty state.

Read / Write **Reset Value: Undefined**

| 7     |       |       |       |       |       |       | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DATA7 | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

Bits 7:0 = **DATA**[7:0] *Data*

A data byte of the message. A message can con-

# 10.9.8.3 CAN Filter Registers

# CAN FILTER CONFIGURATION REG.0 (CFCR0)

All bits of this register are set and cleared by software. Read / Write

Reset Value: 0000 0000 (00h)

| 7 |       |       |       |   |       |       | 0     |

|---|-------|-------|-------|---|-------|-------|-------|

| 0 | FSC11 | FSC10 | FACT1 | 0 | FSC01 | FSC00 | FACT0 |

**Note**: To modify the FFAx and FSCx bits, the be-CAN must be in INIT mode.

Bit 7 = Reserved. Forced to 0 by hardware.

Bits 6:5 = **FSC1[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 1.

Bit 4 = **FACT1** *Filter Active* The software sets this bit to activate Filter 1. To modify the Filter 1 registers (CF1R[7:0]), the FACT1 bit must be cleared. 0: Filter 1 is not active 1: Filter 1 is active

Bit 3 = Reserved. Forced to 0 by hardware.

Bits 2:1 = **FSC0[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 0.

Bit 0 = **FACT0** *Filter Active* The software sets this bit to activate Filter 0. To modify the Filter 0 registers (CF0R[0:7]), the FACT0 bit must be cleared. 0: Filter 0 is not active 1: Filter 0 is active

# **CAN FILTER CONFIGURATION REG.1 (CFCR1)**

All bits of this register are set and cleared by software. Read / Write

Reset Value: 0000 0000 (00h)

| 7 |       |       |       |   |       |       | 0     |  |

|---|-------|-------|-------|---|-------|-------|-------|--|

| 0 | FSC31 | FSC30 | FACT3 | 0 | FSC21 | FSC20 | FACT2 |  |

Bit 7 = Reserved. Forced to 0 by hardware.

Bits 6:5 = **FSC3[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 3.

#### Bit 4 = FACT3 Filter Active

The software sets this bit to activate filter 3. To modify the Filter 3 registers (CF3R[0:7]) the FACT3 bit must be cleared. 0: Filter 3 is not active 1: Filter 3 is active

Bit 3 = Reserved. Forced to 0 by hardware.

Bits 2:1 = **FSC2[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 2.

#### Bit 0 = FACT2 Filter Active

The software sets this bit to activate Filter 2. To modify the Filter 2 registers (CF2R[0:7]), the FACT2 bit must be cleared. 0: Filter 2 is not active

1: Filter 2 is active

57

# Table 32. beCAN Control and Status Page - Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Name | 7     | 6    | 5     | 4     | 3      | 2     | 1      | 0          |

|-------------------|------------------|-------|------|-------|-------|--------|-------|--------|------------|

| 68h               | CMCR             |       | ABOM | AWUM  | NART  | RFLM   | TXFP  | SLEEP  | INRQ       |

| 0011              | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 1      | 0          |

| coh               | CMSR             |       |      | REC   | TRAN  | WKUI   | ERRI  | SLAK   | INAK       |

| 69h               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 1      | 0          |

| CAL               | CTSR             |       |      | TXOK1 | TXOK0 |        |       | RQCP1  | RQCP0      |

| 6Ah               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 0      | <b>C</b> 0 |

|                   | CTPR             |       | LOW1 | LOW0  |       | TME1   | TME0  |        | CODE0      |

| 6Bh               | Reset Value      | 0     | 0    | 0     | 1     | 1      | 1     | 0      | 0          |

| 001               | CRFR             |       |      | RFOM  | FOVR  | FULL   | 0     | FMP1   | FMP0       |

| 6Ch               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 0      | 0          |

|                   | CIER             | WKUIE | 0    | 0     | 0     | FOVIE0 | FFIE0 | FMPIE0 | TMEIE      |

| 6Dh               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 0      | 0          |

| 0.E.h             | CDGR             |       |      |       | 0     | RX     | SAMP  | SILM   | LBKM       |

| 6Eh               | Reset Value      | 0     | 0    | 0     | 0     | 1      | 1     | 0      | 0          |

|                   | CFPSR            |       |      | C     | R -   |        | FPS2  | FPS1   | FPS0       |

| 6Fh               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 0      | 0          |

# Table 33. beCAN Mailbox Pages - Register Map and Reset Values

1C

|   | Address<br>(Hex.) | Register<br>Name | $\langle O \rangle$ | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---|-------------------|------------------|---------------------|--------|--------|--------|--------|--------|--------|--------|

|   | 70h               | MFMI             | FMI7                | FMI6   | FMI5   | FMI4   | FMI3   | FMI2   | FMI1   | FMI0   |

|   | Receive           | Reset Value      | 0                   | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Ī | 70h               | MCSR             |                     |        | TERR   | ALST   | тхок   | RQCP   | ABRQ   | TXRQ   |

|   | Transmit          | Reset Value      | 0                   | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 5 | 0<br>71h          | MDLC             | 0                   |        |        |        | DLC3   | DLC2   | DLC1   | DLC0   |

|   | 71h               | Reset Value      | х                   | х      | х      | х      | x      | х      | х      | х      |

|   | 72h               | MIDR0            |                     | IDE    | RTR    | STID10 | STID9  | STID8  | STID7  | STID6  |

|   |                   | Reset Value      | x                   | x      | x      | х      | х      | х      | х      | x      |

|   | 704               | MIDR1            | STID5               | STID4  | STID3  | STID2  | STID1  | STID0  | EXID17 | EXID16 |

|   | 73h               | Reset Value      | x                   | x      | x      | х      | х      | х      | х      | x      |

|   | 74h               | MIDR2            | EXID15              | EXID14 | EXID13 | EXID12 | EXID11 | EXID10 | EXID9  | EXID8  |

|   | 7411              | Reset Value      | х                   | х      | х      | х      | х      | х      | х      | х      |

|   | 756               | MIDR3            | EXID7               | EXID6  | EXID5  | EXID4  | EXID3  | EXID2  | EXID1  | EXID0  |

|   | 75h               | Reset Value      | x                   | x      | x      | х      | х      | х      | х      | х      |

|   | 76h.7Dh           | MDAR[0:7]        | MDAR7               | MDAR6  | MDAR5  | MDAR4  | MDAR3  | MDAR2  | MDAR1  | MDAR0  |

|   | 76h:7Dh           | Reset Value      | x                   | x      | x      | x      | x      | x      | x      | x      |

207/265

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

# 10.10.6 Register Description

# **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only) Reset Value: 0000 0000 (00h)

| 7   |       |      |      |     |     |     | 0   |

|-----|-------|------|------|-----|-----|-----|-----|

| EOC | SPEED | ADON | SLOW | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by software reading the ADCDRH register or writing to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 =**SPEED** *A/D clock selection* This bit is set and cleared by software.

#### Table 35. A/D Clock Selection

| f <sub>ADC</sub>                                           | SLOW | SPEED |  |

|------------------------------------------------------------|------|-------|--|

| f <sub>CPU</sub> /2                                        | 0    | 0     |  |

| f <sub>CPU</sub> (where f <sub>CPU</sub> <= 4 MHz)         | 0    | 11    |  |

| f <sub>CPU</sub> /4                                        | 1    | 0     |  |

| f <sub>CPU</sub> /2 (same frequency as<br>SLOW=0, SPEED=0) | 15   |       |  |

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **SLOW** A/D Clock Selection This bit is set and cleared by software. It works together with the SPEED bit. Refer to Table 35.

# Bits 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

\*The number of channels is device dependent. Refer to the device pinout description.

| Channel Pin* | СНЗ | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | S D | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

# DATA REGISTER (ADCDRH)

Read Only

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

Bits 7:0 = D[9:2] MSB of Analog Converted Value

# DATA REGISTER (ADCDRL)

Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bits 7:2 = Reserved. Forced by hardware to 0.

Bits 1:0 = D[1:0] LSB of Analog Converted Value

57

Obsolete Product(s) - Obsolete Product(s)

Obsolete Product(s) - Obsolete Product(s)

uctls

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

57