Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, LINbusSCI, SPI                                               |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561k6ta |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| F      | Pin n | 0    |                   |      | Le      | evel   |       |     | P   | ort |     |     | Main                             |                                 |                    |

|--------|-------|------|-------------------|------|---------|--------|-------|-----|-----|-----|-----|-----|----------------------------------|---------------------------------|--------------------|

| P64    | P44   | P32  | Pin Name          | Type | ut      | out    |       | In  | out |     | Out | put | function<br>(after               | function<br>(after              | Alternate function |

| LQFP64 | LQFI  | LQFI |                   |      | Input   | Output | float | ndm | int | ana | OD  | РР  | reset)                           |                                 |                    |

| 54     | 36    | 26   | PD4 / SCI2_RDI    | I/O  | CT      |        | x     |     | ei3 |     | х   | х   | Port D4                          | LINSCI2 Receive Data in-<br>put |                    |

| 55     | 37    | 27   | V <sub>SSA</sub>  | S    |         |        |       |     |     |     |     |     | Analog Ground Voltage            |                                 |                    |

| 56     | 38    | 28   | V <sub>SS_0</sub> | S    |         |        |       |     |     |     |     |     | Digital Ground Voltage           |                                 |                    |

| 57     | 39    | 29   | V <sub>DDA</sub>  | Ι    |         |        |       |     |     |     |     |     | Analog Reference Voltage for ADC |                                 |                    |

| 58     | 40    | 30   | V <sub>DD_0</sub> | S    |         |        |       |     |     |     |     |     | Digital M                        | ain Supply Voltage              |                    |

| 59     | 41    | 31   | PD5 / SCI2_TDO    | I/O  | CT      |        | x     | х   |     |     | х   | х   | Port D5                          | LINSCI2 Transmit Data<br>output |                    |

| 60     | 42    | 32   | RESET             | I/O  | $C_T$   |        |       |     |     |     |     |     | Top prior                        | ity non maskable interrupt.     |                    |

| 61     | 43    | -    | PD6 / AIN10       | I/O  | $C_T$   |        | Х     | е   | i3  | Х   | Х   | Х   | Port D6 ADC Analog Input 10      |                                 |                    |

| 62     | 44    | -    | PD7 / AIN11       | I/O  | $C_T$   |        | Х     |     | ei3 | Х   | Х   | Х   | Port D7 ADC Analog Input 11      |                                 |                    |

| 63     | -     | -    | PF6               | I/O  | $T_T$   |        | Х     | Х   |     |     | Х   | Х   | Port F6                          |                                 |                    |

| 64     | -     | -    | PF7               | I/O  | $T_{T}$ |        | Х     | Х   |     |     | Х   | X   | Port F7                          |                                 |                    |

#### Notes:

1. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

2. Input mode can be used for general purpose I/O, output mode only for CANTX.

3. OSC1 and OSC2 pins connect a crystal/ceramic resonator, or an external source to the on-chip oscillator; see Section 6 and Section 12.5 "CLOCK AND TIMING CHARACTERISTICS" for more details.

4. On the chip, each I/O port has eight pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

| Address                                                                                                                             | Block      | Register<br>Label                                    | Register Name                                                                                                                                                                                                                                                                                                      | Reset<br>Status | Remarks                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------|

| 0068h<br>0069h<br>006Ah<br>006Bh<br>006Ch<br>006Dh<br>006Eh                                                                         |            | CMCR<br>CMSR<br>CTSR<br>CTPR<br>CRFR<br>CIER<br>CDGB | CAN Master Control Register<br>CAN Master Status Register<br>CAN Transmit Status Register<br>CAN Transmit Priority Register<br>CAN Receive FIFO Register<br>CAN Interrupt Enable Register<br>CAN Diagnosis Register                                                                                                |                 | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W                             |

| 006Fh                                                                                                                               |            | CPSR                                                 | CAN Page Selection Register                                                                                                                                                                                                                                                                                        |                 | R/W                                                                |

| 0070h<br>0071h<br>0072h<br>0073h<br>0074h<br>0075h<br>0076h<br>0077h<br>0078h<br>007Ah<br>007Ah<br>007Ah<br>007Ch<br>007Ch<br>007Fh | Active CAN | PAGES                                                | PAGE REGISTER 0<br>PAGE REGISTER 1<br>PAGE REGISTER 2<br>PAGE REGISTER 3<br>PAGE REGISTER 4<br>PAGE REGISTER 5<br>PAGE REGISTER 6<br>PAGE REGISTER 7<br>PAGE REGISTER 7<br>PAGE REGISTER 8<br>PAGE REGISTER 10<br>PAGE REGISTER 11<br>PAGE REGISTER 12<br>PAGE REGISTER 13<br>PAGE REGISTER 14<br>PAGE REGISTER 15 | 00110           | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W |

Legend: x = undefined, R/W = read/write

#### Notes:

1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

C

# INTERRUPTS (Cont'd)

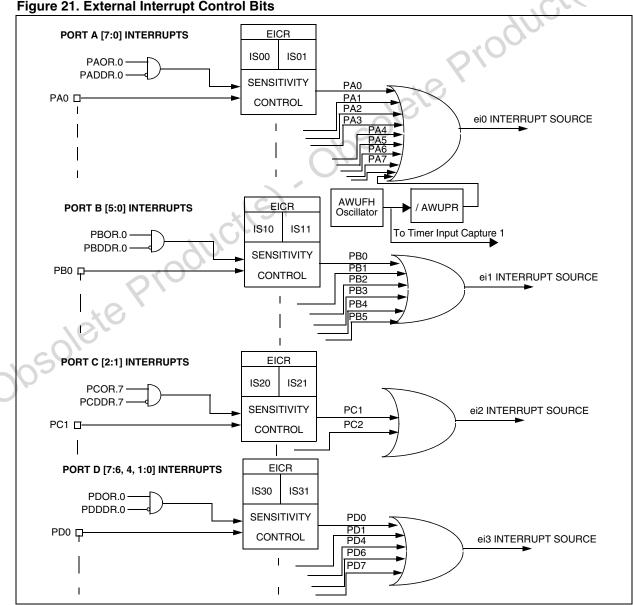

# **7.6 EXTERNAL INTERRUPTS**

## 7.6.1 I/O Port Interrupt Sensitivity

The external interrupt sensitivity is controlled by the ISxx bits in the EICR register (Figure 21). This control allows up to four fully independent external interrupt source sensitivities.

Each external interrupt source can be generated on four (or five) different events on the pin:

- Falling edge

- Rising edge

**لركم**

#### Figure 21. External Interrupt Control Bits

- Falling and rising edge

- Falling edge and low level

To guarantee correct functionality, the sensitivity bits in the EICR register can be modified only when the I1 and I0 bits of the CC register are both set to 1 (level 3). This means that interrupts must be disabled before changing sensitivity.

The pending interrupts are cleared by writing a different value in the ISx[1:0] of the EICR.

# I/O PORTS (Cont'd)

# Table 14. Port Configuration

| Port Pin name |          | Ir             | nput                     | Output       |           |  |

|---------------|----------|----------------|--------------------------|--------------|-----------|--|

| Port          | Pin name | OR = 0         | OR = 1                   | OR = 0       | OR = 1    |  |

|               | PA0      |                | pull-up interrupt (ei0)  |              |           |  |

|               | PA1      |                | floating interrupt (ei0) |              |           |  |

|               | PA2      |                | pull-up interrupt (ei0)  |              |           |  |

| Port A        | PA3      | floating       | floating interrupt (ei0) | open drain   |           |  |

| POILA         | PA4      | noating        | pull-up interrupt (ei0)  | open drain   | push-pull |  |

|               | PA5      |                | floating interrupt (ei0) |              |           |  |

|               | PA6      |                | pull-up interrupt (ei0)  |              |           |  |

|               | PA7      |                | floating interrupt (ei0) |              | (5)       |  |

|               | PB0      |                | pull-up interrupt (ei1)  |              | <u> </u>  |  |

|               | PB1      |                | floating interrupt (ei1) |              |           |  |

|               | PB2      | floating       | pull-up interrupt (ei1)  | open drain   |           |  |

| Port B        | PB3      | floating       | floating interrupt (ei1) |              | push-pull |  |

|               | PB4      |                | pull-up interrupt (ei1)  |              |           |  |

|               | PB5      |                | floating interrupt (ei1) | 0            |           |  |

|               | PC0      |                | pull-up                  | (0)          |           |  |

|               | PC1      | fleeting       | pull-up interrupt (ei2)  | opon drain   |           |  |

| Port C        | PC2      | floating       | floating interrupt (ei2) | open drain   | push-pull |  |

| PontC         | PC3      |                | pull-up                  |              |           |  |

|               | PC4      | pı             | ull-up                   | controlled b | y CANTX * |  |

|               | PC7:5    | floating       | pull-up                  | open drain   | push-pull |  |

|               | PD0      |                | pull-up interrupt (ei3)  |              |           |  |

|               | PD1      | 16             | floating interrupt (ei3) |              |           |  |

|               | PD3:2    |                | pull-up                  |              |           |  |

| Port D        | PD4      | floating       | floating interrupt (ei3) | open drain   | push-pull |  |

|               | PD5      | $\mathcal{O}$  | pull-up                  |              |           |  |

|               | PD6      |                | pull-up interrupt (ei3)  |              |           |  |

|               | PD7      |                | floating interrupt (ei3) |              |           |  |

| Port E        | PE7:0    | floating (TTL) | pull-up (TTL)            | open drain   | push-pull |  |

| Port F        | PF7:0    | floating (TTL) | pull-up (TTL)            | open drain   | push-pull |  |

\* Note: When the CANTX alternate function is selected, the I/O port operates in output push-pull mode.

57

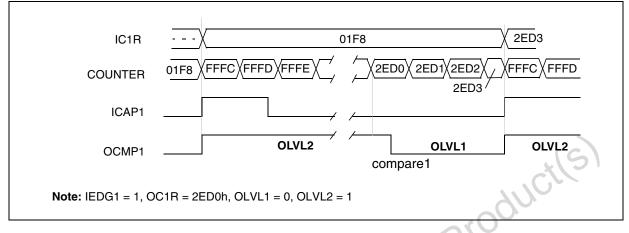

# 16-BIT TIMER (Cont'd)

**Note:** On timers with only one Output Compare register, a fixed frequency PWM signal can be generated using the output compare and the counter overflow to define the pulse length.

1 C

# 16-BIT TIMER (Cont'd) CONTROL REGISTER 2 (CR2)

# Read/Write

Reset Value: 0000 0000 (00h)

| 1    |      |     |     |     |     |       | 0     |

|------|------|-----|-----|-----|-----|-------|-------|

| OC1E | OC2E | OPM | PWM | CC1 | CC0 | IEDG2 | EXEDG |

# Bit 7 = **OC1E** *Output Compare 1 Pin Enable.*

This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode). Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.

- 0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP1 pin alternate function enabled.

#### Bit 6 = **OC2E** Output Compare 2 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.

- 0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP2 pin alternate function enabled.

# Bit 5 = **OPM** One Pulse Mode.

0: One Pulse mode is not active.

1: One Pulse mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.

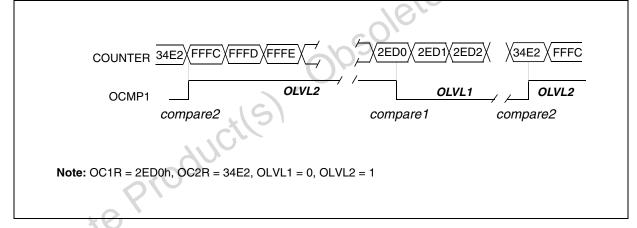

#### Bit 4 = **PWM** *Pulse Width Modulation.*

- 0: PWM mode is not active.

- 1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.

## Bit 3, 2 = **CC[1:0]** *Clock Control.*

The timer clock mode depends on these bits:

#### Table 18. Clock Control Bits

| Timer Clock                      | CC1 | CC0 |

|----------------------------------|-----|-----|

| f <sub>CPU</sub> / 4             | 0   | 0   |

| f <sub>CPU</sub> / 2             |     | 1   |

| f <sub>CPU</sub> / 8             | 1   | 0   |

| External Clock (where available) | 1   | 1   |

**Note**: If the external clock pin is not available, programming the external clock configuration stops the counter.

## Bit 1 = IEDG2 Input Edge 2.

This bit determines which type of level transition on the ICAP2 pin will trigger the capture. 0: A falling edge triggers the capture. 1: A rising edge triggers the capture.

#### Bit 0 = **EXEDG** External Clock Edge.

This bit determines which type of level transition on the external clock pin EXTCLK will trigger the counter register.

0: A falling edge triggers the counter register. 1: A rising edge triggers the counter register.

# 8-BIT TIMER (Cont'd)

# 10.5.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 8-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                       |

|      | 8-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                            |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                             |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequently, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

# 10.5.5 Interrupts

| Interrupt Event                                    |     | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------------|-----|---------------|--------------------------|----------------------|----------------------|

| Input Capture 1 event/Counter reset in PWM mode    |     | ICF1          | ICIE                     |                      |                      |

| Input Capture 2 event                              | . ( | ICF2          | ICIE                     |                      |                      |

| Output Compare 1 event (not available in PWM mode) | 101 | OCF1          | OCIE                     | Yes                  | No                   |

| Output Compare 2 event (not available in PWM mode) |     | OCF2          | OCIE                     |                      |                      |

| Timer Overflow event                               | S   | TOF           | TOIE                     |                      |                      |

**Note:** The 8-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# 10.5.6 Summary of Timer modes

| MODES                       | AVAILABLE RESOURCES |                               |                  |                         |  |  |  |  |

|-----------------------------|---------------------|-------------------------------|------------------|-------------------------|--|--|--|--|

| MODES                       | Input Capture 1     | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |  |  |  |

| Input Capture (1 and/or 2)  | Yes                 | Yes                           | Yes              | Yes                     |  |  |  |  |

| Output Compare (1 and/or 2) | 165                 | 165                           | 165              | 103                     |  |  |  |  |

| One Pulse Mode              | No                  | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |  |  |  |

| PWM Mode                    | NO                  | Not Recommended <sup>3)</sup> | NO               | No                      |  |  |  |  |

1) See note 4 in "One Pulse Mode" on page 100

2) See note 5 in "One Pulse Mode" on page 100

3) See note 4 in "Pulse Width Modulation Mode" on page 102

# 10.7 LINSCI SERIAL COMMUNICATION INTERFACE (LIN MASTER/SLAVE)

## 10.7.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

The LIN-dedicated features support the LIN (Local Interconnect Network) protocol for both master and slave nodes.

This chapter is divided into SCI Mode and LIN mode sections. For information on general SCI communications, refer to the SCI mode section. For LIN applications, refer to both the SCI mode and LIN mode sections.

# 10.7.2 SCI Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- 2 receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Overrun, Noise and Frame error detection

- 6 interrupt sources

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error

- Parity interrupt

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

## 10.7.3 LIN Features

- LIN Master

- 13-bit LIN Synch Break generation

- LIN Slave

- Automatic Header Handling

- Automatic baud rate resynchronization based on recognition and measurement of the LIN Synch Field (for LIN slave nodes)

- Automatic baud rate adjustment (at CPU frequency precision)

- 11-bit LIN Synch Break detection capability

- LIN Parity check on the LIN Identifier Field (only in reception)

- LIN Error management

- LIN Header Timeout

- Hot plugging support

## LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

†<sub>CPU</sub>

(16\*PR)\*RR

#### 10.7.5.4 Conventional Baud Rate Generation

The baud rates for the receiver and transmitter (Rx and Tx) are set independently and calculated as follows:

$Tx = \frac{f_{CPU}}{(16 \cdot PR) \cdot TR} \qquad Rx = -\frac{f_{CPU}}{(16 \cdot PR) \cdot TR}$

with:

PR = 1, 3, 4 or 13 (see SCP[1:0] bits)

TR = 1, 2, 4, 8, 16, 32, 64,128

(see SCT[2:0] bits)

RR = 1, 2, 4, 8, 16, 32, 64,128

(see SCR[2:0] bits)

All these bits are in the SCIBRR register.

obsolete Product(s)

**Example:** If  $f_{CPU}$  is 8 MHz (normal mode) and if PR = 13 and TR = RR = 1, the transmit and receive baud rates are 38400 baud.

**Note:** The baud rate registers MUST NOT be changed while the transmitter or the receiver is enabled.

#### 10.7.5.5 Extended Baud Rate Generation

The extended prescaler option gives a very fine tuning on the baud rate, using a 255 value prescaler, whereas the conventional Baud Rate Generator retains industry standard software compatibility.

The extended baud rate generator block diagram is described in Figure 3.

The output clock rate sent to the transmitter or to the receiver will be the output from the 16 divider divided by a factor ranging from 1 to 255 set in the SCIERPR or the SCIETPR register.

**Note:** The extended prescaler is activated by setting the SCIETPR or SCIERPR register to a value other than zero. The baud rates are calculated as follows:

$$Tx = \frac{f_{CPU}}{16 \times ETPR^{*}(PR^{*}TR)} Rx = \frac{f_{CPU}}{16 \times ERPR^{*}(PR^{*}RR)}$$

with:

ETPR = 1, ..., 255 (see SCIETPR register) ERPR = 1, ..., 255 (see SCIERPR register)

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd) CONTROL REGISTER 1 (SCICR1)

Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

Bit 7 = R8 Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

#### Bit 6 = T8 Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software. 0: SCI enabled

1: SCI prescaler and outputs disabled

Bit 4 = M Word length.

This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

## Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line

1: Address Mark

## Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

# Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

## Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software. 0: Parity error interrupt disabled

1: Parity error interrupt enabled

10501

# beCAN CONTROLLER (Cont'd)

#### Side-effect of Workround 1

Because the while loop lasts 10 CPU cycles, at high baud rate, it is possible to miss a dominant state on the bus if it lasts just one CAN bit time and the bus speed is high enough (see Table 1).

# Table 29. While Loop Timing

| f <sub>CPU</sub> | Software<br>timing:   | Minimum baud rate for possible missed |  |  |

|------------------|-----------------------|---------------------------------------|--|--|

| 8 MHz            | While loop<br>1.25 µs | dominant bit<br>800 Kbaud             |  |  |

| 4 MHz            | 2.5 µs                | 400 Kbaud                             |  |  |

| f <sub>CPU</sub> | 10/f <sub>CPU</sub>   | f <sub>CPU</sub> /10                  |  |  |

If this happens, we will continue waiting in the while loop instead of releasing the FIFO immediately. The workaround is still valid because we will not release the FIFO during the critical period. But the application may lose additional time waiting in the while loop as we are no longer able to guarantee a maximum of 6 CAN bit times spent in the workaround.

In this particular case the time the application can spend in the workaround may increase up to a full CAN frame, depending of the frame contents. This

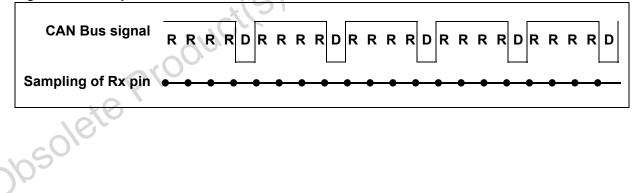

Figure 113. Reception at Maximum CAN Baud Rate

case is very rare but happens when a specific sequence is present on in the CAN frame.

The example in Figure 20 shows reception at maximum CAN baud rate: In this case  $t_{CAN}$  is  $8/f_{CPU}$  and the sampling time is  $10/f_{CPU}$ .

If the application is using the maximum baud rate and the possible delay caused by the workaround is not acceptable, there is another workaround which reduces the Rx pin sampling time.

Workaround 2 (see Figure 21) first tests that FMP = 2 and the CAN cell is receiving, if not the FIFO can be released immediately. If yes, the program goes through a sequence of test instructions on the RX pin that last longer than the time between the acknowledge dominant bit and the critical time slot. If the Rx pin is in recessive state for more than 8 CAN bit times, it means we are now after the acknowledge and the critical slot. If a dominant bit is read on the bus, we can release the FIFO immediately. This workaround has to be written in assembly language to avoid the compiler optimizing the test sequence.

The implementation shown here is for the CAN bus maximum speed (1 Mbaud @ 8 MHz CPU clock).

# beCAN CONTROLLER (Cont'd)

# CAN FILTER MODE REGISTER (CFMR1)

All bits of this register are set and cleared by software.

Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |      |      |      | 0    |

|---|---|---|---|------|------|------|------|

| 0 | 0 | 0 | 0 | FMH5 | FML5 | FMH4 | FML4 |

Bits 7:4 = Reserved. Forced to 0 by hardware.

#### Bit 3 = FMH5 Filter Mode High

Mode of the high registers of Filter 5. 0: High registers are in mask mode 1: High registers are in identifier list mode

Bit 2 = **FML5** *Filter Mode Low* Mode of the low registers of filter 5. 0: Low registers are in mask mode 1: Low registers are in identifier list mode

Bit 1 = FMH4 Filter Mode High

Mode of the high registers of filter 4.

0: High registers are in mask mode

1: High registers are in identifier list mode

Bit 0 = **FML4** *Filter Mode Low* Mode of the low registers of filter 4. 0: Low registers are in mask mode 1: Low registers are in identifier list mode

# FILTER x REGISTER[7:0] (CFxR[7:0])

Read / Write

Reset Value: Undefined

| 1   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| FB7 | FB6 | FB5 | FB4 | FB3 | FB2 | FB1 | FB0 |

#### In all configurations:

Bits 7:0 = FB[7:0] Filter Bits

#### Identifier

Each bit of the register specifies the level of the corresponding bit of the expected identifier.

0: Dominant bit is expected

1: Recessive bit is expected

#### Mask

Each bit of the register specifies whether the bit of the associated identifier register must match with the corresponding bit of the expected identifier or not.

0: Don't care, the bit is not used for the comparison

1: Must match, the bit of the incoming identifier must have the same level has specified in the corresponding identifier register of the filter.

**Note:** Each filter x is composed of 8 registers, CFxR[7:0]. Depending on the scale and mode configuration of the filter the function of each register can differ. For the filter mapping, functions description and mask registers association, refer to Section 0.1.4.3 Identifier Filtering.

A Mask/Identifier register in **mask mode** has the same bit mapping as in **identifier list** mode.

**Note**: To modify these registers, the corresponding FACT bit in the CFCR register must be cleared.

)psolete

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

## 10.10.6 Register Description

# **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only) Reset Value: 0000 0000 (00h)

| 7   |       |      |      |     |     |     | 0   |

|-----|-------|------|------|-----|-----|-----|-----|

| EOC | SPEED | ADON | SLOW | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by software reading the ADCDRH register or writing to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 =**SPEED** *A/D clock selection* This bit is set and cleared by software.

#### Table 35. A/D Clock Selection

| f <sub>ADC</sub>                                           | SLOW | SPEED |  |

|------------------------------------------------------------|------|-------|--|

| f <sub>CPU</sub> /2                                        | 0    | 0     |  |

| f <sub>CPU</sub> (where f <sub>CPU</sub> <= 4 MHz)         | 0    | 11    |  |

| f <sub>CPU</sub> /4                                        | 1    | 0     |  |

| f <sub>CPU</sub> /2 (same frequency as<br>SLOW=0, SPEED=0) | 15   |       |  |

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **SLOW** A/D Clock Selection This bit is set and cleared by software. It works together with the SPEED bit. Refer to Table 35.

# Bits 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

\*The number of channels is device dependent. Refer to the device pinout description.

| Channel Pin* | СНЗ | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | SU) | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

# DATA REGISTER (ADCDRH)

Read Only

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

Bits 7:0 = D[9:2] MSB of Analog Converted Value

## DATA REGISTER (ADCDRL)

Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bits 7:2 = Reserved. Forced by hardware to 0.

Bits 1:0 = D[1:0] LSB of Analog Converted Value

57

# **INSTRUCTION SET OVERVIEW** (Cont'd)

# **11.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| LD   | CLR                                                                           |                                                                  |                                                                                              |                                                                                                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

|------|-------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUSH | POP                                                                           | RSP                                                              |                                                                                              |                                                                                                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

| INC  | DEC                                                                           |                                                                  |                                                                                              |                                                                                                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

| CP   | TNZ                                                                           | BCP                                                              |                                                                                              |                                                                                                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

| AND  | OR                                                                            | XOR                                                              | CPL                                                                                          | NEG                                                                                                         |                                                                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\sum$                                                                                                                                                          |

| BSET | BRES                                                                          |                                                                  |                                                                                              |                                                                                                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

| BTJT | BTJF                                                                          |                                                                  |                                                                                              |                                                                                                             | 21/                                                                                                                                 | J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                 |

| ADC  | ADD                                                                           | SUB                                                              | SBC                                                                                          | MUL                                                                                                         | 0,0                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

| SLL  | SRL                                                                           | SRA                                                              | RLC                                                                                          | RRC                                                                                                         | SWAP                                                                                                                                | SLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                 |

| JRA  | JRT                                                                           | JRF                                                              | JP                                                                                           | CALL                                                                                                        | CALLR                                                                                                                               | NOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RET                                                                                                                                                             |

| JRxx |                                                                               |                                                                  | 0.1                                                                                          |                                                                                                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

| TRAP | WFI                                                                           | HALT                                                             | IRET                                                                                         |                                                                                                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

| SIM  | RIM                                                                           | SCF                                                              | RCF                                                                                          |                                                                                                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |

|      | PUSH<br>INC<br>CP<br>AND<br>BSET<br>BTJT<br>ADC<br>SLL<br>JRA<br>JRXX<br>TRAP | PUSHPOPINCDECCPTNZANDORBSETBRESBTJTBTJFADCADDSLLSRLJRAJRTJRAPWFI | PUSHPOPRSPINCDECINCDECCPTNZBCPANDORXORBSETBRESBTJTBTJFADCADDSUBSLLSRLSRAJRAJRTJRFTRAPWFIHALT | PUSHPOPRSPINCDECIINCDECICPTNZBCPANDORXORCPLBSETBRESIBTJTBTJFIADCADDSUBSBCSLLSRLSRARLCJRAXIIITRAPWFIHALTIRET | PUSHPOPRSPIINCDECIIINCDECIICPTNZBCPIANDORXORCPLNEGBSETBRESIIBTJTBTJFIIADCADDSUBSBCMULSLLSRLSRARLCRRCJRAJRTJRFJPCALLTRAPWFIHALTIRETI | PUSHPOPRSPImage: Constraint of the sector o | PUSHPOPRSPIIIINCDECIIIIINCDECIIIICPTNZBCPIIIANDORXORCPLNEGIIBSETBRESIIIIBTJTBTJFIIIIADCADDSUBSBCMULISLLSRLSRARLCRRCSWAPJRAJRTJRFJPCALLCALLRNOPJRAPWFIHALTIRETII |

## Using a prebyte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

PC-2 End of previous instruction

PC-1

PC

Prebyte Opcode

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

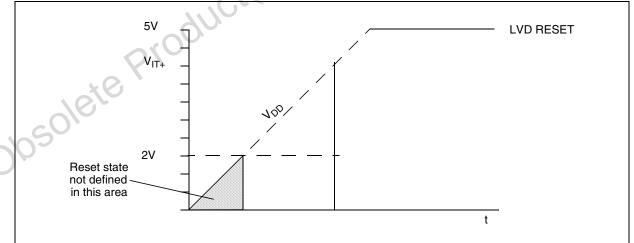

# 12.3.2 Operating Conditions with Low Voltage Detector (LVD)

Subject to general operating conditions for T<sub>A</sub>.

| Symbol                | Parameter                                               | Conditions                                   | Min               | Тур | Max                | Unit |

|-----------------------|---------------------------------------------------------|----------------------------------------------|-------------------|-----|--------------------|------|

| V <sub>IT+(LVD)</sub> | Reset release threshold (V <sub>DD</sub> rise)          |                                              | 4.0 <sup>1)</sup> | 4.2 | 4.5                | V    |

| V <sub>IT-(LVD)</sub> | Reset generation threshold ( $V_{DD}$ fall)             |                                              | 3.8               | 4.0 | 4.25 <sup>1)</sup> | v    |

| V <sub>hys(LVD)</sub> | LVD voltage threshold hysteresis <sup>1)</sup>          | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub> | 150               | 200 | 250                | mV   |

| \/+                   | V <sub>DD</sub> rise time rate <sup>1)</sup>            |                                              | 6                 |     |                    | μs/V |

| Vt <sub>POR</sub>     | VDD lise lille late /                                   |                                              |                   |     | 100                | ms/V |

| t <sub>g(VDD)</sub>   | $V_{DD}$ glitches filtered (not detected) by $LVD^{1)}$ | Measured at $V_{\text{IT-(LVD)}}$            |                   |     | 40                 | ns   |

# 12.3.3 Auxiliary Voltage Detector (AVD) Thresholds

| g(vbb)                                                                                                                    | LVD'                                                                           | 11-(EVD)                                     |                   |     |                    |      |  |  |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------|-------------------|-----|--------------------|------|--|--|

| Notes:<br>1. Data based on characterization results, not tested in production.                                            |                                                                                |                                              |                   |     |                    |      |  |  |

| <b>12.3.3 Auxiliary Voltage Detector (AVD) Thresholds</b><br>Subject to general operating conditions for T <sub>A</sub> . |                                                                                |                                              |                   |     |                    |      |  |  |