Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | CANbus, LINbusSCI, SPI                                                |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 6x10b                                                             |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561k6tae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

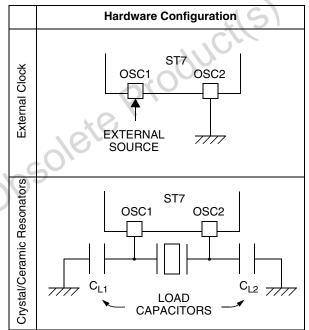

### 6.2 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by two different source types coming from the multioscillator block:

- an external source

- a crystal or ceramic resonator oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configuration are shown in Table 6. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effect Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (> 16 MHz), putting the ST7 in an unsafe/undefined state. The product behavior must therefore be considered undefined when the OSC pins are left unconnected.

### **External Clock Source**

In external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

### Crystal/Ceramic Oscillators

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of five oscillators with different frequency ranges must be done by option byte in order to reduce consumption (refer to Section 14.1 on page 252 for more details on the frequency ranges). The resonator and the load capacitors must be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

### Table 6. ST7 Clock Sources

)bsole

### INTERRUPTS (Cont'd)

### **Table 9. Interrupt Mapping**

| N° | Source<br>Block | Description                                          | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT <sup>1)</sup> | Address<br>Vector |

|----|-----------------|------------------------------------------------------|-------------------|-------------------|------------------------------------|-------------------|

|    | RESET           | Reset                                                | N/A               |                   | yes                                | FFFEh-FFFFh       |

|    | TRAP            | Software interrupt                                   | IN/A              |                   | no                                 | FFFCh-FFFDh       |

| 0  | TLI             | External top level interrupt                         | EICR              | Highest           | yes                                | FFFAh-FFFBh       |

| 1  | MCC/RTC         | Main clock controller time base interrupt            | MCCSR             | Priority          | yes                                | FFF8h-FFF9h       |

| 2  | ei0/AWUFH       | External interrupt ei0/ Auto wake-up from Halt       | EICR/<br>AWUCSR   |                   |                                    | FFF6h-FFF7h       |

| 3  | ei1/AVD         | External interrupt ei1/Auxiliary Voltage Detector    | EICR/<br>SICSR    |                   | yes <sup>2)</sup>                  | FFF4h-FFF5h       |

| 4  | ei2             | External interrupt ei2                               | EICR              |                   | 0.                                 | FFF2h-FFF3h       |

| 5  | ei3             | External interrupt ei3                               | EICR              |                   |                                    | FFF0h-FFF1h       |

| 6  | CAN             | CAN peripheral interrupt - RX                        | CIER              |                   | no                                 | FFEEh-FFEFh       |

| 7  | CAN             | CAN peripheral interrupt - TX / ER / SC              | CIER              |                   | yes <sup>3)</sup>                  | FFECh-FFEDh       |

| 8  | SPI             | SPI peripheral interrupts                            | SPICSR            |                   | yes                                | FFEAh-FFEBh       |

| 9  | TIMER8          | 8-bit TIMER peripheral interrupts                    | T8_TCR1           |                   | no                                 | FFE8h-FFE9h       |

| 10 | TIMER16         | 16-bit TIMER peripheral interrupts                   | TCR1              |                   | no                                 | FFE6h-FFE7h       |

| 11 | LINSCI2         | LINSCI2 Peripheral interrupts                        | SCI2CR1           |                   | no                                 | FFE4h-FFE5h       |

| 12 | LINSCI1         | LINSCI1 Peripheral interrupts (LIN Master/<br>Slave) | SCI1CR1           | ↓<br>Lowest       | no <sup>4)</sup>                   | FFE2h-FFE3h       |

| 13 | PWM ART         | 8-bit PWM ART interrupts                             | PWMCR             | Priority          | yes                                | FFE0h-FFE1h       |

Notes:

1050'

1. Valid for HALT and ACTIVE HALT modes except for the MCC/RTC interrupt source which exits from ACTIVE HALT mode only. .....

2. Except AVD interrupt

3. Exit from Halt only when a wake-up condition is detected, generating a Status Change interrupt. See Section 10.8.6 on page 160.

4. It is possible to exit from Halt using the external interrupt which is mapped on the RDI pin.

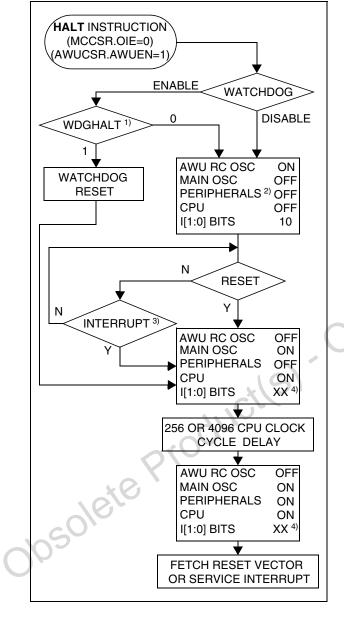

### POWER SAVING MODES (Cont'd)

### Figure 31. AWUFH Mode Flow-chart

#### Notes:

**1.** WDGHALT is an option bit. See option byte section for more details.

**2.** Peripheral clocked with an external clock source can still be active.

**3.** Only an AWUFH interrupt and some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 34 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

### **ON-CHIP PERIPHERALS** (Cont'd)

### **10.3.3 Register Description**

### CONTROL / STATUS REGISTER (ARTCSR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |     |     |     |     |      |     | 0   |  |

|------|-----|-----|-----|-----|------|-----|-----|--|

| EXCL | CC2 | CC1 | CC0 | TCE | FCRL | OIE | OVF |  |

### Bit 7 = **EXCL** External Clock

This bit is set and cleared by software. It selects the input clock for the 7-bit prescaler.

0: CPU clock. 1: External clock.

Bit 6:4 = **CC[2:0]** Counter Clock Control These bits are set and cleared by software. They determine the prescaler division ratio from  $f_{INPUT}$ .

| <b>f</b> COUNTER         | With f <sub>INPUT</sub> =8 MHz | CC2 | CC1 | CC0 |

|--------------------------|--------------------------------|-----|-----|-----|

| f <sub>INPUT</sub>       | 8 MHz                          | 0   | 0   | 0   |

| f <sub>INPUT</sub> / 2   | 4 MHz                          | 0   | 0   | 1   |

| f <sub>INPUT</sub> / 4   | 2 MHz                          | 0   | 1   | 0   |

| f <sub>INPUT</sub> / 8   | 1 MHz                          | 0   | 1   | 1   |

| f <sub>INPUT</sub> / 16  | 500 kHz                        | 1   | 0   | 0   |

| f <sub>INPUT</sub> / 32  | 250 kHz                        | 1   | 0   | 1   |

| f <sub>INPUT</sub> / 64  | 125 kHz                        | 1   | 1   | 0   |

| f <sub>INPUT</sub> / 128 | 62.5 kHz                       | 1   | 1   | 1   |

### Bit 3 = **TCE** *Timer Counter Enable*

This bit is set and cleared by software. It puts the timer in the lowest power consumption mode. 0: Counter stopped (prescaler and counter frozen).

1: Counter running.

### Bit 2 = **FCRL** Force Counter Re-Load

This bit is write-only and any attempt to read it will yield a logical zero. When set, it causes the contents of ARTARR register to be loaded into the counter, and the content of the prescaler register to be cleared in order to initialize the timer before starting to count.

### Bit 1 = **OIE** Overflow Interrupt Enable

This bit is set and cleared by software. It allows to enable/disable the interrupt which is generated when the OVF bit is set.

0: Overflow Interrupt disable.

1: Overflow Interrupt enable.

### Bit 0 = **OVF** Overflow Flag

This bit is set by hardware and cleared by software reading the ARTCSR register. It indicates the transition of the counter from FFh to the ARTARR value.

#### 0: New transition not yet reached 1: Transition reached

### COUNTER ACCESS REGISTER (ARTCAR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CA7 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 |

Bit 7:0 = CA[7:0] Counter Access Data

These bits can be set and cleared either by hardware or by software. The ARTCAR register is used to read or write the auto-reload counter "on the fly" (while it is counting).

## AUTO-RELOAD REGISTER (ARTARR)

### Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| AR7 | AR6 | AR5 | AR4 | AR3 | AR2 | AR1 | AR0 |

### Bit 7:0 = AR[7:0] Counter Auto-Reload Data

These bits are set and cleared by software. They are used to hold the auto-reload value which is automatically loaded in the counter when an overflow occurs. At the same time, the PWM output levels are changed according to the corresponding OPx bit in the PWMCR register.

This register has two PWM management functions:

- Adjusting the PWM frequency

- Setting the PWM duty cycle resolution

### PWM Frequency vs Resolution:

|            | Resolution | f <sub>P\</sub> | мм        |  |

|------------|------------|-----------------|-----------|--|

| value      | Resolution | Min             | Max       |  |

| 0          | 8-bit      | ~0.244 kHz      | 31.25 kHz |  |

| [ 0127 ]   | > 7-bit    | ~0.244 kHz      | 62.5 kHz  |  |

| [ 128191 ] | > 6-bit    | ~0.488 kHz      | 125 kHz   |  |

| [ 192223 ] | > 5-bit    | ~0.977 kHz      | 250 kHz   |  |

| [ 224239 ] | > 4-bit    | ~1.953 kHz      | 500 kHz   |  |

### 16-BIT TIMER (Cont'd)

#### 10.4.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are two output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC*i*E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

### Procedure:

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OC*i*R register and CR register:

OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \text{ OC}_{i}\text{R} = \frac{\Delta t * f_{CPU}}{\text{PRESC}}$$

Where:

1

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 17 Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC} i \mathbb{R} = \Delta t * f_{\text{EXT}}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OCiLR register (enables the output compare function and clears the OCF*i* bit).

57/

### 8-BIT TIMER (Cont'd)

### 10.5.7 Register Description

Each Timer is associated with three control and status registers, and with six data registers (8-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

### **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = **ICIE** *Input Capture Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

### Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.* 0: Interrupt is inhibited.

Josolete P

**لرك**ا

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

#### Bit 4 = FOLV2 Forced Output Compare 2.

- This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

Bit 3 = FOLV1 Forced Output Compare 1.

- This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

### Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode.

### Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture. 0: A falling edge triggers the capture. 1: A rising edge triggers the capture.

### Bit 0 = OLVL1 Output Level 1.

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

105/265

### **ON-CHIP PERIPHERALS** (cont'd)

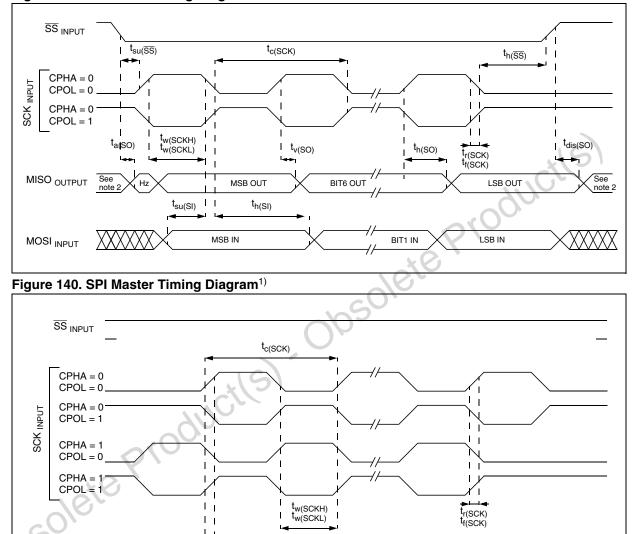

### **10.6 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 10.6.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 10.6.2 Main Features

- Full duplex synchronous transfers (on three lines)

- Simplex synchronous transfers (on two lines)

- Master or slave operation

- 6 master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

Note: In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

### **10.6.3 General Description**

Figure 70 on page 110 shows the serial peripheral interface (SPI) block diagram. There are three registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through four pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

### LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

### **CONTROL REGISTER 2 (SCICR2)**

Read/Write Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |                   | 0                 |

|-----|------|-----|------|----|----|-------------------|-------------------|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU <sup>1)</sup> | SBK <sup>1)</sup> |

<sup>1)</sup>This bit has a different function in LIN mode, please refer to the LIN mode register description.

Bit 7 = **TIE** *Transmitter interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: In SCI interrupt is generated whenever TDRE = 1 in the SCISR register

Bit 6 = **TCIE** *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC = 1 in the SCISR register

Bit 5 = **RIE** *Receiver interrupt enable*

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR = 1 or RDRF = 1 in the SCISR register

Bit 4 = ILIE Idle line interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE = 1 in the SCISR register.

Bit 3 = **TE** Transmitter enable

This bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

### Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

### Bit 2 = **RE** *Receiver enable*

This bit enables the receiver. It is set and cleared by software.

0: Receiver is disabled in the SCISR register

1: Receiver is enabled and begins searching for a start bit

### Bit 1 = RWU Receiver wake-up

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in active mode

- 1: Receiver in mute mode

### Notes:

- Before selecting Mute mode (by setting the RWU bit) the SCI must first receive a data byte, otherwise it cannot function in Mute mode with wakeup by Idle line detection.

- In Address Mark Detection Wake-Up configuration (WAKE bit = 1) the RWU bit cannot be modified by software while the RDRF bit is set.

### Bit 0 = SBK Send break

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter will send a BREAK word at the end of the current word.

### DATA REGISTER (SCIDR)

Read/Write

Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

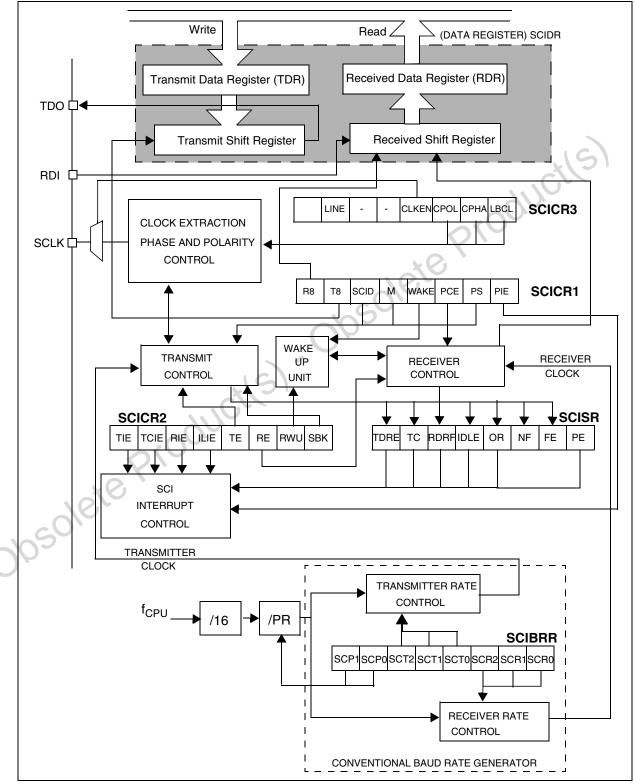

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 1).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 1).

<u>ل</u>رک

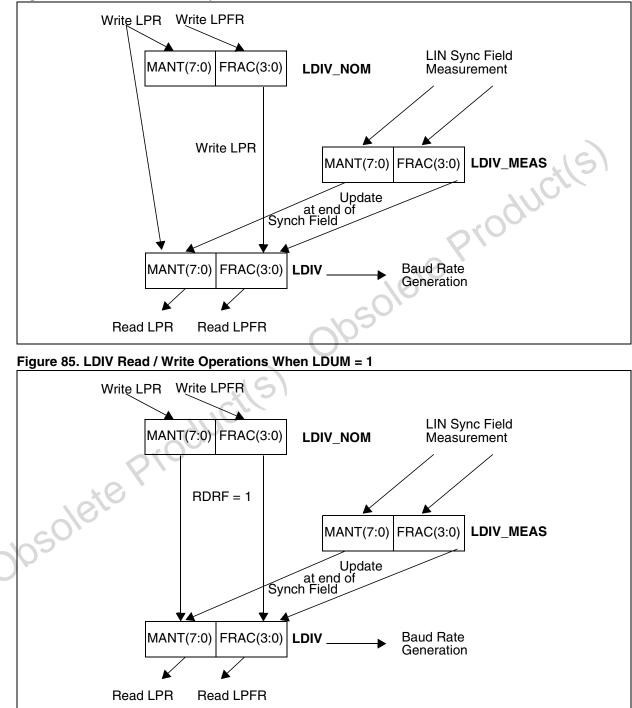

### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

LIN PRESCALER FRACTION REGISTER (LPFR)

### Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |           |           |           | 0         |

|---|---|---|---|-----------|-----------|-----------|-----------|

| 0 | 0 | 0 | 0 | LPFR<br>3 | LPFR<br>2 | LPFR<br>1 | LPFR<br>0 |

Bits 7:4 = Reserved.

### Bits 3:0 = LPFR[3:0] Fraction of LDIV

These 4 bits define the fraction of the LIN Divider (LDIV):

| LPFR[3:0] | Fraction (LDIV) |

|-----------|-----------------|

| 0h        | 0               |

| 1h        | 1/16            |

|           |                 |

| Eh        | 14/16           |

| Fh        | 15/16           |

1. When initializing LDIV, the LPFR register must be written first. Then, the write to the LPR register will effectively update LDIV and so the clock generation.

2. In LIN Slave mode, if the LPR[7:0] register is equal to 00h, the transceiver and receiver input clocks are switched off.

### Examples of LDIV coding:

Example 1: LPR = 27d and LPFR = 12d

This leads to:

Mantissa (LDIV) = 27d

Fraction (LDIV) = 12/16 = 0.75dTherefore LDIV = 27.75d

Example 2: LDIV = 25.62dThis leads to: LPFR = rounded(16\*0.62d) = rounded(9.92d) = 10d = Ah LPR = mantissa (25.620d) = 25d = 1Bh

Example 3: LDIV = 25.99d This leads to: LPFR = rounded(16\*0.99d) = rounded(15.84d) = 16d

### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

### Figure 88. SCI Block Diagram

### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

### **10.8.4 Functional Description**

The block diagram of the Serial Control Interface, is shown in Figure 88 on page 153. It contains seven dedicated registers:

- Three control registers (SCICR1, SCICR2 and SCICR3)

- A status register (SCISR)

**47/**

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 10.7.8 for the definitions of each bit.

### 10.8.4.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 89).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

|   | 9.                        | bit W                                       | /ord le | enath  | (M bit | is set | t)     |                           |                 | \ C                    | 10           |                 | 1                           |

|---|---------------------------|---------------------------------------------|---------|--------|--------|--------|--------|---------------------------|-----------------|------------------------|--------------|-----------------|-----------------------------|

|   |                           | 9-bit Word length (M bit is set) Data Frame |         |        |        |        |        | Possible<br>Parity<br>Bit |                 |                        |              | Next Data Frame |                             |

|   |                           | Start<br>Bit                                | Bit0    | Bit1   | Bit2   | Bit3   | Bit4   | Bit5                      | Bit6            | Bit7                   | Bit8         | Stop<br>Bit     | Start<br>Bit                |

|   | CLOCK                     |                                             |         |        |        |        | 3      |                           |                 |                        | **  <br>L    |                 |                             |

|   | Idle Frame<br>Break Frame |                                             |         |        |        |        |        |                           |                 | Start<br>Bit           |              |                 |                             |

|   |                           |                                             |         |        |        |        |        |                           |                 | Extra Start<br>'1' Bit |              |                 |                             |

|   |                           | 8-bi                                        | t Wor   | d leng | th (M  | bit is | reset) |                           |                 | **                     | LBCL I       | oit cont        | rols last data clock pulse  |

|   | c01                       | 0                                           |         | -      | ata Fr |        | ,      |                           |                 | Possi<br>Pari<br>Bi    | ty           | Ne              | Next Data Frame             |

| 2 | )                         | Star<br>Bit                                 | Bit     | 0 Bit  | 1 Bit  | 2 Bit  | 3 Bit  | 4 Bi                      | t5 Bite         | 6 Bit                  | 7 Sto<br>Bit | p Sta           | art                         |

|   |                           | <                                           |         |        |        |        |        |                           |                 | <u> </u>               | ** !<br>     |                 |                             |

|   | Idle Frame                |                                             |         |        |        |        |        | Sta<br>Bi                 |                 |                        |              |                 |                             |

|   | Break Frame               |                                             |         |        |        |        |        | Ext<br>'1                 | ra Start<br>Bit |                        |              |                 |                             |

|   |                           |                                             |         |        |        |        |        |                           |                 | **                     | LBCL         | bit cont        | trols last data clock pulse |

#### Figure 89. Word Length Programming

155/265

### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

### 10.8.4.3 Receiver

The SCI can receive data words of either 8 or 9 bits. When the M bit is set, word length is 9 bits and the MSB is stored in the R8 bit in the SCICR1 register.

### Character reception

During a SCI reception, data shifts in least significant bit first through the RDI pin. In this mode, the SCIDR register consists or a buffer (RDR) between the internal bus and the received shift register (see Figure 88 on page 153).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIERPR registers.

- Set the RE bit, this enables the receiver which begins searching for a start bit.

When a character is received:

- The RDRF bit is set. It indicates that the content of the shift register is transferred to the RDR.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CCR register.

- The error flags can be set if a frame error, noise or an overrun error has been detected during reception.

Clearing the RDRF bit is performed by the following software sequence done by:

- 1. An access to the SCISR register

- 2. A read to the SCIDR register.

The RDRF bit must be cleared before the end of the reception of the next character to avoid an overrun error.

### **Break Character**

When a break character is received, the SCI handles it as a framing error.

#### **Idle Character**

When an idle frame is detected, there is the same procedure as a data received character plus an interrupt if the ILIE bit is set and the I bit is cleared in the CCR register.

#### **Overrun Error**

An overrun error occurs when a character is received when RDRF has not been reset. Data cannot be transferred from the shift register to the RDR register until the RDRF bit is cleared.

When a overrun error occurs:

- The OR bit is set.

- The RDR content is not lost.

- The shift register is overwritten.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CCR register.

The OR bit is reset by an access to the SCISR register followed by a SCIDR register read operation.

#### Noise Error

Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

When noise is detected in a frame:

- The NF is set at the rising edge of the RDRF bit.

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The NF bit is reset by a SCISR register read operation followed by a SCIDR register read operation.

### Framing Error

A framing error is detected when:

- The stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

- A break is received.

- When the framing error is detected:

- the FE bit is set by hardware

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The FE bit is reset by a SCISR register read operation followed by a SCIDR register read operation.

### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd) CONTROL REGISTER 1 (SCICR1)

Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    |     |  |

|----|----|------|---|------|-----|----|-----|--|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |  |

Bit 7 = R8 Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

### Bit 6 = T8 Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software. 0: SCI enabled

1: SCI prescaler and outputs disabled

Bit 4 = M Word length.

This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

### Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line

1: Address Mark

### Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

### Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

### Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software. 0: Parity error interrupt disabled

1: Parity error interrupt enabled

### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd) CONTROL REGISTER 2 (SCICR2)

Λ

#### Read/Write

Reset Value: 0000 0000 (00h)

7

| '   |      |     |      |    |    |     | Ũ   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TDRE = 1 in the SCISR register

Bit 6 = **TCIE** *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC = 1 in the SCISR register

Bit 5 = **RIE** *Receiver interrupt enable.*

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR = 1 or RDRF = 1 in the SCISR register

Bit 4 = ILIE Idle line interrupt enable.

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE = 1 in the SCISR register.

### Bit 3 = TE Transmitter enable.

This bit enables the transmitter. It is set and cleared by software.

- 0: Transmitter is disabled

- 1: Transmitter is enabled

- Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

### Bit 2 = RE Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

### Bit 1 = RWU Receiver wake-up.

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

0: Receiver in active mode

1: Receiver in mute mode

### Notes:

- Before selecting Mute mode (by setting the RWU bit) the SCI must first receive a data byte, otherwise it cannot function in Mute mode with wakeup by Idle line detection.

- In Address Mark Detection Wake-Up configuration (WAKE bit = 1) the RWU bit cannot be modified by software while the RDRF bit is set.

Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

### beCAN CONTROLLER (Cont'd)

### 10.9.8.2 Mailbox Registers

This chapter describes the registers of the transmit and receive mailboxes. Refer to Section 0.1.4.4 Message Storage for detailed register mapping.

Transmit and receive mailboxes have the same registers except:

- MCSR register in a transmit mailbox is replaced by MFMI register in a receive mailbox.

- A receive mailbox is always write protected.

- A transmit mailbox is write enable only while empty, corresponding TME bit in the CTPR register set.

# MAILBOX CONTROL STATUS REGISTER (MCSR)

### Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |      |      |      |      |      | 0    |

|---|---|------|------|------|------|------|------|

| 0 | 0 | TERR | ALST | тхок | RQCP | ABRQ | TXRQ |

Bits 7:6 = Reserved. Forced to 0 by hardware.

Bit 5 = **TERR** *Transmission Error* - Read

This bit is updated by hardware after each transmission attempt.

0: The previous transmission was successful

1: The previous transmission failed due to an error

Bit 4 = **ALST** Arbitration Lost - Read

This bit is updated by hardware after each transmission attempt.

0: The previous transmission was successful

1: The previous transmission failed due to an arbitration lost

### Bit 3 = **TXOK** Transmission OK

- Read

The hardware updates this bit after each transmission attempt.

0: The previous transmission failed

1: The previous transmission was successful

**Note**: This bit has the same value as the corresponding TXOKx bit in the CTSR register.

### Bit 2 = RQCP Request Completed

- Read/Clear

Set by hardware when the last request (transmit or abort) has been performed.

Cleared by software writing a "1" or by hardware on transmission request.

**Note**: This bit has the same value as the corresponding RQCPx bit of the CTSR register.

Clearing this bit clears all the status bits (TX-OK, ALST and TERR) in the MCSR register and the RQCP and TXOK bits in the CTSR register.

#### Bit 1 = **ABRQ** Abort Request for Mailbox - Read/Set

Set by software to abort the transmission request for the corresponding mailbox.

Cleared by hardware when the mailbox becomes empty.

Setting this bit has no effect when the mailbox is not pending for transmission.

Bit 0 = **TXRQ** *Transmit Mailbox Request*

- Read/Set

Set by software to request the transmission for the corresponding mailbox.

Cleared by hardware when the mailbox becomes empty.

**Note**: This register is implemented only in transmit mailboxes. In receive mailboxes, the MFMI register is mapped at this location.

### beCAN CONTROLLER (Cont'd)

### 10.9.8.3 CAN Filter Registers

### CAN FILTER CONFIGURATION REG.0 (CFCR0)

All bits of this register are set and cleared by software. Read / Write

Reset Value: 0000 0000 (00h)

| 7 |       |       |       |   |       |       | 0     |  |

|---|-------|-------|-------|---|-------|-------|-------|--|

| 0 | FSC11 | FSC10 | FACT1 | 0 | FSC01 | FSC00 | FACT0 |  |

**Note**: To modify the FFAx and FSCx bits, the be-CAN must be in INIT mode.

Bit 7 = Reserved. Forced to 0 by hardware.

Bits 6:5 = **FSC1[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 1.

Bit 4 = **FACT1** *Filter Active* The software sets this bit to activate Filter 1. To modify the Filter 1 registers (CF1R[7:0]), the FACT1 bit must be cleared. 0: Filter 1 is not active 1: Filter 1 is active

Bit 3 = Reserved. Forced to 0 by hardware.

Bits 2:1 = **FSC0[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 0.

Bit 0 = **FACT0** *Filter Active* The software sets this bit to activate Filter 0. To modify the Filter 0 registers (CF0R[0:7]), the FACT0 bit must be cleared. 0: Filter 0 is not active 1: Filter 0 is active

### **CAN FILTER CONFIGURATION REG.1 (CFCR1)**

All bits of this register are set and cleared by software. Read / Write

Reset Value: 0000 0000 (00h)

| 7 |       |       |       |   |       |       | 0     |  |

|---|-------|-------|-------|---|-------|-------|-------|--|

| 0 | FSC31 | FSC30 | FACT3 | 0 | FSC21 | FSC20 | FACT2 |  |

Bit 7 = Reserved. Forced to 0 by hardware.

Bits 6:5 = **FSC3[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 3.

### Bit 4 = FACT3 Filter Active

The software sets this bit to activate filter 3. To modify the Filter 3 registers (CF3R[0:7]) the FACT3 bit must be cleared. 0: Filter 3 is not active 1: Filter 3 is active

Bit 3 = Reserved. Forced to 0 by hardware.

Bits 2:1 = **FSC2[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 2.

### Bit 0 = FACT2 Filter Active

The software sets this bit to activate Filter 2. To modify the Filter 2 registers (CF2R[0:7]), the FACT2 bit must be cleared. 0: Filter 2 is not active

1: Filter 2 is active

### COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

### Figure 139. SPI Slave Timing Diagram with CPHA = 1<sup>1)</sup>

### Notes:

MISO INPUT

MOSI OUTPUT

1. Measurement points are done at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}.$

1

L 1 Í

I.

MSB OUT

t<sub>h(MI)</sub>

MSB IN

t<sub>h(MO)</sub>

t<sub>su(MI)</sub>

t<sub>v(MO)</sub>

See note 2

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

BIT6 IN

BIT6 OUT

ХΧ

See note 2

LSB IN

LSB OUT

### TRANSFER OF CUSTOMER CODE (Cont'd)

|   |                                                                            | S                                                                                                                                                                    | T72561 MICROCON<br>(Last update:                                                                                                                            | TROLLER OF<br>September 20                               |                                       | LIST                                                     |                                                   |  |  |  |  |  |

|---|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------|----------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

|   | Customer<br>Address                                                        |                                                                                                                                                                      |                                                                                                                                                             |                                                          | · · · · · · · · · · · · · · · · · · · |                                                          |                                                   |  |  |  |  |  |

|   | *The ROM/FA                                                                | DM Code*                                                                                                                                                             | e is assigned by STMic<br>ent in .S19 formatHe:                                                                                                             | croelectronics.                                          | <br><br>                              | processed.                                               |                                                   |  |  |  |  |  |

|   | Device Type/                                                               | Memory Size/Packag                                                                                                                                                   | ge (check only one opt                                                                                                                                      | ion)                                                     |                                       |                                                          |                                                   |  |  |  |  |  |

|   | ROM:                                                                       | Package                                                                                                                                                              | 60K                                                                                                                                                         | 48K                                                      | <br>                                  | 32K                                                      | 16K                                               |  |  |  |  |  |

|   | I                                                                          | LQFP44:                                                                                                                                                              | [ ] ST72561AR9<br>  [ ] ST72561J9<br>  [ ] ST72561K9<br>                                                                                                    |                                                          | 7                                     | [] ST72561J6                                             | [] ST72561AR4  <br>[] ST72561J4  <br>[] ST72561K4 |  |  |  |  |  |

|   | FASTROM:                                                                   | Package                                                                                                                                                              | 60K                                                                                                                                                         | 48K                                                      | <br>                                  | 32K                                                      | 16K                                               |  |  |  |  |  |

|   | I                                                                          | LQFP44:                                                                                                                                                              | [ ] ST72P561AR9<br>  [ ] ST72P561J9<br>  [ ] ST72P561K9                                                                                                     |                                                          | J7                                    |                                                          | []ST72P561J4                                      |  |  |  |  |  |

|   |                                                                            | Conditioning: [] Tray [] Tape & Reel<br>Special Marking: [] No [] Yes "" (10 char. max]<br>Authorized characters are letters, digits, '.', '-', '/' and spaces only. |                                                                                                                                                             |                                                          |                                       |                                                          |                                                   |  |  |  |  |  |

|   | Temp. Range                                                                | emp. Range. Please refer to datasheet for specific sales conditions:                                                                                                 |                                                                                                                                                             |                                                          |                                       |                                                          |                                                   |  |  |  |  |  |

|   | -                                                                          |                                                                                                                                                                      | mp. Range                                                                                                                                                   |                                                          |                                       |                                                          |                                                   |  |  |  |  |  |

|   | []<br>[]                                                                   | <ul> <li>-40°C to +8</li> <li>-40°C to +</li> </ul>                                                                                                                  |                                                                                                                                                             |                                                          |                                       |                                                          |                                                   |  |  |  |  |  |

|   | Clock Source                                                               | Selection:                                                                                                                                                           | [] Resonator:<br>[] External Source                                                                                                                         |                                                          |                                       |                                                          |                                                   |  |  |  |  |  |

|   | Oscillator/Exte<br>LVD<br>PLL <sup>1</sup><br>Watchdog Sel<br>Watchdog Res |                                                                                                                                                                      | [] LP: Low power (1<br>[] MP: Medium power<br>[] MS: Medium spee<br>[] HS: High speed (8<br>[] Disabled<br>[] Disabled<br>[] Software Activatio<br>[] Reset | er (2 to 4 MHz)<br>d (4 to 8 MHz)<br>to 16 MHz)          | ĺ                                     | ] Enabled<br>] Enabled<br>] Hardware Activation<br>Reset | 1                                                 |  |  |  |  |  |

| C | Read-out Prot                                                              | ection                                                                                                                                                               | [] Disabled                                                                                                                                                 |                                                          | [] Ena                                | bled                                                     |                                                   |  |  |  |  |  |

|   | Reset Delay                                                                |                                                                                                                                                                      | [] 256 Cycles [                                                                                                                                             | ] 4096 Cycles                                            |                                       |                                                          |                                                   |  |  |  |  |  |

|   | LINSCI2 Mapp<br>T16_ICAP2 M                                                |                                                                                                                                                                      | [ ] Not available (AFI<br>[ ] On PD1 (AFIMAP                                                                                                                | [ ] Mapped (AFIMAP[1] = 1)<br>[ ] On PC1 (AFIMAP[0] = 1) |                                       |                                                          |                                                   |  |  |  |  |  |

|   | Comments:<br>Supply Opera                                                  | Comments:<br>Supply Operating Range in the application:                                                                                                              |                                                                                                                                                             |                                                          |                                       |                                                          |                                                   |  |  |  |  |  |

|   | Notes<br>Signature<br>Date                                                 |                                                                                                                                                                      |                                                                                                                                                             |                                                          |                                       |                                                          |                                                   |  |  |  |  |  |

|   |                                                                            | load the latest vers                                                                                                                                                 | r (2 to 4 MHz range) h<br>sion of this option list                                                                                                          |                                                          | d (MP)                                |                                                          |                                                   |  |  |  |  |  |

|   |                                                                            |                                                                                                                                                                      |                                                                                                                                                             |                                                          |                                       |                                                          |                                                   |  |  |  |  |  |

SCIBRR = 0xC9), the wrong break duration occurrence is around 1%.

### Workaround

If this wrong duration is not compliant with the communication protocol in the application, software can request that an Idle line be generated before the break character. In this case, the break duration is always correct assuming the application is not doing anything between the idle and the break. This can be ensured by temporarily disabling interrupts.

- Disable interrupts

- Reset and Set TE (IDLE request)

- Set and Reset SBK (Break Request)

- Re-enable interrupts

#### LIN mode

If the LINE bit in the SCICR3 is set and the M bit in the SCICR1 register is reset, the LINSCI is in LIN master mode. A single break character is sent by e st .naracte .cted: .cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cted:.cte setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may