Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, LINbusSCI, SPI                                               |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561k6tc |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# CENTRAL PROCESSING UNIT (Cont'd)

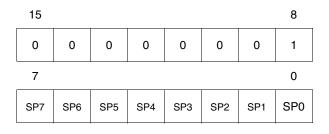

# Stack Pointer (SP)

### Read/Write

Reset Value: 01 FFh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 9).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

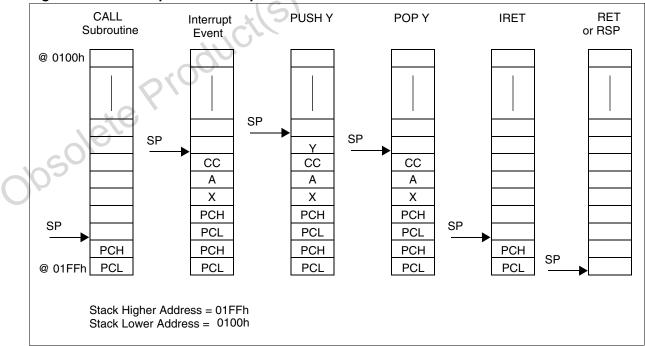

### Figure 9. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 9.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

**47/**

### SYSTEM INTEGRITY MANAGEMENT (Cont'd)

## 6.4.4 Register Description

### SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

Read/Write

Reset Value: 000x 000x (00h)

| 7 |           |          |           |   |   |   | 0         |

|---|-----------|----------|-----------|---|---|---|-----------|

| 0 | AVD<br>IE | AVD<br>F | LVD<br>RF | 0 | 0 | 0 | WDG<br>RF |

Bit 7 = Reserved, must be kept cleared.

Bit 6 = **AVDIE** Voltage Detector interrupt enable This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag changes (toggles). The pending interrupt information is automatically cleared when software enters the AVD interrupt routine. 0: AVD interrupt disabled

1: AVD interrupt enabled

#### Bit 5 = **AVDF** Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 16 and to Section 6.4.2.1 for additional details.

0:  $V_{DD}$  over  $V_{IT+(AVD)}$  threshold 1:  $V_{DD}$  under  $V_{IT-(AVD)}$  threshold

#### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined. Bits 3:1 = Reserved, must be kept cleared.

#### Bit 0 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

|                    |       |       |

### Application notes

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

**CAUTION:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

### POWER SAVING MODES (Cont'd)

### 8.6.1 Register Description

# AWUFH CONTROL/STATUS REGISTER (AWUCSR)

Read/Write (except bit 2 read only) Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |          |          | 0         |

|---|---|---|---|---|----------|----------|-----------|

| 0 | 0 | 0 | 0 | 0 | AWU<br>F | AWU<br>M | AWU<br>EN |

Bits 7:3 = Reserved.

#### Bit 2 = AWUF Auto Wake-Up Flag

This bit is set by hardware when the AWU module generates an interrupt and cleared by software on reading AWUCSR.

0: No AWU interrupt occurred

1: AWU interrupt occurred

Bit 1 = **AWUM** Auto Wake-Up Measurement This bit enables the AWU RC oscillator and connects its output to the ICAP1 input of the 16-bit timer. This allows the timer to be used to measure the AWU RC oscillator dispersion and then compensate this dispersion by providing the right value in the AWUPR register.

0: Measurement disabled

1: Measurement enabled

Bit 0 = **AWUEN** Auto Wake-Up From Halt Enabled This bit enables the Auto Wake-Up From Halt feature: once HALT mode is entered, the AWUFH wakes up the microcontroller after a time delay defined by the AWU prescaler value. It is set and cleared by software.

Table 11. AWU Register Map and Reset Values

| 0: AWUFH (Auto Wake-Up From Halt) mode disa- | • |

|----------------------------------------------|---|

| bled                                         |   |

1: AWUFH (Auto Wake-Up From Halt) mode enabled

### AWUFH PRESCALER REGISTER (AWUPR) Read/Write

Reset Value: 1111 1111 (FFh)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

|     |     |     |     |     |     |     | AWU |

| PR7 | PR6 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 |

Bits 7:0 = **AWUPR[7:0]** Auto Wake-Up Prescaler These 8 bits define the AWUPR Dividing factor (as explained below:

| AWUPR[7:0] | Dividing factor      |

|------------|----------------------|

| 00h        | Forbidden (See note) |

| 01h        | 1                    |

|            |                      |

| C FEh      | 254                  |

| FFh        | 255                  |

In AWU mode, the period that the MCU stays in Halt Mode (t<sub>AWU</sub> in Figure 30) is defined by

$$^{t}AWU = 64 \times AWUPR \times \frac{1}{f_{AWURC}} + ^{t}RCSTRT$$

This prescaler register can be programmed to modify the time that the MCU stays in Halt mode before waking up automatically.

**Note:** If 00h is written to AWUPR, depending on the product, an interrupt is generated immediately after a HALT instruction or the AWUPR remains unchanged.

| Address<br>(Hex.) | Register<br>Label     | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------------|-----------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 002Bh             | AWUCSR<br>Reset Value | 0           | 0           | 0           | 0           | 0           | AWUF<br>0   | AWUM<br>0   | AWUEN<br>0  |

| 002Ch             | AWUPR<br>Reset Value  | AWUPR7<br>1 | AWUPR6<br>1 | AWUPR5<br>1 | AWUPR4<br>1 | AWUPR3<br>1 | AWUPR2<br>1 | AWUPR1<br>1 | AWUPR0<br>1 |

# WINDOW WATCHDOG (Cont'd)

10.1.9 Interrupts

None.

# 10.1.10 Register Description CONTROL REGISTER (WDGCR)

Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | Т3 | T2 | T1 | то |

# Bit 7 = WDGA Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte.

Bits 6:0 = **T[6:0]** 7-bit counter (MSB to LSB). These bits contain the value of the watchdog counter. It is decremented every 16384  $f_{OSC2}$  cycles (approx.). A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

# WINDOW REGISTER (WDGWR)

Read/Write

Reset Value: 0111 1111 (7Fh)

| 7 |    |    |    |    |    |    | 0  |

|---|----|----|----|----|----|----|----|

| - | W6 | W5 | W4 | WЗ | W2 | W1 | WO |

Bit 7 = Reserved

Bits 6:0 = **W[6:0]** *7-bit window value* These bits contain the window value to be compared to the downcounter.

# Figure 38. Watchdog Timer Register Map and Reset Values

|        | Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |

|--------|-------------------|-------------------|------|----|----|----|----|----|----|----|--|

|        | 2F                | WDGCR             | WDGA | Т6 | T5 | T4 | ТЗ | T2 | T1 | то |  |

|        | $O^{2}$           | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |  |

| $\cup$ | 30                | WDGWR             | -    | W6 | W5 | W4 | W3 | W2 | W1 | W0 |  |

|        | 30                | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |  |

# **ON-CHIP PERIPHERALS** (Cont'd)

# INPUT CAPTURE CONTROL / STATUS REGISTER (ARTICCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |     |     |      |      |     | 0   |

|---|---|-----|-----|------|------|-----|-----|

| 0 | 0 | CS2 | CS1 | CIE2 | CIE1 | CF2 | CF1 |

Bit 7:6 = Reserved, always read as 0.

### Bit 5:4 = **CS[2:1]** Capture Sensitivity

These bits are set and cleared by software. They determine the trigger event polarity on the corresponding input capture channel.

0: Falling edge triggers capture on channel x.

1: Rising edge triggers capture on channel x.

Bit 3:2 = **CIE[2:1]** Capture Interrupt Enable

These bits are set and cleared by software. They enable or disable the Input capture channel interrupts independently.

0: Input capture channel x interrupt disabled. 1: Input capture channel x interrupt enabled.

## Bit 1:0 = CF[2:1] Capture Flag

These bits are set by hardware and cleared by software reading the corresponding ARTICRx register. Each CFx bit indicates that an input capture x has occurred.

0: No input capture on channel x.

210501et

<u>ل</u>حک

1: An input capture has occurred on channel x.

# **INPUT CAPTURE REGISTERS (ARTICRx)**

Read only

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IC7 | IC6 | IC5 | IC4 | IC3 | IC2 | IC1 | IC0 |

# Bit 7:0 = IC[7:0] Input Capture Data

These read only bits are set and cleared by hardware. An ARTICRx register contains the 8-bit auto-reload counter value transferred by the input capture channel x event.

### 16-BIT TIMER (Cont'd)

### 10.4.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are two output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC*i*E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

### Procedure:

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OC*i*R register and CR register:

OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \text{ OC}_{i}\text{R} = \frac{\Delta t * f_{CPU}}{\text{PRESC}}$$

Where:

1

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 17 Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC}_{i} R = \Delta t * f_{EXT}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OCiLR register (enables the output compare function and clears the OCF*i* bit).

57/

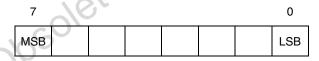

# 16-BIT TIMER (Cont'd) INPUT CAPTURE 1 HIGH REGISTER (IC1HR)

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

### **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

|            | 7   |     |    |    |    |     |    | 0   |  |

|------------|-----|-----|----|----|----|-----|----|-----|--|

|            | MSB |     |    |    |    |     |    | LSB |  |

| -          |     |     |    |    |    |     |    |     |  |

|            |     |     |    |    |    |     | iG | Ń   |  |

|            |     |     |    |    |    | . C |    |     |  |

|            |     |     |    |    | -0 | S.C |    |     |  |

|            |     |     |    | 05 | 0  |     |    |     |  |

|            |     |     | je | X  |    |     |    |     |  |

|            |     | 16  |    |    |    |     |    |     |  |

|            | S   | 0/, |    |    |    |     |    |     |  |

| $\bigcirc$ |     |     |    |    |    |     |    |     |  |

|            |     |     |    |    |    |     |    |     |  |

# OUTPUT COMPARE 1 HIGH REGISTER (OC1HR)

#### Read/Write

\_

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

<u>ل</u>رک

### 16-BIT TIMER (Cont'd)

# OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

#### Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| /   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

### **COUNTER HIGH REGISTER (CHR)**

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   | 0   |

|-----|-----|

| MSB | LSB |

|     |     |

# **COUNTER LOW REGISTER (CLR)**

#### Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# ALTERNATE COUNTER HIGH REGISTER (ACHR)

#### Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# ALTERNATE COUNTER LOW REGISTER (ACLR)

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# INPUT CAPTURE 2 HIGH REGISTER (IC2HR)

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

### **INPUT CAPTURE 2 LOW REGISTER (IC2LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 1   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# 8-BIT TIMER (Cont'd) 10.5.8 8-bit Timer Register Map

# SERIAL PERIPHERAL INTERFACE (cont'd)

# 10.6.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the device is woken up<br>by an interrupt with "exit from HALT mode"<br>capability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the Device. |

# 10.6.6.1 Using the SPI to wake up the device from Halt mode

In slave configuration, the SPI is able to wake up the device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

Note: When waking up from HALT mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from HALT mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the device from HALT mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the device enters HALT mode. So, if Slave selection is configured as external (see Section 10.6.3.2), make sure the master drives a low level on the SS pin when the slave enters HALT mode.

# 10.6.7 Interrupts

|                              |               |                          | X \                  |                      |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

| SPI End of<br>Transfer Event | SPIF          | 0                        |                      | Yes                  |

| Master Mode<br>Fault Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          |                      |                      |

|                              |               | •                        |                      |                      |

**Note:** The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

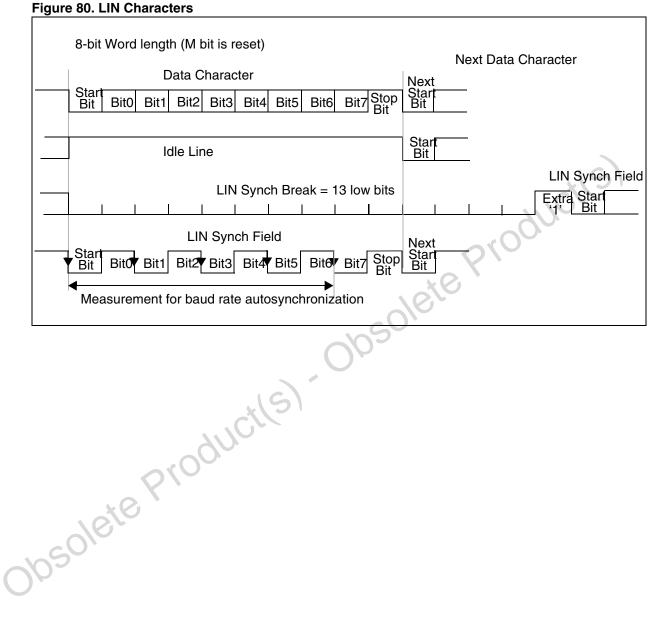

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

57

## LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

#### 10.8.4.4 Conventional Baud Rate Generation

The baud rates for the receiver and transmitter (Rx and Tx) are set independently and calculated as follows

:

$$Tx = \frac{f_{CPU}}{(16*PR)*TR} \qquad Rx = \frac{f_{CPU}}{(16*PR)*RR}$$

with:

67/

PR = 1, 3, 4 or 13 (see SCP[1:0] bits)

TR = 1, 2, 4, 8, 16, 32, 64, 128

(see SCT[2:0] bits)

RR = 1, 2, 4, 8, 16, 32, 64, 128

(see SCR[2:0] bits)

All these bits are in the SCIBRR register.

**Example:** If  $f_{CPU}$  is 8 MHz (normal mode) and if PR = 13 and TR = RR = 1, the transmit and receive baud rates are 38400 baud.

**Note:** The baud rate registers MUST NOT be changed while the transmitter or the receiver is enabled.

#### 10.8.4.5 Extended Baud Rate Generation

The extended prescaler option gives a very fine tuning on the baud rate, using a 255 value prescaler, whereas the conventional Baud Rate Generator retains industry standard software compatibility.

The extended baud rate generator block diagram is described in the Figure 90.

The output clock rate sent to the transmitter or to the receiver is the output from the 16 divider divided by a factor ranging from 1 to 255 set in the SCI-ERPR or the SCIETPR register.

**Note:** The extended prescaler is activated by setting the SCIETPR or SCIERPR register to a value

other than zero. The baud rates are calculated as follows:

$$Tx = \frac{f_{CPU}}{16 \cdot ETPR^{*}(PR^{*}TR)} Rx = \frac{f_{CPU}}{16 \cdot ERPR^{*}(PR^{*}RR)}$$

with:

ETPR = 1, ..., 255 (see SCIETPR register)

ERPR = 1, ..., 255 (see SCIERPR register)

### 10.8.4.6 Receiver Muting and Wake-up Feature

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non addressed receivers.

The non addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits cannot be set.

All the receive interrupts are inhibited.

A muted receiver may be awakened by one of the following two ways:

- by Idle Line detection if the WAKE bit is reset,

- by Address Mark detection if the WAKE bit is set.

Receiver wakes-up by Idle Line detection when the Receive line has recognized an Idle Frame. Then the RWU bit is reset by hardware but the IDLE bit is not set.

Receiver wakes-up by Address Mark detection when it received a "1" as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

159/265

### 10.9 beCAN CONTROLLER (beCAN)

The beCAN controller (Basic Enhanced CAN), interfaces the CAN network and supports the CAN protocol version 2.0A and B. It has been designed to manage high number of incoming messages efficiently with a minimum CPU load. It also meets the priority requirements for transmit messages.

## 10.9.1 Main Features

- Supports CAN protocol version 2.0 A, B Active

- Bit rates up to 1Mbit/s

# Transmission

- 2 transmit mailboxes

- Configurable transmit priority

# Reception

- 1 receive FIFO with three stages

- 6 scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

# Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

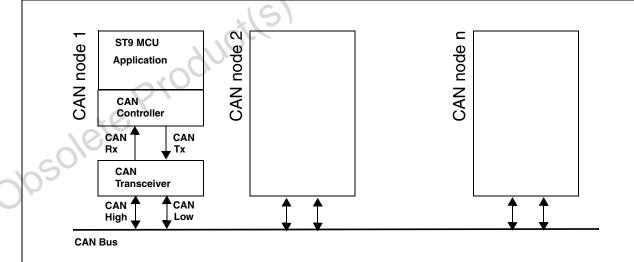

# Figure 94. CAN Network Topology

## **10.9.2 General Description**

In today's CAN applications, the number of nodes in a network is increasing and often several networks are linked together via gateways. Typically the number of messages in the system (and thus to be handled by each node) has significantly increased. In addition to the application messages, Network Management and Diagnostic messages have been introduced.

An enhanced filtering mechanism is required to handle each type of message.

Furthermore, application tasks require more CPU time, therefore real-time constraints caused by message reception have to be reduced.

A receive FIFO scheme allows the CPU to be dedicated to application tasks for a long time period without losing messages.

The standard HLP (Higher Layer Protocol) based on standard CAN drivers requires an efficient interface to the CAN controller.

All mailboxes and registers are organized in 16byte pages mapped at the same address and selected via a page select register.

**47/**

# Figure 102. Filter Bank Scale Configuration - Register Organisation

|                           | Filter Bank Scale  | Configuration            | Filter Bank Scale Co   | nfig. Bits <sup>1</sup> |

|---------------------------|--------------------|--------------------------|------------------------|-------------------------|

|                           | One 32-Bit Filter  |                          | FSCx = 3               |                         |

| Identifier                | CFxR0              | CFxR1                    | CFxR2                  | CFxR3                   |

| Mask/Ident.               | CFxR4              | CFxR5                    | CFxR6                  | CFxR7                   |

| Bit Mapping               | STID10:3           | STID2:0 RTR DE EXID17:15 | EXID14:7               | EXID6:0                 |

|                           | Two 16-Bit Filters |                          |                        |                         |

| Identifier                | CFxR0              | CFxR1                    |                        | .151                    |

| Mask/Ident.               | CFxR2              | CFxR3                    | 500 0                  | CIL S                   |

| Identifier                | CFxR4              | CFxR5                    | FSCx = 2               | 21/0                    |

| Mask/Ident.               | CFxR6              | CFxR7                    | . (                    | $\gamma^{O}$            |

| Bit Mapping               | STID10:3           | STID2:0 RTR DE EXID17:15 | 01                     | oduct(S)                |

|                           | One 16-Bit / Two   |                          | oletepri               |                         |

| Identifier                | CFxR0              | CFxR1                    |                        |                         |

| Mask/Ident.               | CFxR2              | CFxR3                    | 5                      |                         |

| ldentifier<br>Mask/Ident. | CFxR4<br>CFxR5     |                          |                        |                         |

| ldentifier<br>Mask/Ident. | CFxR6<br>CFxR7     | ((5)                     | FSCx = 1               |                         |

|                           | Four 8-Bit Filters |                          |                        |                         |

| ldentifier<br>Mask/Ident. | CFxR0<br>CFxR1     | ]                        |                        |                         |

| ldentifier<br>Mask/Ident. | CFxR2<br>CFxR3     | ]                        |                        |                         |

| Identifier<br>Mask/Ident. | CFxR4<br>CFxR5     | ]                        | FSCx = 0               |                         |

| Identifier                | CFxR6              | ] ,                      | k = filter bank number |                         |

| Mask/Ident.               | CFxR7              | 1                        | Those bits are leasts  | d in the CFCR register  |

| Bit Mapping               | STID10:3           | 1                        |                        | a in the Cron register  |

57

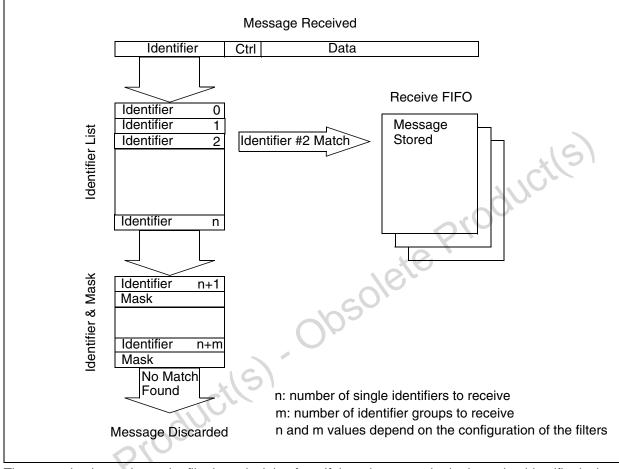

# Figure 103. Filtering Mechanism - example

The example above shows the filtering principle of the beCAN. On reception of a message, the identifier is compared first with the filters configured in identifier list mode. If there is a match, the message is stored in the FIFO and the index of the matching filter is stored in the Filter Match Index. As shown in the example, the identifier matches with Identifier #2 thus the message content and MFMI 2 is stored in the FIFO. If there is no match, the incoming identifier is then compared with the filters configured in mask mode.

If the identifier does not match any of the identifiers configured in the filters, the message is discarded by hardware without software intervention.

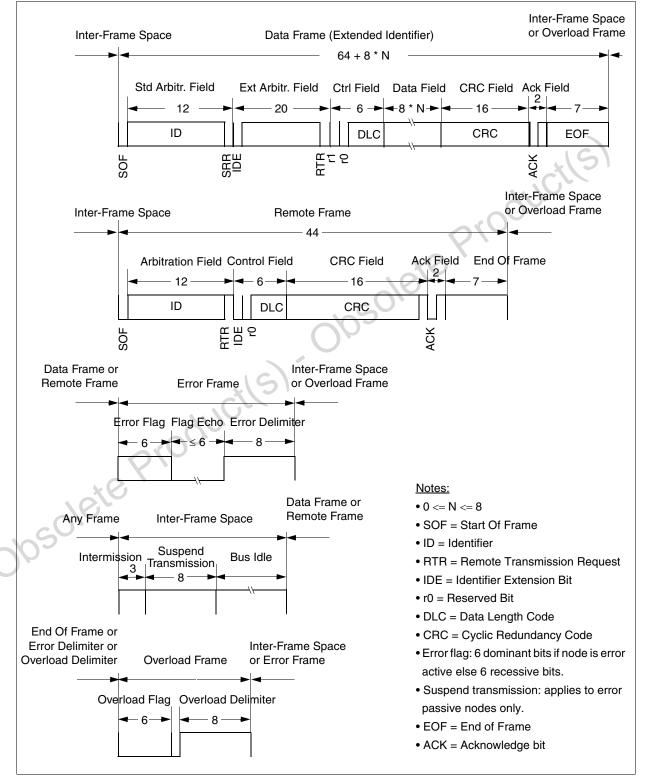

# Figure 107. CAN Frames (Part 2 of 2)

- The FIFO interrupt can be generated by the following events:

- Reception of a new message, FMP bits in the CRFR0 register incremented.

- FIFO0 full condition, FULL bit in the CRFR0 register set.

- FIFO0 overrun condition, FOVR bit in the CRFR0 register set.

- The transmit, error and status change interrupt can be generated by the following events:

- Transmit mailbox 0 becomes empty, RQCP0 bit in the CTSR register set.

- Transmit mailbox 1 becomes empty, RQCP1 bit in the CTSR register set.

- Error condition, for more details on error conditions please refer to the CAN Error Status register (CESR).

- Wake-up condition, SOF monitored on the done by s

CAN Rx signal.

### **10.9.6 Register Access Protection**

Erroneous access to certain configuration registers can cause the hardware to temporarily disturb the whole CAN network. Therefore the following registers can be modified by software only while the hardware is in initialization mode:

CBTR0, CBTR1, CFCR0, CFCR1, CFMR and CDGR registers.

Although the transmission of incorrect data will not cause problems at the CAN network level, it can severely disturb the application. A transmit mailbox can be only modified by software while it is in empty state (refer to Figure 7. Transmit Mailbox States).

The filters must be deactivated before their value can be modified by software. The modification of the filter configuration (scale or mode) can be done by software only in initialization mode.

# beCAN CONTROLLER (Cont'd) MAILBOX FILTER MATCH INDEX (MFMI)

This register is read only.

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| FMI7 | FMI6 | FMI5 | FMI4 | FMI3 | FMI2 | FMI1 | FMI0 |

### Bits 7:0 = **FMI**[7:0] *Filter Match Index*

This register contains the index of the filter the message stored in the mailbox passed through. For more details on identifier filtering please refer to Section 0.1.4.3 - Filter Match Index paragraph.

**Note**: This register is implemented only in receive mailboxes. In transmit mailboxes, the MCSR register is mapped at this location.

# MAILBOX IDENTIFIER REGISTERS (MIDR[3:0])

Read / Write Reset Value: Undefined MIDR0

| 7 |     |     |        |       |       |       | 0     |  |

|---|-----|-----|--------|-------|-------|-------|-------|--|

| 0 | IDE | RTR | STID10 | STID9 | STID8 | STID7 | STID6 |  |

Bit 7 = Reserved. Forced to 0 by hardware.

### Bit 6 = IDE Extended Identifier

This bit defines the identifier type of message in the mailbox.

0: Standard identifier.

1: Extended identifier.

Bit 5 = RTR Remote Transmission Request

- 0: Data frame

- 1: Remote frame

Bits 4:0 = **STID[10:6]** *Standard Identifier* 5 most significant bits of the standard part of the identifier.

# MIDR1

| 7     |       |       |       |       |       |        | 0      |

|-------|-------|-------|-------|-------|-------|--------|--------|

| STID5 | STID4 | STID3 | STID2 | STID1 | STID0 | EXID17 | EXID16 |

Bits 7:2 = **STID**[5:0] *Standard Identifier* 6 least significant bits of the standard part of the identifier.

Bits 1:0 = **EXID[17:16]** *Extended Identifier* 2 most significant bits of the extended part of the identifier.

# MIDR2

| 7      | 10     | 10     |        |        |        |       | 0     |

|--------|--------|--------|--------|--------|--------|-------|-------|

| EXID15 | EXID14 | EXID13 | EXID12 | EXID11 | EXID10 | EXID9 | EXID8 |

Bits 7:0 = **EXID[15:8]** *Extended Identifier*

Bits 15 to 8 of the extended part of the identifier.

# MIDR3

| 7     |       |       |       |       |       |       | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EXID7 | EXID6 | EXID5 | EXID4 | EXID3 | EXID2 | EXID1 | EXID0 |

Bits 7:1 = **EXID[6:0]** *Extended Identifier* 6 least significant bits of the extended part of the identifier.

# I/O PORT PIN CHARACTERISTICS (Cont'd)

# 12.9.2 Output Driving Current

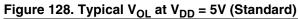

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                        | Parameter                                                                             | Conditions        |                                                                     | Min                  | Мах        | Unit |

|-------------------------------|---------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------|----------------------|------------|------|

|                               | Output low level voltage for a standard I/O pin                                       |                   | I <sub>IO</sub> =+5mA                                               |                      | 1.2        |      |

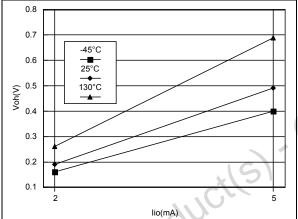

| · · · 1)                      | when eight pins are sunk at same time (see Figure 128)                                |                   | I <sub>IO</sub> =+2mA                                               |                      | 0.5        |      |

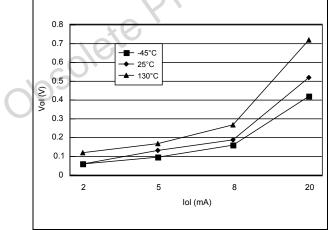

| V <sub>OL</sub> <sup>1)</sup> | Output low level voltage for a high sink I/O pin when four pins are sunk at same time | <sub>0</sub> =5V  | I <sub>IO</sub> =+20mA,T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C |                      | 1.3<br>1.5 | V    |

|                               | (see Figure 129 and Figure 132)                                                       | V <sub>DD</sub> : | I <sub>IO</sub> =+8mA                                               |                      | 0.6        |      |

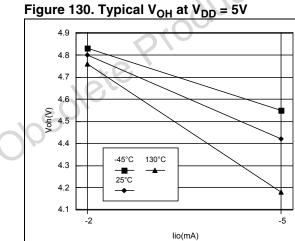

| V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when four pins are sourced at same time      |                   | I <sub>IO</sub> =-5mA, T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C |                      | 10         |      |

|                               | (see Figure 130 and Figure 133)                                                       |                   | I <sub>IO</sub> =-2mA                                               | V <sub>DD</sub> -0.7 |            |      |

Figure 129. Typical V<sub>OL</sub> at V<sub>DD</sub> = 5V (High-sink)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins does not have V<sub>OH</sub>.

# **12.11 TIMER PERIPHERAL CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}, f_{OSC},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

# 12.11.1 8-Bit PWM-ART Autoreload Timer

| Symbol                | Parameter                        | Conditions                         | Min   | Тур | Max                 | Unit             |

|-----------------------|----------------------------------|------------------------------------|-------|-----|---------------------|------------------|

| +                     | PWM resolution time              |                                    | 1     |     |                     | t <sub>CPU</sub> |

| t <sub>res(PWM)</sub> |                                  | f <sub>CPU</sub> = 8 MHz           | 125   |     |                     | ns               |

| f <sub>EXT</sub>      | ART external clock frequency     |                                    | 0     |     | f <sub>CPU</sub> /2 | MHz              |

| f <sub>PWM</sub>      | PWM repetition rate              |                                    | 0     |     | 'CPU/~              | SWIIZ            |

| Res <sub>PWM</sub>    | PWM resolution                   |                                    |       |     | 8                   | bit              |

| V <sub>OS</sub>       | PWM/DAC output step voltage      | V <sub>DD</sub> = 5V, Res = 8-bits |       | 20  | N<br>V              | mV               |

| t                     | Timer clock period when internal | f <sub>CPU</sub> = 8 MHz           | 1     |     | 128                 | t <sub>CPU</sub> |

| <sup>t</sup> COUNTER  | clock is selected                | ICPU - 0 10112                     | 0.125 |     | 16                  | μs               |

| 12.11.2 8             | -Bit Timer                       |                                    | 10    |     |                     |                  |

# 12.11.2 8-Bit Timer

| Symbol                 | Parameter                | Conditions               | Min   | Тур | Max                 | Unit             |

|------------------------|--------------------------|--------------------------|-------|-----|---------------------|------------------|

| t <sub>w(ICAP)in</sub> | Input capture pulse time | - vS                     | 1     |     |                     | <b>t</b>         |

| t <sub>res(PWM)</sub>  | PWM resolution time      | $\mathbf{O}\mathbf{Y}$   | 2     |     |                     | t <sub>CPU</sub> |

|                        |                          | f <sub>CPU</sub> = 8 MHz | 250   |     |                     | ns               |

| f <sub>PWM</sub>       | PWM repetition rate      |                          | 0     |     | f <sub>CPU</sub> /4 | MHz              |

| Res <sub>PWM</sub>     | PWM resolution           |                          |       |     | 8                   | bit              |

| <sup>t</sup> COUNTER   | Timer clock period       | f <sub>CPU</sub> = 8 MHz | 2     |     | 8000                | t <sub>CPU</sub> |

|                        |                          |                          | 0.250 |     | 1000                | μs               |

# 12.11.3 16-Bit Timer

| Symbol                 | Parameter                                             | Conditions               | Min   | Тур | Max                 | Unit             |

|------------------------|-------------------------------------------------------|--------------------------|-------|-----|---------------------|------------------|

| t <sub>w(ICAP)in</sub> | Input capture pulse time                              |                          | 1     |     |                     | tanu             |

| t <sub>res(PWM)</sub>  | PWM resolution time                                   |                          | 2     |     |                     | t <sub>CPU</sub> |

|                        |                                                       | f <sub>CPU</sub> = 8 MHz | 250   |     |                     | ns               |

| f <sub>EXT</sub>       | Timer external clock frequency                        |                          | 0     |     | f//                 | MHz              |

| f <sub>PWM</sub>       | PWM repetition rate                                   |                          | 0     |     | f <sub>CPU</sub> /4 |                  |

| Res <sub>PWM</sub>     | PWM resolution                                        |                          |       |     | 16                  | bit              |

| t <sub>COUNTER</sub>   | Timer clock period when internal<br>clock is selected | f <sub>CPU</sub> = 8 MHz | 2     |     | 8                   | t <sub>CPU</sub> |

|                        |                                                       |                          | 0.250 |     | 1                   | μs               |