Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, LINbusSCI, SPI                                               |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 48KB (48K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561k7t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents** -

| 1 DESC | CRIPTION                         | 4  |

|--------|----------------------------------|----|

|        | DESCRIPTION                      |    |

|        | STER AND MEMORY MAP              |    |

|        | SH PROGRAM MEMORY                |    |

|        | INTRODUCTION                     |    |

|        | MAIN FEATURES                    |    |

|        | STRUCTURE                        |    |

|        | ICC INTERFACE                    |    |

|        | ICP (IN-CIRCUIT PROGRAMMING)     |    |

|        | IAP (IN-APPLICATION PROGRAMMING) |    |

| 4.7    | RELATED DOCUMENTATION            | 17 |

| 4.8    | REGISTER DESCRIPTION             | 17 |

| 5 CENT | FRAL PROCESSING UNIT             | 18 |

| 5.1    | INTRODUCTION                     | 18 |

| 5.2    | MAIN FEATURES                    | 18 |

| 5.3    | CPU REGISTERS                    | 18 |

| 6 SUPF | PLY, RESET AND CLOCK MANAGEMENT  | 21 |

| 6.1    | PHASE LOCKED LOOP                | 21 |

| 6.2    | MULTI-OSCILLATOR (MO)            | 22 |

|        | RESET SEQUENCE MANAGER (RSM)     |    |

|        | SYSTEM INTEGRITY MANAGEMENT (SI) |    |

| 7 INTE | RRUPTS                           | 29 |

|        |                                  |    |

|        | MASKING AND PROCESSING FLOW      |    |

|        | INTERRUPTS AND LOW POWER MODES   |    |

|        | CONCURRENT & NESTED MANAGEMENT   |    |

|        | INTERRUPT REGISTER DESCRIPTION   |    |

|        | EXTERNAL INTERRUPTS              |    |

|        | ER SAVING MODES                  |    |

|        | INTRODUCTION                     |    |

|        | SLOW MODE                        |    |

|        | WAIT MODE                        |    |

| _      | HALT MODE                        |    |

|        | ACTIVE HALT MODE                 |    |

|        | AUTO WAKE-UP FROM HALT MODE      |    |

|        | ORTS                             |    |

|        | INTRODUCTION                     |    |

|        | FUNCTIONAL DESCRIPTION           |    |

|        | I/O PORT IMPLEMENTATION          |    |

|        | LOW POWER MODES                  |    |

|        | INTERRUPTS                       |    |

| 9.6    | I/O PORT REGISTER CONFIGURATIONS | 50 |

## **6.4 SYSTEM INTEGRITY MANAGEMENT (SI)**

The System Integrity Management block contains the Low Voltage Detector (LVD) and Auxiliary Voltage Detector (AVD) functions. It is managed by the SICSR register.

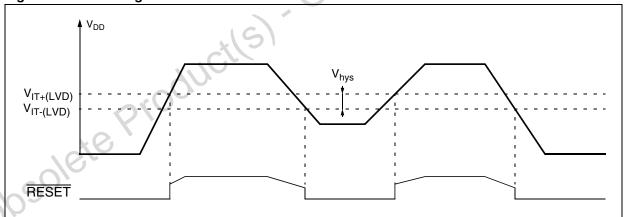

#### 6.4.1 Low Voltage Detector (LVD)

The Low Voltage Detector function (LVD) generates a static reset when the  $V_{DD}$  supply voltage is below a  $V_{IT-(LVD)}$  reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The  $V_{IT-(LVD)}$  reference value for a voltage drop is lower than the  $V_{IT+(LVD)}$  reference value for poweron in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD Reset circuitry generates a reset when  $V_{DD}$  is below:

- $-V_{IT+(LVD)}$  when  $V_{DD}$  is rising

- $-V_{IT-(LVD)}$  when  $V_{DD}$  is falling

The LVD function is illustrated in Figure 15.

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{IT\text{-}(LVD)}$ , the MCU can only be in two modes:

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a Low Voltage Detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

#### **Notes**

The LVD allows the device to be used without any external RESET circuitry.

The LVD is an optional function which can be selected by option byte.

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

Figure 15. Low Voltage Detector vs Reset

**577**

## **INTERRUPTS** (Cont'd)

**Table 8. Dedicated Interrupt Instruction Set**

| Instruction | New Description                 | Function/Example      | l1 | Н | 10 | N | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|---|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |   |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | l1 | Н | 10 | N | Z | С |

| JRM         | Jump if I1:0 = 11 (level 3)     | I1:0 = 11 ?           |    |   |    |   |   |   |

| JRNM        | Jump if I1:0 <> 11              | l1:0 <> 11 ?          |    |   |    |   |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | l1 | Н | 10 | N | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |   | G |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  | 1 |   | 1 |

| TRAP        | Software trap                   | Software NMI          | 1  |   | .1 |   |   |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  | 5 |   |   |

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

**477**

#### WINDOW WATCHDOG (Cont'd)

The application program must write in the WDGCR register at regular intervals during normal operation to prevent an MCU reset. This operation must occur only when the counter value is lower than the window register value. The value to be stored in the WDGCR register must be between FFh and C0h (see Figure 2):

Enabling the watchdog:

When Software Watchdog is selected (by option byte), the watchdog is disabled after a reset. It is enabled by setting the WDGA bit in the WDGCR register, then it cannot be disabled again except by a reset.

When Hardware Watchdog is selected (by option byte), the watchdog is always active and the WDGA bit is not used.

Controlling the downcounter:

This downcounter is free-running: It counts down even if the watchdog is disabled. When the watchdog is enabled, the T6 bit must be set to prevent generating an immediate reset.

The T[5:0] bits contain the number of increments which represents the time delay before the watchdog produces a reset (see Figure 2. Approximate Timeout Duration). The timing varies

between a minimum and a maximum value due to the unknown status of the prescaler when writing to the WDGCR register (see Figure 3).

The window register (WDGWR) contains the high limit of the window: To prevent a reset, the downcounter must be reloaded when its value is lower than the window register value and greater than 3Fh. Figure 4 describes the window watchdog process.

**Note:** The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is cleared).

Watchdog Reset on Halt option

If the watchdog is activated and the watchdog reset on halt option is selected, then the HALT instruction will generate a Reset.

#### 10.1.4 Using Halt Mode with the WDG

If Halt mode with Watchdog is enabled by option byte (no watchdog reset on HALT instruction), it is recommended before executing the HALT instruction to refresh the WDG counter, to avoid an unexpected WDG reset immediately after waking up the microcontroller.

# PWM AUTO-RELOAD TIMER (Cont'd)

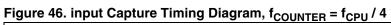

#### **10.4 16-BIT TIMER**

#### 10.4.1 Introduction

The timer consists of a 16-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (*input capture*) or generation of up to two output waveforms (*output compare* and *PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the CPU clock prescaler.

Some ST7 devices have two on-chip 16-bit timers. They are completely independent, and do not share any resources. They are synchronized after a MCU reset as long as the timer clock frequencies are not modified.

This description covers one or two 16-bit timers. In ST7 devices with two timers, register names are prefixed with TA (Timer A) or TB (Timer B).

#### 10.4.2 Main Features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4 or 8

- Overflow status flag and maskable interrupt

- External clock input (must be at least four times slower than the CPU clock speed) with the choice of active edge

- 1 or 2 Output Compare functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- 1 or 2 Input Capture functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One Pulse mode

- Reduced Power Mode

- 5 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2, EXTCLK)\*

The Block Diagram is shown in Figure 48.

\*Note: Some timer pins may not be available (not bonded) in some ST7 devices. Refer to the device pin out description.

When reading an input signal on a non-bonded pin, the value will always be '1'.

### 10.4.3 Functional Description

#### 10.4.3.1 Counter

The main block of the Programmable Timer is a 16-bit free running upcounter and its associated 16-bit registers. The 16-bit registers are made up of two 8-bit registers called high and low.

Counter Register (CR):

- Counter High Register (CHR) is the most significant byte (MS Byte).

- Counter Low Register (CLR) is the least significant byte (LS Byte).

Alternate Counter Register (ACR)

- Alternate Counter High Register (ACHR) is the most significant byte (MS Byte).

- Alternate Counter Low Register (ACLR) is the least significant byte (LS Byte).

These two read-only 16-bit registers contain the same value but with the difference that reading the ACLR register does not clear the TOF bit (Timer overflow flag), located in the Status register, (SR), (see note at the end of paragraph titled 16-bit read sequence).

Writing in the CLR register or ACLR register resets the free running counter to the FFFCh value. Both counters have a reset value of FFFCh (this is the only value which is reloaded in the 16-bit timer). The reset value of both counters is also FFFCh in One Pulse mode and PWM mode.

The timer clock depends on the clock control bits of the CR2 register, as illustrated in Table 17 Clock Control Bits. The value in the counter register repeats every 131072, 262144 or 524288 CPU clock cycles depending on the CC[1:0] bits.

The timer frequency can be f<sub>CPU</sub>/2, f<sub>CPU</sub>/4, f<sub>CPU</sub>/8 or an external frequency.

### 8-BIT TIMER (Cont'd)

#### 10.5.7 Register Description

Each Timer is associated with three control and status registers, and with six data registers (8-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

# **CONTROL REGISTER 1 (CR1)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = ICIE Input Capture Interrupt Enable.

0: Interrupt is inhibited.

Josolete P

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable*. 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.* 0: Interrupt is inhibited.

A timer interrupt is enabled whenever the TOF bit of the SR register is set.

Bit 4 = FOLV2 Forced Output Compare 2.

This bit is set and cleared by software.

0: No effect on the OCMP2 pin.

1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

Bit 3 = FOLV1 Forced Output Compare 1.

This bit is set and cleared by software.

0: No effect on the OCMP1 pin.

1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

#### Bit 2 = **OLVL2** Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode.

### Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

#### Bit 0 = **OLVL1** Output Level 1.

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

# SERIAL PERIPHERAL INTERFACE (cont'd) 10.6.5 Error Flags

# 10.6.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device's SS pin is pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

- A read access to the SPICSR register while the MODF bit is set.

- 2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the  $\overline{SS}$  pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

In a slave device, the MODF bit can not be set, but in a multimaster configuration the device can be in slave mode with the MODF bit set.

The MODF bit indicates that there might have been a multimaster conflict and allows software to handle this using an interrupt routine and either perform a reset or return to an application default state.

#### 10.6.5.2 Overrun Condition (OVR)

An overrun condition occurs when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

#### 10.6.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 10.6.3.2 "Slave Select Management".

**Note:** A "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the CPU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

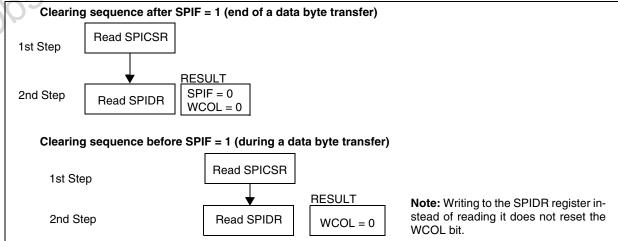

Clearing the WCOL bit is done through a software sequence (see Figure 75).

Figure 75. Clearing the WCOL Bit (Write Collision Flag) Software Sequence

# SERIAL PERIPHERAL INTERFACE (cont'd) 10.6.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI. SPI interrupt events cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                        |

| HALT | SPI registers are frozen. In HALT mode, the SPI is inactive. SPI operation resumes when the device is woken up by an interrupt with "exit from HALT mode" capability. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetching). If several data are received before the wake-up event, then an overrun error is generated. This error can be detected after the fetch of the interrupt routine that woke up the Device. |

# 10.6.6.1 Using the SPI to wake up the device from Halt mode

In slave configuration, the SPI is able to wake up the device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

Note: When waking up from HALT mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring

the SPI from HALT mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

Caution: The SPI can wake up the device from HALT mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the device enters HALT mode. So, if Slave selection is configured as external (see Section 10.6.3.2), make sure the master drives a low level on the SS pin when the slave enters HALT mode

#### 10.6.7 Interrupts

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of<br>Transfer Event | SPIF          |                          |                      | Yes                  |

| Master Mode<br>Fault Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          |                      |                      |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# $\textbf{LINSCI}^{\text{\tiny{TM}}} \textbf{ SERIAL COMMUNICATION INTERFACE (SCI Mode)} \ (\text{cont'd})$

#### 10.7.6 Low Power Modes

# 10.7.7 Interrupts

| Mode | Description                                                                                                |

|------|------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SCI. SCI interrupts cause the device to exit from Wait mode.                                  |

| HALT | SCI registers are frozen.<br>In Halt mode, the SCI stops transmitting/receiving until Halt mode is exited. |

| Interrupt Event                              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| Transmit Data Register Empty                 | TDRE          | TIE                      |                      |                      |

| Transmission Complete                        | TC            | TCIE                     |                      |                      |

| Received Data Ready to be Read               | RDRF          | RIF                      | Yes                  | No                   |

| Overrun Error or LIN<br>Synch Error Detected | OR/<br>LHE    | TILL                     | J.C                  |                      |

| Idle Line Detected                           | IDLE          | ILIE                     |                      |                      |

| Parity Error                                 | PE            | PIE                      |                      |                      |

| LIN Header Detection                         | LHDF          | LHIE                     |                      |                      |

The SCI interrupt events are connected to the same interrupt vector (see Interrupts chapter).

These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd) CONTROL REGISTER 1 (SCICR1)

Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |                   |    | 0   |

|----|----|------|---|------|-------------------|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE <sup>1)</sup> | PS | PIE |

<sup>&</sup>lt;sup>1)</sup>This bit has a different function in LIN mode, please refer to the LIN mode register description.

#### Bit 7 = **R8** Receive data bit 8

This bit is used to store the 9th bit of the received word when M = 1.

#### Bit 6 = **T8** Transmit data bit 8

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** Disabled for low power consumption When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.

0: SCI enabled

1: SCI prescaler and outputs disabled

#### Bit 4 = M Word length

This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = **WAKE** Wake-Up method

This bit determines the SCI Wake-Up method, it is set or cleared by software.

0: Idle Line

1: Address Mark

**Note:** If the LINE bit is set, the WAKE bit is deactivated and replaced by the LHDM bit.

### Bit 2 = PCE Parity control enable

This bit is set and cleared by software. It selects the hardware parity control (generation and detection for byte parity, detection only for LIN parity).

0: Parity control disabled

1: Parity control enabled

### Bit 1 = **PS** Parity selection

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity will be selected after the current byte.

0: Even parity

1: Odd parity

#### Bit 0 = **PIE** Parity interrupt enable

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). The parity error involved can be a byte parity error (if bit PCE is set and bit LPE is reset) or a LIN parity error (if bit PCE is set and bit LPE is set).

0: Parity error interrupt disabled

1: Parity error interrupt enabled

## LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

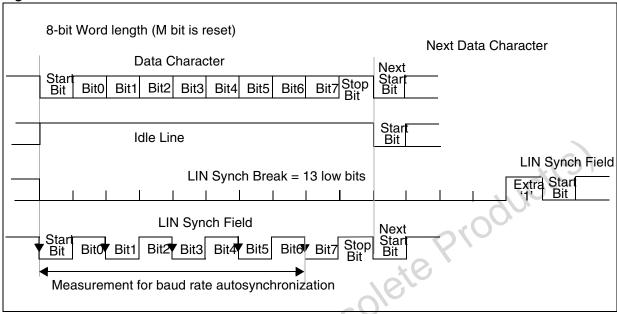

## Figure 80. LIN Characters

Obsolete Product(s)

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

### 10.8.4 Functional Description

The block diagram of the Serial Control Interface, is shown in Figure 88 on page 153. It contains seven dedicated registers:

- Three control registers (SCICR1, SCICR2 and SCICR3)

- A status register (SCISR)

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 10.7.8 for the definitions of each bit.

#### 10.8.4.1 Serial Data Format

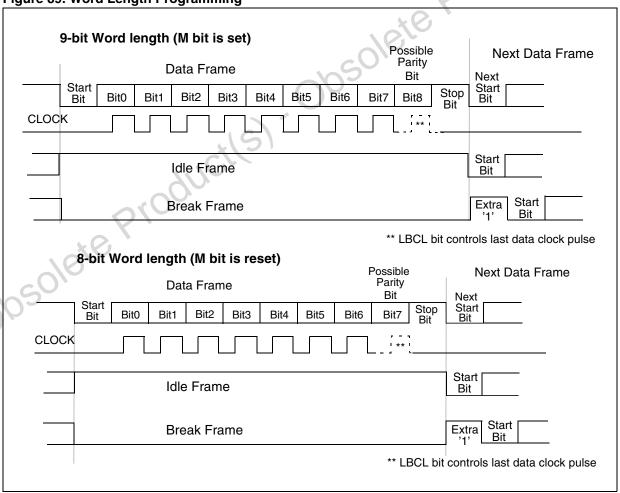

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 89).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

Figure 89. Word Length Programming

## beCAN CONTROLLER (Cont'd)

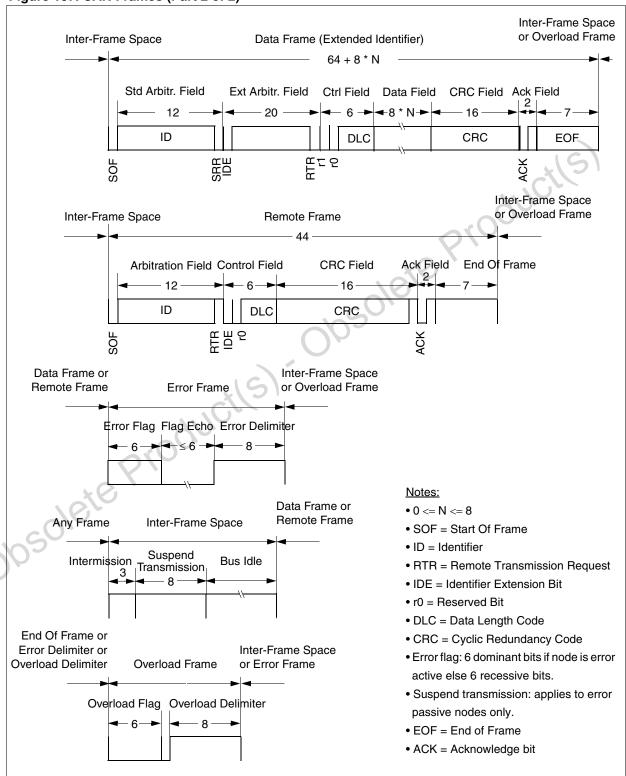

Figure 107. CAN Frames (Part 2 of 2)

#### Figure 114. Workaround 2

```

a, CRFR

Ld

And

a,#3

Ср

a,#2

; test FMP=2 ?

_RELEASE

Jrne

; if not release

Btjf

CMSR, #5, RELEASE; test if reception on going.

; if not release

Obsolete Product(s) - Obsolete Product(s)

```

## beCAN CONTROLLER (Cont'd)

### MAILBOX DATA LENGTH CONTROL REGIS-TER (MDLC)

All bits of this register is write protected when the mailbox is not in empty state.

Read / Write

Reset Value: xxxx xxxx (xxh)

| 7 |   |   |   |      |      |      | 0    |

|---|---|---|---|------|------|------|------|

| 0 | 0 | 0 | 0 | DLC3 | DLC2 | DLC1 | DLC0 |

Bit 7 = Reserved, must be kept cleared.

Obsolete Products). A mes

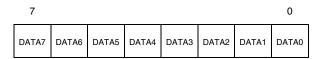

## MAILBOX DATA REGISTERS (MDAR[7:0])

All bits of this register are write protected when the mailbox is not in empty state.

Read / Write

Reset Value: Undefined

Bits 7:0 = **DATA[7:0]** *Data*

A data byte of the message. A message can con-

# beCAN CONTROLLER (Cont'd)

Table 32. beCAN Control and Status Page - Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Name | 7     | 6    | 5     | 4     | 3      | 2     | 1      | 0          |

|-------------------|------------------|-------|------|-------|-------|--------|-------|--------|------------|

| COL               | CMCR             |       | ABOM | AWUM  | NART  | RFLM   | TXFP  | SLEEP  | INRQ       |

| 68h               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 1      | 0          |

| COL               | CMSR             |       |      | REC   | TRAN  | WKUI   | ERRI  | SLAK   | INAK       |

| 69h               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 1      | 0          |

| CAb               | CTSR             |       |      | TXOK1 | TXOK0 |        |       | RQCP1  | RQCP0      |

| 6Ah               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 0      | <b>C</b> 0 |

| CDI               | CTPR             |       | LOW1 | LOW0  |       | TME1   | TME0  |        | CODE0      |

| 6Bh               | Reset Value      | 0     | 0    | 0     | 1     | 1      | 1     | 0      | 0          |

| COL               | CRFR             |       |      | RFOM  | FOVR  | FULL   | .0    | FMP1   | FMP0       |

| 6Ch               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 0      | 0          |

| CDI               | CIER             | WKUIE | 0    | 0     | 0     | FOVIE0 | FFIE0 | FMPIE0 | TMEIE      |

| 6Dh               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 0      | 0          |

| CE!               | CDGR             |       |      |       | -0    | RX     | SAMP  | SILM   | LBKM       |

| 6Eh               | Reset Value      | 0     | 0    | 0     | 0     | 1      | 1     | 0      | 0          |

| CE!               | CFPSR            |       |      |       | NO.   |        | FPS2  | FPS1   | FPS0       |

| 6Fh               | Reset Value      | 0     | 0    | 0     | 0     | 0      | 0     | 0      | 0          |

Table 33. beCAN Mailbox Pages - Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Name |        | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 70h               | MFMI             | FMI7   | FMI6   | FMI5   | FMI4   | FMI3   | FMI2   | FMI1   | FMI0   |

| Receive           | Reset Value      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 70h               | MCSR             |        |        | TERR   | ALST   | TXOK   | RQCP   | ABRQ   | TXRQ   |

| Transmit          | Reset Value      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 71h               | MDLC             | 0      |        |        |        | DLC3   | DLC2   | DLC1   | DLC0   |

| 7 111             | Reset Value      | Х      | Х      | х      | Х      | х      | х      | х      | х      |

| 72h               | MIDR0            |        | IDE    | RTR    | STID10 | STID9  | STID8  | STID7  | STID6  |

| 7211              | Reset Value      | x      | х      | х      | х      | х      | х      | х      | х      |

| 73h               | MIDR1            | STID5  | STID4  | STID3  | STID2  | STID1  | STID0  | EXID17 | EXID16 |

| 7311              | Reset Value      | X      | Х      | х      | X      | х      | х      | х      | х      |

| 74h               | MIDR2            | EXID15 | EXID14 | EXID13 | EXID12 | EXID11 | EXID10 | EXID9  | EXID8  |

| 7411              | Reset Value      | X      | Х      | х      | X      | х      | х      | х      | х      |

| 75h               | MIDR3            | EXID7  | EXID6  | EXID5  | EXID4  | EXID3  | EXID2  | EXID1  | EXID0  |

| 75h               | Reset Value      | x      | х      | х      | х      | х      | х      | х      | х      |

| 76h:7Dh           | MDAR[0:7]        | MDAR7  | MDAR6  | MDAR5  | MDAR4  | MDAR3  | MDAR2  | MDAR1  | MDAR0  |

| 76h:7Dh           | Reset Value      | X      | х      | х      | х      | х      | х      | х      | х      |

#### 12 ELECTRICAL CHARACTERISTICS

#### 12.1 PARAMETER CONDITIONS

Unless otherwise specified, all voltages are referred to  $V_{SS}$ .

#### 12.1.1 Minimum and Maximum Values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25^{\circ}\text{C}$  and  $T_A = T_A \text{max}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 12.1.2 Typical Values

Unless otherwise specified, typical data is based on  $T_A = 25^{\circ}C$ ,  $V_{DD} = 5V$  (for the  $4.5V \le V_{DD} \le 5.5V$  voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

#### 12.1.3 Typical Curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

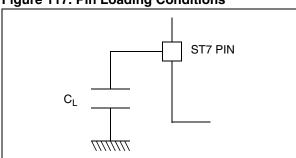

#### 12.1.4 Loading Capacitor

The loading conditions used for pin parameter measurement are shown in Figure 117.

Figure 117. Pin Loading Conditions

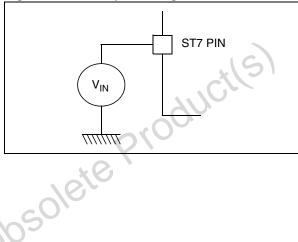

#### 12.1.5 Pin Input Voltage

The input voltage measurement on a pin of the device is described in Figure 118.

Figure 118. Pin input voltage

## **CLOCK CHARACTERISTICS (Cont'd)**

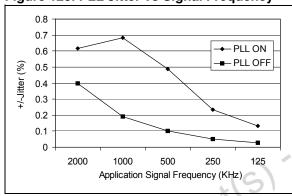

#### 12.5.4 PLL Characteristics

Operating conditions:  $V_{DD}$  3.8 to 5.5V @  $T_A$  0 to 70°C<sup>1)</sup> or  $V_{DD}$  4.5 to 5.5V @  $T_A$  -40 to 125°C

| Symbol                               | Parameter                 | Conditions                                                       | Min | Тур      | Max | Unit |

|--------------------------------------|---------------------------|------------------------------------------------------------------|-----|----------|-----|------|

| V <sub>DD(PLL)</sub>                 | PLL Voltage Range         | $T_A = 0 \text{ to } +70^{\circ}\text{C}$                        | 3.8 |          | 5.5 |      |

|                                      |                           | T <sub>A</sub> = -40 to +125°C                                   | 4.5 |          |     |      |

| f <sub>OSC</sub>                     | PLL input frequency range |                                                                  | 2   |          | 4   | MHz  |

| Δ f <sub>CPU</sub> /f <sub>CPU</sub> | PLL jitter <sup>1)</sup>  | $f_{OSC} = 4 \text{ MHz}, V_{DD} = 4.5 \text{ to } 5.5 \text{V}$ |     | - Note 2 |     | %    |

|                                      |                           | $f_{OSC} = 2 \text{ MHz}, V_{DD} = 4.5 \text{ to } 5.5 \text{V}$ |     |          |     | /6   |

#### Notes:

- 1. Data characterized but not tested.

- 2. Under characterization

Figure 123. PLL Jitter vs Signal Frequency<sup>1)</sup>

#### Notes:

1. Measurement conditions:  $f_{CPU} = 4 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$

The user must take the PLL jitter into account in the application (for example in serial communication or sampling of high frequency signals). The PLL jitter is a periodic effect, which is integrated over several CPU cycles. Therefore, the longer the period of the application signal, the less it is impacted by the PLL jitter.

Figure 123 shows the PLL jitter integrated on application signals in the range 125 kHz to 2 MHz. At frequencies of less than 125 kHz, the jitter is negligible.

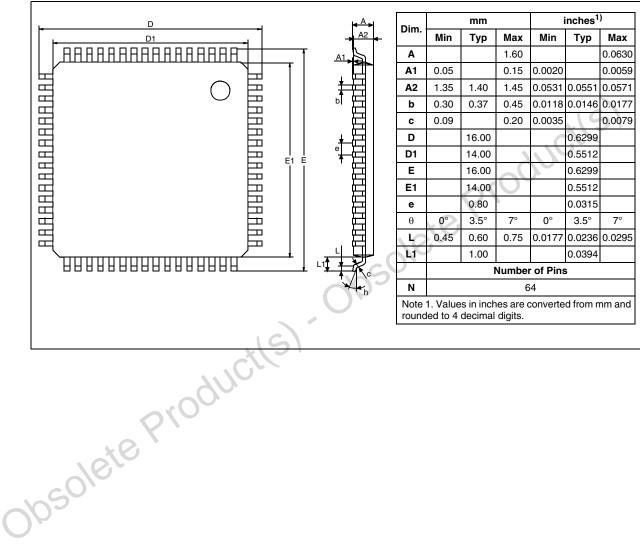

## 13 PACKAGE CHARACTERISTICS

## 13.1 PACKAGE MECHANICAL DATA

Figure 146. 64-Pin Low Profile Quad Flat Package (14x14)