Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, LINbusSCI, SPI                                               |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561k9tc |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| F      | Pin n° |      |                   |      | Level    |        | Port        |       |     |         |                     |    | Main      |                                 |                    |                     |

|--------|--------|------|-------------------|------|----------|--------|-------------|-------|-----|---------|---------------------|----|-----------|---------------------------------|--------------------|---------------------|

| P64    | P44    | P32  | Pin Name          |      | Pin Name |        | ut          | out   |     | In      | out                 |    | Out       | put                             | function<br>(after | Alternate function  |

| LQFP64 | LQFI   | LQFI |                   | Type | Input    | Output | float       | ndm   | int | ana     | OD                  | РР | reset)    |                                 |                    |                     |

| 54     | 36     | 26   | PD4 / SCI2_RDI    | I/O  | CT       |        | x           |       | ei3 |         | х                   | х  | Port D4   | LINSCI2 Receive Data in-<br>put |                    |                     |

| 55     | 37     | 27   | V <sub>SSA</sub>  | S    |          |        |             |       |     |         |                     |    | Analog G  | iround Voltage                  |                    |                     |

| 56     | 38     | 28   | V <sub>SS_0</sub> | S    |          |        |             |       |     |         |                     |    | Digital G | round Voltage                   |                    |                     |

| 57     | 39     | 29   | V <sub>DDA</sub>  | Ι    |          |        |             |       |     |         |                     |    | Analog F  | eference Voltage for ADC        |                    |                     |

| 58     | 40     | 30   | V <sub>DD_0</sub> | S    |          |        |             |       |     |         |                     |    | Digital M | ain Supply Voltage              |                    |                     |

| 59     | 41     | 31   | PD5 / SCI2_TDO    | I/O  | CT       |        | x           | х     |     |         | х                   | х  | Port D5   | LINSCI2 Transmit Data<br>output |                    |                     |

| 60     | 42     | 32   | RESET             | I/O  | $C_T$    |        |             |       |     |         | Т                   |    | Top prior | ity non maskable interrupt.     |                    |                     |

| 61     | 43     | -    | PD6 / AIN10       | I/O  | $C_T$    |        | Х           | X ei3 |     | X ei3 X |                     | Х  | Х         | Х                               | Port D6            | ADC Analog Input 10 |

| 62     | 44     | -    | PD7 / AIN11       | I/O  | $C_T$    |        | X ei3 X X X |       | Х   | Port D7 | ADC Analog Input 11 |    |           |                                 |                    |                     |

| 63     | -      | -    | PF6               | I/O  | $T_T$    |        | X X X X     |       | Х   | Port F6 |                     |    |           |                                 |                    |                     |

| 64     | -      | -    | PF7               | I/O  | $T_{T}$  |        | Х           | Х     |     |         | Х                   | X  | Port F7   |                                 |                    |                     |

#### Notes:

1. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

2. Input mode can be used for general purpose I/O, output mode only for CANTX.

3. OSC1 and OSC2 pins connect a crystal/ceramic resonator, or an external source to the on-chip oscillator; see Section 6 and Section 12.5 "CLOCK AND TIMING CHARACTERISTICS" for more details.

4. On the chip, each I/O port has eight pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

#### SYSTEM INTEGRITY MANAGEMENT (Cont'd)

#### 6.4.2 Auxiliary Voltage Detector (AVD)

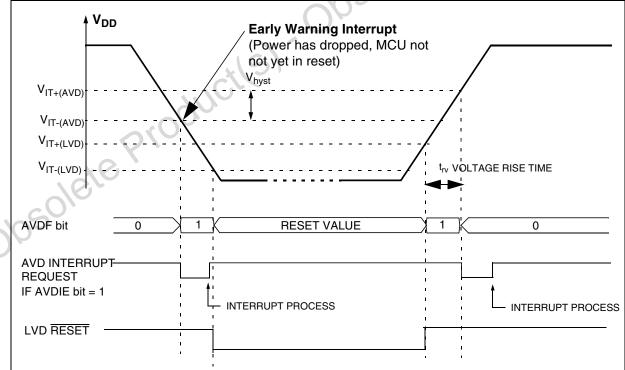

The Voltage Detector function (AVD) is based on an analog comparison between a V<sub>IT-(AVD)</sub> and V<sub>IT+(AVD)</sub> reference value and the V<sub>DD</sub> main supply. The V<sub>IT-(AVD)</sub> reference value for falling voltage is lower than the V<sub>IT+(AVD)</sub> reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (AVDF) in the SICSR register. This bit is read only.

**Caution**: The AVD function is active only if the LVD is enabled through the option byte.

#### 6.4.2.1 Monitoring the V<sub>DD</sub> Main Supply

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the  $V_{IT+(AVD)}$  or  $V_{IT-(AVD)}$  threshold (AVDF bit toggles).

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut

#### Figure 16. Using the AVD to Monitor V<sub>DD</sub>

down safely before the LVD resets the microcontroller. See Figure 16.

The interrupt on the rising edge is used to inform the application that the  $V_{DD}$  warning state is over.

If the voltage rise time  $t_{rv}$  is less than 256 or 4096 CPU cycles (depending on the reset delay selected by option byte), no AVD interrupt will be generated when  $V_{\rm IT+(AVD)}$  is reached.

If t<sub>rv</sub> is greater than 256 or 4096 cycles then:

- If the AVD interrupt is enabled before the  $V_{IT+(AVD)}$  threshold is reached, then two AVD interrupts will be received: The first when the AVDIE bit is set and the second when the threshold is reached.

- If the AVD interrupt is enabled after the V<sub>IT+(AVD)</sub> threshold is reached, then only one AVD interrupt occurs.

# **7 INTERRUPTS**

#### 7.1 INTRODUCTION

The ST7 enhanced interrupt management provides the following features:

- Hardware interrupts

- Software interrupt (TRAP)

- Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 2 non maskable events: RESET, TRAP

- 1 maskable Top Level Event: TLI

- This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) ST7 interrupt controller.

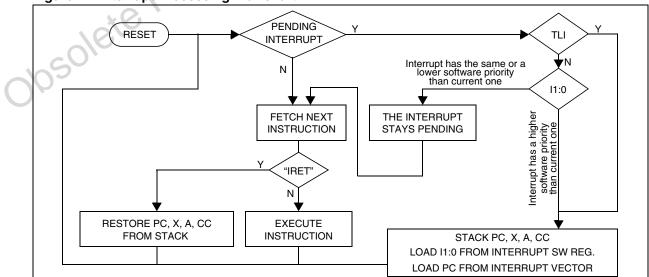

#### 7.2 MASKING AND PROCESSING FLOW

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of

each interrupt vector (see Table 6). The processing flow is shown in Figure 17.

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to "Interrupt Mapping" table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note**: As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.

#### Table 7. Interrupt Software Priority Levels

| Interrupt software priority   | Level | 11 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | . ★   | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

# Figure 17. Interrupt Processing Flowchart

57

#### INTERRUPTS (Cont'd)

#### 7.6.2 Register Description

#### EXTERNAL INTERRUPT CONTROL REGISTER 0 (EICR0) Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| IS31 | IS30 | IS21 | IS20 | IS11 | IS10 | IS01 | IS00 |

#### Bits 7:6 = IS3[1:0] ei3 sensitivity

The interrupt sensitivity, defined using the IS3[1:0] bits, is applied to the ei3 external interrupts:

| IS31 | IS30 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

#### Bits 5:4 = IS2[1:0] ei2 sensitivity

The interrupt sensitivity, defined using the IS2[1:0] bits, is applied to the ei2 external interrupts:

| IS21 | IS20 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when 11 and 10 of the CC register are both set to 1 (level 3).

#### Bits 3:2 = IS1[1:0] ei1 sensitivity

The interrupt sensitivity, defined using the IS1[1:0] bits, is applied to the ei1 external interrupts:

| IS11 | IS10 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

#### Bits 1:0 = ISO[1:0] ei0 sensitivity

The interrupt sensitivity, defined using the ISO[1:0] bits, is applied to the ei0 external interrupts:

| IS01 | IS00 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

#### EXTERNAL INTERUPT CONTROL REGISTER 1 (EICR1)

Read/Write Reset Value: 0000 0000 (00h)

| 7 | 0 |   |   |   |   |      | 0    |

|---|---|---|---|---|---|------|------|

| 0 | 0 | 0 | 0 | 0 | 0 | TLIS | TLIE |

Blts 7:2 = Reserved

Bit 1 = TLIS Top Level Interrupt sensitivity This bit configures the TLI edge sensitivity. It can be set and cleared by software only when TLIE bit is cleared.

- 0: Falling edge

- 1: Rising edge

Bit 0 =**TLIE** *Top Level Interrupt enable* This bit allows to enable or disable the TLI capability on the dedicated pin. It is set and cleared by software.

- 0: TLI disabled

- 1: TLI enabled

#### Notes:

- A parasitic interrupt can be generated when clearing the TLIE bit.

- In some packages, the TLI pin is not available. In this case, the TLIE bit must be kept low to avoid parasitic TLI interrupts.

## WINDOW WATCHDOG (Cont'd)

# Figure 36. Exact Timeout Duration ( $t_{min}$ and $t_{max}$ )

#### WHERE:

$t_{min0} = (LSB + 128) \times 64 \times t_{OSC2}$  $t_{max0} = 16384 \text{ x } t_{OSC2}$

$t_{OSC2}$  = 125ns if  $f_{OSC2}$  = 8 MHz

CNT = Value of T[5:0] bits in the WDGCR register (6 bits)

MSB and LSB are values from the table below depending on the timebase selected by the TB[1:0] bits in the MCCSR register

| TB1 Bit<br>(MCCSR Reg.) | TB0 Bit<br>(MCCSR Reg.) | Selected MCCSR<br>Timebase | MSB | LSB |

|-------------------------|-------------------------|----------------------------|-----|-----|

| 0                       | 0                       | 2ms                        | 4   | 59  |

| 0                       | 1                       | 4ms                        | 8   | 53  |

| 1                       | 0                       | 10ms                       | 20  | 35  |

| 1                       | 1                       | 25ms                       | 49  | 54  |

To calculate the minimum Watchdog Timeout (t<sub>min</sub>):

**IF** CNT <  $\left[\frac{MS}{4}\right]$

$$\begin{array}{|c|c|c|c|c|c|}\hline TB0 Bit & Selected MCCSR \\\hline Timebase & MSB & LSB \\\hline 0 & 2ms & 4 & 59 \\\hline 0 & 2ms & 4 & 59 \\\hline 1 & 4ms & 8 & 53 \\\hline 0 & 10ms & 20 & 35 \\\hline 1 & 25ms & 49 & 54 \\\hline \end{array}$$

the minimum Watchdog Timeout (t<sub>min</sub>):

$$\begin{array}{|c|c|c|c|c|}\hline B \\\hline B \\\hline B \\\hline ELSE t_{min} = t_{min0} + \begin{bmatrix} 16384 \times CNT \times t_{osc2} \\\hline 16384 \times (CNT - \begin{bmatrix} 4CNT \\ MSB \end{bmatrix}) + (192 + LSB) \times 64 \times \begin{bmatrix} 4CNT \\ MSB \end{bmatrix} \end{bmatrix} \times t_{osc2}$$

To calculate the maximum Watchdog Timeout (t<sub>max</sub>):

**IF** CNT

$$\leq \left[\frac{\text{MSB}}{4}\right]$$

**THEN**  $t_{\text{max}} = t_{\text{max0}} + 16384 \times \text{CNT} \times t_{\text{osc2}}$

**ELSE**  $t_{\text{max}} = t_{\text{max0}} + \left[16384 \times \left(\text{CNT} - \left[\frac{4\text{CNT}}{\text{MSB}}\right]\right) + (192 + \text{LSB}) \times 64 \times \left[\frac{4\text{CNT}}{\text{MSB}}\right]\right] \times t_{\text{osc2}}$

Note: In the above formulae, division results must be rounded down to the next integer value. Example:

With 2ms timeout selected in MCCSR register

| Min. Watchdog<br>Timeout (ms)<br>t <sub>min</sub> | Max. Watchdog<br>Timeout (ms)<br>t <sub>max</sub> |

|---------------------------------------------------|---------------------------------------------------|

| 1.496                                             | 2.048                                             |

| 128                                               | 128.552                                           |

|                                                   | Timeout (ms)<br>t <sub>min</sub><br>1.496         |

#### PWM AUTO-RELOAD TIMER (Cont'd)

**لركم**

#### **Output compare and Time base interrupt**

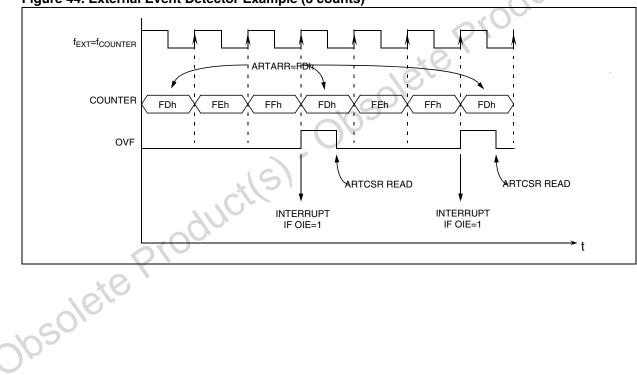

On overflow, the OVF flag of the ARTCSR register is set and an overflow interrupt request is generated if the overflow interrupt enable bit, OIE, in the ARTCSR register, is set. The OVF flag must be reset by the user software. This interrupt can be used as a time base in the application.

#### External clock and event detector mode

Using the  $f_{EXT}$  external prescaler input clock, the auto-reload timer can be used as an external clock event detector. In this mode, the ARTARR register is used to select the  $n_{EVENT}$  number of events to be counted before setting the OVF flag.

# n<sub>EVENT</sub> = 256 - ARTARR

**Caution:** The external clock function is not available in HALT mode. If HALT mode is used in the application, prior to executing the HALT instruction, the counter must be disabled by clearing the TCE bit in the ARTCSR register to avoid spurious counter increments.

Figure 44. External Event Detector Example (3 counts)

#### **ON-CHIP PERIPHERALS** (Cont'd)

#### **10.3.3 Register Description**

#### CONTROL / STATUS REGISTER (ARTCSR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |     |     |     |     |      |     | 0   |  |

|------|-----|-----|-----|-----|------|-----|-----|--|

| EXCL | CC2 | CC1 | CC0 | TCE | FCRL | OIE | OVF |  |

#### Bit 7 = **EXCL** External Clock

This bit is set and cleared by software. It selects the input clock for the 7-bit prescaler.

0: CPU clock. 1: External clock.

Bit 6:4 = **CC[2:0]** Counter Clock Control These bits are set and cleared by software. They determine the prescaler division ratio from  $f_{INPUT}$ .

| <b>f</b> COUNTER         | With f <sub>INPUT</sub> =8 MHz | CC2 | CC1 | CC0 |

|--------------------------|--------------------------------|-----|-----|-----|

| f <sub>INPUT</sub>       | 8 MHz                          | 0   | 0   | 0   |

| f <sub>INPUT</sub> / 2   | 4 MHz                          | 0   | 0   | 1   |

| f <sub>INPUT</sub> / 4   | 2 MHz                          | 0   | 1   | 0   |

| f <sub>INPUT</sub> / 8   | 1 MHz                          | 0   | 1   | 1   |

| f <sub>INPUT</sub> / 16  | 500 kHz                        | 1   | 0   | 0   |

| f <sub>INPUT</sub> / 32  | 250 kHz                        | 1   | 0   | 1   |

| f <sub>INPUT</sub> / 64  | 125 kHz                        | 1   | 1   | 0   |

| f <sub>INPUT</sub> / 128 | 62.5 kHz                       | 1   | 1   | 1   |

#### Bit 3 = **TCE** *Timer Counter Enable*

This bit is set and cleared by software. It puts the timer in the lowest power consumption mode. 0: Counter stopped (prescaler and counter frozen).

1: Counter running.

#### Bit 2 = **FCRL** Force Counter Re-Load

This bit is write-only and any attempt to read it will yield a logical zero. When set, it causes the contents of ARTARR register to be loaded into the counter, and the content of the prescaler register to be cleared in order to initialize the timer before starting to count.

#### Bit 1 = **OIE** Overflow Interrupt Enable

This bit is set and cleared by software. It allows to enable/disable the interrupt which is generated when the OVF bit is set.

0: Overflow Interrupt disable.

1: Overflow Interrupt enable.

# Bit 0 = **OVF** Overflow Flag

This bit is set by hardware and cleared by software reading the ARTCSR register. It indicates the transition of the counter from FFh to the ARTARR value.

#### 0: New transition not yet reached 1: Transition reached

# COUNTER ACCESS REGISTER (ARTCAR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CA7 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 |

Bit 7:0 = CA[7:0] Counter Access Data

These bits can be set and cleared either by hardware or by software. The ARTCAR register is used to read or write the auto-reload counter "on the fly" (while it is counting).

# AUTO-RELOAD REGISTER (ARTARR)

# Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| AR7 | AR6 | AR5 | AR4 | AR3 | AR2 | AR1 | AR0 |

#### Bit 7:0 = AR[7:0] Counter Auto-Reload Data

These bits are set and cleared by software. They are used to hold the auto-reload value which is automatically loaded in the counter when an overflow occurs. At the same time, the PWM output levels are changed according to the corresponding OPx bit in the PWMCR register.

This register has two PWM management functions:

- Adjusting the PWM frequency

- Setting the PWM duty cycle resolution

#### PWM Frequency vs Resolution:

| ARTARR     | Resolution | f <sub>P\</sub> | мм        |

|------------|------------|-----------------|-----------|

| value      | Resolution | Min             | Max       |

| 0          | 8-bit      | ~0.244 kHz      | 31.25 kHz |

| [ 0127 ]   | > 7-bit    | ~0.244 kHz      | 62.5 kHz  |

| [ 128191 ] | > 6-bit    | ~0.488 kHz      | 125 kHz   |

| [ 192223 ] | > 5-bit    | ~0.977 kHz      | 250 kHz   |

| [ 224239 ] | > 4-bit    | ~1.953 kHz      | 500 kHz   |

# 16-BIT TIMER (Cont'd) CONTROL/STATUS REGISTER (CSR)

Read/Write (bits 7:3 read only)

Reset Value: xxxx x0xx (xxh)

| 7    |      |     |      |      |      |   | 0 |

|------|------|-----|------|------|------|---|---|

| ICF1 | OCF1 | TOF | ICF2 | OCF2 | TIMD | 0 | 0 |

#### Bit 7 = **ICF1** Input Capture Flag 1.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP1 pin or the counter has reached the OC2R value in PWM mode. To clear this bit, first read the SR register, then read or write the low byte of the IC1R (IC1LR) register.

#### Bit 6 = **OCF1** Output Compare Flag 1.

0: No match (reset value).

1: The content of the free running counter has matched the content of the OC1R register. To clear this bit, first read the SR register, then read or write the low byte of the OC1R (OC1LR) register.

Bit 5 = **TOF** *Timer Overflow Flag.*

- 0: No timer overflow (reset value).

- 1: The free running counter rolled over from FFFFh to 0000h. To clear this bit, first read the SR register, then read or write the low byte of the CR (CLR) register.

**Note:** Reading or writing the ACLR register does not clear TOF.

#### Bit 4 = ICF2 Input Capture Flag 2.

- 0: No input capture (reset value).

- 1: An input capture has occurred on the ICAP2 pin. To clear this bit, first read the SR register, then read or write the low byte of the IC2R (IC2LR) register.

Bit 3 = OCF2 Output Compare Flag 2.

- 0: No match (reset value).

- 1: The content of the free running counter has matched the content of the OC2R register. To clear this bit, first read the SR register, then read or write the low byte of the OC2R (OC2LR) register.

#### Bit 2 = **TIMD** *Timer disable.*

This bit is set and cleared by software. When set, it freezes the timer prescaler and counter and disabled the output functions (OCMP1 and OCMP2 pins) to reduce power consumption. Access to the timer registers is still available, allowing the timer configuration to be changed, or the counter reset, while it is disabled.

0: Timer enabled

1: Timer prescaler, counter and outputs disabled

Bits 1:0 = Reserved, must be kept cleared.

#### 10.5 8-BIT TIMER (TIM8)

#### 10.5.1 Introduction

The timer consists of a 8-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (*input capture*) or generation of up to two output waveforms (*output compare* and *PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the clock prescaler.

#### 10.5.2 Main Features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4, 8 or f<sub>OSC2</sub> divided by 8000.

- Overflow status flag and maskable interrupt

- Output compare functions with

- 2 dedicated 8-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Input capture functions with

- 2 dedicated 8-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One pulse mode

- Reduced Power Mode

- 4 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2)\*

The Block Diagram is shown in Figure 59.

\*Note: Some timer pins may not be available (not bonded) in some ST7 devices. Refer to the device pin out description.

When reading an input signal on a non-bonded pin, the value will always be '1'.

#### 10.5.3 Functional Description

One Pulse mode and PWM mode.

#### 10.5.3.1 Counter

The main block of the Programmable Timer is a 8bit free running upcounter and its associated 8-bit registers.

These two read-only 8-bit registers contain the same value but with the difference that reading the ACTR register does not clear the TOF bit (Timer overflow flag), located in the Status register, (SR).

Writing in the CTR register or ACTR register resets the free running counter to the FCh value. Both counters have a reset value of FCh (this is the only value which is reloaded in the 8-bit timer). The reset value of both counters is also FCh in

The timer clock depends on the clock control bits of the CR2 register, as shown in Table 19 Clock Control Bits. The value in the counter register repeats every 512, 1024, 2048 or 20480000  $f_{CPU}$  clock cycles depending on the CC[1:0] bits. The timer frequency can be  $f_{CPU}/2$ ,  $f_{CPU}/4$ ,  $f_{CPU}/8$  or  $f_{OSC2}$  /8000.

For example, if  $f_{OSC2}$ /8000 is selected, and  $f_{OSC2} = 8$  MHz, the timer frequency will be 1 ms. Refer to Table 19 on page 105.

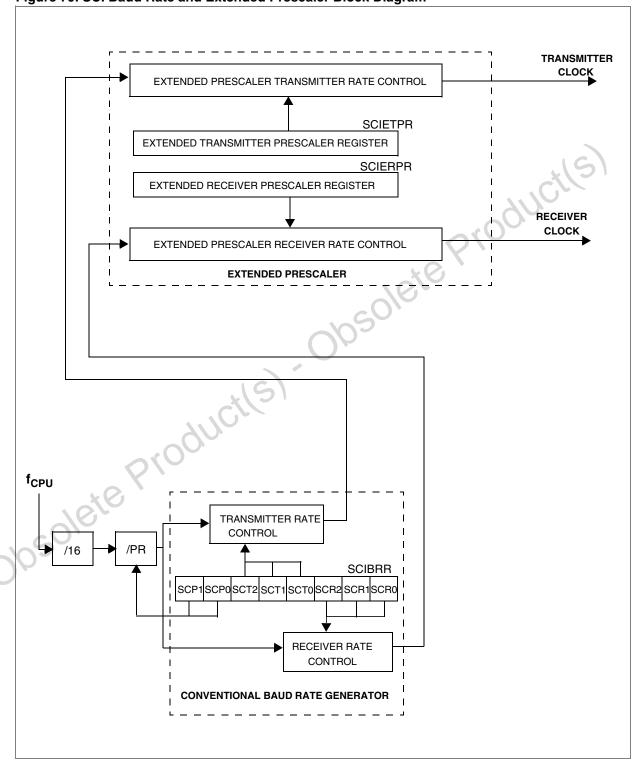

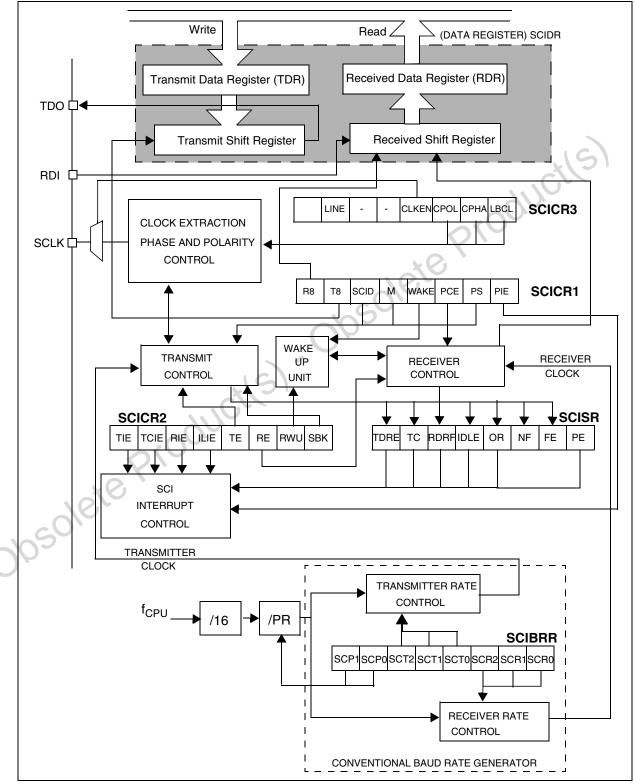

# LINSCI<sup>™</sup> SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont<sup>\*</sup>d) Figure 79. SCI Baud Rate and Extended Prescaler Block Diagram

57

129/265

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### 10.7.9.4 LIN Error Detection

#### LIN Header Error Flag

The LIN Header Error Flag indicates that an invalid LIN Header has been detected.

When a LIN Header Error occurs:

- The LHE flag is set

- An interrupt is generated if the RIE bit is set and the I[1:0] bits are cleared in the CCR register.

If autosynchronization is enabled (LASE bit = 1), this can mean that the LIN Synch Field is corrupted, and that the SCI is in a blocked state (LSF bit is set). The only way to recover is to reset the LSF bit and then to clear the LHE bit.

- The LHE bit is reset by an access to the SCISR register followed by a read of the SCIDR register.

#### LHE/OVR Error Conditions

When Auto Resynchronization is disabled (LASE bit = 0), the LHE flag detects:

- That the received LIN Synch Field is not equal to 55h.

- That an overrun occurred (as in standard SCI mode)

- Furthermore, if LHDM is set it also detects that a LIN Header Reception Timeout occurred (only if LHDM is set).

When the LIN auto-resynchronization is enabled (LASE bit = 1), the LHE flag detects:

- That the deviation error on the Synch Field is outside the LIN specification which allows up to +/-15.5% of period deviation between the slave and master oscillators.

- A LIN Header Reception Timeout occurred.

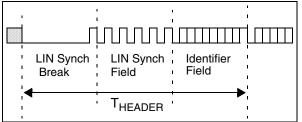

If T<sub>HEADER</sub> > T<sub>HEADER\_MAX</sub> then the LHE flag is set. Refer to Figure 6. (only if LHDM is set to 1)

- An overflow during the Synch Field Measurement, which leads to an overflow of the divider registers. If LHE is set due to this error then the SCI goes into a blocked state (LSF bit is set).

- That an overrun occurred on Fields other than the Synch Field (as in standard SCI mode)

#### **Deviation Error on the Synch Field**

The deviation error is checking by comparing the current baud rate (relative to the slave oscillator) with the received LIN Synch Field (relative to the master oscillator). Two checks are performed in parallel:

The first check is based on a measurement between the first falling edge and the last falling edge of the Synch Field. Let us refer to this period deviation as D:

If the LHE flag is set, it means that:

D > 15.625%

If LHE flag is not set, it means that:

D < 16.40625%

If  $15.625\% \le D < 16.40625\%$ , then the flag can be either set or reset depending on the dephasing between the signal on the RDI line and the CPU clock.

The second check is based on the measurement of each bit time between both edges of the Synch Field: this checks that each of these bit times is large enough compared to the bit time of the current baud rate.

When LHE is set due to this error then the SCI goes into a blocked state (LSF bit is set).

#### LIN Header Time-out Error

When the LIN Identifier Field Detection Method is used (by configuring LHDM to 1) or when LIN auto-resynchronization is enabled (LASE bit = 1), the LINSCI automatically monitors the  $T_{HEADER\_MAX}$  condition given by the LIN protocol.

If the entire Header (up to and including the STOP bit of the LIN Identifier Field) is not received within the maximum time limit of 57 bit times then a LIN Header Error is signalled and the LHE bit is set in the SCISR register.

#### Figure 82. LIN Header Reception Timeout

The time-out counter is enabled at each break detection. It is stopped in the following conditions:

- A LIN Identifier Field has been received

- An LHE error occurred (other than a timeout error).

- A software reset of LSF bit (transition from high to low) occurred during the analysis of the LIN Synch Field or

If LHE bit is set due to this error during the LIN Synchr Field (if LASE bit = 1) then the SCI goes into a blocked state (LSF bit is set).

### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

#### LIN HEADER LENGTH REGISTER (LHLR)

Read Only

Reset Value: 0000 0000 (00h).

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| LHL7 | LHL6 | LHL5 | LHL4 | LHL3 | LHL2 | LHL1 | LHL0 |

**Note:** In LIN Slave mode when LASE = 1 or LHDM = 1, the LHLR register is accessible at the address of the SCIERPR register.

Otherwise this register is always read as 00h.

#### Bits 7:0 = LHL[7:0] LIN Header Length.

This is a read-only register, which is updated by hardware if one of the following conditions occurs: - After each break detection, it is loaded with "FFh".

- If a timeout occurs on  $T_{\mbox{\scriptsize HEADER}},$  it is loaded with 00h.

- After every successful LIN Header reception (at the same time than the setting of LHDF bit), it is loaded with a value (LHL) which gives access to the number of bit times of the LIN header length ( $T_{HEADER}$ ). The coding of this value is explained below:

#### LHL Coding:

$T_{HEADER_MAX} = 57$

LHL(7:2) represents the mantissa of (57 -  $T_{HEAD-ER}$ )

| LHL(1:0) represents | the fraction (57 | 7 - T <sub>HEADER</sub> ) |

|---------------------|------------------|---------------------------|

|---------------------|------------------|---------------------------|

| LHL[7:2] | Mantissa<br>(57 - T <sub>HEADER</sub> )      | Mantissa<br>(T <sub>HEADER</sub> )                                                                                                                                                                     |

|----------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0h       | 0                                            | 57                                                                                                                                                                                                     |

| 1h       | 1                                            | 56                                                                                                                                                                                                     |

| 0        |                                              |                                                                                                                                                                                                        |

| 39h      | 56                                           | 1                                                                                                                                                                                                      |

| 3Ah      | 57                                           | 0                                                                                                                                                                                                      |

| 3Bh      | 58                                           | Never Occurs                                                                                                                                                                                           |

|          |                                              |                                                                                                                                                                                                        |

| 3Eh      | 62                                           | Never Occurs                                                                                                                                                                                           |

| 3Fh      | 63                                           | Initial value                                                                                                                                                                                          |

|          | 0h<br>1h<br><br>39h<br>3Ah<br>3Bh<br><br>3Eh | LHL[7:2]         (57 - T <sub>HEADER</sub> )           0h         0           1h         1               39h         56           3Ah         57           3Bh         58               3Eh         62 |

| LHL[1:0] | Fraction (57 - T <sub>HEADER</sub> ) |

|----------|--------------------------------------|

| 0h       | 0                                    |

| 1h       | 1/4                                  |

| 2h       | 1/2                                  |

| 3h       | 3/4                                  |

#### Example of LHL coding:

Example 1: LHL =  $33h = 001100 \ 11b$ LHL(7:3) = 1100b = 12dLHL(1:0) = 11b = 3dThis leads to: Mantissa (57 - T<sub>HEADER</sub>) = 12dFraction (57 - T<sub>HEADER</sub>) = 3/4 = 0.75Therefore: (57 - T<sub>HEADER</sub>) = 12.75dand T<sub>HEADER</sub> = 44.25d

Example 2: 57 -  $T_{HEADER} = 36.21d$ LHL(1:0) = rounded(4\*0.21d) = 1d LHL(7:2) = Mantissa (36.21d) = 36d = 24h Therefore LHL(7:0) = 10010001 = 91h

Example 3:

$57 - T_{HEADER} = 36.90d$ LHL(1:0) = rounded(4\*0.90d) = 4d The carry must be propagated to the matissa: LHL(7:2) = Mantissa (36.90d) + 1 = 37d = Therefore LHL(7:0) = 10110000 = A0h

**/**

# LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

### Figure 88. SCI Block Diagram

5

#### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

#### 10.8.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

When the transmit enable bit (TE) is set, the data in the transmit shift register is output on the TDO pin and the corresponding clock pulses are output on the SCLK pin.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 89).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to send an idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

1. An access to the SCISR register

2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit or after the break frame) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

1. An access to the SCISR register

2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 89).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### **Idle Characters**

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

#### LIN Transmission

The same procedure has to be applied for LIN Master transmission with the following differences:

- Clear the M bit to configure 8-bit word length.

- Set the LINE bit to enter LIN master mode. In this case, setting the SBK bit sends 13 low bits.

#### 10.9.3 Operating Modes

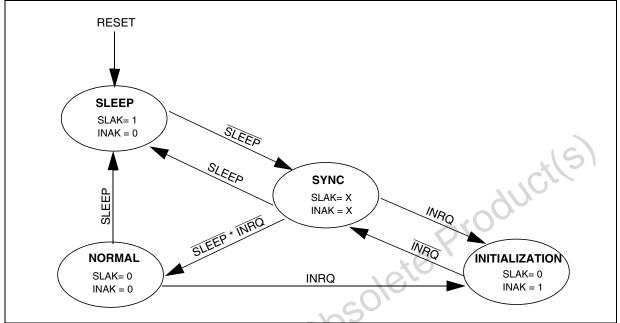

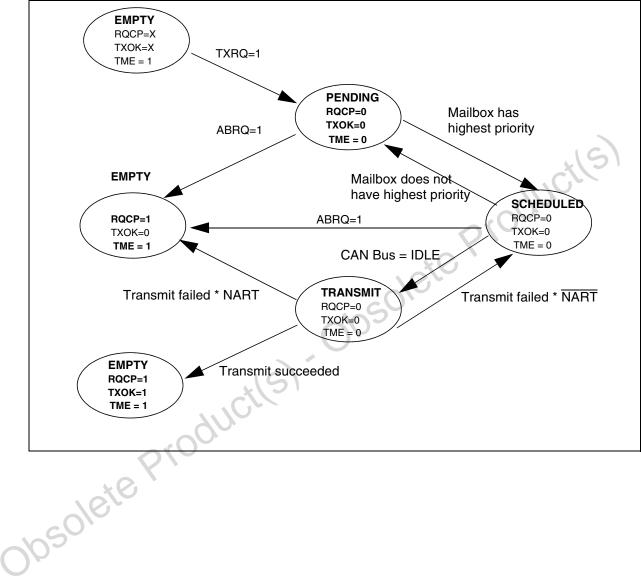

The beCAN has three main operating modes: Initialization, Normal and Sleep. After a hardware reset, beCAN is in Sleep mode to reduce power consumption. The software requests beCAN to enter Initialization or Sleep mode by setting the INRQ or SLEEP bits in the CMCR register. Once the mode has been entered, beCAN confirms it by setting the INAK or SLAK bits in the CMSR register. When neither INAK nor SLAK are set, beCAN is in Normal mode. Before entering Normal mode beCAN always has to **synchronize** on the CAN bus. To synchronize, beCAN waits until the CAN bus is idle, this means 11 consecutive recessive bits have been monitored on CANRX.

#### 10.9.3.1 Initialization Mode

The software initialization can be done while the hardware is in Initialization mode. To enter this mode the software sets the INRQ bit in the CMCR register and waits until the hardware has confirmed the request by setting the INAK bit in the CMSR register.

To leave Initialization mode, the software clears the INQR bit. beCAN has left Initialization mode once the INAK bit has been cleared by hardware.

While in Initialization mode, all message transfers to and from the CAN bus are stopped and the status of the CAN bus output CANTX is recessive (high).

Entering Initialization Mode does not change any of the configuration registers.

To initialize the CAN Controller, software has to set up the Bit Timing registers and the filter banks. If a filter bank is not used, it is recommended to leave it non active (leave the corresponding FACT bit cleared).

#### 10.9.3.2 Normal Mode

Once the initialization has been done, the software must request the hardware to enter Normal mode, to synchronize on the CAN bus and start reception and transmission. Entering Normal mode is done by clearing the INRQ bit in the CMCR register and waiting until the hardware has confirmed the request by clearing the INAK bit in the CMSR register. Afterwards, the beCAN synchronizes with the data transfer on the CAN bus by waiting for the occurrence of a sequence of 11 consecutive recessive bits (= Bus Idle) before it can take part in bus activities and start message transfer.

The initialization of the filter values is independent from Initialization mode but must be done while the filter bank is not active (corresponding FACTx bit cleared). The filter bank scale and mode configuration must be configured in initialization mode.

57

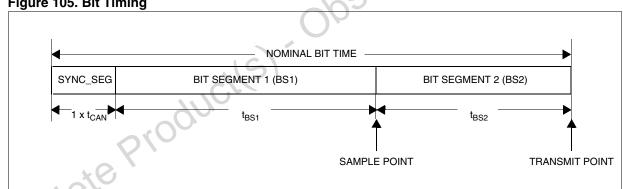

#### 10.9.4.6 Bit Timing

The bit timing logic monitors the serial bus-line and performs sampling and adjustment of the sample point by synchronizing on the start-bit edge and resynchronizing on the following edges.

Its operation may be explained simply by splitting nominal bit time into three segments as follows:

- Synchronization segment (SYNC SEG): a bit change is expected to occur within this time segment. It has a fixed length of one time quantum (1 x t<sub>CAN</sub>).

- Bit segment 1 (BS1): defines the location of the sample point. It includes the PROP\_SEG and PHASE SEG1 of the CAN standard. Its duration is programmable between 1 and 16 time guanta but may be automatically lengthened to compensate for positive phase drifts due to differences in the frequency of the various nodes of the network.

- Bit segment 2 (BS2): defines the location of the transmit point. It represents the PHASE SEG2 of the CAN standard. Its duration is programmable between 1 and 8 time quanta but may also be automatically shortened to compensate for negative phase drifts.

- Resynchronization Jump Width (RJW): defines an upper bound to the amount of lengthening or shortening of the bit segments. It is programmable between 1 and 4 time quanta.

To guarantee the correct behaviour of the CAN controller, SYNC\_SEG + BS1 + BS2 must be greater than or equal to 5 time quanta.

For a detailed description of the CAN resynchronization mechanism and other bit timing configuration constraints, please refer to the Bosch CAN standard 2.0.

As a safeguard against programming errors, the configuration of the Bit Timing Registers CBTR1 and CBTR0 is only possible while the device is in Initialization mode.

#### Figure 105. Bit Timing

<u>لرک</u>

#### Figure 106. CAN Frames (Part 1of 2)

Bit 4 = **TXOK0** *Transmission OK for mailbox 0* - Read

This bit is set by hardware when the transmission request on mailbox 0 has been completed successfully. Please refer to Figure 7.

This bit is cleared by hardware when mailbox 0 is requested for transmission or when the software clears the RQCP0 bit.

Bits 3:2 = Reserved. Forced to 0 by hardware.

Bit 1 = **RQCP1** *Request Completed for Mailbox 1* - Read/Clear

This bit is set by hardware to signal that the last request for mailbox 1 has been completed. The request could be a transmit or an abort request.

This bit is cleared by software.

#### Bit 0 = **RQCP0** Request Completed for Mailbox 0 - Read/Clear

This bit is set by hardware to signal that the last request for mailbox 0 has been completed. The request could be a transmit or an abort request.

This bit is cleared by software.

# CAN TRANSMIT PRIORITY REGISTER (CTPR)

All bits of this register are read only.

Reset Value: 0000 1100 (0Ch)

| 7 | 010  |      |   |      |      |   |      |  |

|---|------|------|---|------|------|---|------|--|

| 0 | LOW1 | LOW0 | 0 | TME1 | TME0 | 0 | CODE |  |

Bit 7 = Reserved. Forced to 0 by hardware.

Bit 6 = **LOW1** *Lowest Priority Flag for Mailbox 1* - Read

This bit is set by hardware when more than one

mailbox are pending for transmission and mailbox 1 has the lowest priority.

Bit 5 = **LOW0** *Lowest Priority Flag for Mailbox 0* - Read

This bit is set by hardware when more than one mailbox are pending for transmission and mailbox 0 has the lowest priority.

**Note**: These bits are set to zero when only one mailbox is pending.

Bit 4 = Reserved. Forced to 0 by hardware.

#### Bit 3 = TME1 Transmit Mailbox 1 Empty

- Read This bit is set by hardware when no transmit request is pending for mailbox 1.

# Bit 2 = **TME0** *Transmit Mailbox 0 Empty* - Read

This bit is set by hardware when no transmit request is pending for mailbox 0.

#### Bit 1:0 = CODE Mailbox Code

- Read

In case at least one transmit mailbox is free, the code value is equal to the number of the next transmit mailbox free.

In case all transmit mailboxes are pending, the code value is equal to the number of the transmit mailbox with the lowest priority.

#### CAN RECEIVE FIFO REGISTERS (CRFR) Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |      |      |      |   |      | 0    |

|---|---|------|------|------|---|------|------|

| 0 | 0 | RFOM | FOVR | FULL | 0 | FMP1 | FMP0 |

**Note**: To clear a bit in this register, software must write a "1" to the bit.

Bits 7:6 = Reserved. Forced to 0 by hardware.

# Bit 5 = **RFOM** *Release FIFO Output Mailbox* - Read/Set

Set by software to release the output mailbox of the FIFO. The output mailbox can only be released when at least one message is pending in the FIFO. Setting this bit when the FIFO is empty has no effect. If more than one message are pending in the FIFO, the software has to release the output mailbox to access the next message.

Cleared by hardware when the output mailbox has been released.

### Bit 4 = FOVR FIFO Overrun

- Read/Clear This bit is set by hardware when a new message has been received and passed the filter while the FIFO was full.

This bit is cleared by software.

#### Bit 3 = FULL FIFO Full

- Read/Clear

Set by hardware when three messages are stored in the FIFO.

This bit can be cleared by software writing a one to this bit or releasing the FIFO by means of RFOM.

Bit 2 = Reserved. Forced to 0 by hardware.

Bits 1:0 = **FMP[1:0]** *FIFO Message Pending* - Read

These bits indicate how many messages are pending in the receive FIFO.

FMP is increased each time the hardware stores a new message in to the FIFO. FMP is decreased each time the software releases the output mailbox by setting the RFOM bit.

#### CAN INTERRUPT ENABLE REGISTER (CIER)

All bits of this register are set and cleared by software.

Read / Write Reset Value: 0000 0000 (00h) 7 0

| WKUIE | 0 | 0 | 0 | FOVIE0 | FFIE0 | FMPIE0 | TMEIE |

|-------|---|---|---|--------|-------|--------|-------|

|       |   |   | Y |        |       |        |       |

Bit 7 = **WKUIE** *Wake-Up Interrupt Enable* 0: No interrupt when WKUI is set.

1: Interrupt generated when WKUI bit is set.

Bits 6:4 = Reserved. Forced to 0 by hardware.

Bit 3 = FOVIE FIFO Overrun Interrupt Enable

- 0: No interrupt when FOVR bit is set.

- 1: Interrupt generated when FOVR bit is set.

Bit 2 = **FFIE** *FIFO Full Interrupt Enable*

0: No interrupt when FULL bit is set.

1: Interrupt generated when FULL bit is set.

Bit 1 = **FMPIE** *FIFO Message Pending Interrupt Enable*

- 0: No interrupt on FMP[1:0] bits transition from 00b to 01b.

- 1: Interrupt generated on FMP[1:0] bits transition from 00b to 01b.

Bit 0 = **TMEIE** *Transmit Mailbox Empty Interrupt Enable*

0: No interrupt when RQCPx bit is set.

1: Interrupt generated when RQCPx bit is set.

57

# beCAN CONTROLLER (Cont'd) MAILBOX FILTER MATCH INDEX (MFMI)

This register is read only.

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| FMI7 | FMI6 | FMI5 | FMI4 | FMI3 | FMI2 | FMI1 | FMI0 |

#### Bits 7:0 = **FMI**[7:0] *Filter Match Index*

This register contains the index of the filter the message stored in the mailbox passed through. For more details on identifier filtering please refer to Section 0.1.4.3 - Filter Match Index paragraph.

**Note**: This register is implemented only in receive mailboxes. In transmit mailboxes, the MCSR register is mapped at this location.

# MAILBOX IDENTIFIER REGISTERS (MIDR[3:0])

Read / Write Reset Value: Undefined MIDR0

| 7 |     |     |        |       |       |       | 0     |  |

|---|-----|-----|--------|-------|-------|-------|-------|--|

| 0 | IDE | RTR | STID10 | STID9 | STID8 | STID7 | STID6 |  |

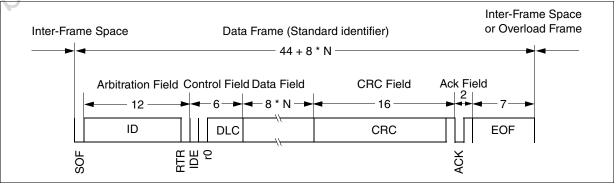

Bit 7 = Reserved. Forced to 0 by hardware.

#### Bit 6 = IDE Extended Identifier

This bit defines the identifier type of message in the mailbox.

0: Standard identifier.

1: Extended identifier.

Bit 5 = RTR Remote Transmission Request

- 0: Data frame

- 1: Remote frame

Bits 4:0 = **STID[10:6]** *Standard Identifier* 5 most significant bits of the standard part of the identifier.

# MIDR1

| 7     |       |       |       |       |       |        | 0      |

|-------|-------|-------|-------|-------|-------|--------|--------|

| STID5 | STID4 | STID3 | STID2 | STID1 | STID0 | EXID17 | EXID16 |

Bits 7:2 = **STID**[5:0] *Standard Identifier* 6 least significant bits of the standard part of the identifier.

Bits 1:0 = **EXID[17:16]** *Extended Identifier* 2 most significant bits of the extended part of the identifier.

# MIDR2

| 7    |        | Ó     | 10     |        |        |        |       | 0     |

|------|--------|-------|--------|--------|--------|--------|-------|-------|

| EXID | 15 EXI | D14 I | EXID13 | EXID12 | EXID11 | EXID10 | EXID9 | EXID8 |

Bits 7:0 = **EXID[15:8]** *Extended Identifier*

Bits 15 to 8 of the extended part of the identifier.

#### MIDR3

| 7     |       |       |       |       |       |       | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EXID7 | EXID6 | EXID5 | EXID4 | EXID3 | EXID2 | EXID1 | EXID0 |

Bits 7:1 = **EXID[6:0]** *Extended Identifier* 6 least significant bits of the extended part of the identifier.