Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, LINbusSCI, SPI                                               |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 48                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561r6ta |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **1 DESCRIPTION**

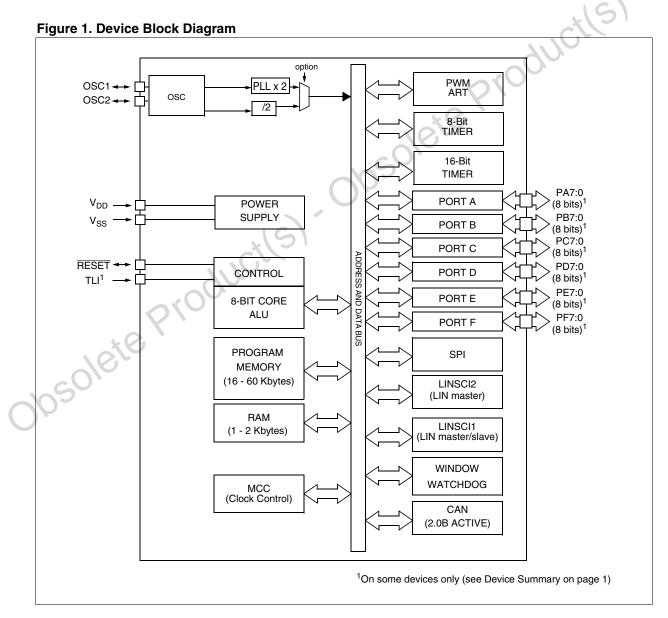

The ST72561 devices are members of the ST7 microcontroller family designed for mid-range applications with CAN (Controller Area Network) and LIN (Local Interconnect Network) interface.

All devices are based on a common industrystandard 8-bit core, featuring an enhanced instruction set and are available with Flash or ROM program memory. The ST7 family architecture offers both power and flexibility to software developers, enabling the design of highly efficient and compact application code. The on-chip peripherals include an A/D converter, a PWM Autoreload timer, 2 general purpose timers, 2 asynchronous serial interfaces, and an SPI interface.

For power economy, microcontroller can switch dynamically into WAIT, SLOW, Active-Halt, Auto Wake-up from HALT (AWU) or HALT mode when the application is in idle or stand-by state.

Typical applications are consumer, home, office and industrial products.

<u>لرکم</u>

#### SYSTEM INTEGRITY MANAGEMENT (Cont'd)

#### 6.4.2 Auxiliary Voltage Detector (AVD)

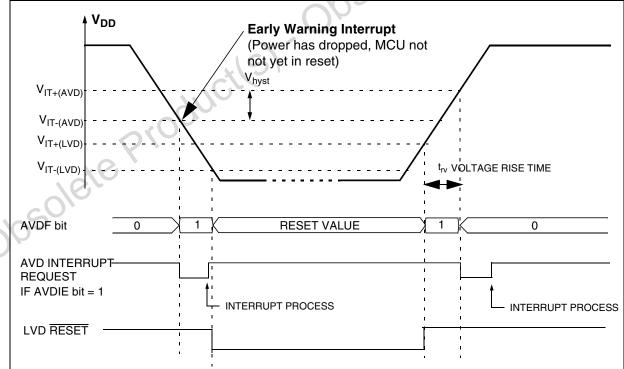

The Voltage Detector function (AVD) is based on an analog comparison between a  $V_{IT-(AVD)}$  and  $V_{IT+(AVD)}$  reference value and the  $V_{DD}$  main supply. The  $V_{IT-(AVD)}$  reference value for falling voltage is lower than the  $V_{IT+(AVD)}$  reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (AVDF) in the SICSR register. This bit is read only.

**Caution**: The AVD function is active only if the LVD is enabled through the option byte.

#### 6.4.2.1 Monitoring the V<sub>DD</sub> Main Supply

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the  $V_{IT+(AVD)}$  or  $V_{IT-(AVD)}$  threshold (AVDF bit toggles).

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut

#### Figure 16. Using the AVD to Monitor V<sub>DD</sub>

down safely before the LVD resets the microcontroller. See Figure 16.

The interrupt on the rising edge is used to inform the application that the  $V_{DD}$  warning state is over.

If the voltage rise time  $t_{rv}$  is less than 256 or 4096 CPU cycles (depending on the reset delay selected by option byte), no AVD interrupt will be generated when  $V_{\rm IT+(AVD)}$  is reached.

If  $t_{rv}$  is greater than 256 or 4096 cycles then:

- If the AVD interrupt is enabled before the  $V_{IT+(AVD)}$  threshold is reached, then two AVD interrupts will be received: The first when the AVDIE bit is set and the second when the threshold is reached.

- If the AVD interrupt is enabled after the V<sub>IT+(AVD)</sub> threshold is reached, then only one AVD interrupt occurs.

#### **INTERRUPTS** (Cont'd)

#### **Servicing Pending Interrupts**

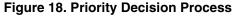

As several interrupts can be pending at the same time, the interrupt to be taken into account is determined by the following two-step process:

- the highest software priority interrupt is serviced,

- if several interrupts have the same software priority then the interrupt with the highest hardware priority is serviced first.

Figure 18 describes this decision process.

When an interrupt request is not serviced immediately, it is latched and then processed when its software priority combined with the hardware priority becomes the highest one.

**Note 1**: The hardware priority is exclusive while the software one is not. This allows the previous process to succeed with only one interrupt.

**Note 2**: RESET, TRAP and TLI can be considered as having the highest software priority in the decision process.

#### **Different Interrupt Vector Sources**

Two interrupt source types are managed by the ST7 interrupt controller: the non-maskable type (RESET, TRAP) and the maskable type (external or from internal peripherals).

#### Non-Maskable Sources

These sources are processed regardless of the state of the 11 and I0 bits of the CC register (see Figure 17). After stacking the PC, X, A and CC registers (except for RESET), the corresponding vector is loaded in the PC register and the 11 and I0 bits of the CC are set to disable interrupts (level 3). These sources allow the processor to exit HALT mode.

TRAP (Non Maskable Software Interrupt)

This software interrupt is serviced when the TRAP instruction is executed. It will be serviced according to the flowchart in Figure 17 as a TLI.

Caution: TRAP can be interrupted by a TLI.

## RESET

The RESET source has the highest priority in the ST7. This means that the first current routine has the highest software priority (level 3) and the highest hardware priority.

See the RESET chapter for more details.

#### **Maskable Sources**

Maskable interrupt vector sources can be serviced if the corresponding interrupt is enabled and if its own interrupt software priority (in ISPRx registers) is higher than the one currently being serviced (I1 and I0 in CC register). If any of these two conditions is false, the interrupt is latched and thus remains pending.

TLI (Top Level Hardware Interrupt)

This hardware interrupt occurs when a specific edge is detected on the dedicated TLI pin.

**Caution**: A TRAP instruction must not be used in a TLI service routine.

External Interrupts

External interrupts allow the processor to exit from HALT low power mode.

External interrupt sensitivity is software selectable through the External Interrupt Control register (EICR).

External interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

If several input pins of a group connected to the same interrupt line are selected simultaneously, these will be logically ORed.

Peripheral Interrupts

Usually the peripheral interrupts cause the MCU to exit from HALT mode except those mentioned in the "Interrupt Mapping" table.

A peripheral interrupt occurs when a specific flag is set in the peripheral status registers and if the corresponding enable bit is set in the peripheral control register.

The general sequence for clearing an interrupt is based on an access to the status register followed by a read or write to an associated register.

**Note**: The clearing sequence resets the internal latch. A pending interrupt (that is, waiting for being serviced) will therefore be lost if the clear sequence is executed.

30/265

## **8 POWER SAVING MODES**

#### **8.1 INTRODUCTION**

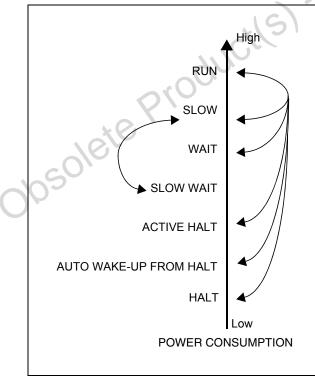

To give a large measure of flexibility to the application in terms of power consumption, five main power saving modes are implemented in the ST7 (see Figure 22):

- Slow

- Wait (and Slow-Wait)

- Active Halt

- Auto Wake-up From Halt (AWUFH)

- Halt

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 ( $f_{OSC2}$ ).

From RUN mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

#### Figure 22. Power Saving Mode Transitions

## 8.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

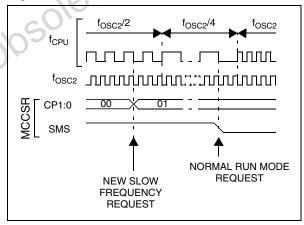

SLOW mode is controlled by three bits in the MCCSR register: the SMS bit which enables or disables Slow mode and two CPx bits which select the internal slow frequency (f<sub>CPU</sub>).

In this mode, the master clock frequency ( $f_{OSC2}$ ) can be divided by 2, 4, 8 or 16. The CPU and peripherals are clocked at this lower frequency ( $f_{CPU}$ ).

**Note**: SLOW-WAIT mode is activated by entering WAIT mode while the device is in SLOW mode.

#### Figure 23. SLOW Mode Clock Transitions

#### POWER SAVING MODES (Cont'd)

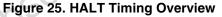

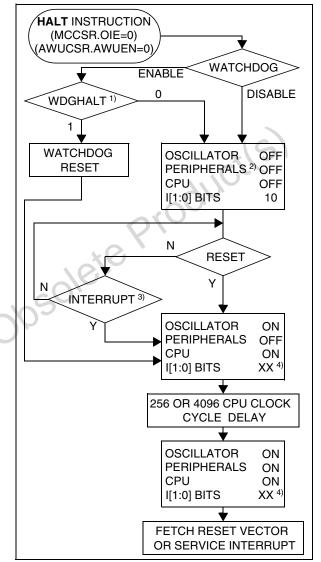

#### 8.4 HALT MODE

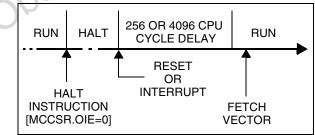

The HALT mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is cleared (see Section 10.2 on page 59 for more details on the MCCSR register) and when the AWUEN bit in the AWUCSR register is cleared.

The MCU can exit HALT mode on reception of either a specific interrupt (see Table 9, "Interrupt Mapping," on page 34) or a RESET. When exiting HALT mode by means of a RESET or an interrupt, the oscillator is immediately turned on and the 256 or 4096 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 26).

When entering HALT mode, the I[1:0] bits in the CC register are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In HALT mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with HALT mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET (see Section 10.1 on page 53 for more details).

#### Figure 26. HALT Mode Flow-chart

#### Notes:

**1.** WDGHALT is an option bit. See option byte section for more details.

**2.** Peripheral clocked with an external clock source can still be active.

**3.** Only some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 34 for more details.

**4.** Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

#### PWM AUTO-RELOAD TIMER (Cont'd)

**لركم**

#### **Output compare and Time base interrupt**

On overflow, the OVF flag of the ARTCSR register is set and an overflow interrupt request is generated if the overflow interrupt enable bit, OIE, in the ARTCSR register, is set. The OVF flag must be reset by the user software. This interrupt can be used as a time base in the application.

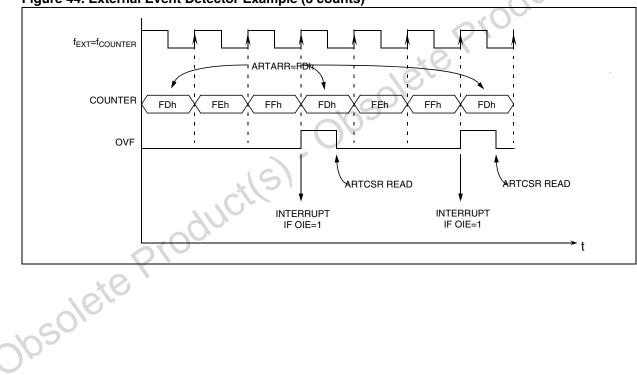

#### External clock and event detector mode

Using the  $f_{EXT}$  external prescaler input clock, the auto-reload timer can be used as an external clock event detector. In this mode, the ARTARR register is used to select the  $n_{EVENT}$  number of events to be counted before setting the OVF flag.

## n<sub>EVENT</sub> = 256 - ARTARR

**Caution:** The external clock function is not available in HALT mode. If HALT mode is used in the application, prior to executing the HALT instruction, the counter must be disabled by clearing the TCE bit in the ARTCSR register to avoid spurious counter increments.

Figure 44. External Event Detector Example (3 counts)

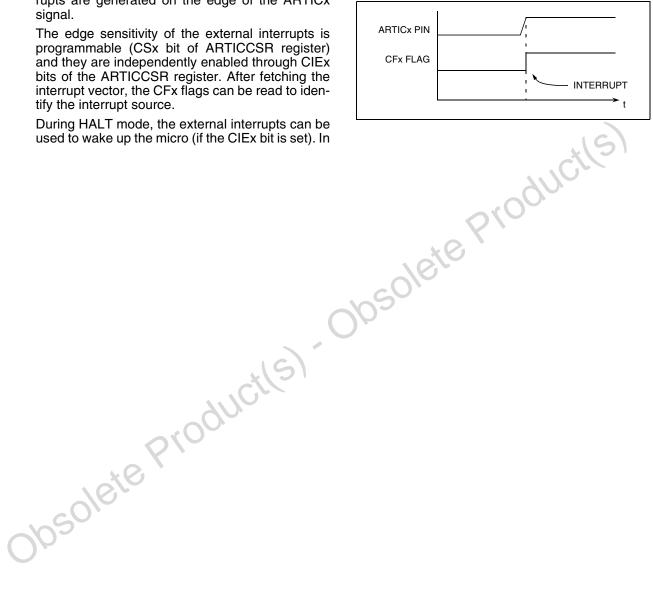

#### **External Interrupt Capability**

This mode allows the Input capture capabilities to be used as external interrupt sources. The interrupts are generated on the edge of the ARTICx signal.

The edge sensitivity of the external interrupts is programmable (CSx bit of ARTICCSR register) and they are independently enabled through CIEx bits of the ARTICCSR register. After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

this case, the interrupt synchronization is done directly on the ARTICx pin edge (Figure 47).

#### Figure 47. ART External Interrupt in Halt Mode

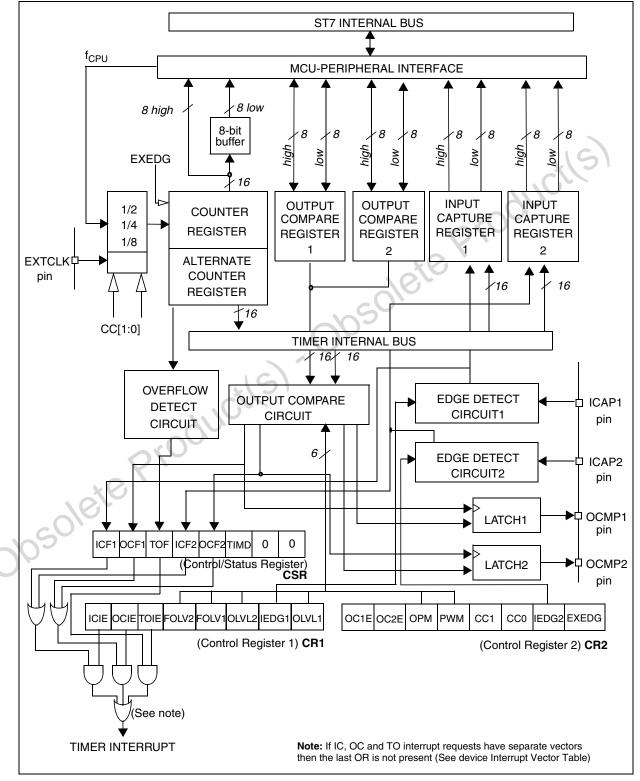

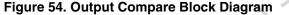

## 16-BIT TIMER (Cont'd)

#### Figure 48. Timer Block Diagram

## 16-BIT TIMER (Cont'd)

#### 10.4.3.3 Input Capture

In this section, the index, *i*, may be 1 or 2 because there are two input capture functions in the 16-bit timer.

The two 16-bit input capture registers (IC1R and IC2R) are used to latch the value of the free running counter after a transition is detected on the ICAP*i* pin (see Figure 52).

|      | MS Byte        | LS Byte        |

|------|----------------|----------------|

| ICiR | IC <i>i</i> HR | IC <i>i</i> LR |

IC*i*R register is a read-only register.

The active transition is software programmable through the IEDG*i* bit of Control Registers (CR*i*).

Timing resolution is one count of the free running counter:  $(f_{CPU}/CC[1:0])$ .

#### Procedure:

To use the input capture function select the following in the CR2 register:

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

- Select the edge of the active transition on the ICAP2 pin with the IEDG2 bit (the ICAP2 pin must be configured as floating input or input with pull-up without interrupt if this configuration is available).

And select the following in the CR1 register:

- Set the ICIE bit to generate an interrupt after an input capture coming from either the ICAP1 pin or the ICAP2 pin

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1pin must be configured as floating input or input with pullup without interrupt if this configuration is available).

When an input capture occurs:

- ICF*i* bit is set.

- The IC*i*R register contains the value of the free running counter on the active transition on the ICAP*i* pin (see Figure 53).

- A timer interrupt is generated if the ICIE bit is set and the I bit is cleared in the CC register. Otherwise, the interrupt remains pending until both conditions become true.

Clearing the Input Capture interrupt request (that is, clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set.

- 2. An access (read or write) to the ICiLR register.

#### Notes:

- 1. After reading the IC*i*HR register, transfer of input capture data is inhibited and ICF*i* will never be set until the IC*i*LR register is also read.

- 2. The IC/R register contains the free running counter value which corresponds to the most recent input capture.

- 3. The two input capture functions can be used together even if the timer also uses the two output compare functions.

- 4. In One Pulse mode and PWM mode only Input Capture 2 can be used.

- 5. The alternate inputs (ICAP1 and ICAP2) are always directly connected to the timer. So any transitions on these pins activates the input capture function. Moreover if one of the ICAP*i* pins is configured as an input and the second one as an output, an interrupt can be generated if the user toggles the output pin and if the ICIE bit is set.

This can be avoided if the input capture function i is disabled by reading the IC*i*HR (see note 1).

6. The TOF bit can be used with interrupt generation in order to measure events that go beyond the timer range (FFFFh).

**/رگ**

#### 16-BIT TIMER (Cont'd)

#### Notes:

- 1. After a processor write cycle to the OC*i*HR register, the output compare function is inhibited until the OCILR register is also written.

- 2. If the OCIE bit is not set, the OCMPi pin is a general I/O port and the OLVLi bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- 3. In both internal and external clock modes, OCFi and OCMPi are set while the counter value equals the OCiR register value (see Figure 55 on page 80 for an example with f<sub>CPU</sub>/2 and Figure 56 on page 80 for an example with f<sub>CPU</sub>/4). This behavior is the same in OPM or PWM mode.

- 4. The output compare functions can be used both for generating external events on the OCMPi pins even if the input capture mode is also used.

- 5. The value in the 16-bit OCiR register and the OLVi bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

#### Forced Compare Output capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMPi pin. The OLVi bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OCiE bit = 1). The OCFi bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVLi bits have no effect in both One Pulse mode and PWM mode.

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

#### How to operate the SPI in master mode

To operate the SPI in master mode, perform the following steps in order:

- Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 74 shows the four possible configurations. **Note:** The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits

Note: MSTR and SPE bits remain set only if SS is high).

Important note: if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account.

The transmit sequence begins when software writes a byte in the SPIDR register.

#### 10.6.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register

Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### 10.6.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- 1. Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see Figure 74). Note: The slave must have the same CPOL and CPHA settings as the master.

- Manage the  $\overline{SS}$  pin as described in Section 10.6.3.2 and Figure 72. If CPHA = 1 SS must be held low continuously. If CPHA = 0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- 2. Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

#### 10.6.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- A write or a read to the SPIDR register

Notes: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.6.5.2).

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

LIN PRESCALER FRACTION REGISTER (LPFR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |           |           |           | 0         |

|---|---|---|---|-----------|-----------|-----------|-----------|

| 0 | 0 | 0 | 0 | LPFR<br>3 | LPFR<br>2 | LPFR<br>1 | LPFR<br>0 |

Bits 7:4 = Reserved.

## Bits 3:0 = LPFR[3:0] Fraction of LDIV

These 4 bits define the fraction of the LIN Divider (LDIV):

| LPFR[3:0] | Fraction (LDIV) |

|-----------|-----------------|

| 0h        | 0               |

| 1h        | 1/16            |

|           |                 |

| Eh        | 14/16           |

| Fh        | 15/16           |

1. When initializing LDIV, the LPFR register must be written first. Then, the write to the LPR register will effectively update LDIV and so the clock generation.

2. In LIN Slave mode, if the LPR[7:0] register is equal to 00h, the transceiver and receiver input clocks are switched off.

## Examples of LDIV coding:

Example 1: LPR = 27d and LPFR = 12d

This leads to:

Mantissa (LDIV) = 27d

Fraction (LDIV) = 12/16 = 0.75dTherefore LDIV = 27.75d

Example 2: LDIV = 25.62dThis leads to: LPFR = rounded(16\*0.62d) = rounded(9.92d) = 10d = Ah LPR = mantissa (25.620d) = 25d = 1Bh

Example 3: LDIV = 25.99d This leads to: LPFR = rounded(16\*0.99d) = rounded(15.84d) = 16d

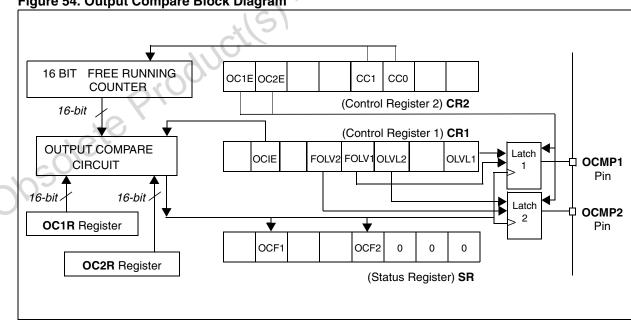

#### beCAN CONTROLLER (Cont'd)

#### Side-effect of Workround 1

Because the while loop lasts 10 CPU cycles, at high baud rate, it is possible to miss a dominant state on the bus if it lasts just one CAN bit time and the bus speed is high enough (see Table 1).

#### Table 29. While Loop Timing

| f <sub>CPU</sub> | Software<br>timing:<br>While loop | Minimum baud rate for<br>possible missed<br>dominant bit |

|------------------|-----------------------------------|----------------------------------------------------------|

| 8 MHz            | 1.25 µs                           | 800 Kbaud                                                |

| 4 MHz            | 2.5 µs                            | 400 Kbaud                                                |

| f <sub>CPU</sub> | 10/f <sub>CPU</sub>               | f <sub>CPU</sub> /10                                     |

If this happens, we will continue waiting in the while loop instead of releasing the FIFO immediately. The workaround is still valid because we will not release the FIFO during the critical period. But the application may lose additional time waiting in the while loop as we are no longer able to guarantee a maximum of 6 CAN bit times spent in the workaround.

In this particular case the time the application can spend in the workaround may increase up to a full CAN frame, depending of the frame contents. This

Figure 113. Reception at Maximum CAN Baud Rate

case is very rare but happens when a specific sequence is present on in the CAN frame.

The example in Figure 20 shows reception at maximum CAN baud rate: In this case  $t_{CAN}$  is  $8/f_{CPU}$  and the sampling time is  $10/f_{CPU}$ .

If the application is using the maximum baud rate and the possible delay caused by the workaround is not acceptable, there is another workaround which reduces the Rx pin sampling time.

Workaround 2 (see Figure 21) first tests that FMP = 2 and the CAN cell is receiving, if not the FIFO can be released immediately. If yes, the program goes through a sequence of test instructions on the RX pin that last longer than the time between the acknowledge dominant bit and the critical time slot. If the Rx pin is in recessive state for more than 8 CAN bit times, it means we are now after the acknowledge and the critical slot. If a dominant bit is read on the bus, we can release the FIFO immediately. This workaround has to be written in assembly language to avoid the compiler optimizing the test sequence.

The implementation shown here is for the CAN bus maximum speed (1 Mbaud @ 8 MHz CPU clock).

## beCAN CONTROLLER (Cont'd)

Bits 3:0 **BS1[3:0]** *Time Segment 1* These bits define the number of time quanta in Time Segment 1

Time Segment 1 = (BS1+1)

For more information on bit timing, please refer to Section 0.1.4.6 Bit Timing.

## CAN FILTER PAGE SELECT REGISTER

#### (CPSR)

All bits of this register are set and cleared by software.

Read / Write

Reset Value: 0000 0000 (00h)

|   | 7  |     |    |    |    |      |      | 0    |   | 4     | Acceptance  |

|---|----|-----|----|----|----|------|------|------|---|-------|-------------|

|   |    |     |    |    |    | 1    |      | Ű    | 1 | 5     | Reserved    |

|   | 0  | 0   | 0  | 0  | 0  | FPS2 | FPS1 | FPS0 |   | 6     | Configurati |

|   |    | -   | -  |    |    | -    |      |      | J | 7     | Receive FI  |

| 0 | 05 | 016 | ţO | Р1 | 00 |      | 19   |      | 0 | psolf | ste '       |

Bits 7:3 = Reserved. Forced to 0 by hardware.

## Bits 2:0 = **PS[2:0]** *Page Select* - Read/Write

This register contains the page number.

#### Table 31. Filter Page Selection

| PS[2:0] | Page Selected           |  |  |  |  |

|---------|-------------------------|--|--|--|--|

| 0       | Tx Mailbox 0            |  |  |  |  |

| 1       | Tx Mailbox 1            |  |  |  |  |

| 2       | Acceptance Filter 0:1   |  |  |  |  |

| 3       | Acceptance Filter 2:3   |  |  |  |  |

| 4       | Acceptance Filter 4:5   |  |  |  |  |

| 5       | Reserved                |  |  |  |  |

| 6       | Configuration/Diagnosis |  |  |  |  |

| 7       | Receive FIFO            |  |  |  |  |

## **11 INSTRUCTION SET**

## **11.1 CPU ADDRESSING MODES**

The CPU features 17 different addressing modes which can be classified in seven main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The CPU Instruction set is designed to minimize the number of bytes required per instruction: To do

<u>ل</u>رک

so, most of the addressing modes may be subdivided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

|           | Mode     |          | Syntax              | Destination | Pointer<br>Address<br>(Hex.) | Pointer Size<br>(Hex.) | Length<br>(Bytes) |

|-----------|----------|----------|---------------------|-------------|------------------------------|------------------------|-------------------|

| Inherent  |          |          | nop                 | 5           |                              |                        | + 0               |

| Immediate |          |          | ld A,#\$55          |             |                              |                        | + 1               |

| Short     | Direct   |          | ld A,\$10           | 00FF        |                              |                        | + 1               |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF    |                              |                        | + 2               |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF        |                              |                        | + 0               |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE       |                              |                        | + 1               |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF    |                              |                        | + 2               |

| Short     | Indirect |          | ld A,[\$10]         | 00FF        | 00FF                         | byte                   | + 2               |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF    | 00FF                         | word                   | + 2               |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE       | 00FF                         | byte                   | + 2               |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF    | 00FF                         | word                   | + 2               |

| Relative  | Direct   |          | jrne loop           | PC+/-127    |                              |                        | + 1               |

| Relative  | Indirect |          | jrne [\$10]         | PC+/-127    | 00FF                         | byte                   | + 2               |

| Bit       | Direct   |          | bset \$10,#7        | 00FF        |                              |                        | + 1               |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF        | 00FF                         | byte                   | + 2               |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF        |                              |                        | + 2               |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF        | 00FF                         | byte                   | + 3               |

5

## 12.4.2 On-Chip Peripherals

$T_A = 25^{\circ}C$ ,  $f_{CPU} = 8$  MHz.

| Symbol                | Parameter                                        | Condi | itions          | Тур | Unit |

|-----------------------|--------------------------------------------------|-------|-----------------|-----|------|

| I <sub>DD(TIM)</sub>  | 16-bit Timer supply current <sup>1)</sup>        |       |                 | 50  |      |

| I <sub>DD(TIM8)</sub> | 8-bit Timer supply current <sup>1)</sup>         |       |                 | 50  |      |

| I <sub>DD(ART)</sub>  | ART PWM supply current <sup>2)</sup>             |       |                 | 75  |      |

| I <sub>DD(SPI)</sub>  | SPI supply current <sup>3)</sup>                 |       | $V_{DD} = 5.0V$ |     | μA   |

| I <sub>DD(SCI)</sub>  | SCI supply current <sup>4)</sup>                 |       |                 | 400 |      |

| I <sub>DD(ADC)</sub>  | ADC supply current when converting <sup>5)</sup> |       | 1               |     |      |

| I <sub>DD(CAN)</sub>  | CAN supply current <sup>6)</sup>                 |       |                 | 800 |      |

#### Notes:

- 1. Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer counter running at f<sub>CPU</sub>/4) and timer counter stopped (only TIMD bit set). Data valid for one timer.

- Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer stopped) and timer counter enabled (only TCE bit set).

- 3. Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to 55h). This measurement includes the pad toggling consumption.

4. Data based on a differential I<sub>DD</sub> measurement between SCI low power state (SCID = 1) and a permanent SCI data transmit sequence. Data valid for one SCI.

- 5. Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions.

- 6. Data based on a differential I<sub>DD</sub> measurement between reset configuration (CAN disabled) and a permanent CAN data transmit sequence with RX and TX connected together. This measurement include the pad toggling consumption.

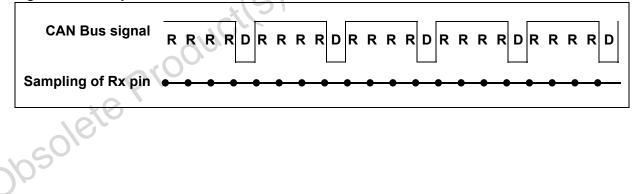

## CLOCK AND TIMING CHARACTERISTICS (Cont'd)

#### 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).  $^{1/2}$

| Symbol                             | Parameter                                                                                                                      | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Min                  | Max                  | Unit      |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------|

|                                    | 3)                                                                                                                             | LP: Low power oscillator<br>MP: Medium power oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1<br>>2              | 2<br>4               | ~ • • • • |

| tosc                               | Oscillator Frequency <sup>3)</sup>                                                                                             | MS: Medium speed oscillator<br>HS: High speed oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | >4<br>>8             | 8<br>16              | MHz       |

| R <sub>F</sub>                     | Feedback resistor                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20                   | 40                   | kΩ        |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance ver-<br>sus equivalent serial resistance of the<br>crystal or ceramic resonator (R <sub>S</sub> ) | $eq:rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_$ | 22<br>22<br>18<br>15 | 56<br>46<br>33<br>33 | pF        |

| Symbol         | Parameter            | Conditions                                                                                       | Тур                     | Max                      | Unit |

|----------------|----------------------|--------------------------------------------------------------------------------------------------|-------------------------|--------------------------|------|

| i <sub>2</sub> | OSC2 driving current | $V_{DD} = 5V$ LP oscillator<br>$V_{IN} = V_{SS}$ MP oscillator<br>MS oscillator<br>HS oscillator | 80<br>160<br>310<br>610 | 150<br>250<br>460<br>910 | μA   |

#### Figure 122. Typical Application with a Crystal or Ceramic Resonator

#### Notes:

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2.  $t_{SU(OSC)}$  is the typical oscillator start-up time measured between  $V_{DD}$  = 2.8V and the fetch of the first instruction (with a quick  $V_{DD}$  ramp-up from 0 to 5V (< 50µs).

3. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

**لركم**

## TRANSFER OF CUSTOMER CODE (Cont'd)

| ST72561 MICROCONTROLLER OPTION LIST<br>(Last update: September 2006) |                                                                                                                                                                                                                                       |                                       |                                                               |     |                                                          |                                                             |                                                   |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|-----|----------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------|--|

|                                                                      | Customer<br>Address                                                                                                                                                                                                                   | · · · · · · · · · · · · · · · · · · · |                                                               |     |                                                          |                                                             |                                                   |  |

|                                                                      | Contact<br>Phone No<br>Reference/ROM Code* .<br>*The ROM/FASTROM code name is assigned by STMicroelectronics.<br>ROM/FASTROM code must be sent in .S19 formatHex extension cannot be processed.                                       |                                       |                                                               |     |                                                          |                                                             |                                                   |  |

|                                                                      | Device Type/Memory Size/Package (check only one option)           ROM:                                                                                                                                                                |                                       |                                                               |     |                                                          |                                                             |                                                   |  |

|                                                                      | ROM:                                                                                                                                                                                                                                  | Package                               | 60K                                                           | 48K | <br>                                                     | 32K                                                         | 16K                                               |  |

|                                                                      | <br> <br> FASTROM<br> <br> <br>                                                                                                                                                                                                       | LQFP44:                               | [] ST72561AR9<br>[] ST72561J9<br>[] ST72561K9                 |     | 7                                                        | []ST72561J6                                                 | [] ST72561AR4  <br>[] ST72561J4  <br>[] ST72561K4 |  |

|                                                                      |                                                                                                                                                                                                                                       | Package                               | 60K                                                           | 48K | <br>                                                     | 32K                                                         | 16K                                               |  |

|                                                                      |                                                                                                                                                                                                                                       | LQFP44:                               | [] ST72P561AR9<br>[] ST72P561J9<br>[] ST72P561K9              |     | J7 I                                                     |                                                             | []ST72P561J4                                      |  |

|                                                                      | Conditioning:       [] Tray       [] Tape & Reel         Special Marking:       [] No       [] Yes "" (10 char. max)         Authorized characters are letters, digits, '.', '-', '/' and spaces only.       [] Yes "" (10 char. max) |                                       |                                                               |     |                                                          |                                                             | max)                                              |  |

|                                                                      | Temp. Range. Please refer to datasheet for specific sales conditions:                                                                                                                                                                 |                                       |                                                               |     |                                                          |                                                             |                                                   |  |

|                                                                      | -<br>[]<br>[]<br>Clock Source                                                                                                                                                                                                         |                                       |                                                               |     |                                                          |                                                             |                                                   |  |

|                                                                      | Oscillator/Exte<br>LVD<br>PLL <sup>1</sup><br>Watchdog Sel<br>Watchdog Res                                                                                                                                                            |                                       | [] Disabled<br>[] Software Activation                         |     |                                                          | [] Enabled<br>[] Enabled<br>[] Hardware Activation<br>Reset |                                                   |  |

|                                                                      | Read-out Protection                                                                                                                                                                                                                   |                                       | [] Disabled                                                   |     | [] Enabled                                               |                                                             |                                                   |  |

|                                                                      | Reset Delay                                                                                                                                                                                                                           |                                       | [] 256 Cycles [] 4096 Cycles                                  |     |                                                          |                                                             |                                                   |  |

|                                                                      | LINSCI2 Mapping<br>T16_ICAP2 Mapping                                                                                                                                                                                                  |                                       | [] Not available (AFIMAP[1] = 0)<br>[] On PD1 (AFIMAP[0] = 0) |     | [ ] Mapped (AFIMAP[1] = 1)<br>[ ] On PC1 (AFIMAP[0] = 1) |                                                             |                                                   |  |

|                                                                      | Comments:<br>Supply Operating Range in the application:                                                                                                                                                                               |                                       |                                                               |     |                                                          |                                                             |                                                   |  |

|                                                                      | Notes<br>Signature<br>Date                                                                                                                                                                                                            |                                       |                                                               |     |                                                          |                                                             |                                                   |  |

|                                                                      | Please download the latest version of this option list from:<br>http://www.st.com                                                                                                                                                     |                                       |                                                               |     |                                                          |                                                             |                                                   |  |

**57**

#### **IMPORTANT NOTES** (Cont'd)

#### Figure 154.LINSCI Interrupt Routine

```

@interrupt void LINSCI_IT ( void ) /* LINSCI interrupt routine */

{

/* clear flags */

SCISR buffer = SCISR;

SCIDR_buffer = SCIDR;

if ( SCISR_buffer & LHE ) /* header error ? */

{

if (!LHLR) /* header time-out? */

{

if ( !(SCICR2 & RWU) )/* active mode ?

_asm("sim");/* disable interrupts */

SCISR:

SCIDR; /* Clear RDRF flag */

SCICR2 |= RWU; /* set mute mode */

SCISR;

SCIDR; /* Clear RDRF flag */

SCICR2 |= RWU; /* set mute mode */

_asm("rim");/* enable interrupts */

}

}

}

}

Example using Cosmic compiler syntax

```

## 16.1.6 TIMD set simultaneously with OC interrupt

If the 16-bit timer is disabled at the same time the output compare event occurs then the output compare flag gets locked and cannot be cleared before the timer is enabled again.

**Impact on the application:** If output compare interrupt is enabled, then the output compare flag cannot be cleared in the timer interrupt routine. Consequently the interrupt service routine is called repeatedly and the application get stuck which causes the watchdog reset if enabled by the application.

**Workaround:** Disable the timer interrupt before disabling the timer. Again while enabling, first enable the timer, then the timer interrupts.

Perform the following to disable the timer:

- TACR1 or TBCR1 = 0x00h; // Disable the compare interrupt

- TACSR | or TBCSR | = 0x40; // Disable the timer

- Perform the following to enable the timer again:

- TACSR & or TBCSR &= ~0x40; // Enable the timer

- TACR1 or TBCR1 = 0x40; // Enable the compare interrupt

#### 16.1.7 CAN FIFO Corruption

The beCAN FIFO gets corrupted when a message is received and simultaneously a message is released while FMP = 2. For details and a description of the workaround refer to Section 10.9.7.1 on page 187.

#### 16.2 FLASH/FASTROM DEVICES ONLY

# 16.2.1 LINSCI Wrong Break Duration SCI mode

A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 20 bits instead of 10 bits if M = 0

- 22 bits instead of 11 bits if M = 1

In the same way, as long as the SBK bit is set, break characters are sent to the TDO pin. This may lead to generate one break more than expected.

#### Occurrence

The occurrence of the problem is random and proportional to the baud rate. With a transmit frequency of 19200 baud ( $f_{CPU} = 8 \text{ MHz}$  and

**/**

uctls

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

57