# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | CANbus, LINbusSCI, SPI                                                 |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 48                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561r9tatr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| F      | Pin n | 0    |                   |      | Le      | evel   |       |     | P   | ort |     |     | Main               |                                 |

|--------|-------|------|-------------------|------|---------|--------|-------|-----|-----|-----|-----|-----|--------------------|---------------------------------|

| P64    | P44   | P32  | Pin Name          | Type | ut      | out    |       | In  | out |     | Out | put | function<br>(after | Alternate function              |

| LQFP64 | LQFI  | LQFI |                   |      | Input   | Output | float | ndm | int | ana | OD  | РР  | reset)             |                                 |

| 54     | 36    | 26   | PD4 / SCI2_RDI    | I/O  | CT      |        | x     |     | ei3 |     | х   | х   | Port D4            | LINSCI2 Receive Data in-<br>put |

| 55     | 37    | 27   | V <sub>SSA</sub>  | S    |         |        |       |     |     |     |     |     | Analog G           | iround Voltage                  |

| 56     | 38    | 28   | V <sub>SS_0</sub> | S    |         |        |       |     |     |     |     |     | Digital G          | round Voltage                   |

| 57     | 39    | 29   | V <sub>DDA</sub>  | Ι    |         |        |       |     |     |     |     |     | Analog F           | eference Voltage for ADC        |

| 58     | 40    | 30   | V <sub>DD_0</sub> | S    |         |        |       |     |     |     |     |     | Digital M          | ain Supply Voltage              |

| 59     | 41    | 31   | PD5 / SCI2_TDO    | I/O  | CT      |        | x     | х   |     |     | х   | х   | Port D5            | LINSCI2 Transmit Data<br>output |

| 60     | 42    | 32   | RESET             | I/O  | $C_T$   |        |       |     |     |     |     |     | Top prior          | ity non maskable interrupt.     |

| 61     | 43    | -    | PD6 / AIN10       | I/O  | $C_T$   |        | Х     | е   | i3  | Х   | Х   | Х   | Port D6            | ADC Analog Input 10             |

| 62     | 44    | -    | PD7 / AIN11       | I/O  | $C_T$   |        | Х     |     | ei3 | Х   | Х   | Х   | Port D7            | ADC Analog Input 11             |

| 63     | -     | -    | PF6               | I/O  | $T_T$   |        | Х     | Х   |     |     | Х   | Х   | Port F6            |                                 |

| 64     | -     | -    | PF7               | I/O  | $T_{T}$ |        | Х     | Х   |     |     | Х   | X   | Port F7            |                                 |

#### Notes:

1. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

2. Input mode can be used for general purpose I/O, output mode only for CANTX.

3. OSC1 and OSC2 pins connect a crystal/ceramic resonator, or an external source to the on-chip oscillator; see Section 6 and Section 12.5 "CLOCK AND TIMING CHARACTERISTICS" for more details.

4. On the chip, each I/O port has eight pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

## 6.4.3 Low Power Modes

| Mode | Description                                                              |

|------|--------------------------------------------------------------------------|

| WAIT | No effect on SI. AVD interrupts cause the device to exit from Wait mode. |

| HALT | The SICSR register is frozen.                                            |

## 6.4.3.1 Interrupts

| Interrupt Event | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |       |      |   | 21 | JĊ |

|-----------------|---------------|--------------------------|----------------------|----------------------|-------|------|---|----|----|

| AVD event       | AVDF          | AVDIE                    | Yes                  | No                   |       |      |   | 00 |    |

|                 |               |                          |                      |                      | 0105( | 916, | Ø |    |    |

| ,501ete         |               | du                       | cille                | 5)                   | 0056  | 216, |   |    |    |

## INTERRUPTS (Cont'd)

## Table 10. Nested Interrupts Register Map and Reset Values

## POWER SAVING MODES (Cont'd)

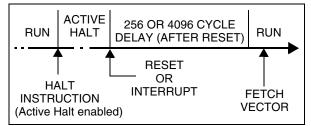

## Figure 27. ACTIVE HALT Timing Overview

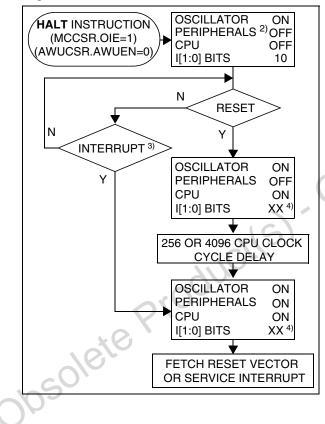

### Figure 28. ACTIVE HALT Mode Flow-chart

#### Notes:

psolete

- 1. This delay occurs only if the MCU exits ACTIVE HALT mode by means of a RESET.

- 2. Peripheral clocked with an external clock source can still be active.

- 3. Only the RTC interrupt and some specific interrupts can exit the MCU from ACTIVE HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 34 for more details.

- 4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits in the CC register are set to the current software priority level of the interrupt routine and restored when the CC register is popped.

## **ON-CHIP PERIPHERALS** (Cont'd)

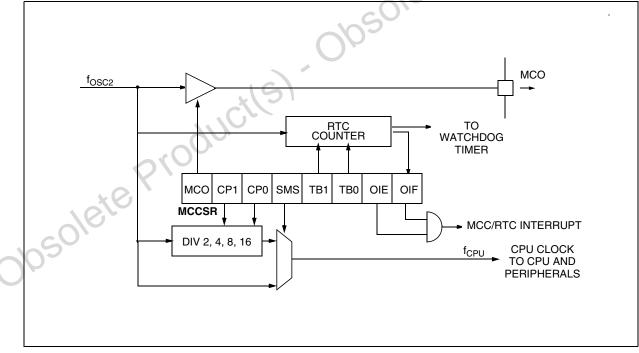

## 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK MCC/RTC

The Main Clock Controller consists of three different functions:

- a programmable CPU clock prescaler

- a clock-out signal to supply external devices

- a real time clock timer with interrupt capability

Each function can be used independently and simultaneously.

### 10.2.1 Programmable CPU Clock Prescaler

The programmable CPU clock prescaler supplies the clock for the ST7 CPU and its internal peripherals. It manages SLOW power saving mode (See Section 8.2 "SLOW MODE" for more details).

The prescaler selects the  $f_{CPU}$  main clock frequency and is controlled by three bits in the MCCSR register: CP[1:0] and SMS.

## 10.2.2 Clock-out Capability

The clock-out capability is an alternate function of an I/O port pin that outputs a  $f_{OSC2}$  clock to drive external devices. It is controlled by the MCO bit in the MCCSR register.

## 10.2.3 Real Time Clock Timer (RTC)

The counter of the real time clock timer allows an interrupt to be generated based on an accurate real time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by 4 bits of the MCCSR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters ACTIVE HALT mode when the HALT instruction is executed. See Section 8.5 "ACTIVE HALT MODE" for more details.

### Figure 39. Main Clock Controller (MCC/RTC) Block Diagram

## **External Interrupt Capability**

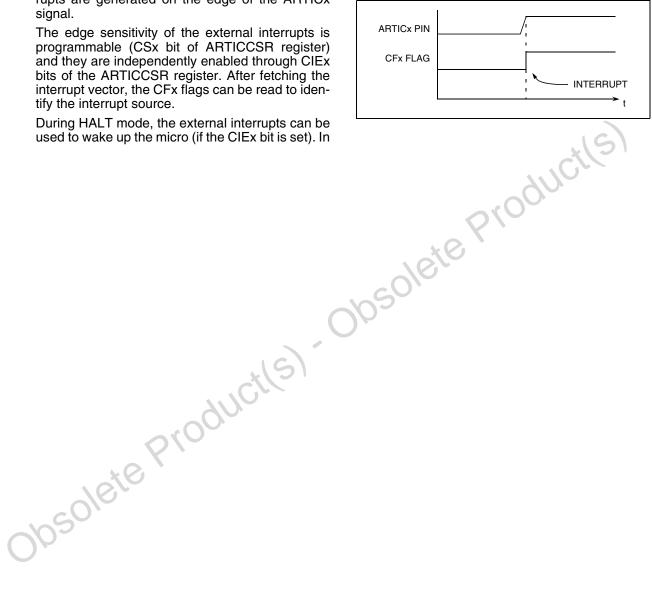

This mode allows the Input capture capabilities to be used as external interrupt sources. The interrupts are generated on the edge of the ARTICx signal.

The edge sensitivity of the external interrupts is programmable (CSx bit of ARTICCSR register) and they are independently enabled through CIEx bits of the ARTICCSR register. After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

this case, the interrupt synchronization is done directly on the ARTICx pin edge (Figure 47).

## Figure 47. ART External Interrupt in Halt Mode

## 16-BIT TIMER (Cont'd) INPUT CAPTURE 1 HIGH REGISTER (IC1HR)

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

## **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

|            | 7   |     |    |    |    |     |    | 0   |  |

|------------|-----|-----|----|----|----|-----|----|-----|--|

|            | MSB |     |    |    |    |     |    | LSB |  |

| -          |     |     |    |    |    |     |    |     |  |

|            |     |     |    |    |    |     | iG | Ń   |  |

|            |     |     |    |    |    | . C |    |     |  |

|            |     |     |    |    | -0 | S.C |    |     |  |

|            |     |     |    | 05 | 0  |     |    |     |  |

|            |     |     | je | X  |    |     |    |     |  |

|            |     | 16  |    |    |    |     |    |     |  |

|            | S   | 0/, |    |    |    |     |    |     |  |

| $\bigcirc$ |     |     |    |    |    |     |    |     |  |

|            |     |     |    |    |    |     |    |     |  |

## OUTPUT COMPARE 1 HIGH REGISTER (OC1HR)

#### Read/Write

\_

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

<u>ل</u>رک

## 16-BIT TIMER (Cont'd)

## OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

#### Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| /   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

## OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

### **COUNTER HIGH REGISTER (CHR)**

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   | 0   |

|-----|-----|

| MSB | LSB |

|     |     |

## **COUNTER LOW REGISTER (CLR)**

#### Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## ALTERNATE COUNTER HIGH REGISTER (ACHR)

#### Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## ALTERNATE COUNTER LOW REGISTER (ACLR)

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## INPUT CAPTURE 2 HIGH REGISTER (IC2HR)

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## **INPUT CAPTURE 2 LOW REGISTER (IC2LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 1   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## 16-BIT TIMER (Cont'd)

## Table 19. 16-Bit Timer Register Map

| Address<br>(Hex.) | Register<br>Name | 7    | 6     | 5          | 4     | 3     | 2     | 1     | 0     |

|-------------------|------------------|------|-------|------------|-------|-------|-------|-------|-------|

| 51                | CR2              | OC1E | OC2E  | OPM        | PWM   | CC1   | CC0   | IEDG2 | EXEDG |

| 52                | CR1              | ICIE | OCIE  | TOIE       | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

| 53                | CSR              | ICF1 | OCF1  | TOF        | ICF2  | OCF2  | TIMD  |       |       |

| 54                | IC1HR            | MSB  |       |            |       |       |       |       | LSB   |

| 55                | IC1LR            | MSB  |       |            |       |       |       | 1     | LSB   |

| 56                | OC1HR            | MSB  |       |            |       |       |       | ×     | LSB   |

| 57                | OC1LR            | MSB  |       |            |       |       |       |       | LSB   |

| 58                | CHR              | MSB  |       |            |       |       |       |       | LSB   |

| 59                | CLR              | MSB  |       |            |       |       |       |       | LSB   |

| 5A                | ACHR             | MSB  |       |            |       |       |       |       | LSB   |

| 5B                | ACLR             | MSB  |       |            |       |       |       |       | LSB   |

| 5C                | IC2HR            | MSB  |       |            |       | 2     |       |       | LSB   |

| 5D                | IC2LR            | MSB  |       |            | 3     |       |       |       | LSB   |

| 5E                | OC2HR            | MSB  |       | $\bigcirc$ |       |       |       |       | LSB   |

| 5F                | OC2LR            | MSB  |       |            |       |       |       |       | LSB   |

| solf              | OC2LR            | odu  | cills | 1          |       |       |       |       |       |

| 22                |                  |      |       |            |       |       |       |       |       |

57

## 8-BIT TIMER (Cont'd)

Whatever the timer mode used (input capture, output compare, one pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFh to 00h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt revyan .vakenedi .vakenedi Obsolete Production mains pending to be issued as soon as they are

Notes: The TOF bit is not cleared by accesses to ACTR register. The advantage of accessing the ACTR register rather than the CTR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by WAIT mode.

In HALT mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a Reset).

## LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

## **BAUD RATE REGISTER (SCIBRR)**

Read/Write Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

Note: When LIN slave mode is disabled, the SCI-BRR register controls the conventional baud rate generator.

Bits 7:6 = SCP[1:0] First SCI Prescaler

These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

| 1                    | 0    | 0    |

| 3                    |      | 1    |

| 4                    | 1    | 0    |

| 13                   |      | 1    |

Bits 5:3 = **SCT[2:0]** SCI Transmitter rate divisor These 3 bits, in conjunction with the SCP1 and SCP0 bits define the total division applied to the Josolete Production bus clock to yield the transmit rate clock in conven-

| TR dividing factor | SCT2 | SCT1 | SCT0 |

|--------------------|------|------|------|

| 1                  |      | •    | 0    |

| 2                  |      | 0    | 1    |

| 4                  | 0    | 4    | 0    |

| 8                  |      | 1    | 1    |

| 16                 |      | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 |      | 1    | 0    |

| 128                |      |      | 1    |

|                    |      |      | 6    |

Bits 2:0 = SCR[2:0] SCI Receiver rate divider These 3 bits, in conjunction with the SCP[1:0] bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| SCR2 | SCR1   | SCR0                        |

|------|--------|-----------------------------|

|      | 0      | 0                           |

| 0    | 0      | 1                           |

| 0    | 1      | 0                           |

|      | I      | 1                           |

|      | 0      | 0                           |

| 4    | 0      | 1                           |

| 1    | 1      | 0                           |

|      | I      | 1                           |

|      | 0<br>1 | SCR2 SCR1   0 0   1 0   1 1 |

<u>ل</u>رک

## Figure 102. Filter Bank Scale Configuration - Register Organisation

|                           | Filter Bank Scale  | Configuration            | Filter Bank Scale Co   | nfig. Bits <sup>1</sup> |

|---------------------------|--------------------|--------------------------|------------------------|-------------------------|

|                           | One 32-Bit Filter  |                          | FSCx = 3               |                         |

| Identifier                | CFxR0              | CFxR1                    | CFxR2                  | CFxR3                   |

| Mask/Ident.               | CFxR4              | CFxR5                    | CFxR6                  | CFxR7                   |

| Bit Mapping               | STID10:3           | STID2:0 RTR DE EXID17:15 | EXID14:7               | EXID6:0                 |

|                           | Two 16-Bit Filters |                          |                        |                         |

| Identifier                | CFxR0              | CFxR1                    |                        | .151                    |

| Mask/Ident.               | CFxR2              | CFxR3                    | 500 0                  | CIL S                   |

| Identifier                | CFxR4              | CFxR5                    | FSCx = 2               | 21/0                    |

| Mask/Ident.               | CFxR6              | CFxR7                    | . (                    | $\gamma^{O}$            |

| Bit Mapping               | STID10:3           | STID2:0 RTR DE EXID17:15 | 01                     | oduct(S)                |

|                           | One 16-Bit / Two   |                          | oletepri               |                         |

| Identifier                | CFxR0              | CFxR1                    |                        |                         |

| Mask/Ident.               | CFxR2              | CFxR3                    | 5                      |                         |

| ldentifier<br>Mask/Ident. | CFxR4<br>CFxR5     |                          |                        |                         |

| ldentifier<br>Mask/Ident. | CFxR6<br>CFxR7     | ((5)                     | FSCx = 1               |                         |

|                           | Four 8-Bit Filters |                          |                        |                         |

| ldentifier<br>Mask/Ident. | CFxR0<br>CFxR1     | ]                        |                        |                         |

| ldentifier<br>Mask/Ident. | CFxR2<br>CFxR3     | ]                        |                        |                         |

| Identifier<br>Mask/Ident. | CFxR4<br>CFxR5     | ]                        | FSCx = 0               |                         |

| Identifier                | CFxR6              | ] ,                      | k = filter bank number |                         |

| Mask/Ident.               | CFxR7              | 1                        | Those bits are leasts  | d in the CFCR register  |

| Bit Mapping               | STID10:3           | 1                        |                        | a in the Cron register  |

57

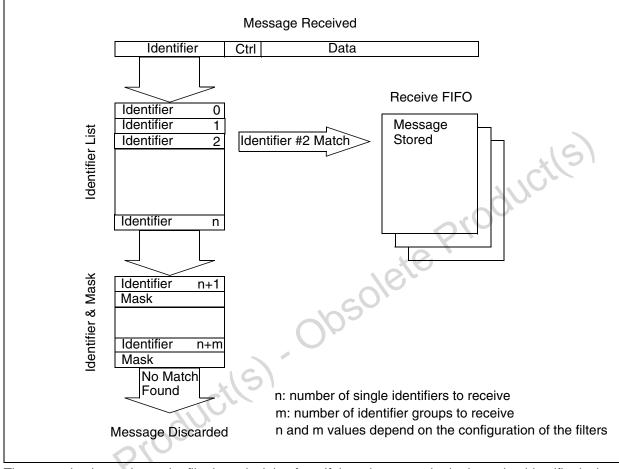

## Figure 103. Filtering Mechanism - example

The example above shows the filtering principle of the beCAN. On reception of a message, the identifier is compared first with the filters configured in identifier list mode. If there is a match, the message is stored in the FIFO and the index of the matching filter is stored in the Filter Match Index. As shown in the example, the identifier matches with Identifier #2 thus the message content and MFMI 2 is stored in the FIFO. If there is no match, the incoming identifier is then compared with the filters configured in mask mode.

If the identifier does not match any of the identifiers configured in the filters, the message is discarded by hardware without software intervention.

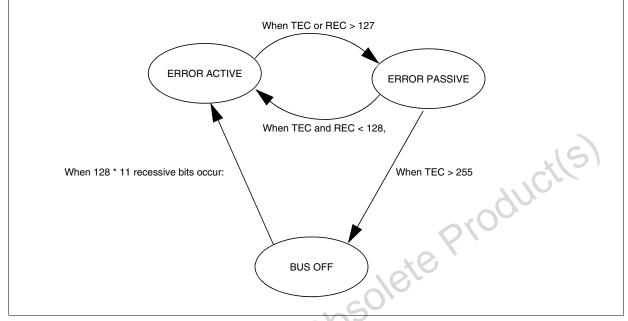

## Figure 104. CAN Error State Diagram

## 10.9.4.5 Error Management

The error management as described in the CAN protocol is handled entirely by hardware using a Transmit Error Counter (TECR register) and a Receive Error Counter (RECR register), which get incremented or decremented according to the error condition. For detailed information about TEC and REC management, please refer to the CAN standard.

Both of them may be read by software to determine the stability of the network. Furthermore, the CAN hardware provides detailed information on the current error status in CESR register. By means of CEIER register and ERRIE bit in CIER register, the software can configure the interrupt generation on error detection in a very flexible way.

## **Bus-Off Recovery**

The Bus-Off state is reached when TECR is greater then 255, this state is indicated by BOFF bit in CESR register. In Bus-Off state, the beCAN acts as disconnected from the CAN bus, hence it is no longer able to transmit and receive messages.

Depending on the ABOM bit in the CMCR register beCAN will recover from Bus-Off (become error active again) either automatically or on software request. But in both cases the beCAN has to wait at least for the recovery sequence specified in the CAN standard (128 x 11 consecutive recessive bits monitored on CANRX).

If ABOM is set, the beCAN will start the recovering sequence automatically after it has entered Bus-Off state.

If ABOM is cleared, the software must initiate the recovering sequence by requesting beCAN to enter initialization mode. Then beCAN starts monitoring the recovery sequence when the beCAN is requested to leave the initialisation mode.

**Note**: In initialization mode, beCAN does not monitor the CANRX signal, therefore it cannot complete the recovery sequence. **To recover, beCAN must be in normal mode**.

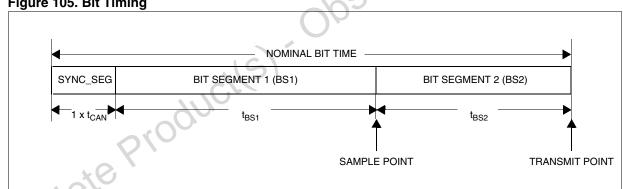

## 10.9.4.6 Bit Timing

The bit timing logic monitors the serial bus-line and performs sampling and adjustment of the sample point by synchronizing on the start-bit edge and resynchronizing on the following edges.

Its operation may be explained simply by splitting nominal bit time into three segments as follows:

- Synchronization segment (SYNC SEG): a bit change is expected to occur within this time segment. It has a fixed length of one time quantum (1 x t<sub>CAN</sub>).

- Bit segment 1 (BS1): defines the location of the sample point. It includes the PROP\_SEG and PHASE SEG1 of the CAN standard. Its duration is programmable between 1 and 16 time guanta but may be automatically lengthened to compensate for positive phase drifts due to differences in the frequency of the various nodes of the network.

- Bit segment 2 (BS2): defines the location of the transmit point. It represents the PHASE SEG2 of the CAN standard. Its duration is programmable between 1 and 8 time quanta but may also be automatically shortened to compensate for negative phase drifts.

- Resynchronization Jump Width (RJW): defines an upper bound to the amount of lengthening or shortening of the bit segments. It is programmable between 1 and 4 time quanta.

To guarantee the correct behaviour of the CAN controller, SYNC\_SEG + BS1 + BS2 must be greater than or equal to 5 time quanta.

For a detailed description of the CAN resynchronization mechanism and other bit timing configuration constraints, please refer to the Bosch CAN standard 2.0.

As a safeguard against programming errors, the configuration of the Bit Timing Registers CBTR1 and CBTR0 is only possible while the device is in Initialization mode.

## Figure 105. Bit Timing

<u>لرک</u>

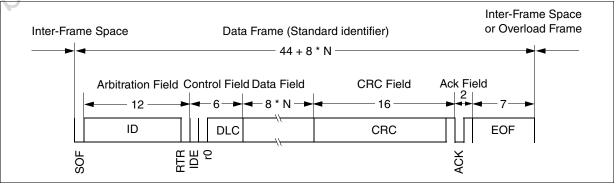

## Figure 106. CAN Frames (Part 1of 2)

### Side-effect of Workround 1

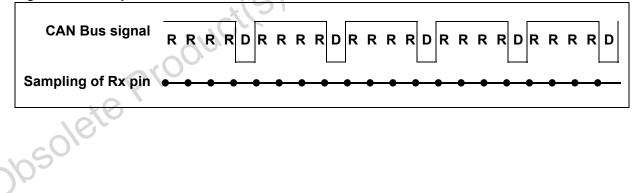

Because the while loop lasts 10 CPU cycles, at high baud rate, it is possible to miss a dominant state on the bus if it lasts just one CAN bit time and the bus speed is high enough (see Table 1).

## Table 29. While Loop Timing

| f <sub>CPU</sub> | Software<br>timing:   | Minimum baud rate for possible missed |

|------------------|-----------------------|---------------------------------------|

| 8 MHz            | While loop<br>1.25 µs | dominant bit<br>800 Kbaud             |

| 4 MHz            | 2.5 µs                | 400 Kbaud                             |

| f <sub>CPU</sub> | 10/f <sub>CPU</sub>   | f <sub>CPU</sub> /10                  |

If this happens, we will continue waiting in the while loop instead of releasing the FIFO immediately. The workaround is still valid because we will not release the FIFO during the critical period. But the application may lose additional time waiting in the while loop as we are no longer able to guarantee a maximum of 6 CAN bit times spent in the workaround.

In this particular case the time the application can spend in the workaround may increase up to a full CAN frame, depending of the frame contents. This

Figure 113. Reception at Maximum CAN Baud Rate

case is very rare but happens when a specific sequence is present on in the CAN frame.

The example in Figure 20 shows reception at maximum CAN baud rate: In this case  $t_{CAN}$  is  $8/f_{CPU}$  and the sampling time is  $10/f_{CPU}$ .

If the application is using the maximum baud rate and the possible delay caused by the workaround is not acceptable, there is another workaround which reduces the Rx pin sampling time.

Workaround 2 (see Figure 21) first tests that FMP = 2 and the CAN cell is receiving, if not the FIFO can be released immediately. If yes, the program goes through a sequence of test instructions on the RX pin that last longer than the time between the acknowledge dominant bit and the critical time slot. If the Rx pin is in recessive state for more than 8 CAN bit times, it means we are now after the acknowledge and the critical slot. If a dominant bit is read on the bus, we can release the FIFO immediately. This workaround has to be written in assembly language to avoid the compiler optimizing the test sequence.

The implementation shown here is for the CAN bus maximum speed (1 Mbaud @ 8 MHz CPU clock).

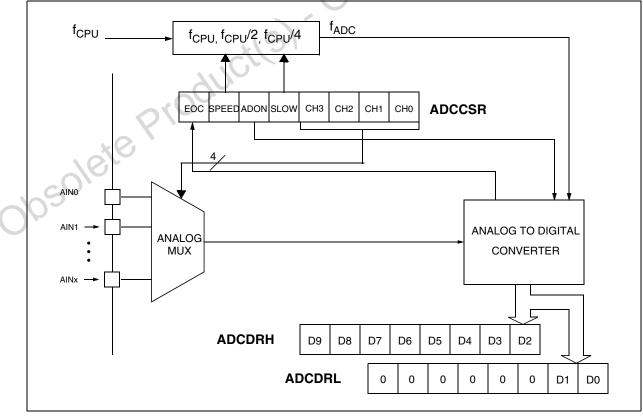

## 10.10 10-BIT A/D CONVERTER (ADC)

#### 10.10.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

#### 10.10.2 Main Features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 116.

## Figure 116. ADC Block Diagram

#### 10.10.3 Functional Description

## 10.10.3.1 Digital A/D Conversion Result

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{DDA}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and AD-CDRL registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the allotted time.

## **11 INSTRUCTION SET**

## **11.1 CPU ADDRESSING MODES**

The CPU features 17 different addressing modes which can be classified in seven main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The CPU Instruction set is designed to minimize the number of bytes required per instruction: To do

<u>ل</u>رک

so, most of the addressing modes may be subdivided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

|           | Mode     |          | Syntax              | Destination | Pointer<br>Address<br>(Hex.) | Pointer Size<br>(Hex.) | Length<br>(Bytes) |

|-----------|----------|----------|---------------------|-------------|------------------------------|------------------------|-------------------|

| Inherent  |          |          | nop                 | 5           |                              |                        | + 0               |

| Immediate |          |          | ld A,#\$55          |             |                              |                        | + 1               |

| Short     | Direct   |          | ld A,\$10           | 00FF        |                              |                        | + 1               |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF    |                              |                        | + 2               |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF        |                              |                        | + 0               |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE       |                              |                        | + 1               |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF    |                              |                        | + 2               |

| Short     | Indirect |          | ld A,[\$10]         | 00FF        | 00FF                         | byte                   | + 2               |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF    | 00FF                         | word                   | + 2               |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE       | 00FF                         | byte                   | + 2               |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF    | 00FF                         | word                   | + 2               |

| Relative  | Direct   |          | jrne loop           | PC+/-127    |                              |                        | + 1               |

| Relative  | Indirect |          | jrne [\$10]         | PC+/-127    | 00FF                         | byte                   | + 2               |

| Bit       | Direct   |          | bset \$10,#7        | 00FF        |                              |                        | + 1               |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF        | 00FF                         | byte                   | + 2               |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF        |                              |                        | + 2               |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF        | 00FF                         | byte                   | + 3               |

## FLASH OPTION BYTES (Cont'd)

OPT2:1 = **PKG[1:0]** Package selection These option bits select the device package.

| Selected Package | PKG |   |  |

|------------------|-----|---|--|

| Selected Fackage | 1   | 0 |  |

| LQFP 64          | 1   | x |  |

| LQFP 44          | 0   | 1 |  |

| LQFP 32          | 0   | 0 |  |

**Note:** Pads that are not bonded to external pins are in input pull-up configuration when the package selection option bits have been properly programmed. The configuration of these pads must be kept in reset state to avoid added current consumption.

OPT0 = **FMP\_R** Flash memory read-out protection

Read-out protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Erasing the option bytes when the FMP\_R option is selected causes the whole user memory to be erased first, and the device can be reprogrammed. Refer to Section 4.3.1 and the *ST7 Flash Programming Reference Manual* for more details.

0: Read-out protection enabled

1: Read-out protection disabled

## **OPTION BYTE 1**

## OPT7:6 = AFI MAP[1:0] AFI Mapping

These option bits allow the mapping of some of the Alternate Functions to be changed.

| AFI Mapping 1                                                                                                                                   | AFI_MAP(1) |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| T16_OCMP1 on PD3<br>T16_OCMP2 on PD5<br>T16_ICAP1 on PD4<br>LINSCI2_SCK not available<br>LINSCI2_TDO not available<br>LINSCI2_RDI not available | 0          |

| T16_OCMP1 on PB6<br>T16_OCMP2 on PB7<br>T16_ICAP1 on PC0<br>LINSCI2_SCK on PD3<br>LINSCI2_TDO on PD5<br>LINSCI2_RDI on PD4                      | 1          |

| AFI Mapping 0              | AFI_MAP(0) |

|----------------------------|------------|

| T16_ICAP2 is mapped on PD1 | 0          |

| T16_ICAP2 is mapped on PC1 | 1          |

OPT5:4 = **OSCTYPE[1:0]** Oscillator Type These option bits select the ST7 main clock source type.

| Clock Source                                           | OSCTYPE |   |  |

|--------------------------------------------------------|---------|---|--|

| Clock Source                                           | 1       | 0 |  |

| Resonator Oscillator                                   | 0       | 0 |  |

| Reserved                                               | 0       | 1 |  |

| Reserved internal clock source (used only in ICC mode) | 1       | 0 |  |

| External Source                                        | 1       | 1 |  |

OPT3:2 = **OSCRANGE[1:0]** Oscillator range If the resonator oscillator type is selected, these option bits select the resonator oscillator. This selection corresponds to the frequency range of the resonator used. If external source is selected with the OSCTYPE option, then the OSCRANGE option must be selected with the corresponding range.

|    |                 | OSCRANGE |   |  |

|----|-----------------|----------|---|--|

| 1) | vp. Freq. Range | 1        | 0 |  |

| LP | 1~2 MHz         | 0        | 0 |  |

| MP | 2~4 MHz         | 0        | 1 |  |

| MS | 4~8 MHz         | 1        | 0 |  |

| HS | 8~16 MHz        | 1        | 1 |  |

## OPT1 = Reserved

OPT0 = **RSTC** *RESET* clock cycle selection This option bit selects the number of CPU cycles inserted during the RESET phase and when exiting HALT mode. For resonator oscillators, it is advised to select 4096 due to the long crystal stabilization time.

0: Reset phase with 4096 CPU cycles

1: Reset phase with 256 CPU cycles

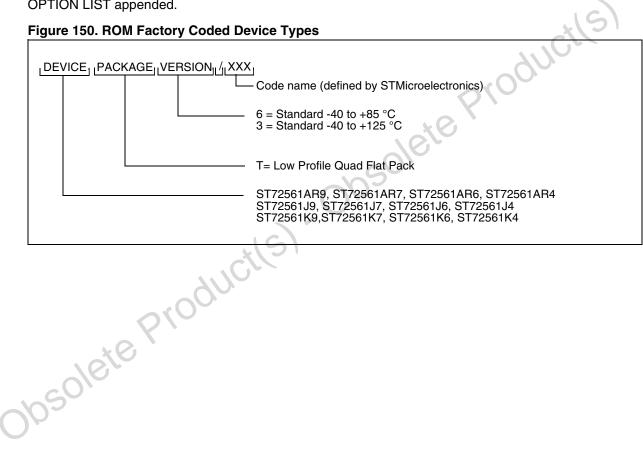

## DEVICE CONFIGURATION AND ORDER INFORMATION (cont'd)

## **14.2 TRANSFER OF CUSTOMER CODE**

Customer code is made up of the ROM/FAS-TROM contents and the list of the selected options (if any). The ROM/FASTROM contents are to be sent on diskette, or by electronic means, with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh.

The selected options are communicated to STMicroelectronics using the correctly completed OPTION LIST appended.

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred.

The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.