Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, LINbusSCI, SPI                                               |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 48                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561r9tc |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents -

\_\_\_\_

|        | CRIPTION                         |     |

|--------|----------------------------------|-----|

|        | DESCRIPTION                      |     |

|        | ISTER AND MEMORY MAP             |     |

|        |                                  |     |

|        |                                  | -   |

|        | MAIN FEATURES                    |     |

|        | STRUCTURE                        |     |

|        | ICC INTERFACE                    |     |

|        | ICP (IN-CIRCUIT PROGRAMMING)     |     |

|        | IAP (IN-APPLICATION PROGRAMMING) |     |

|        | RELATED DOCUMENTATION            | - P |

| 4.8    | REGISTER DESCRIPTION             | 17  |

| 5 CEN  | TRAL PROCESSING UNIT             | 18  |

| 5.1    | INTRODUCTION                     | 18  |

| 5.2    | MAIN FEATURES                    | 18  |

| 5.3    | CPU REGISTERS                    | 18  |

| 6 SUPI | PLY, RESET AND CLOCK MANAGEMENT  | 21  |

| 6.1    | PHASE LOCKED LOOP                | 21  |

| 6.2    | MULTI-OSCILLATOR (MO)            | 22  |

|        | RESET SEQUENCE MANAGER (RSM)     |     |

|        | SYSTEM INTEGRITY MANAGEMENT (SI) |     |

| 7 INTE | RRUPTS                           | 29  |

|        |                                  |     |

|        | MASKING AND PROCESSING FLOW      |     |

|        | INTERRUPTS AND LOW POWER MODES   |     |

|        | CONCURRENT & NESTED MANAGEMENT   |     |

|        | INTERRUPT REGISTER DESCRIPTION   |     |

|        | EXTERNAL INTERRUPTS              |     |

|        | YER SAVING MODES                 |     |

|        |                                  |     |

|        | SLOW MODE                        |     |

|        | WAIT MODE                        |     |

| -      | HALT MODE                        | -   |

|        | ACTIVE HALT MODE                 |     |

|        | AUTO WAKE-UP FROM HALT MODE      |     |

|        | ORTS                             |     |

| -      |                                  | -   |

|        | FUNCTIONAL DESCRIPTION           |     |

|        | I/O PORT IMPLEMENTATION          |     |

|        | LOW POWER MODES                  |     |

|        | INTERRUPTS                       |     |

| 9.6    | I/O PORT REGISTER CONFIGURATIONS | 50  |

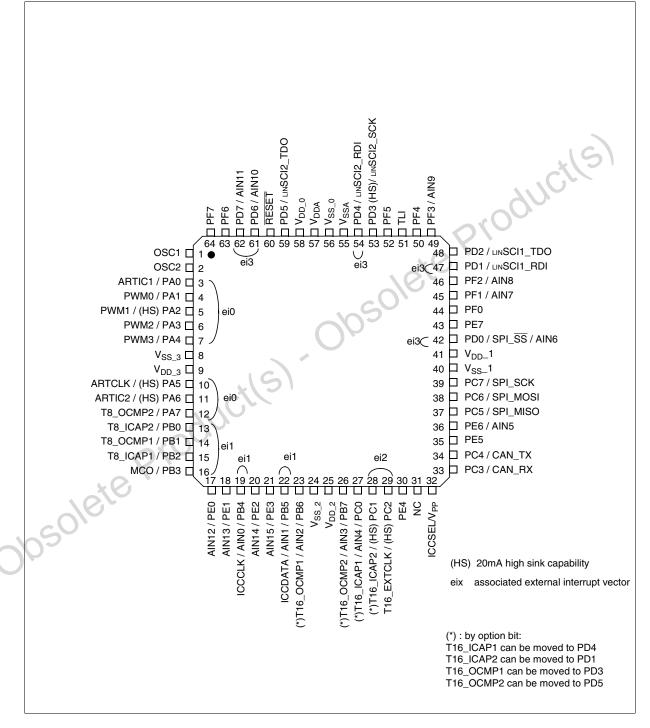

# **2 PIN DESCRIPTION**

57

# Figure 2. LQFP 64-Pin Package Pinout

# **5 CENTRAL PROCESSING UNIT**

# **5.1 INTRODUCTION**

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

# **5.2 MAIN FEATURES**

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power HALT and WAIT modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

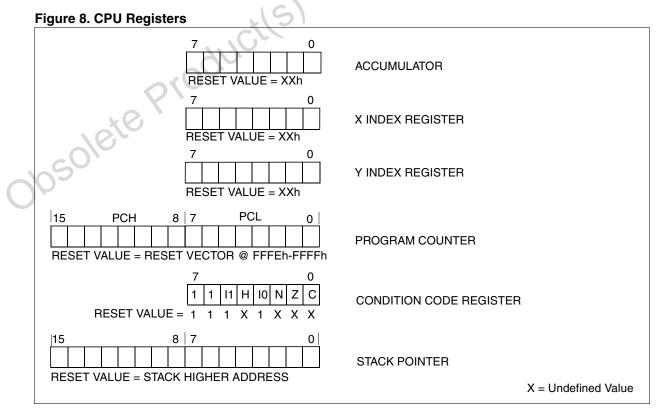

# **5.3 CPU REGISTERS**

The six CPU registers shown in Figure 8 are not present in the memory mapping and are accessed by specific instructions.

# Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

# Index Registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

# Program Counter (PC)

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

# POWER SAVING MODES (Cont'd)

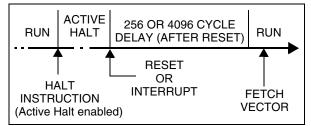

#### Figure 27. ACTIVE HALT Timing Overview

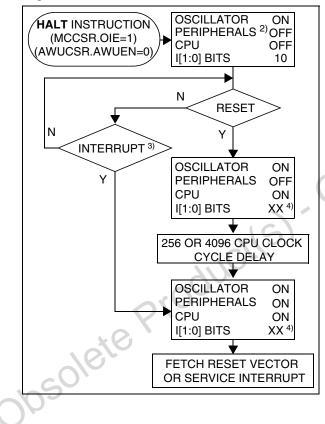

#### Figure 28. ACTIVE HALT Mode Flow-chart

#### Notes:

bsolete F

- 1. This delay occurs only if the MCU exits ACTIVE HALT mode by means of a RESET.

- 2. Peripheral clocked with an external clock source can still be active.

- 3. Only the RTC interrupt and some specific interrupts can exit the MCU from ACTIVE HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 34 for more details.

- 4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits in the CC register are set to the current software priority level of the interrupt routine and restored when the CC register is popped.

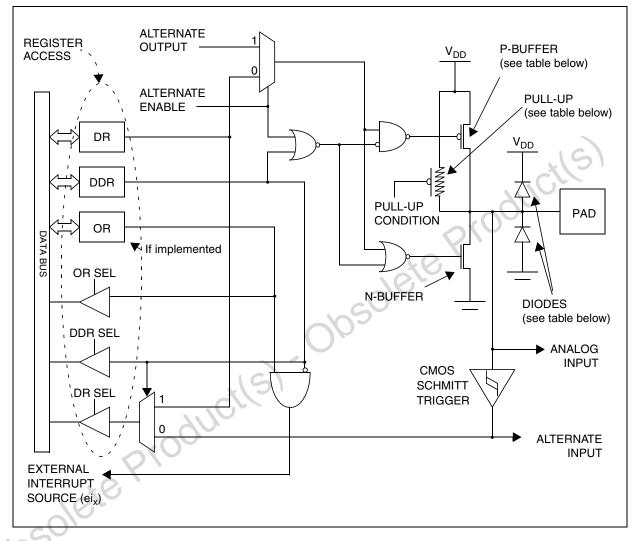

# 9 I/O PORTS

# 9.1 INTRODUCTION

The I/O ports offer different functional modes: - transfer of data through digital inputs and outputs

and for specific pins:

- external interrupt generation

- alternate signal input/output for the on-chip peripherals.

An I/O port contains up to 8 pins. Each pin can be programmed independently as digital input (with or without interrupt generation) or digital output.

# 9.2 FUNCTIONAL DESCRIPTION

Each port has two main registers:

- Data Register (DR)

- Data Direction Register (DDR)

and one optional register:

- Option Register (OR)

Each I/O pin may be programmed using the corresponding register bits in the DDR and OR registers: Bit X corresponding to pin X of the port. The same correspondence is used for the DR register.

The following description takes into account the OR register, (for specific ports which do not provide this register refer to the I/O Port Implementation section). The generic I/O block diagram is shown in Figure 32

#### 9.2.1 Input Modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

#### Notes:

1. Writing the DR register modifies the latch value but does not affect the pin status.

2. When switching from input to output mode, the DR register has to be written first to drive the correct level on the pin as soon as the port is configured as an output.

3. Do not use read/modify/write instructions (BSET or BRES) to modify the DR register as this might corrupt the DR content for I/Os configured as input.

#### **External interrupt function**

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an external interrupt request to the CPU.

Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout description and interrupt section). If several input pins are selected simultaneously as interrupt sources, these are first detected according to the sensitivity bits in the EICR register and then logically ORed.

The external interrupts are hardware interrupts, which means that the request latch (not accessible directly by the application) is automatically cleared when the corresponding interrupt vector is fetched. To clear an unwanted pending interrupt by software, the sensitivity bits in the EICR register must be modified.

# 9.2.2 Output Modes

The output configuration is selected by setting the corresponding DDR register bit. In this case, writing the DR register applies this digital value to the I/O pin through the latch. Then reading the DR register returns the previously stored value.

Two different output modes can be selected by software through the OR register: Output push-pull and open-drain.

DR register value and output pin status:

| DR | Push-pull       | Open-drain |

|----|-----------------|------------|

| 0  | V <sub>SS</sub> | Vss        |

| 1  | V <sub>DD</sub> | Floating   |

#### 9.2.3 Alternate Functions

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over the standard I/O programming.

When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

When the signal is going to an on-chip peripheral, the I/O pin must be configured in input mode. In this case, the pin state is also digitally readable by addressing the DR register.

**Note:** Input pull-up configuration can cause unexpected value at the input of the alternate peripheral input. When an on-chip peripheral use a pin as input and output, this pin has to be configured in input floating mode.

# I/O PORTS (Cont'd)

# Figure 32. I/O Port General Block Diagram

# Table 12. I/O Port Mode Options

| Configuration Mode |                                 | Pull-Up | P-Buffer | Diodes             |                    |

|--------------------|---------------------------------|---------|----------|--------------------|--------------------|

|                    |                                 | rui-op  | F-Duilei | to V <sub>DD</sub> | to V <sub>SS</sub> |

| Input              | Floating with/without Interrupt | Off     | Off      |                    |                    |

| Input              | Pull-up with/without Interrupt  | On      |          | On                 |                    |

|                    | Push-pull                       | Off     | On       |                    | On                 |

| Output             | Open Drain (logic level)        |         | Off      |                    |                    |

|                    | True Open Drain                 | NI      | NI       | NI (see note)      |                    |

Legend: NI - not implemented

Off - implemented not activated On - implemented and activated **Note**: The diode to  $V_{DD}$  is not implemented in the true open drain pads. A local protection between the pad and  $V_{SS}$  is implemented to protect the device against positive stress.

### **16-BIT TIMER** (Cont'd)

#### **10.4.7 Register Description**

Each Timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

#### **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = **ICIE** *Input Capture Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

#### Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.* 0: Interrupt is inhibited.

Jbsolete P

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

#### Bit 4 = FOLV2 Forced Output Compare 2.

- This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

Bit 3 = FOLV1 Forced Output Compare 1.

- This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

#### Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse mode and Pulse Width Modulation mode.

# Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture. 0: A falling edge triggers the capture. 1: A rising edge triggers the capture.

#### Bit 0 = OLVL1 Output Level 1.

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

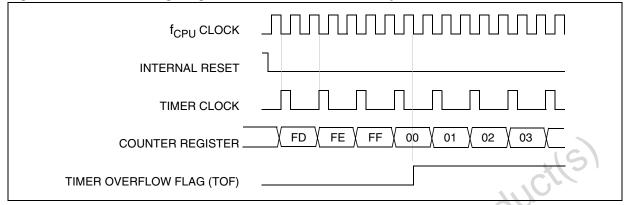

# 8-BIT TIMER (Cont'd)

# Figure 60. Counter Timing Diagram, Internal Clock Divided by 2

# Figure 61. Counter Timing Diagram, Internal Clock Divided by 4

# Figure 62. Counter Timing Diagram, Internal Clock Divided by 8

|   | f <sub>CPU</sub> CLOCK    |          |

|---|---------------------------|----------|

| 1 | INTERNAL RESET            | 1        |

|   | TIMER CLOCK               |          |

|   | COUNTER REGISTER          | FC FD 00 |

|   | TIMER OVERFLOW FLAG (TOF) |          |

Note: The MCU is in reset state when the internal reset signal is high, when it is low the MCU is running.

#### 8-BIT TIMER (Cont'd)

#### 10.5.7 Register Description

Each Timer is associated with three control and status registers, and with six data registers (8-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

#### **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = **ICIE** *Input Capture Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

#### Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.* 0: Interrupt is inhibited.

Josolete P

**لرك**ا

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

#### Bit 4 = FOLV2 Forced Output Compare 2.

- This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

Bit 3 = FOLV1 Forced Output Compare 1.

- This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

#### Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode.

#### Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture. 0: A falling edge triggers the capture. 1: A rising edge triggers the capture.

#### Bit 0 = OLVL1 Output Level 1.

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

105/265

# SERIAL PERIPHERAL INTERFACE (cont'd)

# 10.6.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the device is woken up<br>by an interrupt with "exit from HALT mode"<br>capability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the Device. |

# 10.6.6.1 Using the SPI to wake up the device from Halt mode

In slave configuration, the SPI is able to wake up the device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

Note: When waking up from HALT mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from HALT mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the device from HALT mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the device enters HALT mode. So, if Slave selection is configured as external (see Section 10.6.3.2), make sure the master drives a low level on the SS pin when the slave enters HALT mode.

# 10.6.7 Interrupts

|                              |               |                          | _ X \                |                      |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

| SPI End of<br>Transfer Event | SPIF          | 0                        |                      | Yes                  |

| Master Mode<br>Fault Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          |                      |                      |

|                              |               | •                        |                      |                      |

**Note:** The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# 10.6.8 Register Description SPI CONTROL REGISTER (SPICR)

Read/Write

Reset Value: 0000 xxxx (0xh)

| 7    |     |      |      |      |      |      | 0    |

|------|-----|------|------|------|------|------|------|

| SPIE | SPE | SPR2 | MSTR | CPOL | СРНА | SPR1 | SPR0 |

Bit 7 = **SPIE** *Serial Peripheral Interrupt Enable* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SPI interrupt is generated whenever an End of Transfer event, Master Mode Fault or Overrun error occurs (SPIF = 1, MODF = 1 or OVR = 1 in the SPICSR register)

#### Bit 6 = **SPE** Serial Peripheral Output Enable

This bit is set and cleared by software. It is also cleared by hardware when, in master mode,  $\overline{SS} = 0$  (see Section 10.6.5.1 "Master Mode Fault (MODF)"). The SPE bit is cleared by reset, so the SPI peripheral is not initially connected to the external pins.

0: I/O pins free for general purpose I/O 1: SPI I/O pin alternate functions enabled

#### Bit 5 = **SPR2** *Divider Enable*

This bit is set and cleared by software and is cleared by reset. It is used with the SPR[1:0] bits to set the baud rate. Refer to Table 20 SPI Master Mode SCK Frequency.

0: Divider by 2 enabled

1: Divider by 2 disabled

Note: This bit has no effect in slave mode.

#### Bit 4 = MSTR Master Mode

This bit is set and cleared by software. It is also cleared by hardware when, in master mode, SS = 0 (see Section 10.6.5.1 "Master Mode Fault (MODF)").

0: Slave mode

1: Master mode. The function of the SCK pin changes from an input to an output and the functions of the MISO and MOSI pins are reversed.

#### Bit 3 = CPOL Clock Polarity

This bit is set and cleared by software. This bit determines the idle state of the serial Clock. The CPOL bit affects both the master and slave modes.

0: SCK pin has a low level idle state

1: SCK pin has a high level idle state

**Note:** If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

#### Bit 2 = CPHA Clock Phase

This bit is set and cleared by software.

- 0: The first clock transition is the first data capture edge.

- 1: The second clock transition is the first capture edge.

**Note:** The slave must have the same CPOL and CPHA settings as the master.

#### Bits 1:0 = **SPR[1:0]** Serial Clock Frequency

These bits are set and cleared by software. Used with the SPR2 bit, they select the baud rate of the SPI serial clock SCK output by the SPI in master mode.

**Note:** These 2 bits have no effect in slave mode.

#### Table 21. SPI Master Mode SCK Frequency

| Serial Clock          | SPR2 | SPR1 | SPR0 |

|-----------------------|------|------|------|

| f <sub>CPU</sub> /4   | 1    |      | 0    |

| f <sub>CPU</sub> /8   | 0    | 0    | 0    |

| f <sub>CPU</sub> /16  | 0    |      | 1    |

| f <sub>CPU</sub> /32  | 1    |      | 0    |

| f <sub>CPU</sub> /64  | 0    | 1    | U    |

| f <sub>CPU</sub> /128 | - 0  |      | 1    |

# 10.7 LINSCI SERIAL COMMUNICATION INTERFACE (LIN MASTER/SLAVE)

#### 10.7.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

The LIN-dedicated features support the LIN (Local Interconnect Network) protocol for both master and slave nodes.

This chapter is divided into SCI Mode and LIN mode sections. For information on general SCI communications, refer to the SCI mode section. For LIN applications, refer to both the SCI mode and LIN mode sections.

### 10.7.2 SCI Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- 2 receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Overrun, Noise and Frame error detection

- 6 interrupt sources

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error

- Parity interrupt

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

#### 10.7.3 LIN Features

- LIN Master

- 13-bit LIN Synch Break generation

- LIN Slave

- Automatic Header Handling

- Automatic baud rate resynchronization based on recognition and measurement of the LIN Synch Field (for LIN slave nodes)

- Automatic baud rate adjustment (at CPU frequency precision)

- 11-bit LIN Synch Break detection capability

- LIN Parity check on the LIN Identifier Field (only in reception)

- LIN Error management

- LIN Header Timeout

- Hot plugging support

# LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

#### 10.7.5 SCI Mode - Functional Description

#### **Conventional Baud Rate Generator Mode**

The block diagram of the Serial Control Interface in conventional baud rate generator mode is shown in Figure 1.

It uses four registers:

<u>ل</u>رک

- 2 control registers (SCICR1 and SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

#### **Extended Prescaler Mode**

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

# Figure 78. Word Length Programming

#### 10.7.5.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 2).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as a continuous logic high level for 10 (or 11) full bit times.

A Break character is a character with a sufficient number of low level bits to break the normal data format followed by an extra "1" bit to acknowledge the start bit.

| Extended           | Frescaler moue                                                                     | format followed by an extra "1" bit to acknowledge |                        |  |  |

|--------------------|------------------------------------------------------------------------------------|----------------------------------------------------|------------------------|--|--|

|                    | ional prescalers are available in extend-<br>ler mode. They are shown in Figure 3. | the start bit.                                     | ctl                    |  |  |

| – An exter<br>PR)  | nded prescaler receiver register (SCIER-                                           |                                                    | oducile                |  |  |

| – An exte<br>ETPR) | nded prescaler transmitter register (SCI-                                          | R                                                  |                        |  |  |

| Figure 78          | . Word Length Programming                                                          | 1 CLO                                              |                        |  |  |

|                    | 9-bit Word length (M bit is set)                                                   | Possible                                           |                        |  |  |

|                    | Data Character                                                                     | Possible<br>Parity<br>Bit                          | Next Data Character    |  |  |

|                    | Start<br>Bit Bit0 Bit1 Bit2 Bit3 Bit4 Bit5                                         | Bit6 Bit7 Bit8 Stop<br>Bit                         | Start<br>Bit           |  |  |

|                    | Idle Line                                                                          |                                                    | Start<br>Bit           |  |  |

|                    | due                                                                                |                                                    | Extra Start            |  |  |

|                    | Break Character                                                                    |                                                    | Extra Start<br>'1' Bit |  |  |

|                    | ×O                                                                                 |                                                    |                        |  |  |

|                    | 8-bit Word length (M bit is reset)                                                 | Possible                                           | Next Data Character    |  |  |

| $S^{0}$            | Data Character                                                                     | Parity<br>Bit Ne                                   |                        |  |  |

| 0-                 | Start<br>Bit Bit0 Bit1 Bit2 Bit3 Bit4 E                                            | Bit5 Bit6 Bit7 Stop St.<br>Bit Bit                 | art                    |  |  |

|                    |                                                                                    | Sta                                                | od                     |  |  |

|                    | Idle Line                                                                          | Bi                                                 |                        |  |  |

|                    | Break Character                                                                    | Ext                                                |                        |  |  |

|                    |                                                                                    |                                                    |                        |  |  |

# LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

# Figure 88. SCI Block Diagram

# LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

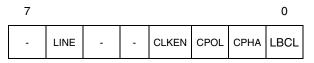

# **CONTROL REGISTER 3 (SCICR3)**

#### Read/Write

Reset Value: 0000 0000 (00h)

Bit 7 = Reserved, must be kept cleared.

#### Bit 6 = LINE LIN Mode Enable.

This bit is set and cleared by software. 0: LIN Mode disabled 1: LIN Master mode enabled

The LIN Master mode enables the capability to send LIN Synch Breaks (13 low bits) using the SBK bit in the SCICR2 register

.In transmission, the LIN Synch Break low phase duration is shown as below:

| LINE | М | Number of low bits sent<br>during a LIN Synch Break |

|------|---|-----------------------------------------------------|

| 0    | 0 | 10                                                  |

| 0    | 1 | 11                                                  |

| 4    | 0 | 13                                                  |

| I    | 1 | 14                                                  |

|      |   |                                                     |

Bits 5:4 = Reserved, forced by hardware to 0. These bits are not used.

Bit 3 = CLKEN Clock Enable.

This bit allows the user to enable the SCLK pin. 0: SLK pin disabled

1: SLK pin enabled

#### Bit 2 = **CPOL** Clock Polarity.

This bit allows the user to select the polarity of the clock output on the SCLK pin. It works in conjunction with the CPHA bit to produce the desired clock/data relationship (see Figure 92 and Figure 93).

- 0: Steady low value on SCLK pin outside transmission window.

- 1: Steady high value on SCLK pin outside transmission window.

### Bit 1 = CPHA Clock Phase.

This bit allows the user to select the phase of the clock output on the SCLK pin. It works in conjunction with the CPOL bit to produce the desired clock/data relationship (see Figure 92 and Figure 93)

- 0: SCLK clock line activated in middle of data bit.

- 1: SCLK clock line activated at beginning of data bit.

# Bit 0 = LBCL Last bit clock pulse.

This bit allows the user to select whether the clock pulse associated with the last data bit transmitted (MSB) has to be output on the SCLK pin.

- 0: The clock pulse of the last data bit is not output to the SCLK pin.

- 1: The clock pulse of the last data bit is output to the SCLK pin.

**Note:** The last bit is the 8th or 9th data bit transmitted depending on the 8 or 9 bit format selected by the M bit in the SCICR1 register.

#### Table 26. SCI clock on SCLK pin

| Data<br>format | M bit | LBCL bit | Number of clock<br>pulses on SCLK |

|----------------|-------|----------|-----------------------------------|

| 8 bit          | 0     | 0        | 7                                 |

| 0 Dit          | 0     | 1        | 8                                 |

| 9 bit          | 1     | 0        | 8                                 |

| 3 DIL          | I     | 1        | 9                                 |

**Note:** These 3 bits (**CPOL**, **CPHA**, **LBCL**) should not be written while the transmitter is enabled.

# beCAN CONTROLLER (Cont'd)

# **10.9.7 BeCAN Cell Limitations**

#### 10.9.7.1 FIFO Corruption

FIFO corruption occurs in the following case:

WHEN the beCAN RX FIFO already holds two messages (that is, FMP == 2)

AND the application releases the FIFO (with the instruction  $CRFR = B_RFOM;$ )

WHILE the beCAN requests the transfer of a new receive message into the FIFO (this lasts one CPU cycle)

As the FIFO pointer is not updated correctly, this causes the last message received to be overwritten by any incoming message. This means one message is lost as shown in the example in Figure 16. The beCAN will not recover normal operation until a device reset occurs.

| cycle)                                             | - <b>(</b> )             |                                                                   |

|----------------------------------------------------|--------------------------|-------------------------------------------------------------------|

| THEN the internal FIFC ed                          | ) pointer is r           | not updat-                                                        |

| BUT the FMP bits are u                             | updated corre            | ectly                                                             |

| Figure 109. FIFO Corruptio                         | on                       |                                                                   |

| FM                                                 | IP FIFO                  | - Pri-                                                            |

| Initial State                                      | 0                        | When the FIFO is empty, v and * point to the same location        |

| Receive Message A                                  | 1 <u>V *</u><br>A<br>V * |                                                                   |

| Receive Message B                                  | 2 A B -                  |                                                                   |

| Receive Message C                                  | 3 A B C                  | does not move because FIFO is full (normal operation)             |

| Release Message A                                  | 2 × V<br>A B C           |                                                                   |

| ▼<br>Release Message B                             |                          | Normal operation                                                  |

| and Receive Message D                              | 2 * v<br>DBC<br>* v      | <ul> <li>* Does not move, pointer corruption</li> </ul>           |

| Receive Message E                                  | 3 E B C                  | D is overwritten by E                                             |

| Release Message C                                  | 2 E B C<br>y             | C released                                                        |

| Release Message E                                  | 1 E B C                  | E released instead of B                                           |

| Release Message B _ (                              | 0 E B C                  | * and v are not pointing to the same message<br>the FIFO is empty |

| * pointer to next receiv<br>v pointer to next mess |                          | leased                                                            |

# beCAN CONTROLLER (Cont'd)

### 10.9.8.3 CAN Filter Registers

# CAN FILTER CONFIGURATION REG.0 (CFCR0)

All bits of this register are set and cleared by software. Read / Write

Reset Value: 0000 0000 (00h)

| 7 |       |       |       |   |       |       | 0     |

|---|-------|-------|-------|---|-------|-------|-------|

| 0 | FSC11 | FSC10 | FACT1 | 0 | FSC01 | FSC00 | FACT0 |

**Note**: To modify the FFAx and FSCx bits, the be-CAN must be in INIT mode.

Bit 7 = Reserved. Forced to 0 by hardware.

Bits 6:5 = **FSC1[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 1.

Bit 4 = **FACT1** *Filter Active* The software sets this bit to activate Filter 1. To modify the Filter 1 registers (CF1R[7:0]), the FACT1 bit must be cleared. 0: Filter 1 is not active 1: Filter 1 is active

Bit 3 = Reserved. Forced to 0 by hardware.

Bits 2:1 = **FSC0[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 0.

Bit 0 = **FACT0** *Filter Active* The software sets this bit to activate Filter 0. To modify the Filter 0 registers (CF0R[0:7]), the FACT0 bit must be cleared. 0: Filter 0 is not active 1: Filter 0 is active

# **CAN FILTER CONFIGURATION REG.1 (CFCR1)**

All bits of this register are set and cleared by software. Read / Write

Reset Value: 0000 0000 (00h)

| 7 |       |       |       |   |       |       | 0     |  |

|---|-------|-------|-------|---|-------|-------|-------|--|

| 0 | FSC31 | FSC30 | FACT3 | 0 | FSC21 | FSC20 | FACT2 |  |

Bit 7 = Reserved. Forced to 0 by hardware.

Bits 6:5 = **FSC3[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 3.

#### Bit 4 = FACT3 Filter Active

The software sets this bit to activate filter 3. To modify the Filter 3 registers (CF3R[0:7]) the FACT3 bit must be cleared. 0: Filter 3 is not active 1: Filter 3 is active

Bit 3 = Reserved. Forced to 0 by hardware.

Bits 2:1 = **FSC2[1:0]** *Filter Scale Configuration* These bits define the scale configuration of Filter 2.

#### Bit 0 = FACT2 Filter Active

The software sets this bit to activate Filter 2. To modify the Filter 2 registers (CF2R[0:7]), the FACT2 bit must be cleared. 0: Filter 2 is not active

1: Filter 2 is active

### 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### 10.10.6 Register Description

#### **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only) Reset Value: 0000 0000 (00h)

| 7   |       |      |      |     |     |     | 0   |

|-----|-------|------|------|-----|-----|-----|-----|

| EOC | SPEED | ADON | SLOW | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by software reading the ADCDRH register or writing to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 = **SPEED** *A/D clock selection* This bit is set and cleared by software.

#### Table 35. A/D Clock Selection

| f <sub>ADC</sub>                                           | SLOW | SPEED |  |

|------------------------------------------------------------|------|-------|--|

| f <sub>CPU</sub> /2                                        | 0    | 0     |  |

| f <sub>CPU</sub> (where f <sub>CPU</sub> <= 4 MHz)         | 0    | 11    |  |

| f <sub>CPU</sub> /4                                        | 1    | 0     |  |

| f <sub>CPU</sub> /2 (same frequency as<br>SLOW=0, SPEED=0) | 15   |       |  |

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **SLOW** A/D Clock Selection This bit is set and cleared by software. It works together with the SPEED bit. Refer to Table 35.

# Bits 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

\*The number of channels is device dependent. Refer to the device pinout description.

| Channel Pin* | CH3 | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | 3   | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

# DATA REGISTER (ADCDRH)

Read Only

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

Bits 7:0 = D[9:2] MSB of Analog Converted Value

#### DATA REGISTER (ADCDRL)

Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bits 7:2 = Reserved. Forced by hardware to 0.

Bits 1:0 = D[1:0] LSB of Analog Converted Value

# EMC CHARACTERISTICS (Cont'd)

# 12.8.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling two LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/ 3 which specifies the board and the loading of each pin.

| Sumbel    | Doromotor                | Conditions                                                              | Monitored         | Max vs. [ | Max vs. [f <sub>OSC</sub> /f <sub>CPU</sub> ] |      |  |

|-----------|--------------------------|-------------------------------------------------------------------------|-------------------|-----------|-----------------------------------------------|------|--|

| Symbol    | Parameter                | Conditions                                                              | Frequency Band    | 8/4 MHz   | 16/8 MHz                                      | Unit |  |

|           |                          |                                                                         | 0.1 MHz to 30 MHz | 10        | 13                                            |      |  |

|           |                          | Flash devices: $V_{DD} = 5V$ , $T_A = +25^{\circ}C$ , LQFP44 package    | 30 MHz to 130 MHz | 12        | 19                                            | dBµ\ |  |

|           |                          | conforming to SAE J 1752/3                                              | 130 MHz to 1 GHz  | 8         | 14                                            |      |  |

|           |                          |                                                                         | SAE EMI Level     | 2.5       | 3                                             | -    |  |

|           |                          |                                                                         | 0.1 MHz to 30 MHz | 31        | 32                                            | 21   |  |

| S         | Peak level <sup>1)</sup> | Flash devices: $V_{DD} = 5V$ , $T_A = +25^{\circ}C$ ,<br>LQFP64 package | 30 MHz to 130 MHz | 32        | 37                                            | dΒμ  |  |

| $S_{EMI}$ | i eak level              | conforming to SAE J 1752/3                                              | 130 MHz to 1 GHz  | 11        | 16                                            |      |  |

|           |                          |                                                                         | SAE EMI Level     | 3.0       | 3.5                                           | -    |  |

|           |                          |                                                                         | 0.1 MHz to 30 MHz | 10        | 18                                            |      |  |

|           |                          | ROM devices: $V_{DD} = 5V$ , $T_A = +25^{\circ}C$ ,<br>LQFP64 package   | 30 MHz to 130 MHz | 15        | 25                                            | dBμ  |  |

|           |                          | conforming to SAE J 1752/3                                              | 130 MHz to 1 GHz  | -3        | 1                                             |      |  |

|           |                          | <b>3</b>                                                                | SAE EMI Level     | 2.0       | 2.5                                           | -    |  |

|           | ted in product           |                                                                         | 25 <sup>0</sup>   |           |                                               |      |  |

| . Not tes | -                        |                                                                         | 25 <sup>0</sup>   |           |                                               |      |  |

| . Not tes | -                        |                                                                         | 25 <sup>0</sup>   |           |                                               |      |  |

| . Not tes | -                        |                                                                         | ,50°              |           |                                               |      |  |

| . Not tes | -                        |                                                                         | 5 <sup>0</sup>    |           |                                               |      |  |

| . Not tes | -                        |                                                                         | ,50°              |           |                                               |      |  |

| . Not tes | -                        |                                                                         | 50,               |           |                                               |      |  |

| . Not tes | -                        |                                                                         | 50,               |           |                                               |      |  |

| . Not tes | -                        |                                                                         | 50,               |           |                                               |      |  |

| . Not tes | -                        |                                                                         | ,50°              |           |                                               |      |  |

| . Not tes | -                        |                                                                         | 50,               |           |                                               |      |  |

| . Not tes | -                        |                                                                         | 50,               |           |                                               |      |  |

### EMC CHARACTERISTICS (Cont'd)

#### 12.8.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity (see Table 39 and Table 40 below). For more details, refer to application note AN1181.

#### 12.8.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the

number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

# 12.8.3.2 Static Latch-Up

■ LU: Two complementary static tests are required on 6 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/ O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard.

#### Table 39. Absolute Maximum Ratings

|                       | n. The sample size depends on the standard             |                        | AUCILS                               | 1.   |

|-----------------------|--------------------------------------------------------|------------------------|--------------------------------------|------|

| Table 39. /<br>Symbol | Absolute Maximum Ratings<br>Ratings                    | Conditions             | Maximum value <sup>1)</sup>          | Unit |

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage (Human Body Model)    | .0.                    | 2000                                 |      |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)       | T <sub>4</sub> = +25°C | 200                                  | v    |

| V <sub>ESD(CDM)</sub> | Electro-static discharge voltage (Charge Device Model) |                        | 750 on corner pins,<br>500 on others |      |

|                       |                                                        |                        |                                      |      |

Notes:

**لركم**

1. Data based on characterization results, not tested in production.

| Table 40. Electrical Sensitivities |           |  |   |

|------------------------------------|-----------|--|---|

|                                    | Cumple al |  | _ |

| Symbol | Parameter             | Conditions                                      | Class      |  |  |  |

|--------|-----------------------|-------------------------------------------------|------------|--|--|--|

| LU     | Static latch-up class | T <sub>A</sub> =+125°C<br>conforming to JESD 78 | II level A |  |  |  |

| R      |                       |                                                 |            |  |  |  |

| 10     |                       |                                                 |            |  |  |  |

| 5010   |                       |                                                 |            |  |  |  |

| 0103   |                       |                                                 |            |  |  |  |

| 0      |                       |                                                 |            |  |  |  |