# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | CANbus, LINbusSCI, SPI                                                 |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 48                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f561r9tctr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Γ | P      | Pin n  | 0      |                           |      | Le             | evel   |       |     | Р   | ort |     |                 | Main               | on                               |                       |  |

|---|--------|--------|--------|---------------------------|------|----------------|--------|-------|-----|-----|-----|-----|-----------------|--------------------|----------------------------------|-----------------------|--|

|   | 964    | 944    | 32     | Pin Name                  | Type | Ħ              | out    |       | In  | out |     | Out | tput            | function<br>(after | Alternate                        | function              |  |

|   | LQFP64 | LQFP44 | LQFP32 |                           | F    | Input          | Output | float | ndm | int | ana | OD  | РР              | reset)             |                                  |                       |  |

| 2 | 23     | 14     | 11     | PB6 / AIN2 /<br>T16_OCMP1 | I/O  | С <sub>Т</sub> |        | x     | х   |     | RB  | х   | х               | Port B6            | TIM16 Out-<br>put Com-<br>pare 1 | ADC Analog<br>Input 2 |  |

| 2 | 24     | 15     | -      | V <sub>SS_2</sub>         | S    |                |        |       |     |     |     |     |                 | Digital G          | round Voltage                    |                       |  |

| 2 | 25     | 16     | -      | V <sub>DD_2</sub>         | S    |                |        |       |     |     |     |     |                 | Digital Ma         | ain Supply Vol                   | tage                  |  |

| 2 | 26     | 17     | 12     | PB7 /AIN3 /<br>T16_OCMP2  | I/O  | С <sub>Т</sub> |        | x     | х   |     | RB  | х   | х               | Port B7            | TIM16 Out-<br>put Com-<br>pare 2 | ADC Analog<br>Input 3 |  |

| 2 | 27     | 18     | 13     | PC0 / AIN4 /<br>T16_ICAP1 | I/O  | CT             |        | x     | х   |     | RB  | х   | х               | Port C0            | TIM16 Input<br>Capture 1         | ADC Analog<br>Input 4 |  |

| 2 | 28     | 19     | 14     | PC1 (HS) / T16_ICAP2      | I/O  | $C_T$          | HS     | Х     | е   | i2  |     | Х   | Х               | Port C1            | TIM16 Input                      | Capture 2             |  |

| 2 | 29     | 20     | 15     | PC2 (HS) /<br>T16_EXTCLK  | I/O  | CT             | HS     | x     |     | ei2 |     | х   | х               | Port C2            | TIM16 Extern                     | al Clock input        |  |

| : | 30     | 21     | -      | PE4                       | I/O  | $T_{T}$        |        | Χ     | Х   |     |     | Х   | X               | Port E4            |                                  |                       |  |

| ; | 31     | -      | -      | NC                        |      | 1              |        |       |     |     |     | Not | Con             | nected             |                                  |                       |  |

| ; | 32     | 22     | 16     | V <sub>PP</sub>           | I    |                |        |       |     |     | 5   | D.  |                 |                    | rogramming voltage. Must b       |                       |  |

| : | 33     | 23     | 17     | PC3 / CANRX               | I/O  | $C_T$          |        | X     | Х   | Y   |     | Х   | Х               | Port C3            | CAN Receive                      | e Data Input          |  |

| ; | 34     | 24     | 18     | PC4 / CANTX               | I/O  | $C_T$          |        | Х     | )   |     |     |     | X <sup>2)</sup> | Port C4            | CAN Transm                       | it Data Output        |  |

| ; | 35     | -      | -      | PE5                       | I/O  | TT             |        | X     | Х   |     |     | Х   | Х               | Port E5            |                                  |                       |  |

| ( | 36     | 25     | -      | PE6 / AIN5                | I/O  | T <sub>T</sub> | 10     | Х     | Х   |     | Х   | Х   | Х               | Port E6            | ADC Analog                       | Input 5               |  |

|   | 37     | 26     | 19     | PC5 /MISO                 | I/O  | CT             |        | Χ     | Х   |     |     | Х   | Х               | Port C5            | SPI Master Ir                    | n/Slave Out           |  |

|   | 38     | 27     | 20     | PC6 / MOSI                | I/O  | $C_{T}$        |        | Χ     | Х   |     |     | Х   | Х               | Port C6            | SPI Master C                     | ut/Slave In           |  |

| ; | 39     | 28     | 21     | PC7 /SCK                  | I/O  | $C_T$          |        | Х     | Х   |     |     | Х   | Х               | Port C7            | SPI Serial Cl                    | ock                   |  |

| 4 | 10     | -      | -      | V <sub>SS_1</sub>         | S    |                |        |       |     |     |     |     |                 | Digital G          | ound Voltage                     |                       |  |

| 4 | 11     | -      | -      | V <sub>DD_1</sub>         | S    |                |        |       |     |     |     |     |                 | Digital Ma         | ain Supply Vol                   | tage                  |  |

| 4 | 12     | 29     | 22     | PD0 / SS/ AIN6            | I/O  | CT             |        | х     | е   | i3  | х   | х   | х               | Port D0            | SPI Slave<br>Select              | ADC Analog<br>Input 6 |  |

| 4 | 13     | 1      | ):     | PE7                       | I/O  | TT             |        | Χ     | Х   |     |     | Х   | Х               | Port E7            |                                  |                       |  |

| 4 | 14     | 2      | -      | PF0                       | I/O  | $T_{T}$        |        | Χ     | Х   |     |     | Х   | Х               | Port F0            |                                  |                       |  |

|   | 15     | 30     | -      | PF1 / AIN7                | I/O  | $T_{T}$        |        | Χ     | Х   |     | Х   | Х   | Х               | Port F1            | ADC Analog                       | Input 7               |  |

| 4 | 16     | 31     | -      | PF2 / AIN8                | I/O  | $T_{T}$        |        | Χ     | Х   |     | Х   | Х   | Х               | Port F2            | ADC Analog                       | Input 8               |  |

| 4 | 17     | 32     | 23     | PD1 / SCI1_RDI            | I/O  | CT             |        | x     |     | ei3 |     | х   | х               | Port D1            | LINSCI1 Rec<br>put               | eive Data in-         |  |

| 4 | 18     | 33     | 24     | PD2 / SCI1_TDO            | I/O  | C <sub>T</sub> |        | x     | х   |     |     | х   | х               | Port D2            | LINSCI1 Trar<br>output           | nsmit Data            |  |

| 4 | 19     | -      | -      | PF3 / AIN9                | I/O  | $T_{T}$        |        | Х     | Х   |     | Х   | Х   | Х               | Port F3            | ADC Analog Input 9               |                       |  |

| ! | 50     | -      | -      | PF4                       | I/O  | $T_T$          |        | Х     | Х   |     |     | Х   | Х               | Port F4            | +                                |                       |  |

| ! | 51     | -      | -      | TLI                       | Ι    | $C_T$          |        | Х     |     | Х   |     |     |                 | Top level          | vel interrupt input pin          |                       |  |

| ! | 52     | 34     | -      | PF5                       | I/O  | $T_T$          |        | Х     | Х   |     |     | Х   | Х               | Port F5            | 5                                |                       |  |

| į | 53     | 35     | 25     | PD3 (HS) / SCI2_SCK       | I/O  | CT             | HS     | x     | х   |     |     | х   | х               | Port D3            | LINSCI2 Seri                     | al Clock Out-         |  |

#### INTERRUPTS (Cont'd)

| Instruction | New Description                 | Function/Example      | 11 | Н | 10 | Ν      | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|--------|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |        |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | 11 | Н | 10 | Ν      | Z | С |

| JRM         | Jump if I1:0 = 11 (level 3)     | 11:0 = 11 ?           |    |   |    |        |   |   |

| JRNM        | Jump if I1:0 <> 11              | 1:0 <> 11 ?           |    |   |    |        |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | 11 | Н | 10 | Ν      | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |        | 9 |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  | X      |   |   |

| TRAP        | Software trap                   | Software NMI          | 1  |   | 1  | D<br>D | / |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  | 5      |   |   |

#### **Table 8. Dedicated Interrupt Instruction Set**

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

57

#### INTERRUPTS (Cont'd)

#### **Table 9. Interrupt Mapping**

| N° | Source<br>Block | Description                                          | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT <sup>1)</sup> | Address<br>Vector |

|----|-----------------|------------------------------------------------------|-------------------|-------------------|------------------------------------|-------------------|

|    | RESET           | Reset                                                | N/A               |                   | yes                                | FFFEh-FFFFh       |

|    | TRAP            | Software interrupt                                   | IN/A              |                   | no                                 | FFFCh-FFFDh       |

| 0  | TLI             | External top level interrupt                         | EICR              | Highest           | yes                                | FFFAh-FFFBh       |

| 1  | MCC/RTC         | Main clock controller time base interrupt            | MCCSR             | Priority          | yes                                | FFF8h-FFF9h       |

| 2  | ei0/AWUFH       | External interrupt ei0/ Auto wake-up from Halt       | EICR/<br>AWUCSR   |                   |                                    | FFF6h-FFF7h       |

| 3  | ei1/AVD         | External interrupt ei1/Auxiliary Voltage Detector    | EICR/<br>SICSR    |                   | yes <sup>2)</sup>                  | FFF4h-FFF5h       |

| 4  | ei2             | External interrupt ei2                               | EICR              |                   | 0.                                 | FFF2h-FFF3h       |

| 5  | ei3             | External interrupt ei3                               | EICR              | 5KC               |                                    | FFF0h-FFF1h       |

| 6  | CAN             | CAN peripheral interrupt - RX                        | CIER              |                   | no                                 | FFEEh-FFEFh       |

| 7  | CAN             | CAN peripheral interrupt - TX / ER / SC              | CIER              |                   | yes <sup>3)</sup>                  | FFECh-FFEDh       |

| 8  | SPI             | SPI peripheral interrupts                            | SPICSR            |                   | yes                                | FFEAh-FFEBh       |

| 9  | TIMER8          | 8-bit TIMER peripheral interrupts                    | T8_TCR1           |                   | no                                 | FFE8h-FFE9h       |

| 10 | TIMER16         | 16-bit TIMER peripheral interrupts                   | TCR1              |                   | no                                 | FFE6h-FFE7h       |

| 11 | LINSCI2         | LINSCI2 Peripheral interrupts                        | SCI2CR1           |                   | no                                 | FFE4h-FFE5h       |

| 12 | LINSCI1         | LINSCI1 Peripheral interrupts (LIN Master/<br>Slave) | SCI1CR1           | ↓<br>Lowest       | no <sup>4)</sup>                   | FFE2h-FFE3h       |

| 13 | PWM ART         | 8-bit PWM ART interrupts                             | PWMCR             | Priority          | yes                                | FFE0h-FFE1h       |

Notes:

1050'

1. Valid for HALT and ACTIVE HALT modes except for the MCC/RTC interrupt source which exits from ACTIVE HALT mode only. ....

2. Except AVD interrupt

3. Exit from Halt only when a wake-up condition is detected, generating a Status Change interrupt. See Section 10.8.6 on page 160.

4. It is possible to exit from Halt using the external interrupt which is mapped on the RDI pin.

#### POWER SAVING MODES (Cont'd)

#### 8.3 WAIT MODE

WAIT mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the 'WFI' instruction.

All peripherals remain active. During WAIT mode, the I[1:0] bits of the CC register are forced to '10', to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or RESET occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine.

The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

Jbsolete Producils

Refer to Figure 24

#### OSCILLATOR ON PERIPHERALS ON WFI INSTRUCTION CPU OFF I[1:0] BITS 10 Ν RESET Y Ν INTERRUPT Y OSCILLATOR ON PERIPHERALS OFF CPU ON I[1:0] BITS 10 256 OR 4096 CPU CLOCK CYCLE DELAY OSCILLATOR ON PERIPHERALS ON CPU ON I[1:0] BITS XX<sup>1)</sup> FETCH RESET VECTOR **OR SERVICE INTERRUPT**

#### Note:

**1.** Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

#### Figure 24. WAIT Mode Flow-chart

#### WINDOW WATCHDOG (Cont'd)

10.1.9 Interrupts

None.

## 10.1.10 Register Description CONTROL REGISTER (WDGCR)

Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | Т3 | T2 | T1 | то |

#### Bit 7 = WDGA Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte.

Bits 6:0 = **T[6:0]** 7-bit counter (MSB to LSB). These bits contain the value of the watchdog counter. It is decremented every 16384  $f_{OSC2}$  cycles (approx.). A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

#### WINDOW REGISTER (WDGWR)

Read/Write

Reset Value: 0111 1111 (7Fh)

| 7 |    |    |    |    |    |    | 0  |

|---|----|----|----|----|----|----|----|

| - | W6 | W5 | W4 | WЗ | W2 | W1 | WO |

Bit 7 = Reserved

Bits 6:0 = **W[6:0]** *7-bit window value* These bits contain the window value to be compared to the downcounter.

#### Figure 38. Watchdog Timer Register Map and Reset Values

|        | Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |

|--------|-------------------|-------------------|------|----|----|----|----|----|----|----|--|

|        | 2F                | WDGCR             | WDGA | Т6 | T5 | T4 | ТЗ | T2 | T1 | то |  |

|        | $O^{2}$           | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |  |

| $\cup$ | 30                | WDGWR             | -    | W6 | W5 | W4 | W3 | W2 | W1 | W0 |  |

|        | 30                | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |  |

#### 16-BIT TIMER (Cont'd)

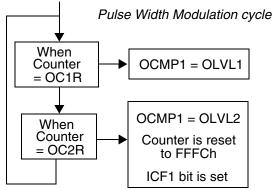

#### 10.4.3.6 Pulse Width Modulation Mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality can not be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

#### Procedure

To use Pulse Width Modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula in the opposite column.

- 2. Load the OC1R register with the value corresponding to the period of the pulse if (OLVL1 = 0 and OLVL2 = 1) using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

If OLVL1 = 1 and OLVL2 = 0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$OC_{i}R Value = \frac{t \cdot t_{CPU}}{PRESC} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 17 Clock Control Bits)

If the timer clock is an external clock the formula is:

Where:

= Signal or pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (See Figure 58)

#### Notes:

- 1. After a write instruction to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- 3. The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4. In PWM mode the ICAP1 pin can not be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and ICF1 can also generates interrupt if ICIE is set.

- 5. When the Pulse Width Modulation (PWM) and One Pulse mode (OPM) bits are both set, the PWM mode is the only active one.

#### 16-BIT TIMER (Cont'd)

## OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

#### Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| /   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

## OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### **COUNTER HIGH REGISTER (CHR)**

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   | 0   |

|-----|-----|

| MSB | LSB |

|     |     |

#### **COUNTER LOW REGISTER (CLR)**

#### Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## ALTERNATE COUNTER HIGH REGISTER (ACHR)

#### Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## ALTERNATE COUNTER LOW REGISTER (ACLR)

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## INPUT CAPTURE 2 HIGH REGISTER (IC2HR)

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### **INPUT CAPTURE 2 LOW REGISTER (IC2LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 1   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

### 8-BIT TIMER (Cont'd) INPUT CAPTURE 1 REGISTER (IC1R)

Read Only

\_

Reset Value: Undefined

This is an 8-bit read only register that contains the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### **OUTPUT COMPARE 1 REGISTER (OC1R)**

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the value to be compared to the CTR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### **OUTPUT COMPARE 2 REGISTER (OC2R)**

Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the value to be compared to the CTR register.

#### **COUNTER REGISTER (CTR)**

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

|     |  |  |  |     |

## ALTERNATE COUNTER REGISTER (ACTR)

Read Only Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 9   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### **INPUT CAPTURE 2 REGISTER (IC2R)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### **ON-CHIP PERIPHERALS** (cont'd)

#### **10.6 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 10.6.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 10.6.2 Main Features

- Full duplex synchronous transfers (on three lines)

- Simplex synchronous transfers (on two lines)

- Master or slave operation

- 6 master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

Note: In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

#### **10.6.3 General Description**

Figure 70 on page 110 shows the serial peripheral interface (SPI) block diagram. There are three registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through four pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 10.6.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

#### How to operate the SPI in master mode

To operate the SPI in master mode, perform the following steps in order:

- Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 74 shows the four possible configurations. **Note:** The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits

Note: MSTR and SPE bits remain set only if SS is high).

Important note: if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account.

The transmit sequence begins when software writes a byte in the SPIDR register.

#### 10.6.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register

Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### 10.6.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- 1. Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see Figure 74). Note: The slave must have the same CPOL and CPHA settings as the master.

- Manage the  $\overline{SS}$  pin as described in Section 10.6.3.2 and Figure 72. If CPHA = 1 SS must be held low continuously. If CPHA = 0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- 2. Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

#### 10.6.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- A write or a read to the SPIDR register

Notes: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.6.5.2).

## 10.6.8 Register Description SPI CONTROL REGISTER (SPICR)

Read/Write

Reset Value: 0000 xxxx (0xh)

| 7    |     |      |      |      |      |      | 0    |

|------|-----|------|------|------|------|------|------|

| SPIE | SPE | SPR2 | MSTR | CPOL | СРНА | SPR1 | SPR0 |

Bit 7 = **SPIE** *Serial Peripheral Interrupt Enable* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SPI interrupt is generated whenever an End of Transfer event, Master Mode Fault or Overrun error occurs (SPIF = 1, MODF = 1 or OVR = 1 in the SPICSR register)

#### Bit 6 = **SPE** Serial Peripheral Output Enable

This bit is set and cleared by software. It is also cleared by hardware when, in master mode,  $\overline{SS} = 0$  (see Section 10.6.5.1 "Master Mode Fault (MODF)"). The SPE bit is cleared by reset, so the SPI peripheral is not initially connected to the external pins.

0: I/O pins free for general purpose I/O 1: SPI I/O pin alternate functions enabled

#### Bit 5 = **SPR2** *Divider Enable*

This bit is set and cleared by software and is cleared by reset. It is used with the SPR[1:0] bits to set the baud rate. Refer to Table 20 SPI Master Mode SCK Frequency.

0: Divider by 2 enabled

1: Divider by 2 disabled

Note: This bit has no effect in slave mode.

#### Bit 4 = MSTR Master Mode

This bit is set and cleared by software. It is also cleared by hardware when, in master mode, SS = 0 (see Section 10.6.5.1 "Master Mode Fault (MODF)").

0: Slave mode

1: Master mode. The function of the SCK pin changes from an input to an output and the functions of the MISO and MOSI pins are reversed.

#### Bit 3 = CPOL Clock Polarity

This bit is set and cleared by software. This bit determines the idle state of the serial Clock. The CPOL bit affects both the master and slave modes.

0: SCK pin has a low level idle state

1: SCK pin has a high level idle state

**Note:** If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

#### Bit 2 = CPHA Clock Phase

This bit is set and cleared by software.

- 0: The first clock transition is the first data capture edge.

- 1: The second clock transition is the first capture edge.

**Note:** The slave must have the same CPOL and CPHA settings as the master.

#### Bits 1:0 = **SPR[1:0]** Serial Clock Frequency

These bits are set and cleared by software. Used with the SPR2 bit, they select the baud rate of the SPI serial clock SCK output by the SPI in master mode.

**Note:** These 2 bits have no effect in slave mode.

#### Table 21. SPI Master Mode SCK Frequency

| Serial Clock          | SPR2 | SPR1 | SPR0 |

|-----------------------|------|------|------|

| f <sub>CPU</sub> /4   | 1    |      | 0    |

| f <sub>CPU</sub> /8   | 0    | 0    | 0    |

| f <sub>CPU</sub> /16  | 0    |      | 1    |

| f <sub>CPU</sub> /32  | 1    |      | 0    |

| f <sub>CPU</sub> /64  | 0    | 1    | U    |

| f <sub>CPU</sub> /128 | - 0  |      | 1    |

57

## LINSCI™ SERIAL COMMUNICATION INTERFACE (SCI Mode) (cont'd)

#### 10.7.8 SCI Mode Register Description

#### **STATUS REGISTER (SCISR)**

Read Only

Reset Value: 1100 0000 (C0h)

| 7    |    |      |      |                  |                  |                  | 0                |

|------|----|------|------|------------------|------------------|------------------|------------------|

| TDRE | тс | RDRF | IDLE | OR <sup>1)</sup> | NF <sup>1)</sup> | FE <sup>1)</sup> | PE <sup>1)</sup> |

Bit 7 = **TDRE** *Transmit data register empty*

This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Data is not transferred to the shift register

1: Data is transferred to the shift register

#### Bit 6 = **TC** Transmission complete

This bit is set by hardware when transmission of a character containing Data is complete. An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

**Note:** TC is not set after the transmission of a Preamble or a Break.

#### Bit 5 = **RDRF** *Received data ready flag*

This bit is set by hardware when the content of the RDR register has been transferred to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: Data is not received

1: Received data is ready to be read

#### Bit 4 = **IDLE** *Idle line detected*

This bit is set by hardware when an Idle Line is detected. An interrupt is generated if the ILIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Idle Line is detected

1: Idle Line is detected

**Note:** The IDLE bit will not be set again until the RDRF bit has been set itself (that is, a new idle line occurs).

#### Bit 3 = **OR** Overrun error

The OR bit is set by hardware when the word currently being received in the shift register is ready to be transferred into the RDR register whereas RDRF is still set. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Overrun error

1: Overrun error detected

**Note:** When this bit is set, RDR register contents will not be lost but the shift register will be overwritten.

#### Bit 2 = NF Character Noise flag

This bit is set by hardware when noise is detected on a received character. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No noise 1: Noise is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.

#### Bit 1 = FE Framing error

This bit is set by hardware when a desynchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Framing error

1: Framing error or break character detected

**Note:** This bit does not generate an interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both a frame error and an overrun error, it will be transferred and only the OR bit will be set.

#### Bit 0 = **PE** Parity error

This bit is set by hardware when a byte parity error occurs (if the PCE bit is set) in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE = 1 in the SCICR1 register.

0: No parity error

1: Parity error detected

#### LINSCI™ SERIAL COMMUNICATION INTERFACE (LIN Mode) (cont'd)

If LHE bit is set due to this error during Fields other than LIN Synch Field or if LASE bit is reset then the current received Header is discarded and the SCI searches for a new Break Field.

#### Note on LIN Header Time-out Limit

According to the LIN specification, the maximum length of a LIN Header which does not cause a timeout is equal to 1.4 \* (34 + 1) = 49 T<sub>BIT MASTER</sub>.

$T_{BIT\_MASTER}$  refers to the master baud rate.

When checking this timeout, the slave node is desynchronized for the reception of the LIN Break and Synch fields. Consequently, a margin must be allowed, taking into account the worst case: This occurs when the LIN identifier lasts exactly 10  $T_{BIT\_MASTER}$  periods. In this case, the LIN Break and Synch fields last 49 - 10 =  $39T_{BIT\_MASTER}$  periods.

Assuming the slave measures these first 39 bits with a desynchronized clock of 15.5%. This leads to a maximum allowed Header Length of:

39 x (1/0.845)  $T_{BIT\_MASTER}$  + 10 $T_{BIT\_MASTER}$

### = 56.15 T<sub>BIT\_SLAVE</sub>

A margin is provided so that the time-out occurs when the header length is greater than 57  $T_{BIT\_SLAVE}$  periods. If it is less than or equal to 57  $T_{BIT\_SLAVE}$  periods, then no timeout occurs.

## LIN Header Length

Even if no timeout occurs on the LIN Header, it is possible to have access to the effective LIN header Length ( $T_{HEADER}$ ) through the LHL register. This allows monitoring at software level the  $T_{FRAME\_MAX}$  condition given by the LIN protocol.

This feature is only available when LHDM bit = 1 or when LASE bit = 1.

#### Mute Mode and Errors

In mute mode when LHDM bit = 1, if an LHE error occurs during the analysis of the LIN Synch Field or if a LIN Header Time-out occurs then the LHE bit is set but it does not wake up from mute mode. In this case, the current header analysis is discarded. If needed, the software has to reset LSF bit. Then the SCI searches for a new LIN header.

In mute mode, if a framing error occurs on a data (which is not a break), it is discarded and the FE bit is not set.

When LHDM bit = 1, any LIN header which respects the following conditions causes a wake-up from mute mode:

- A valid LIN Break Field (at least 11 dominant bits followed by a recessive bit)

- A valid LIN Synch Field (without deviation error)

- A LIN Identifier Field without framing error. Note that a LIN parity error on the LIN Identifier Field does not prevent wake-up from mute mode.

- No LIN Header Time-out should occur during Header reception.

**47/**

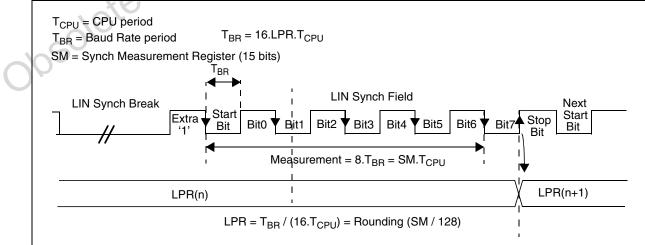

## Figure 83. LIN Synch Field Measurement

<u>ل</u>رک

#### LINSCI<sup>TM</sup> SERIAL COMMUNICATION INTERFACE (LIN Master Only) (Cont'd)

#### 10.8.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

When the transmit enable bit (TE) is set, the data in the transmit shift register is output on the TDO pin and the corresponding clock pulses are output on the SCLK pin.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 89).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to send an idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

1. An access to the SCISR register

2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit or after the break frame) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

1. An access to the SCISR register

2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 89).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### **Idle Characters**

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

#### LIN Transmission

The same procedure has to be applied for LIN Master transmission with the following differences:

- Clear the M bit to configure 8-bit word length.

- Set the LINE bit to enter LIN master mode. In this case, setting the SBK bit sends 13 low bits.

## beCAN CONTROLLER (Cont'd)

### Figure 102. Filter Bank Scale Configuration - Register Organisation

|                           | Filter Bank Scale  | Configuration            | Filter Bank Scale Co   | nfig. Bits <sup>1</sup> |

|---------------------------|--------------------|--------------------------|------------------------|-------------------------|

|                           | One 32-Bit Filter  |                          | FSCx = 3               |                         |

| Identifier                | CFxR0              | CFxR1                    | CFxR2                  | CFxR3                   |

| Mask/Ident.               | CFxR4              | CFxR5                    | CFxR6                  | CFxR7                   |

| Bit Mapping               | STID10:3           | STID2:0 RTR DE EXID17:15 | EXID14:7               | EXID6:0                 |

|                           | Two 16-Bit Filters |                          |                        |                         |

| Identifier                | CFxR0              | CFxR1                    |                        | .151                    |

| Mask/Ident.               | CFxR2              | CFxR3                    | 500 0                  | CIL S                   |

| Identifier                | CFxR4              | CFxR5                    | FSCx = 2               | 21/0                    |

| Mask/Ident.               | CFxR6              | CFxR7                    | . (                    | $\gamma^{O}$            |

| Bit Mapping               | STID10:3           | STID2:0 RTR DE EXID17:15 | 01                     | oduct(S)                |

|                           | One 16-Bit / Two   |                          | oletepri               |                         |

| Identifier                | CFxR0              | CFxR1                    |                        |                         |

| Mask/Ident.               | CFxR2              | CFxR3                    | 5                      |                         |

| ldentifier<br>Mask/Ident. | CFxR4<br>CFxR5     |                          |                        |                         |

| ldentifier<br>Mask/Ident. | CFxR6<br>CFxR7     | ((5)                     | FSCx = 1               |                         |

|                           | Four 8-Bit Filters |                          |                        |                         |

| Identifier<br>Mask/Ident. | CFxR0<br>CFxR1     | ]                        |                        |                         |

| ldentifier<br>Mask/Ident. | CFxR2<br>CFxR3     | ]                        |                        |                         |

| Identifier<br>Mask/Ident. | CFxR4<br>CFxR5     | ]                        | FSCx = 0               |                         |

| Identifier                | CFxR6              | ] ,                      | k = filter bank number |                         |

| Mask/Ident.               | CFxR7              | 1                        | Those bits are leasts  | d in the CFCR register  |

| Bit Mapping               | STID10:3           | 1                        |                        | a in the Cron register  |

57

#### beCAN CONTROLLER (Cont'd)

#### Workaround

To implement the workaround, use the following sequence to release the CAN receive FIFO. This sequence replaces any occurrence of  $CRFR \mid = B_RFOM$ ;

#### Figure 110. Workaround 1

```

if ((CRFR & 0x03) == 0x02)

while (( CMSR & 0x20) && ( CDGR & 0x08) ) { };

CRFR |= B_RFOM;

```

#### **Explanation of Workaround 1**

First, we need to make sure no interrupt can occur between the test and the release of the FIFO to avoid any added delay.

The workaround checks if the first two FIFO levels are already full (FMP = 2) as the problem happens only in this case.

If FMP  $\neq$  2 we release the FIFO immediately, if FMP = 2, we monitor the reception status of the cell.

The reception status is available in the CMSR register bit 5 (REC bit). **Note:** The REC bit was called RX in older versions of the datasheet.

- If the cell is not receiving, then REC bit in CMSR is at 0, the software can release the FIFO immediately: there is no risk.

- If the cell is receiving, it is important to make sure the release of the mailbox will not happen at the time when the received message is loaded into the FIFO.

We could simply wait for the end of the reception, but this could take a long time (200µs for a 100-bit frame at 500 kHz), so we also monitor the Rx pin of the microcontroller to minimize the time the application may wait in the while loop.

We know the critical window is located at the end of the frame, 6+ CAN bit times after the acknowledge bit (exactly six full bit times plus the time from the beginning of the bit to the sample point). Those bits represent the acknowledge delimiter + the end of frame slot.

We know also that those 6+ bits are in recessive state on the bus, therefore if the CAN Rx pin of the device is at '0', (reflecting a CAN dominant state on the bus), this is early enough to be sure we can release the FIFO before the critical time slot.

Therefore, if the device hardware pin Rx is at 0 and there is a reception on going, its message will be transferred to the FIFO only 6+ CAN bit times later at the earliest (if the dominant bit is the acknowledge) or later if the dominant bit is part of the message.

Compiled with Cosmic C compiler, the workaround generates the following assembly lines:

```

Cycles

if ((CRFR \& 0x03) == 0x02)

ld

a, CRFR

3

2

and

a,#3

ср

a,#2

2

jrne

RELEASE

3

test: 10 cycles

while

(( CMSR & 0x20) && ( CDGR & 0x08) )

{ };

WHILELOOP:

btjf

CMSR, #5, RELEASE

5

btjt

CDGR,#3, WHILELOOP

5

loop: 10 cycles

CRFR |= B RFOM;

RELEASE:

CRFR,#5

release: 5 cycles

bset

5

```

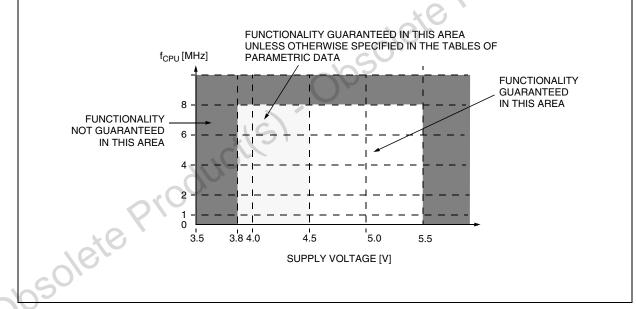

#### **12.3 OPERATING CONDITIONS**

#### **12.3.1 General Operating Conditions**

| Symbol                           | Parameter                                                                        | Conditions                                              | Min | Max | Unit   |

|----------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------|-----|-----|--------|

| f <sub>CPU</sub>                 | Internal clock frequency                                                         |                                                         | 0   | 8   | MHz    |

|                                  | Extended Operating voltage                                                       | No Flash Write/Erase. Analog parameters not guaranteed. | 3.8 | 4.5 | V      |

| $V_{DD}$                         | Internal clock frequency Extended Operating voltage No Flash Write/Erase. Analog | 4.5                                                     | 5.5 |     |        |

|                                  | Operating Voltage for Flash Write/Erase                                          | V <sub>PP</sub> = 11.4 to 12.6V                         | 4.5 | 5.5 |        |

|                                  |                                                                                  | 1 Suffix Version                                        | 0   | 70  |        |

|                                  |                                                                                  | 5 Suffix Version                                        | -10 | 85  | $\sim$ |

| Operating Voltage for Flash Writ | Ambient temperature range                                                        | 6 Suffix Version                                        |     | 85  | D ∘C   |

|                                  |                                                                                  | 7 Suffix Version                                        | -40 | 105 |        |

|                                  |                                                                                  | 3 Suffix Version                                        |     | 125 | 1      |

### Figure 119. f<sub>CPU</sub> Maximum vs V<sub>DD</sub>

**Note:** It is mandatory to connect all available  $V_{DD}$  and  $V_{DDA}$  pins to the supply voltage and all  $V_{SS}$  and  $V_{SSA}$  pins to ground.

## **14 DEVICE CONFIGURATION AND ORDERING INFORMATION**

Each device is available for production in user programmable versions (FLASH) as well as in factory coded versions (ROM/FASTROM).

ST72561 devices are ROM versions. ST72P561 devices are Factory Advanced Service Technique ROM (FASTROM) versions: They are factory-programmed HDFlash devices.

ST72F561 FLASH devices are shipped to customers with a default content (FFh), while ROM factory coded parts contain the code supplied by the customer. This implies that FLASH devices have to be configured by the customer using the Option Bytes while the ROM devices are factory-configured.

#### **14.1 FLASH OPTION BYTES**

The option bytes allows the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program directly the FLASH devices using ICP, FLASH devices are shipped to customers with a reserved internal clock source enabled. In masked ROM devices, the option bytes are fixed in hardware by the ROM code (see option list).

#### **OPTION BYTE 0**

OPT7 = **WDGHALT** Watchdog reset on HALT This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

- 0: No Reset generation when entering Halt mode

- 1: Reset generation when entering Halt mode

OPT6 = **WDGSW** *Hardware or software watchdog* This option bit selects the watchdog type. 0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

OPT4 = **LVD** Voltage detection This option bit enables the voltage detection block (LVD).

| Selected Low Voltage Detector | VD |  |  |

|-------------------------------|----|--|--|

| LVD Off                       | 1  |  |  |

| LVD On                        | 0  |  |  |

#### OPT3 = PLL OFF PLL activation

This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL is guaranteed only with an input frequency between 2 and 4 MHz.

0: PLL x2 enabled

1: PLL x2 disabled

**Caution**: The PLL can be enabled only if the "OSC RANGE" (OPT11:10) bits are configured to "MP - 2~4 MHz". Otherwise, the device functionality is not guaranteed.

|              |                 | STATIC OPTION BYTE 0           7         0 |    |       |     |      |     |   |     | STATIC OPTION BYTE 1 7 |   |         |   |   |   |      | 0   |

|--------------|-----------------|--------------------------------------------|----|-------|-----|------|-----|---|-----|------------------------|---|---------|---|---|---|------|-----|

|              |                 |                                            |    | rved  | LVD | OFF  | PKG |   | ш.  | AFI_MAP                |   | OSCTYPE |   |   |   | rved | TC  |

| $\mathbf{O}$ | 02              | HALT                                       | SW | Resei | LVD | PLLQ | 1   | 0 | FMP | 1                      | 0 | 1       | 0 | 1 | 0 | Rese | 'SH |

|              | De-<br>fault(*) | 1                                          | 1  | 1     | 1   | 1    | 1   | 1 | 1   | 1                      | 1 | 1       | 0 | 1 | 1 | 1    | 1   |

(\*): Option bit values programmed by ST

#### **IMPORTANT NOTES** (Cont'd)

#### Figure 154.LINSCI Interrupt Routine

```

@interrupt void LINSCI_IT ( void ) /* LINSCI interrupt routine */

{

/* clear flags */

SCISR buffer = SCISR;

SCIDR_buffer = SCIDR;

if ( SCISR_buffer & LHE ) /* header error ? */

{

if (!LHLR) /* header time-out? */

{

if ( !(SCICR2 & RWU) )/* active mode ?

_asm("sim");/* disable interrupts */

SCISR:

SCIDR; /* Clear RDRF flag */

SCICR2 |= RWU; /* set mute mode */

SCISR;

SCIDR; /* Clear RDRF flag */

SCICR2 |= RWU; /* set mute mode */

_asm("rim");/* enable interrupts */

}

}

}

}

Example using Cosmic compiler syntax

```

## 16.1.6 TIMD set simultaneously with OC interrupt

If the 16-bit timer is disabled at the same time the output compare event occurs then the output compare flag gets locked and cannot be cleared before the timer is enabled again.

**Impact on the application:** If output compare interrupt is enabled, then the output compare flag cannot be cleared in the timer interrupt routine. Consequently the interrupt service routine is called repeatedly and the application get stuck which causes the watchdog reset if enabled by the application.

**Workaround:** Disable the timer interrupt before disabling the timer. Again while enabling, first enable the timer, then the timer interrupts.

Perform the following to disable the timer:

- TACR1 or TBCR1 = 0x00h; // Disable the compare interrupt

- TACSR | or TBCSR | = 0x40; // Disable the timer

- Perform the following to enable the timer again:

- TACSR & or TBCSR &= ~0x40; // Enable the timer

- TACR1 or TBCR1 = 0x40; // Enable the compare interrupt

#### 16.1.7 CAN FIFO Corruption

The beCAN FIFO gets corrupted when a message is received and simultaneously a message is released while FMP = 2. For details and a description of the workaround refer to Section 10.9.7.1 on page 187.

#### 16.2 FLASH/FASTROM DEVICES ONLY

## 16.2.1 LINSCI Wrong Break Duration SCI mode

A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 20 bits instead of 10 bits if M = 0

- 22 bits instead of 11 bits if M = 1

In the same way, as long as the SBK bit is set, break characters are sent to the TDO pin. This may lead to generate one break more than expected.

#### Occurrence

The occurrence of the problem is random and proportional to the baud rate. With a transmit frequency of 19200 baud ( $f_{CPU} = 8 \text{ MHz}$  and

**/**