# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                  |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A7                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 528MHz                                                                  |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                                  |

| RAM Controllers                 | LPDDR2, DDR3, DDR3L                                                     |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | LCD, LVDS                                                               |

| Ethernet                        | 10/100Mbps (2)                                                          |

| SATA                            | -                                                                       |

| USB                             | USB 2.0 + PHY (2)                                                       |

| Voltage - I/O                   | 1.2V, 1.35V, 1.5V, 1.8V, 2.5V, 2.8V, 3.3V                               |

| Operating Temperature           | -40°C ~ 105°C (TJ)                                                      |

| Security Features               | ARM TZ, A-HAB, CAAM, CSU, SJC, SNVS                                     |

| Package / Case                  | 272-LFBGA                                                               |

| Supplier Device Package         | 272-MAPBGA (9x9)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6g2cvk05ab |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### i.MX 6UltraLite introduction

• A-HAB—Advanced High Assurance Boot—HABv4 with the new embedded enhancements: SHA-256, 2048-bit RSA key, version control mechanism, warm boot, CSU, and TZ initialization.

### NOTE

The actual feature set depends on the part numbers as described in Table 1 and Table 2. Functions such as display and camera interfaces, connectivity interfaces, and security features are not offered on all derivatives.

#### Modules list

| Block Mnemonic   | Block Name                                                                          | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC1<br>uSDHC2 | SD/MMC and SDXC<br>Enhanced Multi-Media<br>Card / Secure Digital Host<br>Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6UltraLite specific SoC characteristics:</li> <li>All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are:</li> <li>Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.5/4.2/4.3/4.4/4.41/ including high-capacity (size &gt; 2 GB) cards HC MMC.</li> <li>Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDXC cards up to 2 TB.</li> <li>Fully compliant with SDIO command/response sets and interrupt/read-wait mode as defined in the SDIO Card Specification, Part E1, v3.0</li> <li>Two ports support:</li> <li>1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>4-bit or 8-bit transfer mode specifications for eMMC chips up to 200 MHz in HS200 mode (200 MB/s max)</li> </ul> |

| USB              | Universal Serial Bus 2.0                                                            | Connectivity<br>Peripherals | <ul> <li>USBO2 (USB OTG1 and USB OTG2) contains:</li> <li>Two high-speed OTG 2.0 modules with integrated HS USB PHYs</li> <li>Support eight Transmit (TX) and eight Receive (Rx) endpoints, including endpoint 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| WDOG1<br>WDOG3   | Watch Dog                                                                           | Timer Peripherals           | The Watch Dog Timer supports two comparison points<br>during each counting period. Each of the comparison<br>points is configurable to evoke an interrupt to the ARM<br>core, and a second point evokes an external event on<br>the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WDOG2<br>(TZ)    | Watch Dog (TrustZone)                                                               | Timer Peripherals           | The TrustZone Watchdog (TZ WDOG) timer module<br>protects against TrustZone starvation by providing a<br>method of escaping normal mode and forcing a switch<br>to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such<br>situation is undesirable as it can compromise the<br>system's security. Once the TZ WDOG module is<br>activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer<br>times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode.<br>If it is still not served, the TZ WDOG asserts a security<br>violation signal to the CSU. The TZ WDOG module<br>cannot be programmed or deactivated by a normal<br>mode SW.                                                                                                                                                                                          |

### Table 3. i.MX 6UltraLite Modules List (continued)

**Modules list**

# 3.1 Special signal considerations

Table 4 lists special signal considerations for the i.MX 6UltraLite processors. The signal names are listed in alphabetical order.

The package contact assignments can be found in Section 6, "Package information and contact assignments"." Signal descriptions are provided in the *i.MX 6UltraLite Reference Manual* (IMX6ULRM).

| Signal Name               | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCM_CLK1_P/<br>CCM_CLK1_N | <ul> <li>One general purpose differential high speed clock Input/output is provided.</li> <li>It can be used: <ul> <li>To feed external reference clock to the PLLs and further to the modules inside SoC.</li> <li>To output internal SoC clock to be used outside the SoC as either reference clock or as a functional clock for peripherals.</li> </ul> </li> <li>See the <i>i.MX 6UltraLite Reference Manual</i> (IMX6ULRM) for details on the respective clock trees. Alternatively one may use single ended signal to drive CLK1_P input. In this case corresponding CLK1_N input should be tied to the constant voltage level equal 1/2 of the input signal swing. Termination should be provided in case of high frequency signals. After initialization, the CLK1 input/output can be disabled (if not used). If unused either or both of the CLK1_N/P pairs may remain unconnected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                             |

| RTC_XTALI/RTC_XTALO       | If the user wishes to configure RTC_XTALI and RTC_XTALO as an RTC oscillator, a 32.768 kHz crystal, ( $\leq$ 100 k $\Omega$ ESR, 10 pF load) should be connected between RTC_XTALI and RTC_XTALO. Keep in mind the capacitors implemented on either side of the crystal are about twice the crystal load capacitor. To hit the exact oscillation frequency, the board capacitors need to be reduced to account for board and chip parasitics. The integrated oscillation amplifier is self biasing, but relatively weak. Care must be taken to limit parasitic leakage from RTC_XTALI and RTC_XTALO to either power or ground (>100 M $\Omega$ ). This will debias the amplifier and cause a reduction of startup margin. Typically RTC_XTALI and RTC_XTALO should bias to approximately 0.5 V. If it is desired to feed an external low frequency clock into RTC_XTALI, the RTC_XTALO pin must remain unconnected or driven with a complimentary signal. The logic level of this forcing clock should not exceed VDD_SNVS_CAP level and the frequency should be <100 kHz under typical conditions. In case when high accuracy real time clock are not required system may use internal low frequency ring oscillator. It is recommended to connect RTC_XTALI to GND and keep RTC_XTALO unconnected. |

| XTALI/XTALO               | A 24.0 MHz crystal should be connected between XTALI and XTALO.<br>The crystal must be rated for a maximum drive level of 250 $\mu$ W. An ESR (equivalent series resistance) of typical 80 $\Omega$ is recommended. NXP BSP (board support package) software requires 24 MHz on XTALI/XTALO.<br>The crystal can be eliminated if an external 24 MHz oscillator is available in the system. In this case, XTALO must be directly driven by the external oscillator and XTALI mounted with 18 pF capacitor. Please refer to the EVK board reference design for details. The logic level of this forcing clock cannot exceed NVCC_PLL level.<br>If this clock is used as a reference for USB, then there are strict frequency tolerance and jitter requirements. See OSC24M chapter and relevant interface specifications chapters for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### Table 4. Special Signal Considerations

See the i.MX 6UltraLite Power Consumption Measurement Application Note (AN5170) for more details on typical power consumption under various use case definitions.

| Power Line                     | Conditions                                      | Max Current                          | Unit |

|--------------------------------|-------------------------------------------------|--------------------------------------|------|

| VDD_SOC_IN                     | 528 MHz ARM clock<br>based on Dhrystone<br>test | 500                                  | mA   |

| VDD_HIGH_IN                    | —                                               | 125 <sup>1</sup>                     | mA   |

| VDD_SNVS_IN                    | —                                               | 500 <sup>2</sup>                     | μA   |

| USB_OTG1_VBUS<br>USB_OTG2_VBUS | _                                               | 50 <sup>3</sup>                      | mA   |

| VDDA_ADC_3P3                   | 100 Ohm maximum<br>loading for touch panel      | 35                                   | mA   |

|                                | Primary Interface (IO) Supplies                 |                                      |      |

| NVCC_DRAM                      | _                                               | (See <sup>4</sup> )                  |      |

| NVCC_DRAM_2P5                  | —                                               | 50                                   | mA   |

| NVCC_GPIO                      | N=16                                            | Use maximum IO Equation <sup>5</sup> |      |

| NVCC_UART                      | N=16                                            | Use maximum IO equation <sup>5</sup> |      |

| NVCC_ENET                      | N=16                                            | Use maximum IO equation <sup>5</sup> |      |

| NVCC_LCD                       | N=29                                            | Use maximum IO equation <sup>5</sup> |      |

| NVCC_NAND                      | N=17                                            | Use maximum IO equation <sup>5</sup> |      |

| NVCC_SD1                       | N=6                                             | Use maximum IO equation <sup>5</sup> |      |

| NVCC_CSI                       | N=12                                            | Use maximum IO equation <sup>5</sup> | _    |

|                                | MISC                                            |                                      |      |

| DRAM_VREF                      | —                                               | 1                                    | mA   |

### Table 14. Maximum Supply Currents

<sup>1</sup> The actual maximum current drawn from VDD\_HIGH\_IN will be as shown plus any additional current drawn from the VDD\_HIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_DRAM\_2P5 supplies).

<sup>2</sup> The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA, if available. VDD\_SNVS\_CAP charge time will increase if less than 1 mA is available.

<sup>3</sup> This is the maximum current per active USB physical interface.

<sup>4</sup> The DRAM power consumption is dependent on several factors, such as external signal termination. DRAM power calculators are typically available from the memory vendors. They take in account factors, such as signal termination. See the *i.MX* 6UltraLite Power Consumption Measurement Application Note (AN5170) or examples of DRAM power consumption during specific use case scenarios.

<sup>5</sup> General equation for estimated, maximum power consumption of an IO power supply: Imax = N x C x V x (0.5 x F)

Where:

N—Number of IO pins supplied by the power line

C—Equivalent external capacitive load

V—IO voltage

(0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

### NOTE

The POR\_B input (if used) must be immediately asserted at power-up and remain asserted until after the last power rail reaches its working voltage. In the absence of an external reset feeding the POR\_B input, the internal POR module takes control. See the *i.MX 6UltraLite Reference Manual* (IMX6ULRM) for further details and to ensure that all necessary requirements are being met.

### NOTE

Need to ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).

### NOTE

USB\_OTG1\_VBUS and USB\_OTG2\_VBUS are not part of the power supply sequence and may be powered at any time.

# 4.2.2 Power-Down sequence

The following restrictions must be followed:

- VDD\_SNVS\_IN supply must be turned off after any other power supply or be connected (shorted) with VDD\_HIGH\_IN supply.

- If a coin cell is used to power VDD\_SNVS\_IN, then ensure that it is removed after any other supply is switched off.

# CAUTION

For power sequence control on VDD\_HIGH\_IN and VDD\_SOC\_IN, refer to the ERR010690 (SNVS\_LP Registers Reset Issue).

# 4.2.3 Power supplies usage

All I/O pins should not be externally driven while the I/O power supply for the pin (NVCC\_xxx) is OFF. This can cause internal latch-up and malfunctions due to reverse current flows. For information about I/O power supply of each pin, see "Power Rail" columns in pin list tables of Section 6, "Package information and contact assignments"."

# 4.3 Integrated LDO voltage regulator parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the *i.MX 6UltraLite Reference Manual* (IMX6ULRM) for details on the power tree scheme.

# NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO operation only.

# 4.3.1 Digital regulators (LDO\_ARM, LDO\_SOC)

There are two digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of their input supply ripple rejection and their on-die trimming. This translates into more stable voltage for the on-chip logics.

These regulators have two basic modes:

- Power Gate. The regulation FET is switched fully off limiting the current draw from the supply. The analog part of the regulator is powered down here limiting the power consumption.

- Analog regulation mode. The regulation FET is controlled such that the output voltage of the regulator equals the programmed target voltage. The target voltage is fully programmable in 25 mV steps.

For additional information, see the *i.MX* 6UltraLite Reference Manual (IMX6ULRM).

# 4.3.2 Regulators for analog modules

# 4.3.2.1 LDO\_1P1

The LDO\_1P1 regulator implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 11 for minimum and maximum input requirements). Typical Programming Operating Range is 1.0 V to 1.2 V with the nominal default setting as 1.1 V. The LDO\_1P1 supplies the USB Phy, and PLLs. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for *i.MX 6UltraLite Applications Processors* (IMX6ULHDG).

For additional information, see the *i.MX* 6UltraLite Reference Manual (IMX6ULRM).

# 4.3.2.2 LDO\_2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 11 for minimum and maximum input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. LDO\_2P5 supplies the DDR IOs, USB Phy, E-fuse module, and PLLs. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be enabled for applications needing to keep the output voltage alive during low-power modes where the main regulator driver and its associated global bandgap reference module are disabled. The output of the weak-regulator is not programmable and is a function of the input supply as well as the load current. Typically, with a 3 V input supply the weak-regulator output is 2.525 V and its output impedance is approximately  $40 \,\Omega$

# 4.4.3 Ethernet PLL

| Parameter          | Value                   |

|--------------------|-------------------------|

| Clock output range | 500 MHz                 |

| Reference clock    | 24 MHz                  |

| Lock time          | <11250 reference cycles |

### Table 19. Ethernet PLL's Electrical Parameters

# 4.4.4 480 MHz PLL

#### Table 20. 480 MHz PLL's Electrical Parameters

| Parameter          | Value                 |

|--------------------|-----------------------|

| Clock output range | 480 MHz PLL output    |

| Reference clock    | 24 MHz                |

| Lock time          | <383 reference cycles |

# 4.4.5 ARM PLL

### Table 21. ARM PLL's Electrical Parameters

| Parameter          | Value                  |

|--------------------|------------------------|

| Clock output range | 648 MHz ~ 1296 MHz     |

| Reference clock    | 24 MHz                 |

| Lock time          | <2250 reference cycles |

# 4.5 On-Chip oscillators

# 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implement an oscillator. The oscillator is powered from NVCC\_PLL.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

# 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implement a low power oscillator. It also implements a power mux such that it can be powered from either a ~3 V backup battery (VDD\_SNVS\_IN) or VDD\_HIGH\_IN such as the oscillator consumes

# 4.8 Output buffer impedance parameters

This section defines the I/O impedance parameters of the i.MX 6UltraLite processors for the following I/O types:

- Single Voltage General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2, and DDR3/DDR3L modes

### NOTE

GPIO and DDR I/O output driver impedance is measured with "long" transmission line of impedance Ztl attached to I/O pad and incident wave launched into transmission line. Rpu/Rpd and Ztl form a voltage divider that defines specific voltage of incident wave relative to OVDD. Output driver impedance is calculated from this voltage divider (see Figure 6).

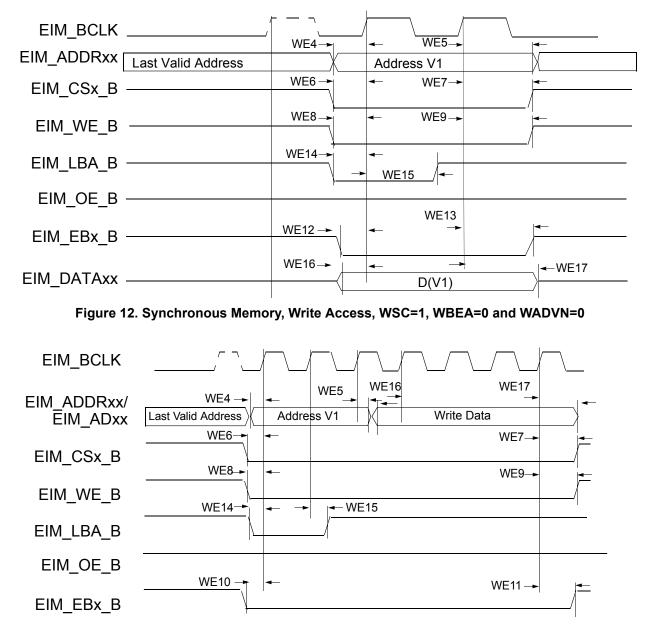

Figure 13. Muxed Address/Data (A/D) Mode, Synchronous Write Access, WSC=6, ADVA=0, ADVN=1, and ADH=1

#### NOTE

In 32-bit muxed address/data (A/D) mode the 16 MSBs are driven on the data bus.

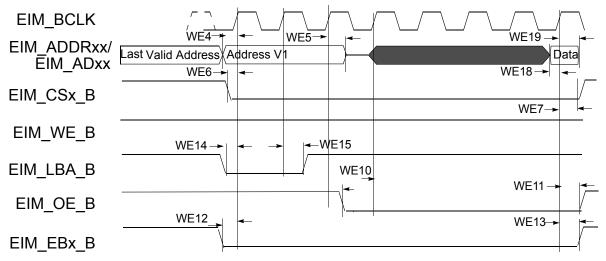

Figure 14. 16-Bit Muxed A/D Mode, Synchronous Read Access, WSC=7, RADVN=1, ADH=1, OEA=0

### 4.9.3.4 General EIM timing-asynchronous mode

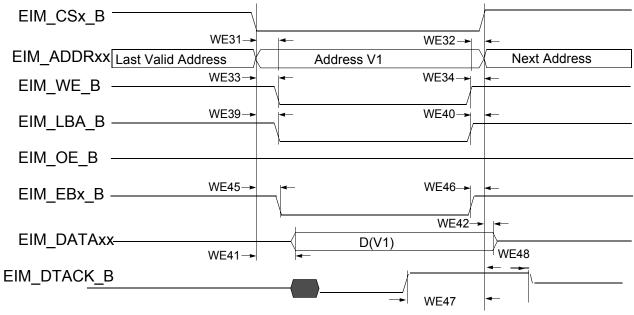

Figure 15 through Figure 19, and Table 40 help to determine timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Asynchronous read & write access length in cycles may vary from what is shown in Figure 15 through Figure 18 as RWSC, OEN and CSN is configured differently. See the *i.MX 6UltraLite Reference Manual (IMX6ULRM)* for the EIM programming model.

Figure 15. Asynchronous Memory Read Access (RWSC = 5)

Figure 20. DTACK Mode Write Access (DAP=0)

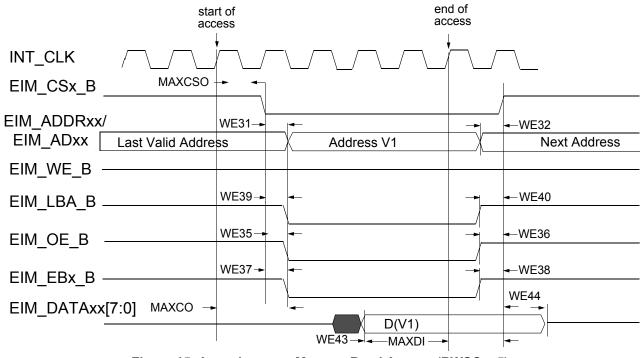

| Ref No.                 | Parameter                                   | Determination by<br>Synchronous measured<br>parameters        | Min                                                     | Max                                                    | Unit |

|-------------------------|---------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|------|

| WE31                    | EIM_CSx_B valid to<br>Address Valid         | WE4 - WE6 - CSA x t                                           | -3.5 - CSA x t                                          | 3.5 - CSA x t                                          | ns   |

| WE32                    | Address Invalid to<br>EIM_CSx_B Invalid     | WE7 - WE5 - CSN x t                                           | -3.5 - CSN x t                                          | 3.5 - CSN x t                                          | ns   |

| WE32A(mu<br>xed A/D     | EIM_CSx_B valid to<br>Address Invalid       | t + WE4 - WE7 + (ADVN +<br>ADVA + 1 - CSA) x t                | t - 3.5 + (ADVN + ADVA<br>+ 1 - CSA) x t                | t + 3.5 + (ADVN +<br>ADVA + 1 - CSA) x t               | ns   |

| WE33                    | EIM_CSx_B Valid to<br>EIM_WE_B Valid        | WE8 - WE6 + (WEA - WCSA) x<br>t                               | -3.5 + (WEA - WCSA) x t                                 | 3.5 + (WEA - WCSA) x t                                 | ns   |

| WE34                    | EIM_WE_B Invalid<br>to EIM_CSx_B<br>Invalid | WE7 - WE9 + (WEN - WCSN) x<br>t                               | -3.5 + (WEN - WCSN) x t                                 | 3.5 + (WEN - WCSN) x t                                 | ns   |

| WE35                    | EIM_CSx_B Valid to<br>EIM_OE_B Valid        | WE10 - WE6 + (OEA - RCSA) x<br>t                              | -3.5 + (OEA - RCSA) x t                                 | 3.5 + (OEA - RCSA) x t                                 | ns   |

| WE35A<br>(muxed<br>A/D) | EIM_CSx_B Valid to<br>EIM_OE_B Valid        | WE10 - WE6 + (OEA + RADVN<br>+ RADVA + ADH + 1 - RCSA) x<br>t | -3.5 + (OEA + RADVN +<br>RADVA + ADH + 1 -<br>RCSA) x t | 3.5 + (OEA + RADVN +<br>RADVA + ADH + 1 -<br>RCSA) x t | ns   |

| WE36                    | EIM_OE_B Invalid<br>to EIM_CSx_B<br>Invalid | WE7 - WE11 + (OEN - RCSN) x<br>t                              | -3.5 + (OEN - RCSN) x t                                 | 3.5 + (OEN - RCSN) x t                                 | ns   |

Table 40. EIM Asynchronous Timing Parameters Table Relative Chip to Select<sup>1,2</sup>

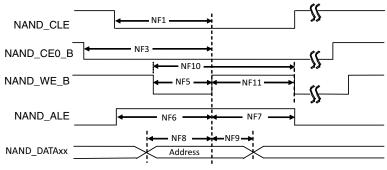

Figure 22. Address Latch Cycle Timing Diagram

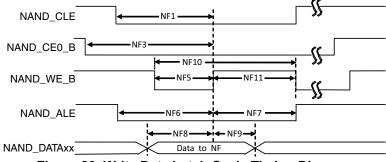

Figure 23. Write Data Latch Cycle Timing Diagram

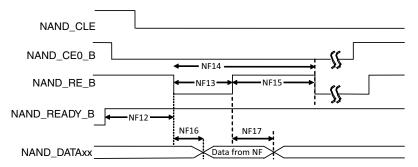

Figure 24. Read Data Latch Cycle Timing Diagram (Non-EDO Mode)

Figure 25. Read Data Latch Cycle Timing Diagram (EDO Mode)

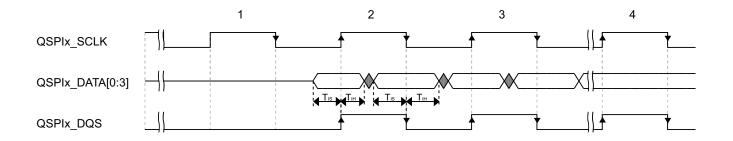

Figure 53. QuadSPI Input/Read Timing (DDR mode with loopback DQS sampling)

| Symbol          | Parameter                               | Value |     | Unit |

|-----------------|-----------------------------------------|-------|-----|------|

|                 | Falameter                               | Min   | Мах | Onit |

| T <sub>IS</sub> | Setup time for incoming data            | 2     | _   | ns   |

| T <sub>IH</sub> | Hold time requirement for incoming data | 1     | _   | ns   |

Table 66. QuadSPI Input/Read Timing (DDR mode with loopback DQS sampling)

### NOTE

- For internal sampling, the timing values assumes using sample point 0, that is QuadSPIx\_SMPR[SDRSMP] = 0.

- For loopback DQS sampling, the data strobe is output to the DQS pad together with the serial clock. The data strobe is looped back from DQS pad and used to sample input data.

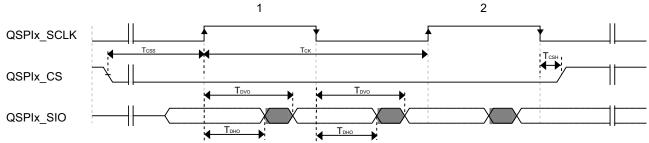

Figure 54. QuadSPI Output/Write Timing (DDR mode)

| Symbol           | Parameter              | Val                      | Unit                            |      |

|------------------|------------------------|--------------------------|---------------------------------|------|

|                  | i arameter             | Min                      | Max                             | Onit |

| T <sub>DVO</sub> | Output data valid time | —                        | 0.25 x T <sub>SCLK</sub> + 2 ns | ns   |

| T <sub>DHO</sub> | Output data hold time  | 0.25 x T <sub>SCLK</sub> | —                               | ns   |

| Т <sub>СК</sub>  | SCK clock period       | 20                       | —                               | ns   |

#### Table 67. QuadSPI Output/Write Timing (DDR mode)

# 4.12.11 SCAN JTAG Controller (SJC) timing parameters

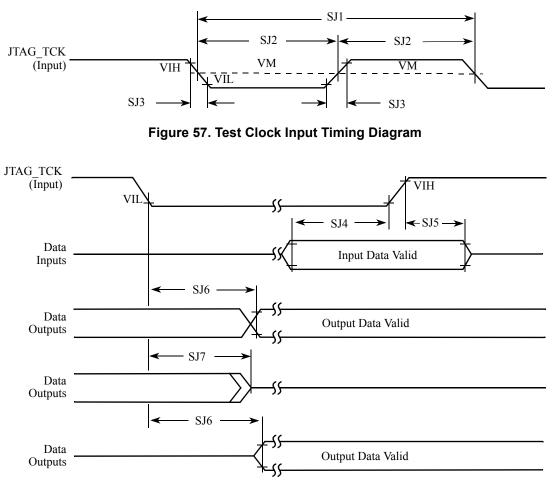

Figure 57 depicts the SJC test clock input timing. Figure 58 depicts the SJC boundary scan timing. Figure 59 depicts the SJC test access port. Signal parameters are listed in Table 70.

Figure 58. Boundary Scan (JTAG) Timing Diagram

| ID Parameter <sup>1,2</sup> | Parameter <sup>1,2</sup>                | All Frequencies |     | Unit |

|-----------------------------|-----------------------------------------|-----------------|-----|------|

|                             | Falameter /                             | Min             | Мах | Unit |

| SJ9                         | JTAG_TMS, JTAG_TDI data hold time       | 25              | _   | ns   |

| SJ10                        | JTAG_TCK low to JTAG_TDO data valid     | —               | 44  | ns   |

| SJ11                        | JTAG_TCK low to JTAG_TDO high impedance | —               | 44  | ns   |

| SJ12                        | JTAG_TRST_B assert time                 | 100             | —   | ns   |

| SJ13                        | JTAG_TRST_B set-up time to JTAG_TCK low | 40              | _   | ns   |

### Table 70. JTAG Timing (continued)

<sup>1</sup>  $T_{DC}$  = target frequency of SJC

<sup>2</sup>  $V_{M}$  = mid-point voltage

# 4.12.12 SPDIF timing parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 71 and Figure 61 and Figure 62 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SPDIF\_SR\_CLK) for SPDIF in Rx mode and the timing of the modulating Tx clock (SPDIF\_ST\_CLK) for SPDIF in Tx mode.

| Characteristics                                                                                                          | Symbol  | Timing Parameter Range                                                                                                                                                                                                                                                                                                                      |      | Unit |

|--------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Gilaracteristics                                                                                                         | Symbol  | Min         Max           -         -         0.7           -         -         1.5           -         -         24.2           -         -         31.3           -         -         1.5           -         -         31.3           -         -         13.6           -         13.6         18.0           kp         40.0         - |      |      |

| SPDIF_IN Skew: asynchronous inputs, no specs apply                                                                       | —       | —                                                                                                                                                                                                                                                                                                                                           | 0.7  | ns   |

| SPDIF_OUT output (Load = 50pf) <ul> <li>Skew</li> <li>Transition rising</li> <li>Transition falling</li> </ul>           |         | _<br>_<br>_                                                                                                                                                                                                                                                                                                                                 | 24.2 | ns   |

| <ul> <li>SPDIF_OUT1 output (Load = 30pf)</li> <li>Skew</li> <li>Transition rising</li> <li>Transition falling</li> </ul> |         | <br><br>_                                                                                                                                                                                                                                                                                                                                   | 13.6 | ns   |

| Modulating Rx clock (SPDIF_SR_CLK) period                                                                                | srckp   | 40.0                                                                                                                                                                                                                                                                                                                                        | —    | ns   |

| SPDIF_SR_CLK high period                                                                                                 | srckph  | 16.0                                                                                                                                                                                                                                                                                                                                        | _    | ns   |

| SPDIF_SR_CLK low period                                                                                                  | srckpl  | 16.0                                                                                                                                                                                                                                                                                                                                        | _    | ns   |

| Modulating Tx clock (SPDIF_ST_CLK) period                                                                                | stclkp  | 40.0                                                                                                                                                                                                                                                                                                                                        | _    | ns   |

| SPDIF_ST_CLK high period                                                                                                 | stclkph | 16.0                                                                                                                                                                                                                                                                                                                                        | —    | ns   |

| SPDIF_ST_CLK low period                                                                                                  | stclkpl | 16.0                                                                                                                                                                                                                                                                                                                                        | —    | ns   |

Table 71. SPDIF Timing Parameters

# 4.12.13.1.2 UART receiver

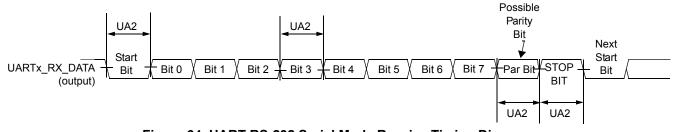

Figure 64 depicts the RS-232 serial mode receives timing with 8 data bit/1 stop bit format. Table 73 lists serial mode receive timing characteristics.

Figure 64. UART RS-232 Serial Mode Receive Timing Diagram

| ID  | Parameter                     | Symbol            | Min                                                                         | Мах                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> - 1/(16<br>x F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 x F <sub>baud_rate</sub> ) | _    |

Table 73. RS-232 Serial Mode Receive Timing Parameters

<sup>1</sup> The UART receiver can tolerate 1/(16 x F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16 x F<sub>baud\_rate</sub>).

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

### 4.12.13.1.3 UART IrDA mode timing

The following subsections give the UART transmit and receive timings in IrDA mode.

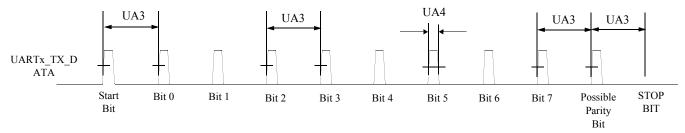

### **UART IrDA mode transmitter**

Figure 65 depicts the UART IrDA mode transmit timing, with 8 data bit/1 stop bit format. Table 74 lists the transmit timing characteristics.

Figure 65. UART IrDA Mode Transmit Timing Diagram

| ID  | Parameter                      | Symbol                | Min                                                            | Мах                                                            | Unit |

|-----|--------------------------------|-----------------------|----------------------------------------------------------------|----------------------------------------------------------------|------|

| UA3 | Transmit Bit Time in IrDA mode | t <sub>TIRbit</sub>   | 1/F <sub>baud_rate</sub> 1 -<br>T <sub>ref_clk</sub> 2         | 1/F <sub>baud_rate</sub> + T <sub>ref_clk</sub>                | _    |

| UA4 | Transmit IR Pulse Duration     | t <sub>TIRpulse</sub> | (3/16) x (1/F <sub>baud_rate</sub> )<br>- T <sub>ref_clk</sub> | (3/16) x (1/F <sub>baud_rate</sub> )<br>+ T <sub>ref_clk</sub> |      |

Table 74. IrDA Mode Transmit Timing Parameters

<sup>1</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

Boot mode configuration

| Ball Name   | Signal Name    | Mux Mode | Commo<br>n | 4-bit | 8-bit | BOOT_CFG1[1]=1<br>(SD Power Cycle) |

|-------------|----------------|----------|------------|-------|-------|------------------------------------|

| NAND_RE_B   | usdhc2.CLK     | Alt 1    | Yes        |       |       |                                    |

| NAND_WE_B   | usdhc2.CMD     | Alt 1    | Yes        |       |       |                                    |

| NAND_DATA00 | usdhc2.DATA0   | Alt 1    | Yes        |       |       |                                    |

| NAND_DATA01 | usdhc2.DATA1   | Alt 1    |            | Yes   | Yes   |                                    |

| NAND_DATA02 | usdhc2.DATA2   | Alt 1    |            | Yes   | Yes   |                                    |

| NAND_DATA03 | usdhc2.DATA3   | Alt 1    | Yes        |       |       |                                    |

| NAND_DATA04 | usdhc2.DATA4   | Alt 1    |            |       | Yes   |                                    |

| NAND_DATA05 | usdhc2.DATA5   | Alt 1    |            |       | Yes   |                                    |

| NAND_DATA06 | usdhc2.DATA6   | Alt 1    |            |       | Yes   |                                    |

| NAND_DATA07 | usdhc2.DATA7   | Alt 1    |            |       | Yes   |                                    |

| NAND_ALE    | usdhc2.RESET_B | Alt 5    |            |       |       | Yes                                |

| GPIO1_IO08  | usdhc2.VSELECT | Alt 4    |            |       |       | Yes                                |

### Table 86. SD/MMC Boot through USDHC2

### Table 87. NOR/OneNAND Boot through EIM

| Ball Name   | Signal Name   | Mux Mode | Common | ADL16<br>Non-Mux | AD16 Mux |

|-------------|---------------|----------|--------|------------------|----------|

| CSI_DATA00  | weim.AD[0]    | Alt 4    | Yes    |                  |          |

| CSI_DATA01  | weim.AD[1]    | Alt 4    | Yes    |                  |          |

| CSI_DATA02  | weim.AD[2]    | Alt 4    | Yes    |                  |          |

| CSI_DATA03  | weim.AD[3]    | Alt 4    | Yes    |                  |          |

| CSI_DATA04  | weim.AD[4]    | Alt 4    | Yes    |                  |          |

| CSI_DATA05  | weim.AD[5]    | Alt 4    | Yes    |                  |          |

| CSI_DATA06  | weim.AD[6]    | Alt 4    | Yes    |                  |          |

| CSI_DATA07  | weim.AD[7]    | Alt 4    | Yes    |                  |          |

| NAND_DATA00 | weim.AD[8]    | Alt 4    | Yes    |                  |          |

| NAND_DATA01 | weim.AD[9]    | Alt 4    | Yes    |                  |          |

| NAND_DATA02 | weim.AD[10]   | Alt 4    | Yes    |                  |          |

| NAND_DATA03 | weim.AD[11]   | Alt 4    | Yes    |                  |          |

| NAND_DATA04 | weim.AD[12]   | Alt 4    | Yes    |                  |          |

| NAND_DATA05 | weim.AD[13]   | Alt 4    | Yes    |                  |          |

| NAND_DATA06 | weim.AD[14]   | Alt 4    | Yes    |                  |          |

| NAND_DATA07 | weim.AD[15]   | Alt 4    | Yes    |                  |          |

| NAND_CLE    | weim.ADDR[16] | Alt 4    |        | Yes              | Yes      |

#### Boot mode configuration

### Table 88. Serial Download through UART1

| Ball Name     | Signal Name   | Mux Mode | Common |

|---------------|---------------|----------|--------|

| UART1_TX_DATA | uart1.TX_DATA | Alt 0    | Yes    |

| UART1_RX_DATA | uart1.RX_DATA | Alt 0    | Yes    |

### Table 89. Serial Download through UART2

| Ball Name     | Signal Name   | Mux Mode | Common |

|---------------|---------------|----------|--------|

| UART2_TX_DATA | uart2.TX_DATA | Alt 0    | Yes    |

| UART2_RX_DATA | uart2.RX_DATA | Alt 0    | Yes    |

### Table 95. 9x9 mm, 0.5 mm Pitch, Ball Map (continued)

|    | Þ                 | F                | ĸ            |

|----|-------------------|------------------|--------------|

| ٢  | VSS               | DRAM_VREF        | DRAM_DM1     |

| 2  | DRAM_DATA09       | DRAM_ZQPAD       | DRAM_DATA11  |

| 3  | DRAM_DATA07       | DRAM_DATA00      | VSS          |

| 4  | DRAM_DQM0         | DRAM_DATA02      | DRAM_DATA06  |

| 5  | DRAM_DATA04       | DRAM_DATA03      | DRAM_SDQS0_N |

| 9  | NSS               | DRAM_DATA05      | ONOFF        |

| 7  | CCM_PMIC_STBY_REQ | SNVS_PMIC_ON_REQ | SNVS_TAMPER6 |

| 8  | BOOT_MODE1        | BOOT_MODE0       | SNVS_TAMPER0 |

| 6  | USB_OTG2_VBUS     | USB_OTG1_VBUS    | VSS          |

| 10 | USB_OTG2_DP       | USB_OTG2_DN      | POR_B        |

| 11 | VDD_HIGH_CAP      | GPANAIO          | USB_OTG1_DN  |

| 12 | RTC_XTALO         | RTC_XTALI        | VSS          |

| 13 | VSS               | NVCC_PLL         | JTAG_MOD     |

| 14 | XTALO             | XTALI            | JTAG_TMS     |

| 15 | VDD_HIGH_IN       | USB_OTG1_CHD_B   | VSS          |

| 16 | CCM_CLK1_N        | CCM_CLK1_P       | JTAG_TDO     |

| 17 | VSS               | VDDA_ADC_3P3     | JTAG_TCK     |

|    | n                 | Т                | R            |

# 6.3 GPIO reset behaviors during reset

Table 96 shows the GPIO behaviors during reset.

### Table 96. GPIO Behaviors during Reset <sup>1</sup>

| Ball Name     | Mux Mode | Function      | Input/Output | Value            |

|---------------|----------|---------------|--------------|------------------|

| GPIO01_IO03   | ALT7     | Reserved      | Input        | 100 kΩ pull-down |

| UART3_TX_DATA | ALT7     | SJC_JTAG_ACT  | Output       | 0                |

| LCD_DATA00    | ALT6     | SRC_BT_CFG[0] | Input        | 100 kΩ pull-down |

| LCD_DATA01    | ALT6     | SRC_BT_CFG[1] | Input        | 100 kΩ pull-down |

| LCD_DATA02    | ALT6     | SRC_BT_CFG[2] | Input        | 100 kΩ pull-down |

| LCD_DATA03    | ALT6     | SRC_BT_CFG[3] | Input        | 100 kΩ pull-down |

| LCD_DATA04    | ALT6     | SRC_BT_CFG[4] | Input        | 100 kΩ pull-down |

| LCD_DATA05    | ALT6     | SRC_BT_CFG[5] | Input        | 100 kΩ pull-down |

| LCD_DATA06    | ALT6     | SRC_BT_CFG[6] | Input        | 100 kΩ pull-down |

| LCD_DATA07    | ALT6     | SRC_BT_CFG[7] | Input        | 100 kΩ pull-down |

| LCD_DATA08    | ALT6     | SRC_BT_CFG[8] | Input        | 100 kΩ pull-down |

| LCD_DATA09    | ALT6     | SRC_BT_CFG[9] | Input        | 100 kΩ pull-down |

#### Package information and contact assignments

| Ball Name  | Mux Mode | Function       | Input/Output | Value                    |

|------------|----------|----------------|--------------|--------------------------|

| LCD_DATA10 | ALT6     | SRC_BT_CFG[10] | Input        | 100 kΩ pull-down         |

| LCD_DATA11 | ALT6     | SRC_BT_CFG[11] | Input        | 100 kΩ pull-down         |

| LCD_DATA12 | ALT6     | SRC_BT_CFG[12] | Input        | 100 kΩ pull-down         |

| LCD_DATA13 | ALT6     | SRC_BT_CFG[13] | Input        | 100 kΩ pull-down         |

| LCD_DATA14 | ALT6     | SRC_BT_CFG[14] | Input        | 100 k $\Omega$ pull-down |

| LCD_DATA15 | ALT6     | SRC_BT_CFG[15] | Input        | 100 k $\Omega$ pull-down |

| LCD_DATA16 | ALT6     | SRC_BT_CFG[16] | Input        | 100 kΩ pull-down         |

| LCD_DATA17 | ALT6     | SRC_BT_CFG[17] | Input        | 100 kΩ pull-down         |

| LCD_DATA18 | ALT6     | SRC_BT_CFG[18] | Input        | 100 kΩ pull-down         |

| LCD_DATA19 | ALT6     | SRC_BT_CFG[19] | Input        | 100 kΩ pull-down         |

| LCD_DATA20 | ALT6     | SRC_BT_CFG[20] | Input        | 100 kΩ pull-down         |

| LCD_DATA21 | ALT6     | SRC_BT_CFG[21] | Input        | 100 kΩ pull-down         |

| LCD_DATA22 | ALT6     | SRC_BT_CFG[22] | Input        | 100 kΩ pull-down         |

| LCD_DATA23 | ALT6     | SRC_BT_CFG[23] | Input        | 100 kΩ pull-down         |

# Table 96. GPIO Behaviors during Reset (continued)<sup>1</sup>

<sup>1</sup> Others are same as value in the column "Out of Reset Condition" of Table 91 and Table 94.