#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                           |

|---------------------------------|------------------------------------------------------------------------------------|

| Core Processor                  | MIPS-I                                                                             |

| Number of Cores/Bus Width       | 1 Core, 64-Bit                                                                     |

| Speed                           | 267MHz                                                                             |

| Co-Processors/DSP               | System Control; CP0                                                                |

| RAM Controllers                 | DRAM                                                                               |

| Graphics Acceleration           | No                                                                                 |

| Display & Interface Controllers | -                                                                                  |

| Ethernet                        | -                                                                                  |

| SATA                            | -                                                                                  |

| USB                             | -                                                                                  |

| Voltage - I/O                   | 3.3V                                                                               |

| Operating Temperature           | 0°C ~ 85°C (TC)                                                                    |

| Security Features               | -                                                                                  |

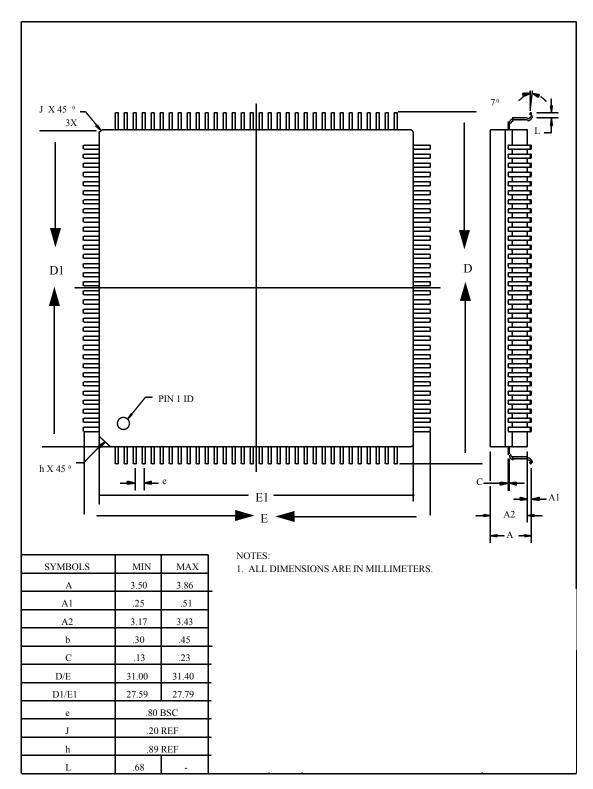

| Package / Case                  | 128-BQFP                                                                           |

| Supplier Device Package         | 128-PQFP (28x28)                                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/renesas-electronics-america/idt79rv4640-267du |

|                                 |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Description

The IDT79RC4640 is a low-cost member of the Integrated Device Technology, Inc. RC4000 family, targeted to a variety of performancehungry embedded applications. The RC4640 continues the RC4000 tradition of high-performance through high-speed pipelines, high-bandwidth caches and bus interface, 64-bit architecture, and careful attention to efficient control. The cost of this performance is reduced by removing functional units frequently not required for many embedded applications.

The RC4640 supports a wide variety of embedded processor-based applications, such as internetworking equipment (routers, switches), office automation equipment (printers, scanners), and consumer multimedia game systems. Also, being upwardly software-compatible with the RC32300 family as well as bus- and upwardly software-compatible with the IDT RC4000 family, the RC4640 will serve in many of the same applications. And, the RC4640 supports applications that require integer digital signal processing (DSP) functions.

The RC64475 and RC64575 processors offer a direct migration path for designs based on IDT's RC4650 processors, through full pin and socket compatibility.

The RC4640 brings 64-bit performance levels to lower cost systems. High performance is preserved by retaining large on-chip two-way setassociative caches, a streamlined high-speed pipeline, high bandwidth, 64-bit execution, and facilities such as early restart for data cache misses.

These techniques allow the system designer over 3.2 GB/sec aggregate internal bandwidth, 500 MB/sec bus bandwidth, almost 352 Dhrystone MIPS, 89MFlops, and 133.5 M Mul-Add/sec. An array of tools facilitates rapid development of RC4640-based systems, allowing a wide variety of customers access to the processor's high-performance capabilities while maintaining short time-to-market goals.

# **Hardware Overview**

Some key elements of the RC4640 are briefly described below. More detailed information is available in the *IDT79RC4640/IDT79RC4650 RISC Processor Hardware User's Manual.*

### **Pipeline**

The RC4640 uses a 5-stage pipeline that is similar to the IDT79RC3000 and the IDT79RC4700 processors. The simplicity of this pipeline allows the RC4640 to cost less than super-scalar processors and require less power than super-pipelined processors. So, unlike superscalar processors, applications that have large data dependencies, or require frequent load/stores, can still achieve peak performance.

### **Integer Execution Engine**

The RC4640 implements the MIPS-III Instruction Set Architecture and is fully upward compatible with applications that run on earlier generation parts. The RC4640 is software-compatible with the RC4650, and includes the instruction set found in the RC4700 microprocessor, targeted at higher performance while maintaining binary compatibility with RC32300 processors. The extensions result in better code density, greater multiprocessing support, improved performance for commonly used code sequences in operating system kernels, and faster execution of floatingpoint intensive applications. All resource dependencies are made transparent to the programmer, insuring transportability among implementations of the MIPS instruction set architecture. In addition, MIPS-III specifies new instructions defined to take advantage of the 64-bit architecture of the processor.

Finally, the RC4640 also implements additional instructions, which are considered extensions to the MIPS-III architecture. These instructions improve the multiply and multiply-add throughput of the CPU, making it well suited to a wide variety of imaging and DSP applications. These extensions, which use opcodes allocated by MIPS Technologies for this purpose, are supported by a wide variety of development tools.

The MIPS integer unit implements a load/store architecture with single cycle ALU operations (logical, shift, add, sub) and autonomous multiply/divide unit. The 64-bit register resources include: 32 general-purpose orthogonal integer registers, the HI/LO result registers for the integer multiply/divide unit, and the program counter. In addition, the on-chip floating-point co-processor adds 32 floating-point registers, and a floating-point control/status register.

# **Register File**

The RC4640 has 32 general-purpose 64-bit registers. These registers are used for scalar integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

# **Arithmetic Logic Unit**

The RC4640 ALU consists of the integer adder and logic unit. The adder performs address calculations in addition to arithmetic operations; the logic unit performs all of the logic and shift operations. Each unit is highly optimized and can perform an operation in a single pipeline cycle.

### **Integer Multiply/Divide**

The RC4640 uses a dedicated integer multiply/divide unit, optimized for high-speed multiply and multiply-accumulate operation. Table 1 shows the performance, expressed in terms of pipeline clocks, achieved by the RC4640 integer multiply unit.

| Opcode        | Operand<br>Size | Latency | Repeat | Stall |

|---------------|-----------------|---------|--------|-------|

| MULT/U, MAD/U | 16 bit          | 3       | 2      | 0     |

|               | 32 bit          | 4       | 3      | 0     |

| MUL           | 16 bit          | 3       | 2      | 1     |

|               | 32 bit          | 4       | 3      | 2     |

| DMULT, DMULTU | any             | 6       | 5      | 0     |

| DIV, DIVU     | any             | 36      | 36     | 0     |

| DDIV, DDIVU   | any             | 68      | 68     | 0     |

Table 1 RC4640 Integer Multiply Operation

#### IDT79RC4640™

The MIPS-III architecture defines that the results of a multiply or divide operation are placed in the HI and LO registers. The values can then be transferred to the general purpose register file using the MFHI/ MFLO instructions.

The RC4640 adds a new multiply instruction, "MUL", which can specify that the multiply results bypass the "Lo" register and are placed immediately in the primary register file. By avoiding the explicit "Move-from-Lo" instruction required when using "Lo", throughput of multiply-intensive operations is increased.

An additional enhancement offered by the RC4640 is an atomic "multiply-add" operation, MAD, used to perform multiply-accumulate operations. This instruction multiplies two numbers and adds the product to the current contents of the HI and LO registers. This operation is used in numerous DSP algorithms, and allows the RC4640 to cost reduce systems requiring a mix of DSP and control functions.

Finally, aggressive implementation techniques feature low latency for these operations along with pipelining to allow new operations to be issued before a previous one has fully completed. Table 1 also shows the repeat rate (peak issue rate), latency, and number of processor stalls required for the various operations. The RC4640 performs automatic operand size detection to determine the size of the operand, and implements hardware interlocks to prevent overrun, allowing this high-performance to be achieved with simple programming.

# **Floating-Point Coprocessor**

The RC4640 incorporates an entire single-precision floating-point coprocessor on chip, including a floating-point register file and execution units. The floating-point coprocessor forms a "seamless" interface with the integer unit, decoding and executing instructions in parallel with the integer unit.

The floating-point unit of the RC4640 directly implements singleprecision floating-point operations, which enables the RC4640 to perform functions such as graphics rendering without requiring extensive die area or power consumption. The single-precision unit of the RC4640 is directly compatible with the single-precision operation of the RC4700, and features the same latencies and repeat rates.

The RC4640 does not directly implement the double-precision operations found in the RC4700. However, to maintain software compatibility, the RC4640 will signal a trap when a double-precision operation is initiated, allowing the requested function to be emulated in software. Alternatively, the system architect could use a software library emulation of double-precision functions, selected at compile time, to eliminate the overhead associated with trap and emulation.

### **Floating-Point Units**

The RC4640's floating-point execution units perform single precision arithmetic, as specified in IEEE Standard 754. The execution unit is broken into a separate multiply unit and a combined add/convert/divide/ square root unit. Overlap of multiply and add/subtract is supported. The multiplier is partially pipelined, allowing a new multiplication instruction to begin every 6 cycles. As in the IDT79RC4700, the RC4640 maintains fully precise floatingpoint exceptions while allowing both overlapped and pipelined operations. Precise exceptions are extremely important in mission-critical environments, such as ADA, and highly desirable for debugging in any environment.

The floating-point unit's operation set includes floating-point add, subtract, multiply, divide, square root, conversion between fixed-point and floating-point format, conversion among floating-point formats, and floating-point compare. These operations comply with IEEE Standard 754. Double precision operations are not directly supported; attempts to execute double-precision floating point operations, or refer directly to double-precision registers, result in the RC4640 signalling a "trap" to the CPU, enabling emulation of the requested function. Table 2 gives the latencies of some of the floating-point instructions in internal processor cycles.

| Operation | Instruction<br>Latency |

|-----------|------------------------|

| ADD       | 4                      |

| SUB       | 4                      |

| MUL       | 8                      |

| DIV       | 32                     |

| SQRT      | 31                     |

| CMP       | 3                      |

| FIX       | 4                      |

| FLOAT     | 6                      |

| ABS       | 1                      |

| MOV       | 1                      |

| NEG       | 1                      |

| LWC1      | 2                      |

| SWC1      | 1                      |

Table 2 Floating-Point Operation

### **Floating-Point General Register File**

The floating-point register file is made up of thirty-two 32-bit registers. These registers are used as source or target registers for the single-precision operations.

References to these registers as 64-bit registers (as supported in the RC4700) will cause a trap to be signalled to the integer unit.

The floating-point control register space contains two registers; one for determining configuration and revision information for the coprocessor and one for control and status information. These are primarily involved with diagnostic software, exception handling, state saving and restoring, and control of rounding modes.

#### IDT79RC4640™

#### System Control Coprocessor (CP0)

The system control coprocessor in the MIPS architecture is responsible for the virtual to physical address translation and cache protocols, the exception control system, and the diagnostics capability of the processor. In the MIPS architecture, the system control coprocessor (and thus the kernel software) is implementation dependent.

In the RC4640, significant changes in CP0 relative to the RC4600 have been implemented. These changes are designed to simplify memory management, facilitate debug, and speed real-time processing.

#### **System Control Coprocessor Registers**

The RC4640 incorporates all system control co-processor (CP0) registers on-chip. These registers provide the path through which the virtual memory system's address translation is controlled, exceptions are handled, and operating modes are controlled (kernel vs. user mode, interrupts enabled or disabled, cache features). In addition, the RC4640 includes registers to implement a real-time cycle counting facility, which aids in cache diagnostic testing, assists in data error detection, and facilitates software debug. Alternatively, this timer can be used as the operating system reference timer, and can signal a periodic interrupt.

Table 3 shows the CP0 registers of the RC4640.

| Number                    | Name     | Function                                                              |

|---------------------------|----------|-----------------------------------------------------------------------|

| 0                         | lBase    | Instruction address space base                                        |

| 1                         | IBound   | Instruction address space bound                                       |

| 2                         | DBase    | Data address space base                                               |

| 3                         | DBound   | Data address space bound                                              |

| 4-7, 10, 20-25,<br>29, 31 | -        | Not used                                                              |

| 8                         | BadVAddr | Virtual address on address exceptions                                 |

| 9                         | Count    | Counts every other cycle                                              |

| 11                        | Compare  | Generate interrupt when Count = Compare                               |

| 12                        | Status   | Miscellaneous control/status                                          |

| 13                        | Cause    | Exception/Interrupt information                                       |

| 14                        | EPC      | Exception PC                                                          |

| 15                        | PRId     | Processor ID                                                          |

| 16                        | Config   | Cache and system attributes                                           |

| 17                        | CAlg     | Cache attributes for the 8 512MB regions of the virtual address space |

| 18                        | IWatch   | Instruction breakpoint virtual address                                |

| 19                        | DWatch   | Data breakpoint virtual address                                       |

| 26                        | ECC      | Used in cache diagnostics                                             |

| 27                        | CacheErr | Cache diagnostic information                                          |

| 28                        | TagLo    | Cache index information                                               |

| 30                        | ErrorEPC | CacheError exception PC                                               |

Table 3 RC4640 CPO Registers

### **Operation Modes**

The RC4640 supports two modes of operation: user mode and kernel mode. Kernel mode operation is typically used for exception handling and operating system kernel functions, including CP0 management and access to IO devices. In kernel mode, software has access to the entire address space and all of the co-processor 0 registers, and can select whether to enable co-processor 1 accesses. The processor enters kernel mode at reset, and whenever an exception is recognized.

User mode is typically used for applications programs. User mode accesses are limited to a subset of the virtual address space, and can be inhibited from accessing CP0 functions.

| 0xFFFFFFF  |                                                             |

|------------|-------------------------------------------------------------|

|            | Kernel virtual address space<br>(kseg2)<br>Unmapped, 1.0 GB |

| 0xC0000000 |                                                             |

| 0xBFFFFFF  |                                                             |

|            | Uncached kernel physical address space (kseg1)              |

| 0xA0000000 | Unmapped, 0.5GB                                             |

| 0x9FFFFFFF |                                                             |

| 0,3111111  | Cached kernel physical address space (kseg0)                |

| 00000000   | Unmapped, 0.5GB                                             |

| 0x80000000 |                                                             |

| 0x7FFFFFF  |                                                             |

|            |                                                             |

|            | User virtual address space<br>(useg)                        |

|            | Mapped, 2.0GB                                               |

|            |                                                             |

| 0x00000000 |                                                             |

Figure 1 Mode Virtual Addressing (32-bit mode)

### Virtual-to-Physical Address Mapping

The 4GB virtual address space of the RC4640 is shown in Figure 1. The 4 GB address space is divided into addresses accessible in either kernel or user mode (kuseg), and addresses only accessible in kernel mode (kseg2:0).

The RC4640 supports the use of multiple user tasks sharing common virtual addresses, but mapped to separate physical addresses. This facility is implemented via the "base-bounds" registers contained in CP0.

When a user virtual address is asserted (load, store, or instruction fetch), the RC4640 compares the virtual address with the contents of the appropriate "bounds" register (instruction or data). If the virtual

address is "in bounds", the value of the corresponding "base" register is added to the virtual address to form the physical address for that reference. If the address is not within bounds, an exception is signalled.

This facility enables multiple user processes in a single physical memory without the use of a TLB. This type of operation is further supported by a number of development tools for the RC4640, including real-time operating systems and "position independent code".

Kernel mode addresses do not use the base-bounds registers, but rather undergo a fixed virtual-to-physical address translation.

## **Debug Support**

To facilitate software debug, the RC4640 adds a pair of "watch" registers to CP0. When enabled, these registers will cause the CPU to take an exception when a "watched" address is appropriately accessed.

## **Interrupt Vector**

The RC4640 also adds the capability to speed interrupt exception decoding. Unlike the RC4700, which utilizes a single common exception vector for all exception types (including interrupts), the RC4640 allows kernel software to enable a separate interrupt exception vector. When enabled, this vector location speeds interrupt processing by allowing software to avoid decoding interrupts from general purpose exceptions.

## **Cache Memory**

To keep the RC4640's high-performance pipeline full and operating efficiently, the RC4640 incorporates on-chip instruction and data caches that can each be accessed in a single processor cycle. Each cache has its own 64-bit data path and can be accessed in parallel. The cache subsystem provides the integer and floating-point units with an aggregate bandwidth of over 3200 MB per second at a pipeline clock frequency of 267MHz. The cache subsystem is similar in construction to that found in the RC4700, although some changes have been implemented. Table 4 is an overview of the caches found on the RC4640.

## **Instruction Cache**

The RC4640 incorporates a two-way set associative on-chip instruction cache. This virtually indexed, physically tagged cache is 8KB in size and is parity protected.

Because the cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access, thus further increasing performance by allowing these two operations to occur simultaneously. The tag holds a 20-bit physical address and valid bit, and is parity protected.

The instruction cache is 64-bits wide, and can be refilled or accessed in a single processor cycle. Instruction fetches require only 32 bits per cycle, for a peak instruction bandwidth of 1068MB/sec at 267MHz. Sequential accesses take advantage of the 64-bit fetch to reduce power dissipation, and cache miss refill, can write 64 bits-per-cycle to minimize the cache miss penalty. The line size is eight instructions (32 bytes) to maximize performance. In addition, the contents of one set of the instruction cache (set "A") can be "locked" by setting a bit in a CP0 register. Locking the set prevents its contents from being overwritten by a subsequent cache miss; refill occurs then only into "set B".

This operation effectively "locks" time critical code into one 4kB set, while allowing the other set to service other instruction streams in a normal fashion. Thus, the benefits of cached performance are achieved, while deterministic real-time response is preserved.

### **Data Cache**

For fast, single cycle data access, the RC4640 includes an 8KB onchip data cache that is two-way set associative with a fixed 32-byte (eight words) line size. Table 4 lists the RC4640 cache attributes.

| Characteristics                | Instruction           | Data                  |

|--------------------------------|-----------------------|-----------------------|

| Size                           | 8KB                   | 8KB                   |

| Organization                   | 2-way set associative | 2-way set associative |

| Line size                      | 32B                   | 32B                   |

| Index                          | vAddr <sub>110</sub>  | vAddr <sub>110</sub>  |

| Тад                            | pAddr <sub>3112</sub> | pAddr <sub>3112</sub> |

| Write policy                   | n.a.                  | writeback /writethru  |

| Line transfer order            | read sub-block order  | read sub-block order  |

|                                | write sequential      | write sequential      |

| Miss restart after transfer of | entire line           | first word            |

| Parity                         | per-word              | per-byte              |

| Cache locking                  | set A                 | set A                 |

#### Table 4 RC4640 Cache Attributes

The data cache is protected with byte parity and its tag is protected with a single parity bit. It is virtually indexed and physically tagged to allow simultaneous address translation and data cache access

The normal write policy is writeback, which means that a store to a cache line does not immediately cause memory to be updated. This increases system performance by reducing bus traffic and eliminating the bottleneck of waiting for each store operation to finish before issuing a subsequent memory operation. Software can however select write-through for certain address ranges, using the CAlg register in CP0. Cache protocols supported for the data cache are:

## • Uncached.

Addresses in a memory area indicated as uncached will not be read from the cache. Stores to such addresses will be written directly to main memory, without changing cache contents.

### Writeback.

Loads and instruction fetches will first search the cache, reading main memory only if the desired data is not cache resident. On data store operations, the cache is first searched to see if the target address is cache resident. If it is resident, the cache con-

#### IDT79RC4640™

tents will be updated, and the cache line marked for later writeback. If the cache lookup misses, the target line is first brought into the cache before the cache is updated.

## • Write-through with write allocate.

Loads and instruction fetches will first search the cache, reading main memory only if the desired data is not cache resident. On data store operations, the cache is first searched to see if the target address is cache resident. If it is resident, the cache contents will be updated and main memory will also be written; the state of the "writeback" bit of the cache line will be unchanged. If the cache lookup misses, the target line is first brought into the cache before the cache is updated.

• Write-through without write-allocate.

Loads and instruction fetches will first search the cache, reading main memory only if the desired data is not cache resident. On data store operations, the cache is first searched to see if the target address is cache resident. If it is resident, the cache contents will be updated, and the cache line marked for later writeback. If the cache lookup misses, then only main memory is written.

Associated with the Data Cache is the store buffer. When the RC4640 executes a Store instruction, this single-entry buffer gets written with the store data while the tag comparison is performed. If the tag matches, then the data is written into the Data Cache in the next cycle that the Data Cache is not accessed (the next non-load cycle). The store buffer allows the RC4640 to execute a store every processor cycle and to perform back-to-back stores without penalty.

### **Write Buffer**

Writes to external memory, whether cache miss writebacks or stores to uncached or write-through addresses, use the on-chip write buffer. The write buffer holds up to four address and data pairs. The entire buffer is used for a data cache writeback and allows the processor to proceed in parallel with memory update.

### **System Interface**

The RC4640 supports a 32-bit system interface that is syntactically compatible with the RC4700 system interface.

The interface consists of a 32-bit Address/Data bus with eight check bits and a 9-bit command bus protected with parity. In addition, there are eight handshake signals and six interrupt inputs. The interface has a simple timing specification and is capable of transferring data between the processor and memory at a peak rate of 500MB/sec at 125MHz on the bus.

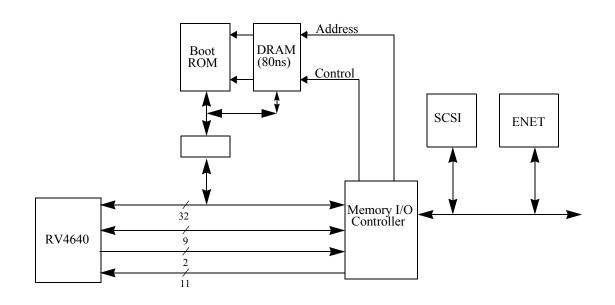

Figure 2 on page 7 shows a typical system using the RC4640. In this example two banks of DRAMs are used to supply and accept data with a **DDxxDD** data pattern.

The RC4640 clocking interface allows the CPU to be easily mated with external reference clocks. The CPU input clock is the bus reference clock, and can be between 50 and 125MHz (somewhat dependent on maximum pipeline speed for the CPU).

An on-chip phase-locked-loop generates the pipeline clock from the system interface clock by multiplying it up an amount selected at system reset. Supported multipliers are values 2 through 8 inclusive, allowing systems to implement pipeline clocks at significantly higher frequency than the system interface clock.

### System Address/Data Bus

The 64-bit System Address Data (SysAD) bus is used to transfer addresses and data between the RC4640 and the rest of the system. It is protected with an 8-bit parity check bus, SysADC. When initialized for 32-bit operation, SysAD can be viewed as a 32-bit multiplexed bus, with 4 parity check bits.

The system interface is configurable to allow easier interfacing to memory and I/O systems of varying frequencies. The bus frequency and reference timing of the RC4640 are taken from the input clock. The rate at which the CPU transmits data to the system interface is programmable via boot time mode control bits. The rate at which the processor receives data is fully controlled by the external device. Therefore, either a low cost interface requiring no read or write buffering or a faster, high performance interface can be designed to communicate with the RC4640. Again, the system designer has the flexibility to make these price/performance trade-offs.

## **System Command Bus**

The RC4640 interface has a 9-bit System Command (SysCmd) bus. The command bus indicates whether the SysAD bus carries an address or data. If the SysAD carries an address, then the SysCmd bus also indicates what type of transaction is to take place (for example, a read or write). If the SysAD carries data, then the SysCmd bus also gives information about the data (for example, this is the last data word transmitted, or the cache state of this data line is clean exclusive). The SysCmd bus is bidirectional to support both processor requests and external requests to the RC4640. Processor requests are initiated by the RC4640 and responded to by an external device. External requests are issued by an external device and require the RC4640 to respond.

The RC4640 supports single datum (one to eight byte) and 8-word block transfers on the SysAD bus. In the case of a single-datum transfer, the low-order 3 address bits gives the byte address of the transfer, and the SysCmd bus indicates the number of bytes being transferred.

### **Handshake Signals**

There are six handshake signals on the system interface. Two of these, RdRdy\* and WrRdy\* are used by an external device to indicate to the RC4640 whether it can accept a new read or write transaction. The RC4640 samples these signals before deasserting the address on read and write requests.

The following is a list of the supported external requests:

- \* Read Response

- Null

#### IDT79RC4640™

#### **Boot-Time Options**

ExtRqst\* and Release\* are used to transfer control of the SysAD and SysCmd buses between the processor and an external device. When an external device needs to control the interface, it asserts ExtRqst\*. The RC4640 responds by asserting Release\* to release the system interface to slave state.

ValidOut\* and ValidIn\* are used by the RC4640 and the external device respectively to indicate that there is a valid command or data on the SysAD and SysCmd buses. The RC4640 asserts ValidOut\* when it is driving these buses with a valid command or data, and the external device drives ValidIn\* when it has control of the buses and is driving a valid command or data.

#### **Non-overlapping System Interface**

The RC4640 requires a non-overlapping system interface, compatible with the RC4700. This means that only one processor request may be outstanding at a time and that the request must be serviced by an external device before the RC4640 issues another request. The RC4640 can issue read and write requests to an external device, and an external device can issue read and write requests to the RC4640.

The RC4640 asserts ValidOut\* and simultaneously drives the address and read command on the SysAD and SysCmd buses. If the system interface has RdRdy\* or Read transactions asserted, then the processor tristates its drivers and releases the system interface to slave state by asserting Release\*. The external device can then begin sending the data to the RC4640.

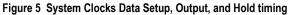

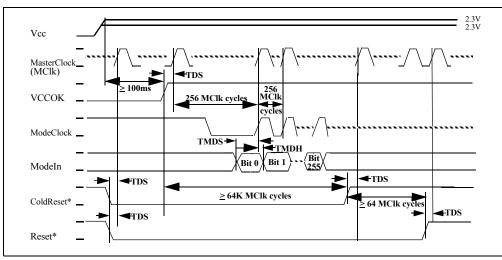

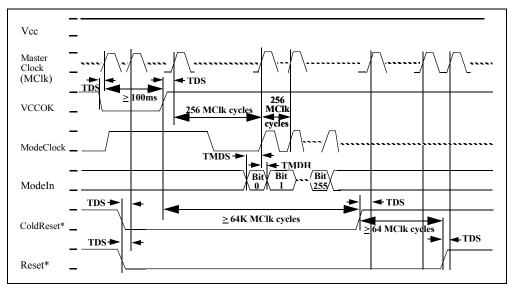

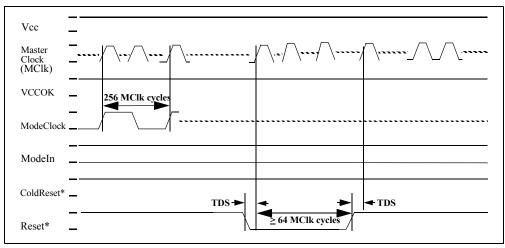

Fundamental operational modes for the processor are initialized by the boot-time mode control interface. The boot-time mode control interface is a serial interface operating at a very low frequency (MasterClock divided by 256). The low-frequency operation allows the initialization information to be kept in a low-cost EPROM; alternatively the twenty-orso bits could be generated by the system interface ASIC or a simple PAL.

Immediately after the VCCOK Signal is asserted, the processor reads a serial bit stream of 256 bits to initialize all fundamental operational modes. After initialization is complete, the processor continues to drive the serial clock output, but no further initialization bits are read.

#### **Boot-Time Modes**

The boot-time serial mode stream is defined in Table 6. Bit 0 is the bit presented to the processor when **VCCOK** is asserted; bit 255 is the last.

#### **Power Management**

CP0 is also used to control the power management for the RC4640. This is the standby mode and it can be used to reduce the power consumption of the internal core of the CPU. The standby mode is entered by executing the WAIT instruction with the SysAD bus idle and is exited by any interrupt.

# **Standby Mode Operation**

The RC4640 provides a means to reduce the amount of power consumed by the internal core when the CPU would otherwise not be performing any useful operations. This is known as "Standby Mode".

#### **Entering Standby Mode**

Executing the WAIT instruction enables interrupts and enters Standby mode. When the WAIT instruction finishes the W pipe-stage, if the SysAd bus is currently idle, the internal clocks will shut down, thus freezing the pipeline. The PLL, internal timer, and some of the input pins (Int[5:0]\*, NMI\*, ExtReg\*, Reset\*, and ColdReset\*) will continue to run.

Figure 2 Typical RC4640 System Architecture

If the conditions are not correct when the WAIT instruction finishes the W pipe-stage (i.e. the SysAd bus is not idle), the WAIT is treated as a NOP.

Once the CPU is in Standby Mode, any interrupt, including the internally generated timer interrupt, will cause the CPU to exit Standby Mode.

# **Thermal Considerations**

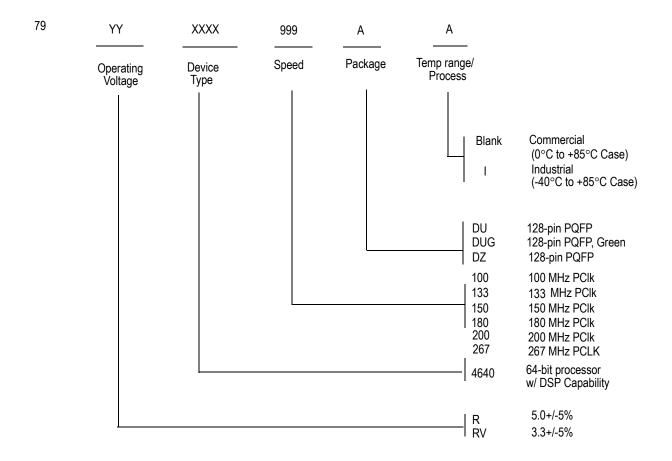

The RC4640 utilizes special packaging techniques to improve the thermal properties of high-speed processors. The RV4640 is packaged using cavity-up packaging in a 128-pin thermally enhanced PQFP package ("DU") with a drop-in heat spreader, for devices with low peak power. The R4640 utilizes the PQFP package for higher power consumption devices (the "DZ" package), which is an all-aluminum package with the die attached to a normal copper lead frame mounted to the aluminum casing.

Due to the heat-spreading effect of the aluminum, the PQFP package allows for an efficient thermal transfer between the die and the case. The aluminum offers less internal resistance from one end of the package to the other, reducing the temperature gradient across the package and therefore presenting a greater area for convection and conduction to the PCB for a given temperature. Even nominal amounts of air flow will dramatically reduce the junction temperature of the die, resulting in cooler operation. The PQFP package is pin and socket compatible with the 128-pin QFP package.

The R4640 and the RV4640 are guaranteed in a case temperature range of  $0^{\circ}$ C to +85°C for commercial temperature parts and the RV4640 in a case temperature range of -40°C to +85°C for industrial

temperature parts. The type of package, speed (power) of the device, and air flow conditions affect the equivalent ambient temperature conditions that will meet this specification.

The equivalent allowable ambient temperature, TA, can be calculated using the thermal resistance from case to ambient ( $\emptyset$ CA) of the given package. The following equation relates ambient and case temperatures:

TA = TC - P \* ØCA

where P is the maximum power consumption at hot temperature, calculated by using the maximum Icc specification for the device. Typical values for  $\emptyset$ CA at various air flows are shown in Table 5.

|                  | ØCA |     |     |     |     |      |

|------------------|-----|-----|-----|-----|-----|------|

| Airflow (ft/min) | 0   | 200 | 400 | 600 | 800 | 1000 |

| 128 PQFP (DU)    | 17  | 9   | 7   | 5   | 4   | 3    |

| 128 PQFP (DZ)    | 20  | 12  | 9.5 | 8   | 7   | 6.5  |

Table 5 Thermal Resistance (ØCA) at Various Airflows

Note that the RC4640 implements advanced power management to substantially reduce the average power dissipation of the device. This operation is described in the *IDT79RC4640/ IDT79RC4650 RISC Processor Hardware User's Manual.*

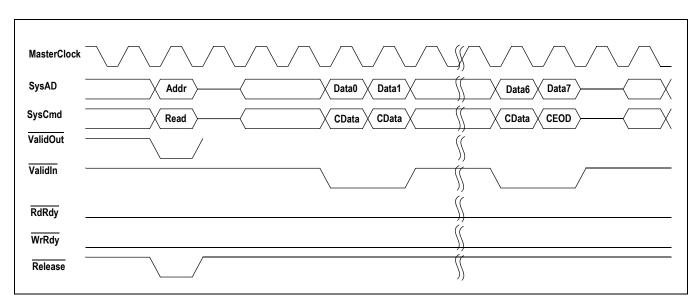

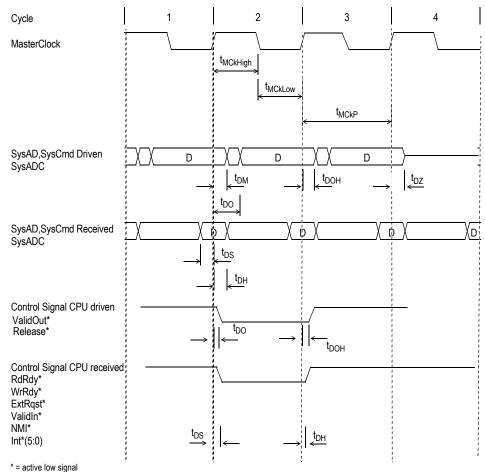

Figure 3 RC4640 Block Read Request

# **Data Sheet Revision History**

# **Changes to version dated December 1995:**

Features:

- Added 32-bit bus interface info

- Deleted items from low-power operation descriptions.

#### Hardware Overview:

- Added detailed descriptions of features.

- Changed Boot Time Mode Stream table values for mode bit 12.

#### DC Electrical Characteristics:

- The C<sub>IN</sub> and C<sub>OUT</sub> values have been changed.

#### AC Electrical Characteristics:

In System Interface Parameters tables (RC4640 and RV4640), Data Setup and Data Hold minimums changed.

#### Valid Combinations:

- List of valid combinations has been corrected.

### **Changes to version dated March 1997:**

#### Features:

- Added preliminary 150 MHz operation frequency

Thermal Considerations:

- Added thermally enhanced packaging ("DU") and drop-in heat spreader information.

- Upgraded 80 to 133MHz speed grade specs to "final."

### **Changes to version dated May 1997:**

Features:

- Added 180 MHz spreader information

- Eliminated 80 MHz

## **Changes to version dated March 1998:**

### Features:

Added 200MHz operating frequency

## Changes to version dated April 1998:

- Features:

- Added 400MB/sec bandwidth reference

- Power Consumption (RV4640):

- Upgraded System Condition Icc active parameters

### **Changes to version dated July 1999:**

- Corrected several incorrect references to tables and figures.

### **Changes to version dated March 2000**

- Replaced existing figure in Mode Configuration Interface Reset Sequence section with 3 reset figures.

- Revised values in System Interface Parameters table.

## **Changes to version dated July 2000**

Revised package information in the Thermal Considerations section, Physical Specifications section, Ordering Information section, and the Valid Combinations section.

## **Changes to version dated April 2001**

In the Data Output and Data Output Hold categories of the System Interface Parameters tables, changed values in the Min column for all speeds from 1.0 and 2.0 to 0.

## **Changes to version dated June 2006**

- Added Green PQFP package for 133MHz DUG on Order Page.

### **Changes to version dated December 2008**

Removed IDT from ordering codes on Ordering Information page.

| <br>MasterClock |                                        |

|-----------------|----------------------------------------|

| SysAD           | Addr X Data0 X Data1 X Data6 X Data7 X |

| SysCmd          | Write CData CData CData CEOD           |

| ValidOut        |                                        |

| ValidIn         |                                        |

| RdRdy           |                                        |

| WrRdy           |                                        |

| Release         |                                        |

|                 | })                                     |

Figure 4 RC4640 Block Write Request

| Mode bit | Description                                                                                                                                                                                                                                                                        |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | Reserved (must be zero)                                                                                                                                                                                                                                                            |

| 4s:1     | Writeback data rate:<br>32-bit<br>$0 \rightarrow \Omega$<br>$1 \rightarrow WWx$<br>$2 \rightarrow WWxx$<br>$3 \rightarrow WxWx$<br>$4 \rightarrow WWxxx$<br>$5 \rightarrow WWxxxx$<br>$6 \rightarrow WxxWxx$<br>$7 \rightarrow WWxxxxx$<br>$8 \rightarrow WxxWxx$<br>9-15 reserved |

| 7:5      | Clock multiplier:<br>$0 \rightarrow 2$<br>$1 \rightarrow 3$<br>$2 \rightarrow 4$<br>$3 \rightarrow 5$<br>$4 \rightarrow 6$<br>$5 \rightarrow 7$<br>$6 \rightarrow 8$<br>7 reserved                                                                                                 |

| 8        | $0 \rightarrow$ Little endian<br>$1 \rightarrow$ Big endian                                                                                                                                                                                                                        |

| 10:9     | $00 \rightarrow \text{R4000 compatible}$<br>$01 \rightarrow \text{reserved}$<br>$10 \rightarrow \text{pipelined writes}$<br>$11 \rightarrow \text{write re-issue}$                                                                                                                 |

| 11       | Disable the timer interrupt on Int[5]                                                                                                                                                                                                                                              |

| 12       | Must be 1                                                                                                                                                                                                                                                                          |

| 14:13    | Output driver strength:<br>$10 \rightarrow 100\%$ strength (fastest)<br>$11 \rightarrow 83\%$ strength<br>$00 \rightarrow 67\%$ strength<br>$01 \rightarrow 50\%$ strength (slowest)                                                                                               |

| 255:15   | Must be zero                                                                                                                                                                                                                                                                       |

Table 6 Boot-time mode stream

# **Pin Description**

The following is a list of interface, interrupt, and miscellaneous pins available on the RC4640. Pin names ending with an asterisk (\*) identify pins that are active when low.

| Туре         | Description                                                                                                                                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| erface       |                                                                                                                                                                    |

| Input        | External request<br>Signals that the system interface needs to submit an external request.                                                                         |

| Output       | Release interface<br>Signals that the processor is releasing the system interface to slave state                                                                   |

| Input        | Read Ready<br>Signals that an external agent can now accept a processor read.                                                                                      |

| Input        | Write Ready<br>Signals that an external agent can now accept a processor write request.                                                                            |

| Input        | Valid Input<br>Signals that an external agent is now driving a valid address or data on the SysAD bus and a valid command or data identifier on the<br>SysCmd bus. |

| Output       | Valid output<br>Signals that the processor is now driving a valid address or data on the SysAD bus and a valid command or data identifier on the<br>SysCmd bus.    |

| Input/Output | System address/data bus<br>A 32-bit address and data bus for communication between the processor and an external agent.                                            |

| Input/Output | System address/data check bus<br>A 4-bit bus containing parity check bits for the SysAD bus during data bus cycles.                                                |

| Input/Output | System command/data identifier bus<br>A 9-bit bus for command and data identifier transmission between the processor and an external agent.                        |

| Input/Output | Reserved system command/data identifier bus parity<br>For the RC4640 this signal is unused on input and zero on output.                                            |

|              | erface<br>Input<br>Output<br>Input<br>Input<br>Input<br>Output<br>Output<br>Input/Output<br>Input/Output                                                           |

| MasterClock | Input | Master clock<br>Master clock input used as the system interface reference clock. All output timings are relative to this input clock. Pipeline operation<br>frequency is derived by multiplying this clock up by the factor selected during boot initialization. |

|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VccP        | Input | Quiet VCC for PLL<br>Quiet VCc for the internal phase locked loop.                                                                                                                                                                                               |

| VssP        | Input | Quiet VSS for PLL   Quiet Vss for the internal phase locked loop.                                                                                                                                                                                                |

Interrupt interface

| Int*(5:0) | Input | Interrupt<br>Six general processor interrupts, bit-wise OR' d with bits 5:0 of the interrupt register. |

|-----------|-------|--------------------------------------------------------------------------------------------------------|

| NMI*      | Input | Non-maskable interrupt<br>Non-maskable interrupt, OR'd with bit 6 of the interrupt register.           |

Initialization interface

| Vccok | Input | VCC is OK                                                                                                                                                                                                                                                 |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |       | When asserted, this signal indicates to the RC4640 that the power supply has been above Vcc minimum for more than 100 millisec-<br>onds and will remain stable. The assertion of Vccok initiates the reading of the boot-time mode control serial stream. |

# **AC Electrical Characteristics — Commercial Temperature Range—R4640**

(V<sub>CC</sub>=5.0V  $\pm$  5%; T<sub>CASE</sub> = -0°C to +85°C)

# **Clock Parameters—R4640**

| Parameter                          | Symbol                            | Test Conditions                   |     | 640<br>MHz       | R4<br>133 | Units            |     |

|------------------------------------|-----------------------------------|-----------------------------------|-----|------------------|-----------|------------------|-----|

|                                    |                                   |                                   | Min | Max              | Min       | Max              |     |

| Pipeline clock frequency           | PClk                              | —                                 | 50  | 100              | 50        | 133              | MHz |

| MasterClock HIGH                   | t <sub>MCHIGH</sub>               | $Transition \leq t_{MCRise/Fall}$ | 4   | —                | 3         | -                | ns  |

| MasterClock LOW                    | t <sub>MCLOW</sub>                | $Transition \leq t_{MCRise/Fall}$ | 4   | —                | 3         | -                | ns  |

| MasterClock Frequency <sup>1</sup> | _                                 | —                                 | 25  | 50               | 25        | 67               | MHz |

| MasterClock Period                 | t <sub>MCP</sub>                  | —                                 | 20  | 40               | 15        | 40               | ns  |

| Clock Jitter for MasterClock       | t <sub>JitterIn</sub> 2           | —                                 | —   | ±250             | —         | ±250             | ps  |

| MasterClock Rise Time              | t <sub>MCRise</sub> 2             | —                                 | -   | 5                | —         | 4                | ns  |

| MasterClock Fall Time              | t <sub>MCFall</sub> 2             | —                                 | -   | 5                | -         | 4                | ns  |

| ModeClock Period                   | t <sub>ModeCKP</sub> <sup>2</sup> | —                                 | -   | 256*             | -         | 256*             | ns  |

|                                    |                                   |                                   |     | t <sub>MCP</sub> |           | t <sub>MCP</sub> |     |

<sup>1.</sup> Operation of the RC4650 is only guaranteed with the Phase Lock Loop enabled.

<sup>2.</sup> Guaranteed by design.

# System Interface Parameters—R4640

(V<sub>CC</sub>=5.0V  $\pm$  5%; T<sub>CASE</sub> = 0°C to +85°C)

Note: Timings are measured from 1.5V of the clock to 1.5V of the signal.

| Parameter                | Symbol                        | Test Conditions                     |                | 640<br>MHz | R4<br>133      | Units |    |

|--------------------------|-------------------------------|-------------------------------------|----------------|------------|----------------|-------|----|

|                          |                               |                                     | Min            | Max        | Min            | Max   |    |

| Data Output <sup>1</sup> | t <sub>DO</sub> = Max         | mode <sub>1413</sub> = 10 (Fastest) | 0 <sup>2</sup> | 9          | 0 <sup>2</sup> | 9     | ns |

|                          |                               | mode <sub>1413</sub> = 11 (85%)     | 0 <sup>2</sup> |            | 0 <sup>2</sup> |       |    |

|                          |                               | mode <sub>1413</sub> = 00 (66%)     | 0 <sup>2</sup> |            | 0 <sup>2</sup> |       |    |

|                          |                               | mode <sub>1413</sub> = 01 (slowest) | 0 <sup>2</sup> | 12         | 0 <sup>2</sup> | 12    | ns |

| Data Output Hold         | t <sub>DOH</sub> <sup>3</sup> | mode <sub>1413</sub> = 10           | 0              | —          | 0              | -     | ns |

|                          |                               | mode <sub>1413</sub> = 11           | 0              | —          | 0              | -     | ns |

|                          |                               | mode <sub>1413</sub> = 00           | 0              | —          | 0              | -     | ns |

|                          |                               | mode <sub>1413</sub> = 01           | 0              | —          | 0              | -     | ns |

| Input Data Setup         | t <sub>DS</sub>               | t <sub>rise</sub> = 5ns             | 5.5            | —          | 4.5            | —     | ns |

| Input Data Hold          | t <sub>DH</sub>               | t <sub>fall</sub> = 5ns             | 2              | -          | 1.5            | -     | ns |

<sup>1</sup> Capacitive load for all output timings is 50pF.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> 50pf loading on external output signals, fastest settings

# **Boot-time Interface Parameters—R4640**

$(V_{CC}=5.0V \pm 5\%; T_{CASE} = 0^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter       | Symbol          | Test       | R4640 100MHz |     | R4640 | 133MHz | Units              |  |

|-----------------|-----------------|------------|--------------|-----|-------|--------|--------------------|--|

| Parameter       | Symbol          | Conditions | Min          | Max | Min   | Max    | Units              |  |

| Mode Data Setup | t <sub>DS</sub> | —          | 3            | —   | 3     | —      | Master Clock Cycle |  |

| Mode Data Hold  | t <sub>DH</sub> | —          | 0            | —   | 0     | _      | Master Clock Cycle |  |

# **Capacitive Load Deration—R4650**

| Parameter   | Symbol          | Test       | 100MHz |     | 133MHz |     | Units   |  |

|-------------|-----------------|------------|--------|-----|--------|-----|---------|--|

| raiametei   | Symbol          | Conditions | Min    | Max | Min    | Max | Units   |  |

| Load Derate | C <sub>LD</sub> | _          | —      | 2   |        | 2   | ns/25pF |  |

## DC Electrical Characteristics — Commercial / Industrial Temperature Range—RV4640

(V<sub>CC</sub> = 3.3 $\pm$ 5%, Commercial T<sub>CASE</sub> = 0°C to +85°C, Industrial T<sub>CASE</sub> = -40°C to +85°C)

| Parameter           | RV4640                 | 133MHz                 | RV4640                 | 150MHz                 | Conditions                |

|---------------------|------------------------|------------------------|------------------------|------------------------|---------------------------|

| Parameter           | Minimum                | Maximum                | Minimum                | Maximum                | Conditions                |

| V <sub>OL</sub>     | -                      | 0.1V                   | -                      | 0.1V                   | I <sub>OUT</sub>   = 20uA |

| V <sub>OH</sub>     | V <sub>CC</sub> - 0.1V | _                      | V <sub>CC</sub> - 0.1V | -                      |                           |

| V <sub>OL</sub>     | _                      | 0.4V                   | _                      | 0.4V                   | I <sub>OUT</sub>   = 4mA  |

| V <sub>OH</sub>     | 2.4V                   | _                      | 2.4V                   | -                      |                           |

| V <sub>IL</sub>     | –0.5V                  | 0.2V <sub>CC</sub>     | –0.5V                  | 0.2V <sub>CC</sub>     | —                         |

| V <sub>IH</sub>     | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | —                         |

| I <sub>IN</sub>     | _                      | ±10uA                  | -                      | ±10uA                  | $0 \le V_{IN} \le V_{CC}$ |

| C <sub>IN</sub>     | —                      | 10pF                   | —                      | 10pF                   | —                         |

| C <sub>OUT</sub>    | —                      | 10pF                   | —                      | 10pF                   | —                         |

| I/O <sub>LEAK</sub> | _                      | 20uA                   | —                      | 20uA                   | Input/Output Leakage      |

| Parameter           | RV4640                 | ) 180MHz               | RV4640                 | ) 200MHz               | RV4640                 | 267MHz <sup>1</sup>    | Conditions                |

|---------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------------|

| Falametei           | Minimum                | Maximum                | Minimum                | Maximum                | Minimum                | Maximum                | Conditions                |

| V <sub>OL</sub>     | -                      | 0.1V                   | —                      | 0.1V                   | -                      | 0.1V                   | I <sub>OUT</sub>   = 20uA |

| V <sub>OH</sub>     | V <sub>CC</sub> - 0.1V | —                      | V <sub>CC</sub> - 0.1V | _                      | V <sub>CC</sub> - 0.1V | _                      |                           |

| V <sub>OL</sub>     | _                      | 0.4V                   | —                      | 0.4V                   | —                      | 0.4V                   | I <sub>OUT</sub>   = 4mA  |

| V <sub>OH</sub>     | 2.4V                   | —                      | 2.4V                   | —                      | 2.4V                   | —                      |                           |

| V <sub>IL</sub>     | -0.5V                  | 0.2V <sub>CC</sub>     | -0.5V                  | 0.2V <sub>CC</sub>     | –0.5V                  | 0.2V <sub>CC</sub>     | _                         |

| V <sub>IH</sub>     | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | —                         |

| I <sub>IN</sub>     | _                      | ±10uA                  | —                      | ±10uA                  | —                      | ±10uA                  | $0 \le V_{IN} \le V_{CC}$ |

| C <sub>IN</sub>     | _                      | 10pF                   | —                      | 10pF                   | —                      | 10pF                   | —                         |

| C <sub>OUT</sub>    | —                      | 10pF                   | —                      | 10pF                   | —                      | 10pF                   | —                         |

| I/O <sub>LEAK</sub> | —                      | 20uA                   | —                      | 20uA                   | —                      | 20uA                   | Input/Output Leakage      |

<sup>1</sup> Industrial temperature range is not available at 267MHz

# **Power Consumption—RV4640**

| De              |                   | RV4640               | 133MHz              | RV4640               | 150MHz             | Conditions                                                                          |

|-----------------|-------------------|----------------------|---------------------|----------------------|--------------------|-------------------------------------------------------------------------------------|

| Pa              | rameter           | Typical <sup>1</sup> | Max                 | Typical <sup>1</sup> | Max                | - Conditions                                                                        |

| Syster          | m Condition       | 133/67MHz            |                     | 150/75MHz            | 1                  | -                                                                                   |

| I <sub>CC</sub> | standby           | -                    | 60 mA <sup>2</sup>  | -                    | 60mA <sup>2</sup>  | $C_L = 0 p F^3$                                                                     |

|                 |                   | —                    | 110 mA <sup>2</sup> | -                    | 110mA <sup>2</sup> | C <sub>L</sub> = 50pF                                                               |

|                 | active,           | 400 mA <sup>2</sup>  | 450 mA <sup>2</sup> | 450 mA <sup>2</sup>  | 500mA <sup>2</sup> | C <sub>L</sub> = 0pF, No SysAd activity <sup>3</sup>                                |

|                 | 64-bit bus option | 450 mA <sup>2</sup>  | 500 mA <sup>2</sup> | 500mA <sup>2</sup>   | 550mA <sup>2</sup> | $C_L$ = 50pF R4x00  compatible writes<br>T <sub>C</sub> = 25°C                      |

|                 |                   | 500 mA <sup>2</sup>  | 575 mA <sup>4</sup> | 550mA <sup>2</sup>   | 625mA <sup>4</sup> | $C_L$ = 50pF Pipelined writes or Write re-issue, T <sub>C</sub> = 25°C <sup>3</sup> |

<sup>1.</sup> Typical integer instruction mix and cache miss rates, Vcc = 3.3V, TA = 25×C.

<sup>2.</sup> These are not tested. They are the result of engineering analysis and are provided for reference only.

<sup>3.</sup> Guaranteed by design.

<sup>4.</sup> These are the specifications IDT tests to insure compliance.

|                 |                   | RV4640 180MHz<br>Typical <sup>1</sup> Max |                    | RV4640                   | 200MHz             | RV4640               | 267MHz              | 0                                                                                      |

|-----------------|-------------------|-------------------------------------------|--------------------|--------------------------|--------------------|----------------------|---------------------|----------------------------------------------------------------------------------------|

| Ра              | rameter           |                                           |                    | Typical <sup>1</sup> Max |                    | Typical <sup>1</sup> | Max                 | - Conditions                                                                           |

| Syste           | m Condition       | 180/60MHz                                 |                    | 200/67MHz                |                    | 267/89MHz            |                     | _                                                                                      |

| I <sub>CC</sub> | standby           | -                                         | 60mA <sup>2</sup>  | -                        | 60mA <sup>2</sup>  | -                    | 60mA <sup>2</sup>   | $C_L = 0 p F^3$                                                                        |

|                 |                   | -                                         | 110mA <sup>2</sup> | -                        | 110mA <sup>2</sup> | -                    | 110mA <sup>2</sup>  | C <sub>L</sub> = 50pF                                                                  |

|                 | active,           | 610 mA <sup>2</sup>                       | 680mA <sup>2</sup> | 685mA <sup>2</sup>       | 760mA <sup>2</sup> | 650mA <sup>2</sup>   | 800mA <sup>2</sup>  | C <sub>L</sub> = 0pF, No SysAd activity <sup>3</sup>                                   |

|                 | 64-bit bus option | 680mA <sup>2</sup>                        | 750mA <sup>2</sup> | 760mA <sup>2</sup>       | 835mA <sup>2</sup> | 750mA <sup>2</sup>   | 900mA <sup>2</sup>  | $C_L$ = 50pF R4x00 compatible writes<br>T <sub>C</sub> = 25°C                          |

|                 |                   | 750mA <sup>2</sup>                        | 850mA <sup>4</sup> | 835mA <sup>2</sup>       | 950mA <sup>4</sup> | 900mA <sup>2</sup>   | 1200mA <sup>4</sup> | $C_L$ = 50pF Pipelined writes or Write<br>re-issue, T <sub>C</sub> = 25 <sup>o</sup> C |

<sup>1.</sup> Typical integer instruction mix and cache miss rates, Vcc = 3.3V, TA = 25×C.

<sup>2.</sup> These are not tested. They are the result of engineering analysis and are provided for reference only.

<sup>3.</sup> Guaranteed by design.

<sup>4.</sup> These are the specifications IDT tests to insure compliance.

# AC Electrical Characteristics — Commercial/Industrial Temperature Range—RV4640

(V<sub>CC</sub>=3.3V  $\pm$  5%; Commercial T<sub>CASE</sub> = 0°C to +85°C, Industrial T<sub>CASE</sub> = -40°C to +85°C)

### **Clock Parameters—RV4640**

Note: Operation of the RC4650 is only guaranteed with the Phase Lock Loop enabled.

| Parameter                    | Symbol                  | Test Conditions                   | RV<br>133 | Units                    |     |  |

|------------------------------|-------------------------|-----------------------------------|-----------|--------------------------|-----|--|

|                              |                         |                                   | Min       | Max                      | ]   |  |

| Pipeline clock Frequency     | PClk                    |                                   | 50        | 133                      | MHz |  |

| MasterClock HIGH             | t <sub>MCHIGH</sub>     | Transition $\leq t_{MCRise/Fall}$ | 3         | —                        | ns  |  |

| MasterClock LOW              | t <sub>MCLOW</sub>      | Transition $\leq t_{MCRise/Fall}$ | 3         | —                        | ns  |  |

| MasterClock Frequency        | _                       | —                                 | 25        | 67                       | MHz |  |

| MasterClock Period           | t <sub>MCP</sub>        | _                                 | 15        | 40                       | ns  |  |

| Clock Jitter for MasterClock | t <sub>JitterIn</sub> 1 | —                                 | —         | ±250                     | ps  |  |

| MasterClock Rise Time        | t <sub>MCRise</sub> 1   | —                                 | —         | 4                        | ns  |  |

| MasterClock Fall Time        | t <sub>MCFall</sub> 1   | <b> </b> _                        | —         | 4                        | ns  |  |

| ModeClock Period             | t <sub>ModeCKP</sub> 1  | -                                 | -         | 256*<br>t <sub>MCP</sub> | ns  |  |

<sup>1.</sup> Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| Parameter                          | RV4640<br>150MHz |                  | RV4640<br>180MHz |                  | RV4640<br>200MHz |                  | RV4640<br>267MHz |                  | Units |

|------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------|

|                                    | Min              | Max              | Min              | Max              | Min              | Max              | Min              | Max              | 1     |

| Pipeline clock Frequency           | 50               | 150              | 50               | 180              | 50               | 200              | 100              | 267              | MHz   |

| MasterClock HIGH                   | 3                | _                | 3                | _                | 3                | _                | 3                | _                | ns    |

| MasterClock LOW                    | 3                | _                | 3                | _                | 3                | _                | 3                | _                | ns    |

| MasterClock Frequency <sup>1</sup> | 25               | 75               | 25               | 90               | 25               | 100              | 50               | 125              | MHz   |

| MasterClock Period                 | 13.3             | 40               | 11.1             | 40               | 10               | 40               | 8                | 20               | ns    |

| Clock Jitter for MasterClock       | _                | ±250             | _                | ±250             | _                | ±250             | _                | ±250             | ps    |

| MasterClock Rise Time              | -                | 3                | —                | 2.5              | —                | 2                | —                | 2                | ns    |

| MasterClock Fall Time              | -                | 3                | —                | 2.5              | —                | 2                | —                | 2                | ns    |

| ModeClock Period                   | _                | 256*             | —                | 256*             | —                | 256*             | —                | 256*             | ns    |

|                                    |                  | t <sub>MCP</sub> |                  | t <sub>MCP</sub> |                  | t <sub>MCP</sub> |                  | t <sub>MCP</sub> |       |

<sup>1.</sup> Operation of the RC4650 is only guaranteed with the Phase Lock Loop enabled.

# System Interface Parameters—RV4640

(V<sub>CC</sub>=3.3V  $\pm$  5%; Commercial T<sub>CASE</sub> = 0°C to +85°C, Industrial T<sub>CASE</sub> = -40°C to +85°C)

**Note:** Timings are measured from 1.5V of the clock to 1.5V of the signal.

| Parameter                | Symbol                        | Test Conditions                     | RV4640<br>133MHz |     | RV4640<br>150MHz |    | Units |  |

|--------------------------|-------------------------------|-------------------------------------|------------------|-----|------------------|----|-------|--|

|                          |                               |                                     | Min              | Max | Max Min Max      |    | 1     |  |

| Data Output <sup>1</sup> | t <sub>DM</sub> = Min         | mode <sub>1413</sub> = 10 (fastest) | 0                | 9   | 0                | 9  | ns    |  |

|                          | t <sub>DO</sub> = Max         | mode <sub>1413</sub> = 01 (slowest) | 0                | 12  | 0                | 12 | ns    |  |

| Data Output Hold         | t <sub>DOH</sub> <sup>2</sup> | mode <sub>1413</sub> = 10 (fastest) | 0                | -   | 0                | -  | ns    |  |

| Input Data Setup         | t <sub>DS</sub>               | t <sub>rise</sub> = 5ns             | 4.5              | -   | 4.5              | -  | ns    |  |

| Input Data Hold          | t <sub>DH</sub>               | t <sub>fall</sub> = 5ns             | 1.5              | -   | 1.5              | —  | ns    |  |

<sup>1.</sup> Capacitive load for all output timings is 50pF.

$^{\rm 2.}$  50pf loading on external output signals, fastest settings

| Parameter        | Symbol                | Test Conditions                     | RV4640<br>180MHz |     |     | l640<br>MHz | RV4<br>267 | Units |    |

|------------------|-----------------------|-------------------------------------|------------------|-----|-----|-------------|------------|-------|----|

|                  |                       |                                     | Min              | Max | Min | Max         | Min        | Max   |    |

| Data Output      | t <sub>DM</sub> = Min | mode <sub>1413</sub> = 10 (fastest) | 0                | 9   | 0   | 4.5         | 0          | 4.5   | ns |

|                  | t <sub>DO</sub> = Max | mode <sub>1413</sub> = 01 (slowest) | 0                | 10  | 0   | 5.0         | 0          | 5.0   | ns |

| Data Output Hold | t <sub>DOH</sub> 1    | mode <sub>1413</sub> = 10 (fastest) | 0                | —   | 0   | —           | 0          | —     | ns |

| Data Input       | t <sub>DS</sub>       | t <sub>rise</sub> = 3ns             | 4.5              | —   | 4.5 | —           | 2.5        | —     | ns |

|                  | t <sub>DH</sub>       | DH t <sub>fall</sub> = 3ns          |                  | -   | 1.5 | —           | 1.0        | -     | ns |

<sup>1.</sup> 50pf loading on external output signals, fastest settings

# **Boot Time Interface Parameters—RV4640**

| Parameter          | Symbol          | DI Test<br>Conditions | 133MHz |     | 150MHz |     | 180MHz |     | 200MHz |     | 267MHz |     | Units | Conditions            |

|--------------------|-----------------|-----------------------|--------|-----|--------|-----|--------|-----|--------|-----|--------|-----|-------|-----------------------|

|                    |                 |                       | Min    | Max |       |                       |

| Mode Data<br>Setup | t <sub>DS</sub> | _                     | 3      | _   | 3      | —   | 3      | 1   | 3      | _   | 3      |     | ns    | Master Clock<br>Cycle |

| Mode Data<br>Hold  | t <sub>DH</sub> | _                     | 0      | _   | 0      | _   | 0      |     | 0      | _   | 0      |     | ns    | Master Clock<br>Cycle |

# **Capacitive Load Deration—RV4640**

| Parameter    | Symbol          | Test<br>Conditions | 133MHz |     | 150MHz |     | 180MHz |     | 200MHz |     | 267MHz |     | Units           |

|--------------|-----------------|--------------------|--------|-----|--------|-----|--------|-----|--------|-----|--------|-----|-----------------|

| i al allocol |                 |                    | Min    | Max | <b>U</b> III () |

| Load Derate  | C <sub>LD</sub> | _                  |        | 2   | 1      | 2   |        | 2   |        | 2   |        | 1   | ns/25pF         |

# **Timing Characteristics—RV4640**

# **Mode Configuration Interface Reset Sequence**

#### Figure 6 Power-on Reset

#### Figure 7 Cold Reset

Figure 8 Warm Reset

# **Physical Specifications - 128-Pin PQFP**

# **RC4640 Package Pin-Out**

N.C. pins should be left floating for maximum flexibility as well as for compatibility with future designs. An asterisk (\*) identifies a pin that is active when low.

| Pin | Function  | Pin | Pin Function |    | Function   | Pin | Function |  |

|-----|-----------|-----|--------------|----|------------|-----|----------|--|

| 1   | N.C.      | 33  | Vcc          | 65 | Vcc        | 97  | Vcc      |  |

| 2   | SysCmd2   | 34  | Vss          | 66 | SysAD28    | 98  | Vss      |  |

| 3   | Vcc       | 35  | SysAD13      | 67 | ColdReset* | 99  | SysAD19  |  |

| 4   | Vss       | 36  | SysAD14      | 68 | SysAD27    | 100 | ValidIn* |  |

| 5   | SysAD5    | 37  | Vss          | 69 | Vss        | 101 | Vcc      |  |

| 6   | WrRdy*    | 38  | Vcc          | 70 | Vcc        | 102 | Vss      |  |

| 7   | ModeClock | 39  | SysAD15      | 71 | N.C.       | 103 | SysAD18  |  |

| 8   | SysAD6    | 40  | Vss          | 72 | SysAD26    | 104 | Int0*    |  |

| 9   | Vcc       | 41  | Vcc          | 73 | N.C.       | 105 | SysAD17  |  |

| 10  | Vss       | 42  | SysADC1      | 74 | Vss        | 106 | Vcc      |  |

| 11  | SysCmd3   | 43  | Vss          | 75 | Vcc        | 107 | Vss      |  |

| 12  | SysAD7    | 44  | Vcc          | 76 | SysAD25    | 108 | Int1*    |  |

| 13  | SysCmd4   | 45  | MasterClock  | 77 | Vss        | 109 | SysAD16  |  |

| 14  | Vcc       | 46  | VssP         | 78 | Vcc        | 110 | Int2*    |  |