Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 768                                                                         |

| Total RAM Bits                 | -                                                                           |

| Number of I/O                  | 66                                                                          |

| Number of Gates                | 30000                                                                       |

| Voltage - Supply               | 1.14V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 81-WFBGA, CSBGA                                                             |

| Supplier Device Package        | 81-UCSP (4x4)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln030v2-zucg81i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Flash Advantages

## Low Power

Flash-based IGLOO nano devices exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. IGLOO nano devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

IGLOO nano devices also have low dynamic power consumption to further maximize power savings; power is reduced even further by the use of a 1.2 V core voltage.

Low dynamic power consumption, combined with low static power consumption and Flash\*Freeze technology, gives the IGLOO nano device the lowest total system power offered by any FPGA.

## Security

Nonvolatile, flash-based IGLOO nano devices do not require a boot PROM, so there is no vulnerable external bitstream that can be easily copied. IGLOO nano devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

IGLOO nano devices utilize a 128-bit flash-based lock and a separate AES key to provide the highest level of security in the FPGA industry for programmed intellectual property and configuration data. In addition, all FlashROM data in IGLOO nano devices can be encrypted prior to loading, using the industry-leading AES-128 (FIPS192) bit block cipher encryption standard. AES was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the 1977 DES standard. IGLOO nano devices have a built-in AES decryption engine and a flash-based AES key that make them the most comprehensive programmable logic device security solution available today. IGLOO nano devices with AES-based security provide a high level of protection for remote field updates over public networks such as the Internet, and are designed to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves.

Security, built into the FPGA fabric, is an inherent component of IGLOO nano devices. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. IGLOO nano devices, with FlashLock and AES security, are unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry-standard security, making remote ISP possible. An IGLOO nano device provides the best available security for programmable logic designs.

## Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based IGLOO nano FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

### Instant On

Microsemi flash-based IGLOO nano devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based IGLOO nano devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs. In addition, glitches and brownouts in system power will not corrupt the IGLOO nano device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based IGLOO nano devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

IGLOO nano flash FPGAs enable the user to quickly enter and exit Flash\*Freeze mode. This is done almost instantly (within 1 µs) and the device retains configuration and data in registers and RAM. Unlike SRAM-based FPGAs, the device does not need to reload configuration and design state from external memory components; instead it retains all necessary information to resume operation immediately.

1-2 Revision 19

IGLOO nano Low Power Flash FPGAs

## Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, performance, and ease of use. Unlike SRAM-based FPGAs, flash-based IGLOO nano devices allow all functionality to be Instant On; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic.

Designers can perform secure remote in-system reprogramming to support future design iterations and field upgrades with confidence that valuable intellectual property cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The IGLOO nano device architecture mitigates the need for ASIC migration at higher user volumes. This makes IGLOO nano devices cost-effective ASIC replacement solutions, especially for applications in the consumer, networking/communications, computing, and avionics markets.

With a variety of devices under \$1, IGLOO nano FPGAs enable cost-effective implementation of programmable logic and quick time to market.

## Firm-Error Immunity

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of IGLOO nano flash-based FPGAs. Once it is programmed, the flash cell configuration element of IGLOO nano FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

## Advanced Flash Technology

The IGLOO nano device offers many benefits, including nonvolatility and reprogrammability, through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

IGLOO nano FPGAs utilize design and process techniques to minimize power consumption in all modes of operation.

### Advanced Architecture

The proprietary IGLOO nano architecture provides granularity comparable to standard-cell ASICs. The IGLOO nano device consists of five distinct and programmable architectural features (Figure 1-3 on page 1-5 to Figure 1-4 on page 1-5):

- Flash\*Freeze technology

- FPGA VersaTiles

- Dedicated FlashROM

- Dedicated SRAM/FIFO memory<sup>†</sup>

- Extensive CCCs and PLLs<sup>†</sup>

- Advanced I/O structure

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the IGLOO nano core tile as either a three-input lookup table (LUT) equivalent or a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the ProASIC<sup>®</sup> family of third-generation-architecture flash FPGAs. VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

Revision 19 1-3

<sup>†</sup> The AGLN030 and smaller devices do not support PLL or SRAM.

Table 2-2 • Recommended Operating Conditions 1

| Symbol              | P                       | arameter                                                | Extended<br>Commercial  | Industrial               | Units |

|---------------------|-------------------------|---------------------------------------------------------|-------------------------|--------------------------|-------|

| T <sub>J</sub>      | Junction temperature    |                                                         | $-20 \text{ to} + 85^2$ | -40 to +100 <sup>2</sup> | °C    |

| VCC                 | 1.5 V DC core supply vo | oltage <sup>3</sup>                                     | 1.425 to 1.575          | 1.425 to 1.575           | V     |

|                     | 1.2 V–1.5 V wide range  | core voltage <sup>4,5</sup>                             | 1.14 to 1.575           | 1.14 to 1.575            | V     |

| VJTAG               | JTAG DC voltage         |                                                         | 1.4 to 3.6              | 1.4 to 3.6               | V     |

| VPUMP <sup>6</sup>  | Programming voltage     | Programming mode                                        | 3.15 to 3.45            | 3.15 to 3.45             | V     |

|                     |                         | Operation                                               | 0 to 3.6                | 0 to 3.6                 | V     |

| VCCPLL <sup>7</sup> | Analog power supply     | 1.5 V DC core supply voltage <sup>3</sup>               | 1.425 to 1.575          | 1.425 to 1.575           | V     |

|                     | (PLL)                   | 1.2 V–1.5 V wide range core supply voltage <sup>4</sup> | 1.14 to 1.575           | 1.14 to 1.575            | V     |

| VCCI and            | 1.2 V DC supply voltage | ,4                                                      | 1.14 to 1.26            | 1.14 to 1.26             | V     |

| VMV <sup>8,9</sup>  | 1.2 V DC wide range su  | pply voltage <sup>4</sup>                               | 1.14 to 1.575           | 1.14 to 1.575            | V     |

|                     | 1.5 V DC supply voltage | •                                                       | 1.425 to 1.575          | 1.425 to 1.575           | V     |

|                     | 1.8 V DC supply voltage |                                                         | 1.7 to 1.9              | 1.7 to 1.9               | V     |

|                     | 2.5 V DC supply voltage |                                                         | 2.3 to 2.7              | 2.3 to 2.7               | V     |

|                     | 3.3 V DC supply voltage | •                                                       | 3.0 to 3.6              | 3.0 to 3.6               | V     |

|                     | 3.3 V DC wide range su  | pply voltage <sup>10</sup>                              | 2.7 to 3.6              | 2.7 to 3.6               | V     |

### Notes:

- 1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 2. Default Junction Temperature Range in the Libero SoC software is set to 0°C to +70°C for commercial, and -40°C to +85°C for industrial. To ensure targeted reliability standards are met across the full range of junction temperatures, Microsemi recommends using custom settings for temperature range before running timing and power analysis tools. For more information regarding custom settings, refer to the New Project Dialog Box in the Libero Online Help.

- 3. For IGLOO® nano V5 devices

- 4. For IGLOO nano V2 devices only, operating at VCCI ≥ VCC

- 5. IGLOO nano V5 devices can be programmed with the VCC core voltage at 1.5 V only. IGLOO nano V2 devices can be programmed with the VCC core voltage at 1.2 V (with FlashPro4 only) or 1.5 V. If you are using FlashPro3 and want to do in-system programming using 1.2 V, please contact the factory.

- 6.  $V_{PUMP}$  can be left floating during operation (not programming mode).

- 7. VCCPLL pins should be tied to VCC pins. See the "Pin Descriptions" chapter for further information.

- 8. VMV pins must be connected to the corresponding VCCI pins. See the Pin Descriptions chapter of the IGLOO nano FPGA Fabric User's Guide for further information.

- 9. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-21 on page 2-19. VCCI should be at the same voltage within a given I/O bank.

- 10. 3.3 V wide range is compliant to the JESD8-B specification and supports 3.0 V VCCI operation.

Table 2-3 • Flash Programming Limits – Retention, Storage, and Operating Temperature<sup>1</sup>

| Product<br>Grade |     | Program Retention (biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) <sup>2</sup> | Maximum Operating Junction<br>Temperature T <sub>J</sub> (°C) <sup>2</sup> |

|------------------|-----|-------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|

| Commercial       | 500 | 20 years                            | 110                                                               | 100                                                                        |

| Industrial       | 500 | 20 years                            | 110                                                               | 100                                                                        |

### Notes:

- 1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

- These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

2-2 Revision 19

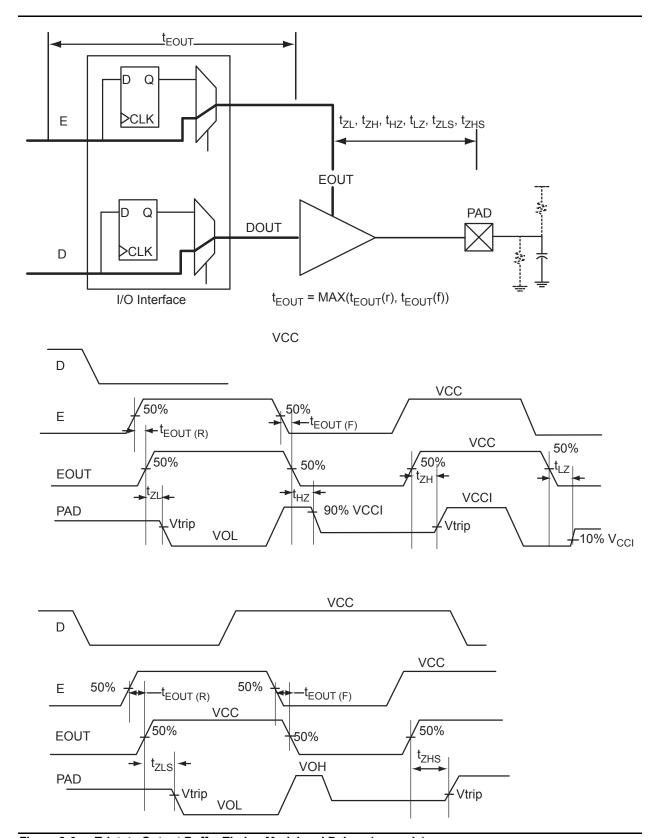

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (example)

2-18 Revision 19

## Applies to 1.2 V DC Core Voltage

Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 4.09            | 0.26             | 0.97            | 1.36             | 1.10              | 4.16            | 3.91            | 2.19            | 2.64            | ns    |

| 4 mA           | STD         | 1.55              | 4.09            | 0.26             | 0.97            | 1.36             | 1.10              | 4.16            | 3.91            | 2.19            | 2.64            | ns    |

| 6 mA           | STD         | 1.55              | 3.45            | 0.26             | 0.97            | 1.36             | 1.10              | 3.51            | 3.32            | 2.43            | 3.03            | ns    |

| 8 mA           | STD         | 1.55              | 3.45            | 0.26             | 0.97            | 1.36             | 1.10              | 3.51            | 3.32            | 2.43            | 3.03            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-39 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 2.68            | 0.26             | 0.97            | 1.36             | 1.10              | 2.72            | 2.26            | 2.19            | 2.74            | ns    |

| 4 mA           | STD         | 1.55              | 2.68            | 0.26             | 0.97            | 1.36             | 1.10              | 2.72            | 2.26            | 2.19            | 2.74            | ns    |

| 6 mA           | STD         | 1.55              | 2.31            | 0.26             | 0.97            | 1.36             | 1.10              | 2.34            | 1.90            | 2.43            | 3.14            | ns    |

| 8 mA           | STD         | 1.55              | 2.31            | 0.26             | 0.97            | 1.36             | 1.10              | 2.34            | 1.90            | 2.43            | 3.14            | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-28 Revision 19

## Applies to 1.2 V DC Core Voltage

Table 2-49 • 2.5 LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 4.61            | 0.26             | 1.21            | 1.39             | 1.10              | 4.55            | 4.61            | 2.15            | 2.43            | ns    |

| 4 mA           | STD         | 1.55              | 4.61            | 0.26             | 1.21            | 1.39             | 1.10              | 4.55            | 4.61            | 2.15            | 2.43            | ns    |

| 6 mA           | STD         | 1.55              | 3.86            | 0.26             | 1.21            | 1.39             | 1.10              | 3.82            | 3.86            | 2.41            | 2.89            | ns    |

| 8 mA           | STD         | 1.55              | 3.86            | 0.26             | 1.21            | 1.39             | 1.10              | 3.82            | 3.86            | 2.41            | 2.89            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-50 • 2.5 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 2.68            | 0.26             | 1.21            | 1.39             | 1.10              | 2.72            | 2.54            | 2.15            | 2.51            | ns    |

| 4 mA           | STD         | 1.55              | 2.68            | 0.26             | 1.21            | 1.39             | 1.10              | 2.72            | 2.54            | 2.15            | 2.51            | ns    |

| 6 mA           | STD         | 1.55              | 2.30            | 0.26             | 1.21            | 1.39             | 1.10              | 2.33            | 2.04            | 2.41            | 2.99            | ns    |

| 8 mA           | STD         | 1.55              | 2.30            | 0.26             | 1.21            | 1.39             | 1.10              | 2.33            | 2.04            | 2.41            | 2.99            | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-34 Revision 19

IGLOO nano Low Power Flash FPGAs

## 1.5 V LVCMOS (JESD8-11)

Low-Voltage CMOS for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for general purpose 1.5 V applications. It uses a 1.5 V input buffer and a push-pull output buffer.

Table 2-57 • Minimum and Maximum DC Input and Output Levels

| 1.5 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 13                      | 16                      | 10                      | 10                      |

### Notes:

- 1. I<sub>II</sub> is the input leakage current per I/O pin over recommended operating conditions where –0.3 < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions where VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Figure 2-10 • AC Loading

Table 2-58 • 1.5 V LVCMOS AC Waveforms, Measuring Points, and Capacitive Loads

| Input LOW (V) | Input HIGH (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.5            | 0.75                 | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

Revision 19 2-37

IGLOO nano Low Power Flash FPGAs

## 1.2 V DC Core Voltage

Table 2-80 • Input DDR Propagation Delays Commercial-Case Conditions:  $T_J = 70^{\circ}\text{C}$ , Worst-Case VCC = 1.14 V

| Parameter               | Description                                          | Std.   | Units |

|-------------------------|------------------------------------------------------|--------|-------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR for Input DDR                    | 0.76   | ns    |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF for Input DDR                    | 0.94   | ns    |

| t <sub>DDRISUD1</sub>   | Data Setup for Input DDR (negedge)                   | 0.93   | ns    |

| t <sub>DDRISUD2</sub>   | Data Setup for Input DDR (posedge)                   | 0.84   | ns    |

| t <sub>DDRIHD1</sub>    | Data Hold for Input DDR (negedge)                    | 0.00   | ns    |

| t <sub>DDRIHD2</sub>    | Data Hold for Input DDR (posedge)                    | 0.00   | ns    |

| t <sub>DDRICLR2Q1</sub> | Asynchronous Clear-to-Out Out_QR for Input DDR       | 1.23   | ns    |

| t <sub>DDRICLR2Q2</sub> | Asynchronous Clear-to-Out Out_QF for Input DDR       | 1.42   | ns    |

| t <sub>DDRIREMCLR</sub> | Asynchronous Clear Removal Time for Input DDR        | 0.00   | ns    |

| t <sub>DDRIRECCLR</sub> | Asynchronous Clear Recovery Time for Input DDR       | 0.24   | ns    |

| t <sub>DDRIWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for Input DDR | 0.19   | ns    |

| t <sub>DDRICKMPWH</sub> | Clock Minimum Pulse Width HIGH for Input DDR         | 0.31   | ns    |

| t <sub>DDRICKMPWL</sub> | Clock Minimum Pulse Width LOW for Input DDR          | 0.28   | ns    |

| F <sub>DDRIMAX</sub>    | Maximum Frequency for Input DDR                      | 160.00 | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Revision 19 2-53

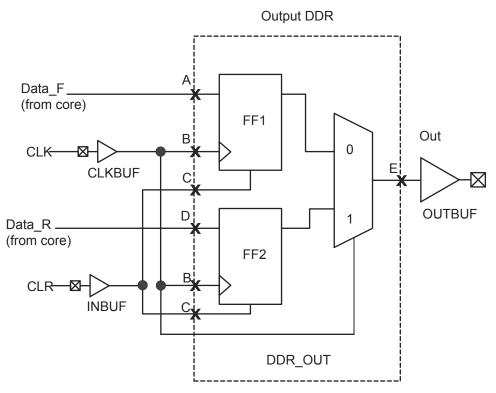

## **Output DDR Module**

Figure 2-19 • Output DDR Timing Model

Table 2-81 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (from, to) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | C, B                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | C, B                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | A, B                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | A, B                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

2-54 Revision 19

Figure 2-22 • Timing Model and Waveforms

2-58 Revision 19

Table 2-92 • AGLN125 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.36              | 1.71              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.39              | 1.82              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.43              | ns    |

### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-93 • AGLN250 Global Resource Commercial-Case Conditions: T<sub>.I</sub> = 70°C, VCC = 1.425 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.39              | 1.73              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.41              | 1.84              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.43              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-66 Revision 19

### 1.2 V DC Core Voltage

Table 2-94 • AGLN010 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           |   | Std.              |                   |       |

|----------------------|-------------------------------------------|---|-------------------|-------------------|-------|

| Parameter            | Description                               | • | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |   | 1.71              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |   | 1.78              | 2.31              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |   | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |   | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |   |                   | 0.53              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-95 • AGLN015 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           |     | Std.            |                   |       |

|----------------------|-------------------------------------------|-----|-----------------|-------------------|-------|

| Parameter            | Description                               | Mir | 1. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.8 | 31              | 2.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.9 | 90              | 2.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.4 | 10              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.6 | 35              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |     |                 | 0.61              | ns    |

### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Revision 19 2-67

IGLOO nano Low Power Flash FPGAs

Table 2-98 • AGLN125 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.08              | 2.54              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.15              | 2.77              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.62              | ns    |

### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-99 • AGLN250 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.11              | 2.57              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.19              | 2.81              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.62              | ns    |

### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Revision 19 2-69

Table 2-105 • RAM512X18

## Commercial-Case Conditions: $T_J = 70^{\circ}C$ , Worst-Case VCC = 1.14 V

| Parameter             | Description                                                                                                         | Std.  | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|-------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 1.28  | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.25  | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 1.13  | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.13  | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                          | 1.10  | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                           | 0.55  | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained)                                                                | 6.56  | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                      | 2.67  | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address; applicable to opening edge | 0.87  | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address; applicable to opening edge |       | ns    |

| t <sub>RSTBQ</sub>    | RESET LOW to data out LOW on RD (flow through)                                                                      | 3.21  | ns    |

|                       | RESET LOW to data out LOW on RD (pipelined)                                                                         | 3.21  | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.93  | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 4.94  | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 1.18  | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 10.90 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 92    | MHz   |

### Notes:

2-80 Revision 19

<sup>1.</sup> For more information, refer to the application note AC374: Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based FPGAs and SoC FPGAs App Note.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

## 1.2 V DC Core Voltage

Table 2-107 • FIFO

Worst Commercial-Case Conditions:  $T_J = 70$ °C, VCC = 1.14 V

| Parameter            | Description                                       | Std.  | Units |

|----------------------|---------------------------------------------------|-------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 3.44  | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.26  | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.30  | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00  | ns    |

| t <sub>DS</sub>      | Input Data (DI) Setup Time                        | 1.30  | ns    |

| t <sub>DH</sub>      | Input Data (DI) Hold Time                         | 0.41  | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 5.67  | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 3.02  | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 6.02  | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 5.71  | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 22.17 | ns    |

| t <sub>RSTFG</sub>   | RESET LOW to Empty/Full Flag Valid                | 5.93  | ns    |

| t <sub>RSTAF</sub>   | RESET LOW to Almost Empty/Full Flag Valid         | 21.94 | ns    |

| t <sub>RSTBQ</sub>   | RESET LOW to Data Out Low on RD (flow-through)    | 3.41  | ns    |

|                      | RESET LOW to Data Out Low on RD (pipelined)       | 4.09  | 3.41  |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 1.02  | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 5.48  | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 1.18  | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 10.90 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 92    | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

2-86 Revision 19

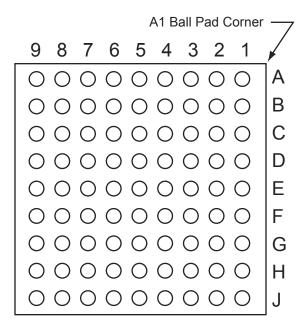

## **UC81**

Note: This is the bottom view of the package.

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

Revision 19 4-3

Package Pin Assignments

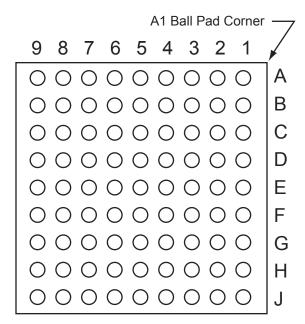

## **CS81**

Note: This is the bottom view of the package.

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

4-6 Revision 19

## Package Pin Assignments

|            | CS81              |  |  |

|------------|-------------------|--|--|

| Pin Number | AGLN060Z Function |  |  |

| A1         | GAA0/IO02RSB0     |  |  |

| A2         | GAA1/IO03RSB0     |  |  |

| A3         | GAC0/IO06RSB0     |  |  |

| A4         | IO09RSB0          |  |  |

| A5         | IO13RSB0          |  |  |

| A6         | IO18RSB0          |  |  |

| A7         | GBB0/IO21RSB0     |  |  |

| A8         | GBA1/IO24RSB0     |  |  |

| A9         | GBA2/IO25RSB0     |  |  |

| B1         | GAA2/IO95RSB1     |  |  |

| B2         | GAB0/IO04RSB0     |  |  |

| В3         | GAC1/IO07RSB0     |  |  |

| B4         | IO08RSB0          |  |  |

| B5         | IO15RSB0          |  |  |

| В6         | GBC0/IO19RSB0     |  |  |

| В7         | GBB1/IO22RSB0     |  |  |

| В8         | IO26RSB0          |  |  |

| В9         | GBB2/IO27RSB0     |  |  |

| C1         | GAB2/IO93RSB1     |  |  |

| C2         | IO94RSB1          |  |  |

| C3         | GND               |  |  |

| C4         | IO10RSB0          |  |  |

| C5         | IO17RSB0          |  |  |

| C6         | GND               |  |  |

| C7         | GBA0/IO23RSB0     |  |  |

| C8         | GBC2/IO29RSB0     |  |  |

| C9         | IO31RSB0          |  |  |

| D1         | GAC2/IO91RSB1     |  |  |

| D2         | IO92RSB1          |  |  |

| D3         | GFA2/IO80RSB1     |  |  |

| D4         | VCC               |  |  |

| D5         | VCCIB0            |  |  |

| D6         | GND               |  |  |

| D7         | GCC2/IO43RSB0     |  |  |

|                 | CS81              |

|-----------------|-------------------|

| Pin Number      | AGLN060Z Function |

| D8              | GCC1/IO35RSB0     |

| D9              | GCC0/IO36RSB0     |

| E1              | GFB0/IO83RSB1     |

| E2              | GFB1/IO84RSB1     |

| E3              | GFA1/IO81RSB1     |

| E4              | VCCIB1            |

| E5              | VCC               |

| E6              | VCCIB0            |

| E7              | GCA1/IO39RSB0     |

| E8              | GCA0/IO40RSB0     |

| E9              | GCB2/IO42RSB0     |

| F1 <sup>1</sup> | VCCPLF            |

| F2 <sup>1</sup> | VCOMPLF           |

| F3              | GND               |

| F4              | GND               |

| F5              | VCCIB1            |

| F6              | GND               |

| F7              | GDA1/IO49RSB0     |

| F8              | GDC1/IO45RSB0     |

| F9              | GDC0/IO46RSB0     |

| G1              | GEA0/IO69RSB1     |

| G2              | GEC1/IO74RSB1     |

| G3              | GEB1/IO72RSB1     |

| G4              | IO63RSB1          |

| G5              | IO60RSB1          |

| G6              | IO54RSB1          |

| G7              | GDB2/IO52RSB1     |

| G8              | VJTAG             |

| G9              | TRST              |

| H1              | GEA1/IO70RSB1     |

| H2              | FF/GEB2/IO67RSB1  |

| H3              | IO65RSB1          |

| H4              | IO62RSB1          |

| H5              | IO59RSB1          |

|                 | CS81              |

|-----------------|-------------------|

| Pin Number      | AGLN060Z Function |

| H6              | IO56RSB1          |

| H7 <sup>2</sup> | GDA2/IO51RSB1     |

| H8              | TDI               |

| H9              | TDO               |

| J1              | GEA2/IO68RSB1     |

| J2              | GEC2/IO66RSB1     |

| J3              | IO64RSB1          |

| J4              | IO61RSB1          |

| J5              | IO58RSB1          |

| J6              | IO55RSB1          |

| J7              | TCK               |

| J8              | TMS               |

| J9              | VPUMP             |

### Notes:

- 1. Pin numbers F1 and F2 must be connected to ground because a PLL is not supported for AGLN060Z-CS81.

- 2. The bus hold attribute (hold previous I/O state in Flash\*Freeze mode) is not supported for pin H7 in AGLN060Z-CS81.

4-10 Revision 19

Package Pin Assignments

|            | CS81              |

|------------|-------------------|

| Pin Number | AGLN125Z Function |

| A1         | GAA0/IO00RSB0     |

| A2         | GAA1/IO01RSB0     |

| A3         | GAC0/IO04RSB0     |

| A4         | IO13RSB0          |

| A5         | IO22RSB0          |

| A6         | IO32RSB0          |

| A7         | GBB0/IO37RSB0     |

| A8         | GBA1/IO40RSB0     |

| A9         | GBA2/IO41RSB0     |

| B1         | GAA2/IO132RSB1    |

| B2         | GAB0/IO02RSB0     |

| В3         | GAC1/IO05RSB0     |

| B4         | IO11RSB0          |

| B5         | IO25RSB0          |

| В6         | GBC0/IO35RSB0     |

| В7         | GBB1/IO38RSB0     |

| B8         | IO42RSB0          |

| В9         | GBB2/IO43RSB0     |

| C1         | GAB2/IO130RSB1    |

| C2         | IO131RSB1         |

| C3         | GND               |

| C4         | IO15RSB0          |

| C5         | IO28RSB0          |

| C6         | GND               |

| C7         | GBA0/IO39RSB0     |

| C8         | GBC2/IO45RSB0     |

| C9         | IO47RSB0          |

| D1         | GAC2/IO128RSB1    |

| D2         | IO129RSB1         |

| D3         | GFA2/IO117RSB1    |

| D4         | VCC               |

| D5         | VCCIB0            |

| D6         | GND               |

| D7         | GCC2/IO59RSB0     |

| D8         | GCC1/IO51RSB0     |

| D9         | GCC0/IO52RSB0     |

|            | CS81              |

|------------|-------------------|

| Pin Number | AGLN125Z Function |

| E1         | GFB0/IO120RSB1    |

| E2         | GFB1/IO121RSB1    |

| E3         | GFA1/IO118RSB1    |

| E4         | VCCIB1            |

| E5         | VCC               |

| E6         | VCCIB0            |

| E7         | GCA0/IO56RSB0     |

| E8         | GCA1/IO55RSB0     |

| E9         | GCB2/IO58RSB0     |

| F1*        | VCCPLF            |

| F2*        | VCOMPLF           |

| F3         | GND               |

| F4         | GND               |

| F5         | VCCIB1            |

| F6         | GND               |

| F7         | GDA1/IO65RSB0     |

| F8         | GDC1/IO61RSB0     |

| F9         | GDC0/IO62RSB0     |

| G1         | GEA0/IO104RSB1    |

| G2         | GEC0/IO108RSB1    |

| G3         | GEB1/IO107RSB1    |

| G4         | IO96RSB1          |

| G5         | IO92RSB1          |

| G6         | IO72RSB1          |

| G7         | GDB2/IO68RSB1     |

| G8         | VJTAG             |

| G9         | TRST              |

| H1         | GEA1/IO105RSB1    |

| H2         | FF/GEB2/IO102RSB1 |

| НЗ         | IO99RSB1          |

| H4         | IO94RSB1          |

| H5         | IO91RSB1          |

| H6         | IO81RSB1          |

| H7         | GDA2/IO67RSB1     |

| H8         | TDI               |

| H9         | TDO               |

| CS81       |                   |  |

|------------|-------------------|--|

| Pin Number | AGLN125Z Function |  |

| J1         | GEA2/IO103RSB1    |  |

| J2         | GEC2/IO101RSB1    |  |

| J3         | IO97RSB1          |  |

| J4         | IO93RSB1          |  |

| J5         | IO90RSB1          |  |

| J6         | IO78RSB1          |  |

| J7         | TCK               |  |

| J8         | TMS               |  |

| J9         | VPUMP             |  |

Note: \* Pin numbers F1 and F2 must be connected to ground because a PLL is not supported for AGLN125Z-CS81.

4-12 Revision 19

## Datasheet Information

| Revision / Version                               | Changes                                                                                                                                                                                                                                                                                                              | Page       |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 2 (Dec 2008) Product Brief Advance v0.4 | The second table note in "IGLOO nano Devices" table was revised to state, "AGLN060, AGLN125, and AGLN250 in the CS81 package do not support PLLs. AGLN030 and smaller devices do not support this feature."                                                                                                          | II         |

|                                                  | The I/Os per package for CS81 were revised to 60 for AGLN060, AGLN125, and AGLN250 in the "I/Os Per Package"table.                                                                                                                                                                                                   | II         |

| Packaging Advance v0.3                           | The "UC36" pin table is new.                                                                                                                                                                                                                                                                                         | 4-2        |

| Revision 1 (Nov 2008)                            | The "Advanced I/Os" section was updated to include wide power supply voltage                                                                                                                                                                                                                                         | I          |

| Product Brief Advance v0.3                       | support for 1.14 V to 1.575 V.                                                                                                                                                                                                                                                                                       |            |

|                                                  | The AGLN030 device was added to product tables and replaces AGL030 entries that were formerly in the tables.                                                                                                                                                                                                         | VI         |

|                                                  | The "I/Os Per Package"table was updated for the CS81 package to change the number of I/Os for AGLN060, AGLN125, and AGLN250 from 66 to 64.                                                                                                                                                                           | II         |

|                                                  | The "Wide Range I/O Support" section is new.                                                                                                                                                                                                                                                                         | 1-8        |

|                                                  | The table notes and references were revised in Table 2-2 • Recommended Operating Conditions <sup>1</sup> . VMV was included with VCCI and a table note was added stating, "VMV pins must be connected to the corresponding VCCI pins. See <i>Pin Descriptions</i> for further information." Please review carefully. | 2-2        |

|                                                  | VJTAG was added to the list in the table note for Table 2-9 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Flash*Freeze Mode*. Values were added for AGLN010, AGLN015, and AGLN030 for 1.5 V.                                                                                                          | 2-7        |

|                                                  | VCCI was removed from the list in the table note for Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Sleep Mode*.                                                                                                                                                                            | 2-8        |

|                                                  | Values for I <sub>CCA</sub> current were updated for AGLN010, AGLN015, and AGLN030 in Table 2-12 • Quiescent Supply Current (IDD), No IGLOO nano Flash*Freeze Mode <sup>1</sup> .                                                                                                                                    | 2-8        |

|                                                  | Values for PAC1 and PAC2 were added to Table 2-15 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices and Table 2-17 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices.                                                                      | 2-10, 2-11 |

|                                                  | Table notes regarding wide range support were added to Table 2-21 • Summary of Maximum and Minimum DC Input and Output Levels.                                                                                                                                                                                       | 2-19       |

|                                                  | 1.2 V LVCMOS wide range values were added to Table 2-22 • Summary of Maximum and Minimum DC Input Levels and Table 2-23 • Summary of AC Measuring Points.                                                                                                                                                            | 2-19, 2-20 |

|                                                  | The following table note was added to Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings and Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings: "All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range, as specified in the JESD8-B specification."  | 2-21       |

|                                                  | 3.3 V LVCMOS Wide Range and 1.2 V Wide Range were added to Table 2-28 • I/O Output Buffer Maximum Resistances <sup>1</sup> and Table 2-30 • I/O Short Currents IOSH/IOSL.                                                                                                                                            | 2-23, 2-24 |

5-6 Revision 19