Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 3072                                                                        |

| Total RAM Bits                 | 36864                                                                       |

| Number of I/O                  | 71                                                                          |

| Number of Gates                | 125000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                    |

| Supplier Device Package        | 100-VQFP (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln125v5-zvq100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# IGLOO nano Products Available in the Z Feature Grade

| IGLOO nano-Z Devices | AGLN030Z* | AGLN060Z* | AGLN125Z* | AGLN250Z* |

|----------------------|-----------|-----------|-----------|-----------|

|                      | QN48      | -         | -         | _         |

|                      | QN68      | ı         | -         | _         |

|                      | UC81      | -         | -         | -         |

|                      | CS81      | CS81      | CS81      | CS81      |

| Packages             | VQ100     | VQ100     | VQ100     | VQ100     |

Note: \*Not recommended for new designs.

# **Temperature Grade Offerings**

|         | AGLN010 | AGLN015 <sup>*</sup> | AGLN020 |           | AGLN060   | AGLN125   | AGLN250               |

|---------|---------|----------------------|---------|-----------|-----------|-----------|-----------------------|

| Package |         |                      |         | AGLN030Z* | AGLN060Z* | AGLN125Z* | AGLN250Z <sup>*</sup> |

| UC36    | C, I    | -                    | _       | _         | -         | -         | -                     |

| QN48    | C, I    | -                    | -       | C, I      | -         | -         | -                     |

| QN68    | -       | C, I                 | C, I    | C, I      | -         | -         | -                     |

| UC81    | _       | -                    | C, I    | C, I      | -         | _         | -                     |

| CS81    | _       | -                    | C, I    | C, I      | C, I      | C, I      | C, I                  |

| VQ100   | _       | -                    | -       | C, I      | C, I      | C, I      | C, I                  |

Note: \* Not recommended for new designs.

C = Enhanced Commercial temperature range: -20°C to +85°C junction temperature

I = Industrial temperature range: -40°C to +100°C junction temperature

Contact your local Microsemi representative for device availability: http://www.microsemi.com/soc/contact/default.aspx.

VI Revision 19

# Specifying I/O States During Programming

You can modify the I/O states during programming in FlashPro. In FlashPro, this feature is supported for PDB files generated from Designer v8.5 or greater. See the *FlashPro User's Guide* for more information.

Note: PDB files generated from Designer v8.1 to Designer v8.4 (including all service packs) have limited display of Pin Numbers only.

- Load a PDB from the FlashPro GUI. You must have a PDB loaded to modify the I/O states during programming.

- 2. From the FlashPro GUI, click PDB Configuration. A FlashPoint Programming File Generator window appears.

- 3. Click the Specify I/O States During Programming button to display the Specify I/O States During Programming dialog box.

- 4. Sort the pins as desired by clicking any of the column headers to sort the entries by that header. Select the I/Os you wish to modify (Figure 1-7 on page 1-9).

- 5. Set the I/O Output State. You can set Basic I/O settings if you want to use the default I/O settings for your pins, or use Custom I/O settings to customize the settings for each pin. Basic I/O state settings:

- 1 I/O is set to drive out logic High

- 0 I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming

Z -Tri-State: I/O is tristated

Figure 1-7 • I/O States During Programming Window

Revision 19 1-9

Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Sleep Mode\*

|                                           | Core<br>Voltage  | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|-------------------------------------------|------------------|---------|---------|---------|---------|---------|---------|-------|

| VCCI= 1.2 V (per bank)<br>Typical (25°C)  | 1.2 V            | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | μΑ    |

| VCCI = 1.5 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | μΑ    |

| VCCI = 1.8 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | μΑ    |

| VCCI = 2.5 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | μΑ    |

| VCCI = 3.3 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | μΑ    |

Note:  $*I_{DD} = N_{BANKS} * I_{CCI}$ .

Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Shutdown Mode

|                   | Core Voltage  | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|-------------------|---------------|---------|---------|---------|---------|---------|---------|-------|

| Typical<br>(25°C) | 1.2 V / 1.5 V | 0       | 0       | 0       | 0       | 0       | 0       | μА    |

Table 2-12 • Quiescent Supply Current (IDD), No IGLOO nano Flash\*Freeze Mode<sup>1</sup>

|                                                   | Core<br>Voltage | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|---------------------------------------------------|-----------------|---------|---------|---------|---------|---------|---------|-------|

| ICCA Current <sup>2</sup>                         |                 |         |         |         |         |         |         |       |

| Typical (25°C)                                    | 1.2 V           | 3.7     | 5       | 5       | 10      | 13      | 18      | μA    |

|                                                   | 1.5 V           | 8       | 14      | 14      | 20      | 28      | 44      | μΑ    |

| ICCI or IJTAG Current                             |                 |         |         |         |         |         |         |       |

| VCCI / VJTAG = 1.2 V (per bank) Typical (25°C)    | 1.2 V           | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | μA    |

| VCCI / VJTAG = 1.5 V (per bank) Typical (25°C)    | 1.2 V / 1.5 V   | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | μA    |

| VCCI / VJTAG = 1.8 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | μA    |

| VCCI / VJTAG = 2.5 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | μA    |

| VCCI / VJTAG = 3.3 V (per bank) Typical (25°C)    | 1.2 V / 1.5 V   | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | μA    |

### Notes:

- IDD = N<sub>BANKS</sub> \* ICCI + ICCA. JTAG counts as one bank when powered.

Includes VCC, VCCPLL, and VPUMP currents.

2-8 Revision 19

Table 2-17 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices For IGLOO nano V2 Devices, 1.2 V Core Supply Voltage

|           |                                                                | [         | Device-Spe | cific Dyna | mic Power   | r (µW/MHz) | )       |  |  |

|-----------|----------------------------------------------------------------|-----------|------------|------------|-------------|------------|---------|--|--|

| Parameter | Definition                                                     | AGLN250   | AGLN125    | AGLN060    | AGLN020     | AGLN015    | AGLN010 |  |  |

| PAC1      | Clock contribution of a Global Rib                             | 2.829     | 2.875      | 1.728      | 0           | 0          | 0       |  |  |

| PAC2      | Clock contribution of a Global Spine                           | 1.731     | 1.265      | 1.268      | 2.562       | 2.562      | 1.685   |  |  |

| PAC3      | Clock contribution of a VersaTile row                          | 0.957     | 0.963      | 0.967      | 0.862       | 0.862      | 0.858   |  |  |

| PAC4      | Clock contribution of a VersaTile used as a sequential module  | 0.098     | 0.098      |            |             |            |         |  |  |

| PAC5      | First contribution of a VersaTile used as a sequential module  |           |            | 0.0        | 45          |            |         |  |  |

| PAC6      | Second contribution of a VersaTile used as a sequential module | 0.186     |            |            |             |            |         |  |  |

| PAC7      | Contribution of a VersaTile used as a combinatorial module     |           |            | 0.1        | 11          |            |         |  |  |

| PAC8      | Average contribution of a routing net                          |           |            | 0.4        | <b>1</b> 5  |            |         |  |  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)          |           | See        | Table 2-10 | 3 on page 2 | 2-9        |         |  |  |

| PAC10     | Contribution of an I/O output pin (standard-dependent)         |           | See        | Table 2-14 | 4 on page 2 | 2-9        |         |  |  |

| PAC11     | Average contribution of a RAM block during a read operation    | 25.00     |            |            |             | N/A        |         |  |  |

| PAC12     | Average contribution of a RAM block during a write operation   | 30.00 N/A |            |            |             |            |         |  |  |

| PAC13     | Dynamic contribution for PLL                                   |           | 2.10       |            |             | N/A        |         |  |  |

Table 2-18 • Different Components Contributing to the Static Power Consumption in IGLOO nano Devices For IGLOO nano V2 Devices, 1.2 V Core Supply Voltage

|                   |                                                       |                            | Device  | -Specific S | tatic Powe  | er (mW) |         |  |  |  |

|-------------------|-------------------------------------------------------|----------------------------|---------|-------------|-------------|---------|---------|--|--|--|

| Parameter         | Definition                                            | AGLN250                    | AGLN125 | AGLN060     | AGLN020     | AGLN015 | AGLN010 |  |  |  |

| PDC1              | Array static power in Active mode                     |                            | Se      | e Table 2-1 | 2 on page 2 | 2-8     |         |  |  |  |

| PDC2              | Array static power in Static (Idle) mode              | See Table 2-12 on page 2-8 |         |             |             |         |         |  |  |  |

| PDC3              | Array static power in Flash*Freeze mode               | See Table 2-9 on page 2-7  |         |             |             |         |         |  |  |  |

| PDC4 <sup>1</sup> | Static PLL contribution                               | 0.90 N/A                   |         |             |             |         |         |  |  |  |

| PDC5              | Bank quiescent power<br>(VCCI-dependent) <sup>2</sup> | See Table 2-12 on page 2-8 |         |             |             |         |         |  |  |  |

#### Notes:

- 1. Minimum contribution of the PLL when running at lowest frequency.

- 2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or the SmartPower tool in Libero SoC.

Revision 19 2-11

### Guidelines

### **Toggle Rate Definition**

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100% because all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ...

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

### **Enable Rate Definition**

Output enable rate is the average percentage of time during which tristate outputs are enabled. When nontristate output buffers are used, the enable rate should be 100%.

Table 2-19 • Toggle Rate Guidelines Recommended for Power Calculation

| Component  | ponent Definition                |     |  |  |  |  |  |  |

|------------|----------------------------------|-----|--|--|--|--|--|--|

| $\alpha_1$ | Toggle rate of VersaTile outputs |     |  |  |  |  |  |  |

| $\alpha_2$ | I/O buffer toggle rate           | 10% |  |  |  |  |  |  |

Table 2-20 • Enable Rate Guidelines Recommended for Power Calculation

| Component | Definition                           | Guideline |

|-----------|--------------------------------------|-----------|

| $\beta_1$ | I/O output buffer enable rate        | 100%      |

| $\beta_2$ | RAM enable rate for read operations  | 12.5%     |

| $\beta_3$ | RAM enable rate for write operations | 12.5%     |

2-14 Revision 19

### Applies to 1.2 V DC Core Voltage

Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 4.09            | 0.26             | 0.97            | 1.36             | 1.10              | 4.16            | 3.91            | 2.19            | 2.64            | ns    |

| 4 mA           | STD         | 1.55              | 4.09            | 0.26             | 0.97            | 1.36             | 1.10              | 4.16            | 3.91            | 2.19            | 2.64            | ns    |

| 6 mA           | STD         | 1.55              | 3.45            | 0.26             | 0.97            | 1.36             | 1.10              | 3.51            | 3.32            | 2.43            | 3.03            | ns    |

| 8 mA           | STD         | 1.55              | 3.45            | 0.26             | 0.97            | 1.36             | 1.10              | 3.51            | 3.32            | 2.43            | 3.03            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-39 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 2.68            | 0.26             | 0.97            | 1.36             | 1.10              | 2.72            | 2.26            | 2.19            | 2.74            | ns    |

| 4 mA           | STD         | 1.55              | 2.68            | 0.26             | 0.97            | 1.36             | 1.10              | 2.72            | 2.26            | 2.19            | 2.74            | ns    |

| 6 mA           | STD         | 1.55              | 2.31            | 0.26             | 0.97            | 1.36             | 1.10              | 2.34            | 1.90            | 2.43            | 3.14            | ns    |

| 8 mA           | STD         | 1.55              | 2.31            | 0.26             | 0.97            | 1.36             | 1.10              | 2.34            | 1.90            | 2.43            | 3.14            | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-28 Revision 19

### **Timing Characteristics**

## Applies to 1.5 V DC Core Voltage

Table 2-53 • 1.8 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | $t_{LZ}$ | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|----------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 5.44            | 0.19             | 1.03            | 1.44             | 0.66              | 5.25            | 5.44            | 1.69     | 1.35            | ns    |

| 4 mA           | STD         | 0.97              | 4.44            | 0.19             | 1.03            | 1.44             | 0.66              | 4.37            | 4.44            | 1.99     | 2.11            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-54 • 1.8 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

| <b>Drive Strength</b> | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-----------------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA                  | STD         | 0.97              | 2.64            | 0.19             | 1.03            | 1.44             | 0.66              | 2.59            | 2.64            | 1.69            | 1.40            | ns    |

| 4 mA                  | STD         | 0.97              | 2.08            | 0.19             | 1.03            | 1.44             | 0.66              | 2.12            | 1.95            | 1.99            | 2.19            | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Applies to 1.2 V DC Core Voltage

Table 2-55 • 1.8 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 5.92            | 0.26             | 1.13            | 1.59             | 1.10              | 5.72            | 5.92            | 2.11            | 1.95            | ns    |

| 4 mA           | STD         | 1.55              | 4.91            | 0.26             | 1.13            | 1.59             | 1.10              | 4.82            | 4.91            | 2.42            | 2.73            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-56 • 1.8 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 3.05            | 0.26             | 1.13            | 1.59             | 1.10              | 3.01            | 3.05            | 2.10            | 2.00            | ns    |

| 4 mA           | STD         | 1.55              | 2.49            | 0.26             | 1.13            | 1.59             | 1.10              | 2.53            | 2.34            | 2.42            | 2.81            | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-36 Revision 19

Table 2-71 • Parameter Definition and Measuring Nodes

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>OCLKQ</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| t <sub>OSUD</sub>     | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| toerecclr             | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

Note: \*See Figure 2-13 on page 2-43 for more information.

2-44 Revision 19

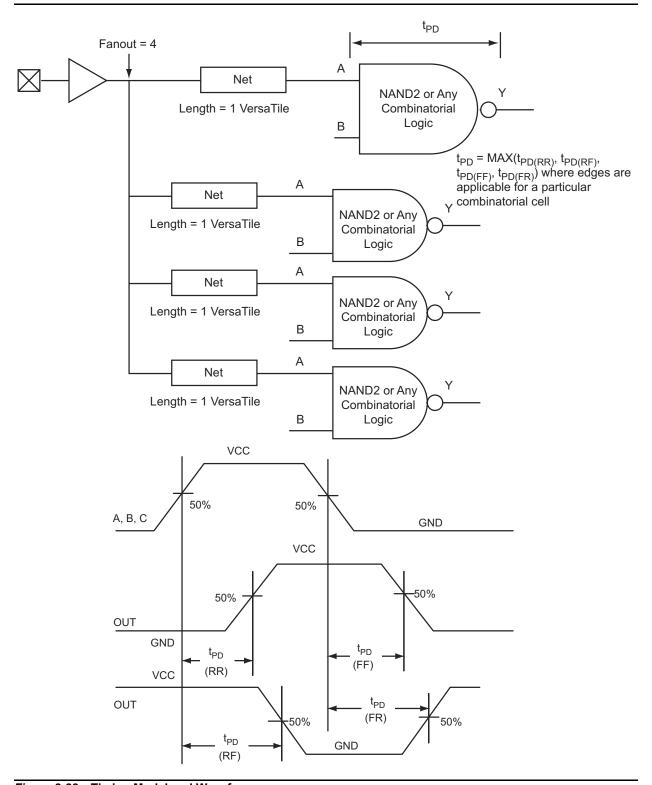

Figure 2-22 • Timing Model and Waveforms

2-58 Revision 19

# 1.2 V DC Core Voltage

Table 2-87 • Register Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 1.61 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 1.17 | ns    |

| $t_{HD}$            | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 1.29 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.87 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.89 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.24 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.24 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.46 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.46 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Core Register          | 0.95 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width LOW for the Core Register           | 0.95 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

2-62 Revision 19

# **Global Resource Characteristics**

# **AGLN125 Clock Tree Topology**

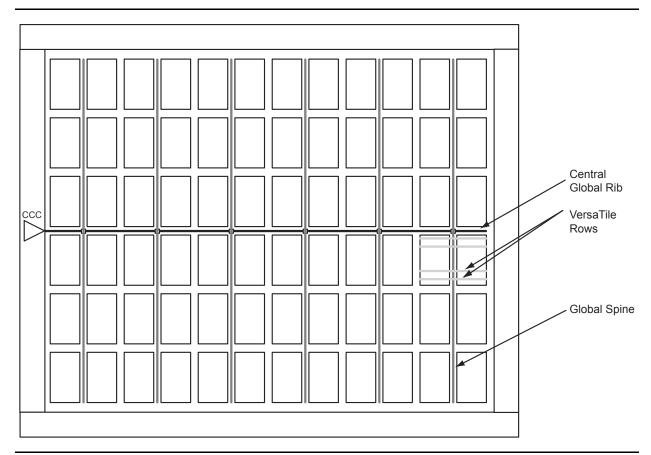

Clock delays are device-specific. Figure 2-25 is an example of a global tree used for clock routing. The global tree presented in Figure 2-25 is driven by a CCC located on the west side of the AGLN125 device. It is used to drive all D-flip-flops in the device.

Figure 2-25 • Example of Global Tree Use in an AGLN125 Device for Clock Routing

Revision 19 2-63

should be treated as a sensitive asynchronous signal. When defining pin placement and board layout, simultaneously switching outputs (SSOs) and their effects on sensitive asynchronous pins must be considered.

Unused FF or I/O pins are tristated with weak pull-up. This default configuration applies to both Flash\*Freeze mode and normal operation mode. No user intervention is required.

Table 3-1 shows the Flash\*Freeze pin location on the available packages for IGLOO nano devices. The Flash\*Freeze pin location is independent of device (except for a PQ208 package), allowing migration to larger or smaller IGLOO nano devices while maintaining the same pin location on the board. Refer to the "Flash\*Freeze Technology and Low Power Modes" chapter of the IGLOO nano FPGA Fabric User's Guide for more information on I/O states during Flash\*Freeze mode.

Table 3-1 • Flash\*Freeze Pin Locations for IGLOO nano Devices

| Package   | Flash*Freeze Pin |

|-----------|------------------|

| CS81/UC81 | H2               |

| QN48      | 14               |

| QN68      | 18               |

| VQ100     | 27               |

| UC36      | E2               |

# **JTAG Pins**

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the part must be supplied to allow JTAG signals to transition the device. Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND.

### TCK Test Clock

Test clock input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pull-up/-down resistor. If JTAG is not used, Microsemi recommends tying off TCK to GND through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements. Refer to Table 3-2 for more information.

Table 3-2 • Recommended Tie-Off Values for the TCK and TRST Pins

| VJTAG          | Tie-Off Resistance 1,2       |

|----------------|------------------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ                |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ                |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ                |

| VJTAG at 1.5 V | 500 $\Omega$ to 1 k $\Omega$ |

### Notes:

- 1. The TCK pin can be pulled-up or pulled-down.

- 2. The TRST pin is pulled-down.

- 3. Equivalent parallel resistance if more than one device is on the JTAG chain

Revision 19 3-3

Pin Descriptions

Table 3-3 • TRST and TCK Pull-Down Recommendations

| VJTAG          | Tie-Off Resistance* |

|----------------|---------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ       |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ       |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ       |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ       |

Note: Equivalent parallel resistance if more than one device is on the JTAG chain

### TDI Test Data Input

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

### TDO Test Data Output

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

### TMS Test Mode Select

The TMS pin controls the use of the IEEE 1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

### TRST Boundary Scan Reset Pin

The TRST pin functions as an active-low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the test access port (TAP) is held in reset mode. The resistor values must be chosen from Table 3-2 and must satisfy the parallel resistance value requirement. The values in Table 3-2 correspond to the resistor recommended when a single device is used, and the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entrance to an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

# **Special Function Pins**

#### NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

# **Packaging**

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Microsemi offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

3-4 Revision 19

| UC36       |                     |  |  |  |  |  |

|------------|---------------------|--|--|--|--|--|

| Pin Number | AGLN010<br>Function |  |  |  |  |  |

| A1         | IO21RSB1            |  |  |  |  |  |

| A2         | IO18RSB1            |  |  |  |  |  |

| A3         | IO13RSB1            |  |  |  |  |  |

| A4         | GDC0/IO00RSB0       |  |  |  |  |  |

| A5         | IO06RSB0            |  |  |  |  |  |

| A6         | GDA0/IO04RSB0       |  |  |  |  |  |

| B1         | GEC0/IO37RSB1       |  |  |  |  |  |

| B2         | IO20RSB1            |  |  |  |  |  |

| В3         | IO15RSB1            |  |  |  |  |  |

| B4         | IO09RSB0            |  |  |  |  |  |

| B5         | IO08RSB0            |  |  |  |  |  |

| B6         | IO07RSB0            |  |  |  |  |  |

| C1         | IO22RSB1            |  |  |  |  |  |

| C2         | GEA0/IO34RSB1       |  |  |  |  |  |

| C3         | GND                 |  |  |  |  |  |

| C4         | GND                 |  |  |  |  |  |

| C5         | VCCIB0              |  |  |  |  |  |

| C6         | IO02RSB0            |  |  |  |  |  |

| D1         | IO33RSB1            |  |  |  |  |  |

| D2         | VCCIB1              |  |  |  |  |  |

| D3         | VCC                 |  |  |  |  |  |

| D4         | VCC                 |  |  |  |  |  |

| D5         | IO10RSB0            |  |  |  |  |  |

| D6         | IO11RSB0            |  |  |  |  |  |

| E1         | IO32RSB1            |  |  |  |  |  |

| E2         | FF/IO31RSB1         |  |  |  |  |  |

| E3         | TCK                 |  |  |  |  |  |

| E4         | VPUMP               |  |  |  |  |  |

| E5         | TRST                |  |  |  |  |  |

| E6         | VJTAG               |  |  |  |  |  |

| F1         | IO29RSB1            |  |  |  |  |  |

| F2         | IO25RSB1            |  |  |  |  |  |

| F3         | IO23RSB1            |  |  |  |  |  |

| F4         | TDI                 |  |  |  |  |  |

| UC36       |                     |  |  |  |

|------------|---------------------|--|--|--|

| Pin Number | AGLN010<br>Function |  |  |  |

| F5         | TMS                 |  |  |  |

| F6         | TDO                 |  |  |  |

4-2 Revision 19

|            | CS81              |

|------------|-------------------|

| Pin Number | AGLN250Z Function |

| A1         | GAA0/IO00RSB0     |

| A2         | GAA1/IO01RSB0     |

| A3         | GAC0/IO04RSB0     |

| A4         | IO07RSB0          |

| A5         | IO09RSB0          |

| A6         | IO12RSB0          |

| A7         | GBB0/IO16RSB0     |

| A8         | GBA1/IO19RSB0     |

| A9         | GBA2/IO20RSB1     |

| B1         | GAA2/IO67RSB3     |

| B2         | GAB0/IO02RSB0     |

| В3         | GAC1/IO05RSB0     |

| B4         | IO06RSB0          |

| B5         | IO10RSB0          |

| B6         | GBC0/IO14RSB0     |

| В7         | GBB1/IO17RSB0     |

| B8         | IO21RSB1          |

| В9         | GBB2/IO22RSB1     |

| C1         | GAB2/IO65RSB3     |

| C2         | IO66RSB3          |

| C3         | GND               |

| C4         | IO08RSB0          |

| C5         | IO11RSB0          |

| C6         | GND               |

| C7         | GBA0/IO18RSB0     |

| C8         | GBC2/IO23RSB1     |

| C9         | IO24RSB1          |

| D1         | GAC2/IO63RSB3     |

| D2         | IO64RSB3          |

| D3         | GFA2/IO56RSB3     |

| D4         | VCC               |

| D5         | VCCIB0            |

| D6         | GND               |

| D7         | IO30RSB1          |

| D8         | GCC1/IO25RSB1     |

| D9         | GCC0/IO26RSB1     |

|            | CS81              |

|------------|-------------------|

| Pin Number | AGLN250Z Function |

| E1         | GFB0/IO59RSB3     |

| E2         | GFB1/IO60RSB3     |

| E3         | GFA1/IO58RSB3     |

| E4         | VCCIB3            |

| E5         | VCC               |

| E6         | VCCIB1            |

| E7         | GCA0/IO28RSB1     |

| E8         | GCA1/IO27RSB1     |

| E9         | GCB2/IO29RSB1     |

| F1*        | VCCPLF            |

| F2*        | VCOMPLF           |

| F3         | GND               |

| F4         | GND               |

| F5         | VCCIB2            |

| F6         | GND               |

| F7         | GDA1/IO33RSB1     |

| F8         | GDC1/IO31RSB1     |

| F9         | GDC0/IO32RSB1     |

| G1         | GEA0/IO51RSB3     |

| G2         | GEC1/IO54RSB3     |

| G3         | GEC0/IO53RSB3     |

| G4         | IO45RSB2          |

| G5         | IO42RSB2          |

| G6         | IO37RSB2          |

| G7         | GDB2/IO35RSB2     |

| G8         | VJTAG             |

| G9         | TRST              |

| H1         | GEA1/IO52RSB3     |

| H2         | FF/GEB2/IO49RSB2  |

| H3         | IO47RSB2          |

| H4         | IO44RSB2          |

| H5         | IO41RSB2          |

| H6         | IO39RSB2          |

| H7         | GDA2/IO34RSB2     |

| H8         | TDI               |

| H9         | TDO               |

| CS81       |                   |  |

|------------|-------------------|--|

| Pin Number | AGLN250Z Function |  |

| J1         | GEA2/IO50RSB2     |  |

| J2         | GEC2/IO48RSB2     |  |

| J3         | IO46RSB2          |  |

| J4         | IO43RSB2          |  |

| J5         | IO40RSB2          |  |

| J6         | IO38RSB2          |  |

| J7         | TCK               |  |

| J8         | TMS               |  |

| J9         | VPUMP             |  |

Note: \* Pin numbers F1 and F2 must be connected to ground because a PLL is not supported for AGLN250Z-CS81.

4-14 Revision 19

|            | VQ100            | VQ100      |                  |

|------------|------------------|------------|------------------|

| Pin Number | AGLN060 Function | Pin Number | AGLN060 Function |

| 1          | GND              | 36         | IO61RSB1         |

| 2          | GAA2/IO51RSB1    | 37         | VCC              |

| 3          | IO52RSB1         | 38         | GND              |

| 4          | GAB2/IO53RSB1    | 39         | VCCIB1           |

| 5          | IO95RSB1         | 40         | IO60RSB1         |

| 6          | GAC2/IO94RSB1    | 41         | IO59RSB1         |

| 7          | IO93RSB1         | 42         | IO58RSB1         |

| 8          | IO92RSB1         | 43         | IO57RSB1         |

| 9          | GND              | 44         | GDC2/IO56RSB1    |

| 10         | GFB1/IO87RSB1    | 45*        | GDB2/IO55RSB1    |

| 11         | GFB0/IO86RSB1    | 46         | GDA2/IO54RSB1    |

| 12         | VCOMPLF          | 47         | TCK              |

| 13         | GFA0/IO85RSB1    | 48         | TDI              |

| 14         | VCCPLF           | 49         | TMS              |

| 15         | GFA1/IO84RSB1    | 50         | VMV1             |

| 16         | GFA2/IO83RSB1    | 51         | GND              |

| 17         | VCC              | 52         | VPUMP            |

| 18         | VCCIB1           | 53         | NC               |

| 19         | GEC1/IO77RSB1    | 54         | TDO              |

| 20         | GEB1/IO75RSB1    | 55         | TRST             |

| 21         | GEB0/IO74RSB1    | 56         | VJTAG            |

| 22         | GEA1/IO73RSB1    | 57         | GDA1/IO49RSB0    |

| 23         | GEA0/IO72RSB1    | 58         | GDC0/IO46RSB0    |

| 24         | VMV1             | 59         | GDC1/IO45RSB0    |

| 25         | GNDQ             | 60         | GCC2/IO43RSB0    |

| 26         | GEA2/IO71RSB1    | 61         | GCB2/IO42RSB0    |

| 27         | FF/GEB2/IO70RSB1 | 62         | GCA0/IO40RSB0    |

| 28         | GEC2/IO69RSB1    | 63         | GCA1/IO39RSB0    |

| 29         | IO68RSB1         | 64         | GCC0/IO36RSB0    |

| 30         | IO67RSB1         | 65         | GCC1/IO35RSB0    |

| 31         | IO66RSB1         | 66         | VCCIB0           |

| 32         | IO65RSB1         | 67         | GND              |

| 33         | IO64RSB1         | 68         | VCC              |

| 34         | IO63RSB1         | 69         | IO31RSB0         |

| 35         | IO62RSB1         | 70         | GBC2/IO29RSB0    |

| VQ100      |                  |  |

|------------|------------------|--|

| Pin Number | AGLN060 Function |  |

| 71         | GBB2/IO27RSB0    |  |

| 72         | IO26RSB0         |  |

| 73         | GBA2/IO25RSB0    |  |

| 74         | VMV0             |  |

| 75         | GNDQ             |  |

| 76         | GBA1/IO24RSB0    |  |

| 77         | GBA0/IO23RSB0    |  |

| 78         | GBB1/IO22RSB0    |  |

| 79         | GBB0/IO21RSB0    |  |

| 80         | GBC1/IO20RSB0    |  |

| 81         | GBC0/IO19RSB0    |  |

| 82         | IO18RSB0         |  |

| 83         | IO17RSB0         |  |

| 84         | IO15RSB0         |  |

| 85         | IO13RSB0         |  |

| 86         | IO11RSB0         |  |

| 87         | VCCIB0           |  |

| 88         | GND              |  |

| 89         | VCC              |  |

| 90         | IO10RSB0         |  |

| 91         | IO09RSB0         |  |

| 92         | IO08RSB0         |  |

| 93         | GAC1/IO07RSB0    |  |

| 94         | GAC0/IO06RSB0    |  |

| 95         | GAB1/IO05RSB0    |  |

| 96         | GAB0/IO04RSB0    |  |

| 97         | GAA1/IO03RSB0    |  |

| 98         | GAA0/IO02RSB0    |  |

| 99         | IO01RSB0         |  |

| 100        | IO00RSB0         |  |

Note: \*The bus hold attribute (hold previous I/O state in Flash\*Freeze mode) is not supported for pin 45 in AGLN060-VQ100.

4-24 Revision 19

| VQ100      |                   |  |

|------------|-------------------|--|

| Pin Number | AGLN125 Function  |  |

| 1          | GND               |  |

| 2          | GAA2/IO67RSB1     |  |

| 3          | IO68RSB1          |  |

| 4          | GAB2/IO69RSB1     |  |

| 5          | IO132RSB1         |  |

| 6          | GAC2/IO131RSB1    |  |

| 7          | IO130RSB1         |  |

| 8          | IO129RSB1         |  |

| 9          | GND               |  |

| 10         | GFB1/IO124RSB1    |  |

| 11         | GFB0/IO123RSB1    |  |

| 12         | VCOMPLF           |  |

| 13         | GFA0/IO122RSB1    |  |

| 14         | VCCPLF            |  |

| 15         | GFA1/IO121RSB1    |  |

| 16         | GFA2/IO120RSB1    |  |

| 17         | VCC               |  |

| 18         | VCCIB1            |  |

| 19         | GEC0/IO111RSB1    |  |

| 20         | GEB1/IO110RSB1    |  |

| 21         | GEB0/IO109RSB1    |  |

| 22         | GEA1/IO108RSB1    |  |

| 23         | GEA0/IO107RSB1    |  |

| 24         | VMV1              |  |

| 25         | GNDQ              |  |

| 26         | GEA2/IO106RSB1    |  |

| 27         | FF/GEB2/IO105RSB1 |  |

| 28         | GEC2/IO104RSB1    |  |

| 29         | IO102RSB1         |  |

| 30         | IO100RSB1         |  |

| 31         | IO99RSB1          |  |

| 32         | IO97RSB1          |  |

| 33         | IO96RSB1          |  |

| 34         | IO95RSB1          |  |

| 35         | IO94RSB1          |  |

| 36         | IO93RSB1          |  |

| VQ100      |                  |  |

|------------|------------------|--|

| Pin Number | AGLN125 Function |  |

| 37         | VCC              |  |

| 38         | GND              |  |

| 39         | VCCIB1           |  |

| 40         | IO87RSB1         |  |

| 41         | IO84RSB1         |  |

| 42         | IO81RSB1         |  |

| 43         | IO75RSB1         |  |

| 44         | GDC2/IO72RSB1    |  |

| 45         | GDB2/IO71RSB1    |  |

| 46         | GDA2/IO70RSB1    |  |

| 47         | TCK              |  |

| 48         | TDI              |  |

| 49         | TMS              |  |

| 50         | VMV1             |  |

| 51         | GND              |  |

| 52         | VPUMP            |  |

| 53         | NC               |  |

| 54         | TDO              |  |

| 55         | TRST             |  |

| 56         | VJTAG            |  |

| 57         | GDA1/IO65RSB0    |  |

| 58         | GDC0/IO62RSB0    |  |

| 59         | GDC1/IO61RSB0    |  |

| 60         | GCC2/IO59RSB0    |  |

| 61         | GCB2/IO58RSB0    |  |

| 62         | GCA0/IO56RSB0    |  |

| 63         | GCA1/IO55RSB0    |  |

| 64         | GCC0/IO52RSB0    |  |

| 65         | GCC1/IO51RSB0    |  |

| 66         | VCCIB0           |  |

| 67         | GND              |  |

| 68         | VCC              |  |

| 69         | IO47RSB0         |  |

| 70         | GBC2/IO45RSB0    |  |

| 71         | GBB2/IO43RSB0    |  |

| 72         | IO42RSB0         |  |

|            |                  |  |

| VQ100      |                  |  |

|------------|------------------|--|

| Pin Number | AGLN125 Function |  |

| 73         | GBA2/IO41RSB0    |  |

| 74         | VMV0             |  |

| 75         | GNDQ             |  |

| 76         | GBA1/IO40RSB0    |  |

| 77         | GBA0/IO39RSB0    |  |

| 78         | GBB1/IO38RSB0    |  |

| 79         | GBB0/IO37RSB0    |  |

| 80         | GBC1/IO36RSB0    |  |

| 81         | GBC0/IO35RSB0    |  |

| 82         | IO32RSB0         |  |

| 83         | IO28RSB0         |  |

| 84         | IO25RSB0         |  |

| 85         | IO22RSB0         |  |

| 86         | IO19RSB0         |  |

| 87         | VCCIB0           |  |

| 88         | GND              |  |

| 89         | VCC              |  |

| 90         | IO15RSB0         |  |

| 91         | IO13RSB0         |  |

| 92         | IO11RSB0         |  |

| 93         | IO09RSB0         |  |

| 94         | IO07RSB0         |  |

| 95         | GAC1/IO05RSB0    |  |

| 96         | GAC0/IO04RSB0    |  |

| 97         | GAB1/IO03RSB0    |  |

| 98         | GAB0/IO02RSB0    |  |

| 99         | GAA1/IO01RSB0    |  |

| 100        | GAA0/IO00RSB0    |  |

4-26 Revision 19

# IGLOO nano Low Power Flash FPGAs

| Revision                  | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page        |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Revision 11<br>(Jul 2010) | The status of the AGLN060 device has changed from Advance to Production.                                                                                                                                                                                                                                                                                                                                                                          | III         |

|                           | The values for PAC1, PAC2, PAC3, and PAC4 were updated in Table 2-15 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices for 1.5 V core supply voltage (SAR 26404).                                                                                                                                                                                                                                            | 2-10        |

|                           | The values for PAC1, PAC2, PAC3, and PAC4 were updated in Table 2-17 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices for 1.2 V core supply voltage (SAR 26404).                                                                                                                                                                                                                                            | 2-11        |

| July 2010                 | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "IGLOO nano Device Status" table on page III indicates the status for each device in the device family.                                                                                                                                                                                  | N/A         |

| Revision 10<br>(Apr 2010) | References to differential inputs were removed from the datasheet, since IGLOO nano devices do not support differential inputs (SAR 21449).                                                                                                                                                                                                                                                                                                       | N/A         |

|                           | A parenthetical note, "hold previous I/O state in Flash*Freeze mode," was added to each occurrence of bus hold in the datasheet (SAR 24079).                                                                                                                                                                                                                                                                                                      | N/A         |

|                           | The "In-System Programming (ISP) and Security" section was revised to add 1.2 V programming.                                                                                                                                                                                                                                                                                                                                                      | I           |

|                           | The note connected with the "IGLOO nano Ordering Information" table was revised to clarify features not available for Z feature grade devices.                                                                                                                                                                                                                                                                                                    | IV          |

|                           | The "IGLOO nano Device Status" table is new.                                                                                                                                                                                                                                                                                                                                                                                                      | III         |

|                           | The definition of C in the "Temperature Grade Offerings" table was changed to "extended commercial temperature range".                                                                                                                                                                                                                                                                                                                            | VI          |

|                           | 1.2 V wide range was added to the list of voltage ranges in the "I/Os with Advanced I/O Standards" section.                                                                                                                                                                                                                                                                                                                                       | 1-8         |

|                           | A note was added to Table 2-2 • Recommended Operating Conditions <sup>1</sup> regarding switching from 1.2 V to 1.5 V core voltage for in-system programming. The VJTAG voltage was changed from "1.425 to 3.6" to "1.4 to 3.6" (SAR 24052). The note regarding voltage for programming V2 and V5 devices was revised (SAR 25213). The maximum value for VPUMP programming voltage (operation mode) was changed from 3.45 V to 3.6 V (SAR 25220). | 2-2         |

|                           | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = 70°C, VCC = 1.425 V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = 70°C, VCC = 1.14 V) were updated. Table 2-8 • Power Supply State per Mode is new.                                                                                                                                                  | 2-6,<br>2-7 |

|                           | The tables in the "Quiescent Supply Current" section were updated (SAR 24882 and SAR 24112).                                                                                                                                                                                                                                                                                                                                                      | 2-7         |

|                           | VJTAG was removed from Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Sleep Mode* (SARs 24112, 24882, and 79503).                                                                                                                                                                                                                                                                                                        | 2-8         |

|                           | The note stating what was included in $I_{DD}$ was removed from Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Shutdown Mode. The note, "per VCCI or VJTAG bank" was removed from Table 2-12 • Quiescent Supply Current (IDD), No IGLOO nano Flash*Freeze Mode <sup>1</sup> . The note giving $I_{DD}$ was changed to " $I_{DD} = N_{BANKS} * I_{CCI} + I_{CCA}$ ."                                                      | 2-8         |

|                           | The values in Table 2-13 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings and Table 2-14 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings <sup>1</sup> were updated. Wide range support information was added.                                                                                                                                                                         | 2-9         |

Revision 19 5-3

# Datasheet Information

| Revision                | Changes                                                                                                                                                                                                                         | Page                    |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Revision 10 (continued) | The following tables were updated with current available information. The equivalent software default drive strength option was added.                                                                                          | 2-19<br>through         |

|                         | Table 2-21 • Summary of Maximum and Minimum DC Input and Output Levels                                                                                                                                                          | 2-40                    |

|                         | Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings                                                                                                                                                    |                         |

|                         | Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings                                                                                                                                                    |                         |

|                         | Table 2-28 • I/O Output Buffer Maximum Resistances <sup>1</sup>                                                                                                                                                                 |                         |

|                         | Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances                                                                                                                                                                             |                         |

|                         | Table 2-30 • I/O Short Currents IOSH/IOSL                                                                                                                                                                                       |                         |

|                         | Timing tables in the "Single-Ended I/O Characteristics" section, including new tables for 3.3 V and 1.2 V LVCMOS wide range.                                                                                                    |                         |

|                         | Table 2-40 • Minimum and Maximum DC Input and Output Levels for LVCMOS 3.3 V Wide Range                                                                                                                                         |                         |

|                         | Table 2-63 • Minimum and Maximum DC Input and Output Levels                                                                                                                                                                     |                         |

|                         | Table 2-67 • Minimum and Maximum DC Input and Output Levels (new)                                                                                                                                                               |                         |

|                         | The formulas in the notes to Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances were revised (SAR 21348).                                                                                                                      | 2-24                    |

|                         | The text introducing Table 2-31 • Duration of Short Circuit Event before Failure was revised to state six months at 100° instead of three months at 110° for reliability concerns. The row for 110° was removed from the table. | 2-25                    |

|                         | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 24916): "It uses a 5-V tolerant input buffer and push-pull output buffer."                                                                              | 2-32                    |

|                         | The $F_{DDRIMAX}$ and $F_{DDOMAX}$ values were added to tables in the "DDR Module Specifications" section (SAR 23919). A note was added stating that DDR is not supported for AGLN010, AGLN015, and AGLN020.                    | 2-51                    |

|                         | Tables in the "Global Tree Timing Characteristics" section were updated with new information available.                                                                                                                         | 2-64                    |

|                         | Table 2-100 • IGLOO nano CCC/PLL Specification and Table 2-101 • IGLOO nano CCC/PLL Specification were revised (SAR 79390).                                                                                                     | 2-70,<br>2-71           |

|                         | Tables in the SRAM "Timing Characteristics" section and FIFO "Timing Characteristics" section were updated with new information available.                                                                                      | 2-77,<br>2-85           |

|                         | Table 3-3 • TRST and TCK Pull-Down Recommendations is new.                                                                                                                                                                      | 3-4                     |

|                         | A note was added to the "CS81" pin tables for AGLN060, AGLN060Z, AGLN125, AGLN125Z, AGLN250, and AGLN250Z indicating that pins F1 and F2 must be grounded (SAR 25007).                                                          | 4-9,<br>through<br>4-14 |

|                         | A note was added to the "CS81" and "VQ100" pin tables for AGLN060 and AGLN060Z stating that bus hold is not available for pin H7 or pin 45 (SAR 24079).                                                                         | 4-9,<br>4-24            |

|                         | The AGLN250 function for pin C8 in the "CS81" table was revised (SAR 22134).                                                                                                                                                    | 4-13                    |

5-4 Revision 19

**Microsemi Corporate Headquarters** One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail:

sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.