Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 6144                                                                        |

| Total RAM Bits                 | 36864                                                                       |

| Number of I/O                  | 60                                                                          |

| Number of Gates                | 250000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 81-WFBGA, CSBGA                                                             |

| Supplier Device Package        | 81-CSP (5x5)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln250v5-zcsg81i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **IGLOO** nano Device Status

| IGLOO nano Devices | Status                           | IGLOO nano-Z Devices | Status                           |

|--------------------|----------------------------------|----------------------|----------------------------------|

| AGLN010            | Production                       |                      |                                  |

| AGLN015            | Not recommended for new designs. |                      |                                  |

| AGLN020            | Production                       |                      |                                  |

|                    |                                  | AGLN030Z             | Not recommended for new designs. |

| AGLN060            | Production                       | AGLN060Z             | Not recommended for new designs. |

| AGLN125            | Production                       | AGLN125Z             | Not recommended for new designs. |

| AGLN250            | Production                       | AGLN250Z             | Not recommended for new designs. |

Revision 19

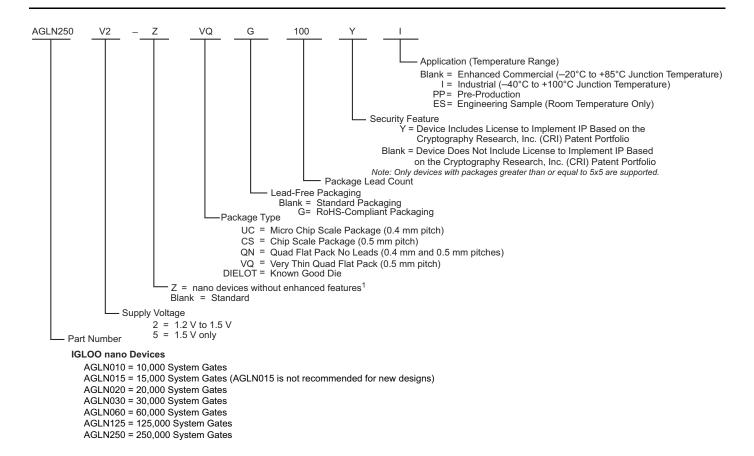

# **IGLOO** nano Ordering Information

#### Notes:

- Z-feature grade devices AGLN060Z, AGLN125Z, and AGLN250Z do not support the enhanced nano features of Schmitt Trigger input, bus hold (hold previous I/O state in Flash\*Freeze mode), cold-sparing, hot-swap I/O capability and 1.2 V programming. The AGLN030 Z feature grade does not support Schmitt trigger input, bus hold and 1.2 V programming. For the VQ100, CS81, UC81, QN68, and QN48 packages, the Z feature grade and the N part number are not marked on the device. Z feature grade devices are not recommended for new designs.

- AGLN030 is available in the Z feature grade only.

- 3. Marking Information: IGLOO nano V2 devices do not have a V2 marking, but IGLOO nano V5 devices are marked with a V5 designator.

# **Devices Not Recommended For New Designs**

AGLN015, AGLN030Z, AGLN060Z, AGLN125Z, and AGLN250Z are not recommended for new designs. For more information on obsoleted devices/packages, refer to the *PDN1503 - IGLOO nano Z and ProASIC3 nano Z Families*.

IV Revision 19

Table 2-2 • Recommended Operating Conditions 1

| Symbol              | P                       | arameter                                                | Extended<br>Commercial  | Industrial               | Units |

|---------------------|-------------------------|---------------------------------------------------------|-------------------------|--------------------------|-------|

| T <sub>J</sub>      | Junction temperature    |                                                         | $-20 \text{ to} + 85^2$ | -40 to +100 <sup>2</sup> | °C    |

| VCC                 | 1.5 V DC core supply vo | oltage <sup>3</sup>                                     | 1.425 to 1.575          | 1.425 to 1.575           | V     |

|                     | 1.2 V–1.5 V wide range  | core voltage <sup>4,5</sup>                             | 1.14 to 1.575           | 1.14 to 1.575            | V     |

| VJTAG               | JTAG DC voltage         |                                                         | 1.4 to 3.6              | 1.4 to 3.6               | V     |

| VPUMP <sup>6</sup>  | Programming voltage     | gramming voltage Programming mode                       |                         | 3.15 to 3.45             | V     |

|                     |                         | Operation                                               | 0 to 3.6                | 0 to 3.6                 | V     |

| VCCPLL <sup>7</sup> | Analog power supply     | power supply 1.5 V DC core supply voltage <sup>3</sup>  |                         | 1.425 to 1.575           | V     |

|                     | (PLL)                   | 1.2 V–1.5 V wide range core supply voltage <sup>4</sup> | 1.14 to 1.575           | 1.14 to 1.575            | V     |

| VCCI and            | 1.2 V DC supply voltage | ,4                                                      | 1.14 to 1.26            | 1.14 to 1.26             | V     |

| VMV <sup>8,9</sup>  | 1.2 V DC wide range su  | pply voltage <sup>4</sup>                               | 1.14 to 1.575           | 1.14 to 1.575            | V     |

|                     | 1.5 V DC supply voltage | •                                                       | 1.425 to 1.575          | 1.425 to 1.575           | V     |

|                     | 1.8 V DC supply voltage |                                                         | 1.7 to 1.9              | 1.7 to 1.9               | V     |

|                     | 2.5 V DC supply voltage |                                                         | 2.3 to 2.7              | 2.3 to 2.7               | V     |

|                     | 3.3 V DC supply voltage | •                                                       | 3.0 to 3.6 3.0 to 3.6   |                          | V     |

|                     | 3.3 V DC wide range su  | pply voltage <sup>10</sup>                              | 2.7 to 3.6              | 2.7 to 3.6               | V     |

#### Notes:

- 1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 2. Default Junction Temperature Range in the Libero SoC software is set to 0°C to +70°C for commercial, and -40°C to +85°C for industrial. To ensure targeted reliability standards are met across the full range of junction temperatures, Microsemi recommends using custom settings for temperature range before running timing and power analysis tools. For more information regarding custom settings, refer to the New Project Dialog Box in the Libero Online Help.

- 3. For IGLOO® nano V5 devices

- 4. For IGLOO nano V2 devices only, operating at VCCI ≥ VCC

- 5. IGLOO nano V5 devices can be programmed with the VCC core voltage at 1.5 V only. IGLOO nano V2 devices can be programmed with the VCC core voltage at 1.2 V (with FlashPro4 only) or 1.5 V. If you are using FlashPro3 and want to do in-system programming using 1.2 V, please contact the factory.

- 6.  $V_{PUMP}$  can be left floating during operation (not programming mode).

- 7. VCCPLL pins should be tied to VCC pins. See the "Pin Descriptions" chapter for further information.

- 8. VMV pins must be connected to the corresponding VCCI pins. See the Pin Descriptions chapter of the IGLOO nano FPGA Fabric User's Guide for further information.

- 9. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-21 on page 2-19. VCCI should be at the same voltage within a given I/O bank.

- 10. 3.3 V wide range is compliant to the JESD8-B specification and supports 3.0 V VCCI operation.

Table 2-3 • Flash Programming Limits – Retention, Storage, and Operating Temperature<sup>1</sup>

| Product<br>Grade |     | Program Retention (biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) <sup>2</sup> | Maximum Operating Junction Temperature T <sub>J</sub> (°C) <sup>2</sup> |

|------------------|-----|-------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|

| Commercial       | 500 | 20 years                            | 110                                                               | 100                                                                     |

| Industrial       | 500 | 20 years                            | 110                                                               | 100                                                                     |

#### Notes:

- 1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

- These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

2-2 Revision 19

Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to  $T_J$  = 70°C, VCC = 1.14 V)

For IGLOO nano V2, 1.2 V DC Core Supply Voltage

| Array Voltage<br>VCC (V) |       | Junction Temperature (°C) |       |       |       |       |       |  |  |  |  |  |  |

|--------------------------|-------|---------------------------|-------|-------|-------|-------|-------|--|--|--|--|--|--|

|                          | -40°C | -20°C                     | 0°C   | 25°C  | 70°C  | 85°C  | 100°C |  |  |  |  |  |  |

| 1.14                     | 0.968 | 0.974                     | 0.979 | 0.991 | 1.000 | 1.006 | 1.009 |  |  |  |  |  |  |

| 1.2                      | 0.863 | 0.868                     | 0.873 | 0.884 | 0.892 | 0.898 | 0.901 |  |  |  |  |  |  |

| 1.26                     | 0.792 | 0.797                     | 0.801 | 0.811 | 0.819 | 0.824 | 0.827 |  |  |  |  |  |  |

# **Calculating Power Dissipation**

# **Quiescent Supply Current**

Quiescent supply current (IDD) calculation depends on multiple factors, including operating voltages (VCC, VCCI, and VJTAG), operating temperature, system clock frequency, and power mode usage. Microsemi recommends using the Power Calculator and SmartPower software estimation tools to evaluate the projected static and active power based on the user design, power mode usage, operating voltage, and temperature.

Table 2-8 • Power Supply State per Mode

|                      |     | Power Supply Configurations |      |       |                 |  |  |  |  |  |  |  |

|----------------------|-----|-----------------------------|------|-------|-----------------|--|--|--|--|--|--|--|

| Modes/Power Supplies | VCC | VCCPLL                      | VCCI | VJTAG | VPUMP           |  |  |  |  |  |  |  |

| Flash*Freeze         | On  | On                          | On   | On    | On/off/floating |  |  |  |  |  |  |  |

| Sleep                | Off | Off                         | On   | Off   | Off             |  |  |  |  |  |  |  |

| Shutdown             | Off | Off                         | Off  | Off   | Off             |  |  |  |  |  |  |  |

| No Flash*Freeze      | On  | On                          | On   | On    | On/off/floating |  |  |  |  |  |  |  |

Note: Off: Power Supply level = 0 V

Table 2-9 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Flash\*Freeze Mode\*

|                | Core<br>Voltage | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|----------------|-----------------|---------|---------|---------|---------|---------|---------|-------|

| Typical (25°C) | 1.2 V           | 1.9     | 3.3     | 3.3     | 8       | 13      | 20      | μΑ    |

|                | 1.5 V           | 5.8     | 6       | 6       | 10      | 18      | 34      | μA    |

Note: \*IDD includes VCC, VPUMP, VCCI, VCCPLL, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-9 through Table 2-14 on page 2-9 and Table 2-15 on page 2-10 through Table 2-18 on page 2-11 (PDC6 and PDC7).

Table 2-17 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices For IGLOO nano V2 Devices, 1.2 V Core Supply Voltage

|           |                                                                | [         | Device-Spe | cific Dyna | mic Power   | r (µW/MHz) | )       |  |

|-----------|----------------------------------------------------------------|-----------|------------|------------|-------------|------------|---------|--|

| Parameter | Definition                                                     | AGLN250   | AGLN125    | AGLN060    | AGLN020     | AGLN015    | AGLN010 |  |

| PAC1      | Clock contribution of a Global Rib                             | 2.829     | 2.875      | 1.728      | 0           | 0          | 0       |  |

| PAC2      | Clock contribution of a Global Spine                           | 1.731     | 1.265      | 1.268      | 2.562       | 2.562      | 1.685   |  |

| PAC3      | Clock contribution of a VersaTile row                          | 0.957     | 0.963      | 0.967      | 0.862       | 0.862      | 0.858   |  |

| PAC4      | Clock contribution of a VersaTile used as a sequential module  | 0.098     | 0.098      | 0.098      | 0.094       | 0.094      | 0.091   |  |

| PAC5      | First contribution of a VersaTile used as a sequential module  | 0.045     |            |            |             |            |         |  |

| PAC6      | Second contribution of a VersaTile used as a sequential module | e 0.186   |            |            |             |            |         |  |

| PAC7      | Contribution of a VersaTile used as a combinatorial module     |           |            | 0.1        | 11          |            |         |  |

| PAC8      | Average contribution of a routing net                          |           |            | 0.4        | <b>1</b> 5  |            |         |  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)          |           | See        | Table 2-10 | 3 on page 2 | 2-9        |         |  |

| PAC10     | Contribution of an I/O output pin (standard-dependent)         |           | See        | Table 2-14 | 4 on page 2 | 2-9        |         |  |

| PAC11     | Average contribution of a RAM block during a read operation    |           | 25.00      | N/A        |             |            |         |  |

| PAC12     | Average contribution of a RAM block during a write operation   | 30.00 N/A |            |            |             | N/A        |         |  |

| PAC13     | Dynamic contribution for PLL                                   |           | 2.10       |            |             | N/A        |         |  |

Table 2-18 • Different Components Contributing to the Static Power Consumption in IGLOO nano Devices For IGLOO nano V2 Devices, 1.2 V Core Supply Voltage

|                   |                                                       |          | Device                     | -Specific S | tatic Powe | er (mW) |  |  |  |

|-------------------|-------------------------------------------------------|----------|----------------------------|-------------|------------|---------|--|--|--|

| Parameter         | Definition                                            | AGLN250  | AGLN125                    | AGLN015     | AGLN010    |         |  |  |  |

| PDC1              | Array static power in Active mode                     |          | See Table 2-12 on page 2-8 |             |            |         |  |  |  |

| PDC2              | Array static power in Static (Idle) mode              |          | See Table 2-12 on page 2-8 |             |            |         |  |  |  |

| PDC3              | Array static power in Flash*Freeze mode               |          | See Table 2-9 on page 2-7  |             |            |         |  |  |  |

| PDC4 <sup>1</sup> | Static PLL contribution                               | 0.90 N/A |                            |             |            |         |  |  |  |

| PDC5              | Bank quiescent power<br>(VCCI-dependent) <sup>2</sup> |          | See Table 2-12 on page 2-8 |             |            |         |  |  |  |

#### Notes:

- 1. Minimum contribution of the PLL when running at lowest frequency.

- 2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or the SmartPower tool in Libero SoC.

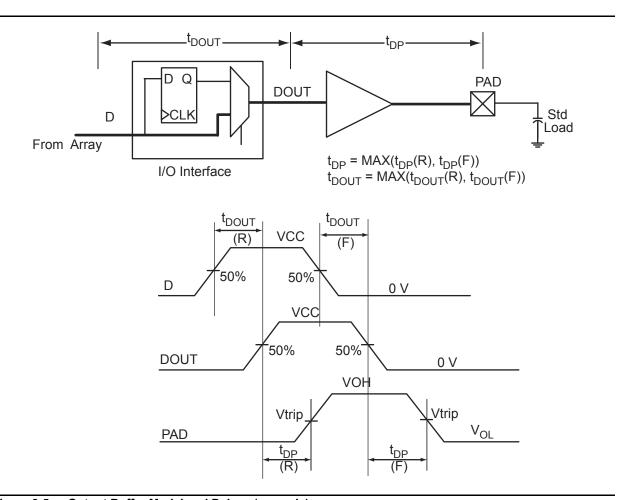

Figure 2-5 • Output Buffer Model and Delays (example)

IGLOO nano Low Power Flash FPGAs

### **Timing Characteristics**

### Applies to 1.5 V DC Core Voltage

Table 2-36 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 3.52            | 0.19             | 0.86            | 1.16             | 0.66              | 3.59            | 3.42            | 1.75            | 1.90            | ns    |

| 4 mA           | STD         | 0.97              | 3.52            | 0.19             | 0.86            | 1.16             | 0.66              | 3.59            | 3.42            | 1.75            | 1.90            | ns    |

| 6 mA           | STD         | 0.97              | 2.90            | 0.19             | 0.86            | 1.16             | 0.66              | 2.96            | 2.83            | 1.98            | 2.29            | ns    |

| 8 mA           | STD         | 0.97              | 2.90            | 0.19             | 0.86            | 1.16             | 0.66              | 2.96            | 2.83            | 1.98            | 2.29            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-37 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 2.16            | 0.19             | 0.86            | 1.16             | 0.66              | 2.20            | 1.80            | 1.75            | 1.99            | ns    |

| 4 mA           | STD         | 0.97              | 2.16            | 0.19             | 0.86            | 1.16             | 0.66              | 2.20            | 1.80            | 1.75            | 1.99            | ns    |

| 6 mA           | STD         | 0.97              | 1.79            | 0.19             | 0.86            | 1.16             | 0.66              | 1.83            | 1.45            | 1.98            | 2.38            | ns    |

| 8 mA           | STD         | 0.97              | 1.79            | 0.19             | 0.86            | 1.16             | 0.66              | 1.83            | 1.45            | 1.98            | 2.38            | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## 1.2 V LVCMOS Wide Range

Table 2-67 • Minimum and Maximum DC Input and Output Levels

| 1.2 V<br>LVCMOS<br>Wide<br>Range |           | VIL        | VIH        |           | VOL       | VOH        | IOL | ЮН  | IOSL                    | юзн                     | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|----------------------------------|-----------|------------|------------|-----------|-----------|------------|-----|-----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength                | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 1 mA                             | -0.3      | 0.3 * VCCI | 0.7 * VCCI | 3.6       | 0.1       | VCCI - 0.1 | 100 | 100 | 10                      | 13                      | 10                      | 10                      |

#### Notes:

- 1. I<sub>II</sub> is the input leakage current per I/O pin over recommended operating conditions where –0.3 < VIN < VIL.

- 2.  $I_{IH}$  is the input leakage current per I/O pin over recommended operating conditions where VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- Applicable to IGLOO nano V2 devices operating at VCCI ≥ VCC.

- 6. Software default selection highlighted in gray.

### Timing Characteristics

Applies to 1.2 V DC Core Voltage

Table 2-68 • 1.2 V LVCMOS Wide Range Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.14 V

| Drive  | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|--------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ | 1 mA                                                                          | STD            | 1.55              | 8.30            | 0.26             | 1.56            | 2.27             | 1.10              | 7.97            | 7.54            | 2.56            | 2.55            | ns    |

#### Notes:

- The minimum drive strength for any LVCMOS 1.2 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-69 • 1.2 V LVCMOS Wide Range HIgh Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.14 V

| Drive  | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|--------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ | 1 mA                                                                          | STD            | 1.55              | 3.50            | 0.26             | 1.56            | 2.27             | 1.10              | 3.37            | 3.10            | 2.55            | 2.66            | ns    |

#### Notes:

- 1. The minimum drive strength for any LVCMOS 1.2 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 3. Software default selection highlighted in gray.

2-40 Revision 19

Table 2-71 • Parameter Definition and Measuring Nodes

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>OCLKQ</sub>    | CLKQ Clock-to-Q of the Output Data Register                     |                                |

| t <sub>OSUD</sub>     | Data Setup Time for the Output Data Register                    |                                |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                        |                                |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| toerecclr             | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      |                                |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

Note: \*See Figure 2-13 on page 2-43 for more information.

2-44 Revision 19

### 1.2 V DC Core Voltage

Table 2-73 • Input Data Register Propagation Delays Commercial-Case Conditions:  $T_J = 70^{\circ}\text{C}$ , Worst-Case VCC = 1.14 V

| Parameter            | Description                                                         | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.68 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         |      | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          |      | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 1.19 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 1.19 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.24 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.24 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.19 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.19 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Input Data Register          | 0.31 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width LOW for the Input Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

2-46 Revision 19

# **DDR Module Specifications**

Note: DDR is not supported for AGLN010, AGLN015, and AGLN020 devices.

# Input DDR Module

Figure 2-17 • Input DDR Timing Model

Table 2-78 • Parameter Definitions

| Parameter Name                             | Parameter Definition         | Measuring Nodes (from, to) |  |  |

|--------------------------------------------|------------------------------|----------------------------|--|--|

| t <sub>DDRICLKQ1</sub> Clock-to-Out Out_QR |                              | B, D                       |  |  |

| t <sub>DDRICLKQ2</sub> Clock-to-Out Out_QF |                              | B, E                       |  |  |

| t <sub>DDRISUD</sub>                       | Data Setup Time of DDR input | A, B                       |  |  |

| t <sub>DDRIHD</sub>                        | Data Hold Time of DDR input  | A, B                       |  |  |

| t <sub>DDRICLR2Q1</sub>                    | Clear-to-Out Out_QR          | C, D                       |  |  |

| t <sub>DDRICLR2Q2</sub>                    | Clear-to-Out Out_QF          | C, E                       |  |  |

| t <sub>DDRIREMCLR</sub> Clear Removal      |                              | C, B                       |  |  |

| t <sub>DDRIRECCLR</sub> Clear Recovery     |                              | C, B                       |  |  |

IGLOO nano Low Power Flash FPGAs

Table 2-90 • AGLN020 Global Resource Commercial-Case Conditions:  $T_J = 70$ °C, VCC = 1.425 V

|                      |                                           |  | Std.              |                   |       |

|----------------------|-------------------------------------------|--|-------------------|-------------------|-------|

| Parameter            | Description                               |  | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |  | 1.21              | 1.55              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |  | 1.23              | 1.65              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |  | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |  |                   | 0.42              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-91 • AGLN060 Global Resource Commercial-Case Conditions: T<sub>.I</sub> = 70°C, VCC = 1.425 V

|                      |                                           | Std. |                   | td.               |       |

|----------------------|-------------------------------------------|------|-------------------|-------------------|-------|

| Parameter            | Description                               |      | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |      | 1.32              | 1.62              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |      | 1.34              | 1.71              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock |      | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  |      | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |      |                   | 0.38              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-92 • AGLN125 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           |  | Std.              |                   |       |

|----------------------|-------------------------------------------|--|-------------------|-------------------|-------|

| Parameter            | Description                               |  | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |  | 1.36              | 1.71              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |  | 1.39              | 1.82              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |  | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |  |                   | 0.43              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-93 • AGLN250 Global Resource Commercial-Case Conditions: T<sub>.I</sub> = 70°C, VCC = 1.425 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.39              | 1.73              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.41              | 1.84              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.43              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-66 Revision 19

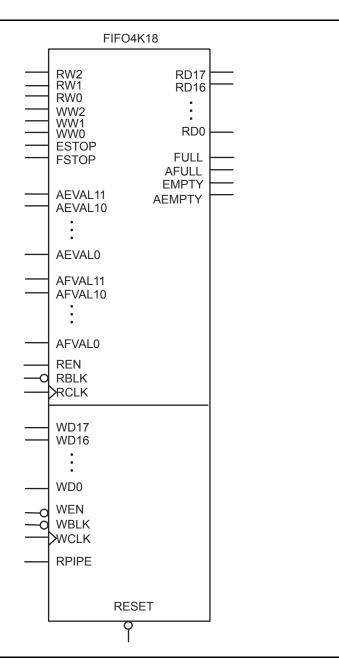

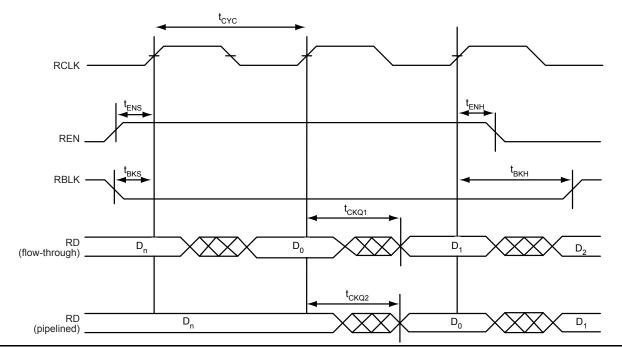

### **FIFO**

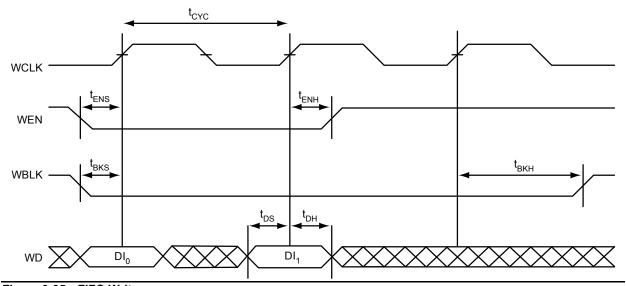

Figure 2-33 • FIFO Model

# Timing Waveforms

Figure 2-34 • FIFO Read

Figure 2-35 • FIFO Write

2-82 Revision 19

# **Related Documents**

### **User Guides**

IGLOO nano FPGA Fabric User's Guide

# **Packaging Documents**

The following documents provide packaging information and device selection for low power flash devices.

### **Product Catalog**

FPGA and SoC Product Catalog

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

### Package Mechanical Drawings

This document contains the package mechanical drawings for all packages currently or previously supplied by Microsemi. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials are on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

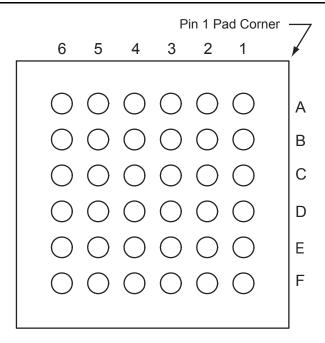

# 4 – Package Pin Assignments

# **UC36**

Note: This is the bottom view of the package.

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

Package Pin Assignments

|            | CS81              |

|------------|-------------------|

| Pin Number | AGLN125Z Function |

| A1         | GAA0/IO00RSB0     |

| A2         | GAA1/IO01RSB0     |

| A3         | GAC0/IO04RSB0     |

| A4         | IO13RSB0          |

| A5         | IO22RSB0          |

| A6         | IO32RSB0          |

| A7         | GBB0/IO37RSB0     |

| A8         | GBA1/IO40RSB0     |

| A9         | GBA2/IO41RSB0     |

| B1         | GAA2/IO132RSB1    |

| B2         | GAB0/IO02RSB0     |

| В3         | GAC1/IO05RSB0     |

| B4         | IO11RSB0          |

| B5         | IO25RSB0          |

| В6         | GBC0/IO35RSB0     |

| В7         | GBB1/IO38RSB0     |

| B8         | IO42RSB0          |

| В9         | GBB2/IO43RSB0     |

| C1         | GAB2/IO130RSB1    |

| C2         | IO131RSB1         |

| C3         | GND               |

| C4         | IO15RSB0          |

| C5         | IO28RSB0          |

| C6         | GND               |

| C7         | GBA0/IO39RSB0     |

| C8         | GBC2/IO45RSB0     |

| C9         | IO47RSB0          |

| D1         | GAC2/IO128RSB1    |

| D2         | IO129RSB1         |

| D3         | GFA2/IO117RSB1    |

| D4         | VCC               |

| D5         | VCCIB0            |

| D6         | GND               |

| D7         | GCC2/IO59RSB0     |

| D8         | GCC1/IO51RSB0     |

| D9         | GCC0/IO52RSB0     |

|            | CS81              |

|------------|-------------------|

| Pin Number | AGLN125Z Function |

| E1         | GFB0/IO120RSB1    |

| E2         | GFB1/IO121RSB1    |

| E3         | GFA1/IO118RSB1    |

| E4         | VCCIB1            |

| E5         | VCC               |

| E6         | VCCIB0            |

| E7         | GCA0/IO56RSB0     |

| E8         | GCA1/IO55RSB0     |

| E9         | GCB2/IO58RSB0     |

| F1*        | VCCPLF            |

| F2*        | VCOMPLF           |

| F3         | GND               |

| F4         | GND               |

| F5         | VCCIB1            |

| F6         | GND               |

| F7         | GDA1/IO65RSB0     |

| F8         | GDC1/IO61RSB0     |

| F9         | GDC0/IO62RSB0     |

| G1         | GEA0/IO104RSB1    |

| G2         | GEC0/IO108RSB1    |

| G3         | GEB1/IO107RSB1    |

| G4         | IO96RSB1          |

| G5         | IO92RSB1          |

| G6         | IO72RSB1          |

| G7         | GDB2/IO68RSB1     |

| G8         | VJTAG             |

| G9         | TRST              |

| H1         | GEA1/IO105RSB1    |

| H2         | FF/GEB2/IO102RSB1 |

| НЗ         | IO99RSB1          |

| H4         | IO94RSB1          |

| H5         | IO91RSB1          |

| H6         | IO81RSB1          |

| H7         | GDA2/IO67RSB1     |

| H8         | TDI               |

| H9         | TDO               |

| CS81       |                   |  |  |  |  |  |

|------------|-------------------|--|--|--|--|--|

| Pin Number | AGLN125Z Function |  |  |  |  |  |

| J1         | GEA2/IO103RSB1    |  |  |  |  |  |

| J2         | GEC2/IO101RSB1    |  |  |  |  |  |

| J3         | IO97RSB1          |  |  |  |  |  |

| J4         | IO93RSB1          |  |  |  |  |  |

| J5         | IO90RSB1          |  |  |  |  |  |

| J6         | IO78RSB1          |  |  |  |  |  |

| J7         | TCK               |  |  |  |  |  |

| J8         | TMS               |  |  |  |  |  |

| J9         | VPUMP             |  |  |  |  |  |

Note: \* Pin numbers F1 and F2 must be connected to ground because a PLL is not supported for AGLN125Z-CS81.

4-12 Revision 19

IGLOO nano Low Power Flash FPGAs

| QN48       |                   |  |  |

|------------|-------------------|--|--|

| Pin Number | AGLN030Z Function |  |  |

| 1          | IO82RSB1          |  |  |

| 2          | GEC0/IO73RSB1     |  |  |

| 3          | GEA0/IO72RSB1     |  |  |

| 4          | GEB0/IO71RSB1     |  |  |

| 5          | GND               |  |  |

| 6          | VCCIB1            |  |  |

| 7          | IO68RSB1          |  |  |

| 8          | IO67RSB1          |  |  |

| 9          | IO66RSB1          |  |  |

| 10         | IO65RSB1          |  |  |

| 11         | IO64RSB1          |  |  |

| 12         | IO62RSB1          |  |  |

| 13         | IO61RSB1          |  |  |

| 14         | FF/IO60RSB1       |  |  |

| 15         | IO57RSB1          |  |  |

| 16         | IO55RSB1          |  |  |

| 17         | IO53RSB1          |  |  |

| 18         | VCC               |  |  |

| 19         | VCCIB1            |  |  |

| 20         | IO46RSB1          |  |  |

| 21         | IO42RSB1          |  |  |

| 22         | TCK               |  |  |

| 23         | TDI               |  |  |

| 24         | TMS               |  |  |

| 25         | VPUMP             |  |  |

| 26         | TDO               |  |  |

| 27         | TRST              |  |  |

| 28         | VJTAG             |  |  |

| 29         | IO38RSB0          |  |  |

| 30         | GDB0/IO34RSB0     |  |  |

| 31         | GDA0/IO33RSB0     |  |  |

| 32         | GDC0/IO32RSB0     |  |  |

| 33         | VCCIB0            |  |  |

| 34         | GND               |  |  |

| 35         | VCC               |  |  |

| 36         | IO25RSB0          |  |  |

|            |                   |  |  |

| QN48       |                   |  |

|------------|-------------------|--|

| Pin Number | AGLN030Z Function |  |

| 37         | IO24RSB0          |  |

| 38         | IO22RSB0          |  |

| 39         | IO20RSB0          |  |

| 40         | IO18RSB0          |  |

| 41         | IO16RSB0          |  |

| 42         | IO14RSB0          |  |

| 43         | IO10RSB0          |  |

| 44         | IO08RSB0          |  |

| 45         | IO06RSB0          |  |

| 46         | IO04RSB0          |  |

| 47         | IO02RSB0          |  |

| 48         | IO00RSB0          |  |

### IGLOO nano Low Power Flash FPGAs

| Revision / Version        | Changes                                                                                                                                                                                                                                                                                                                                 | Page                  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Revision 1 (cont'd)       | The "QN48" pin diagram was revised.                                                                                                                                                                                                                                                                                                     | 4-16                  |

| Packaging Advance<br>v0.2 | Note 2 for the "QN48", "QN68", and "100-Pin QFN" pin diagrams was changed to "The die attach paddle of the package is tied to ground (GND)."                                                                                                                                                                                            | 4-16, 4-19            |

|                           | The "VQ100" pin diagram was revised to move the pin IDs to the upper left corner instead of the upper right corner.                                                                                                                                                                                                                     | 4-23                  |

|                           | The following tables and sections were updated to add the UC81 and CS81 packages for AGL030: "IGLOO nano Devices" "I/Os Per Package" "IGLOO nano Products Available in the Z Feature Grade" "Temperature Grade Offerings"                                                                                                               | N/A                   |

|                           | The "I/Os Per Package" table was updated to add the following information to table note 4: "For nano devices, the VQ100 package is offered in both leaded and RoHS-compliant versions. All other packages are RoHS-compliant only."                                                                                                     | II                    |

|                           | The "IGLOO nano Products Available in the Z Feature Grade" section was updated to remove QN100 for AGLN250.                                                                                                                                                                                                                             | VI                    |

|                           | The device architecture figures, Figure 1-3 • IGLOO Device Architecture Overview with Two I/O Banks (AGLN060, AGLN125) through Figure 1-4 • IGLOO Device Architecture Overview with Four I/O Banks (AGLN250), were revised. Figure 1-1 • IGLOO Device Architecture Overview with Two I/O Banks and No RAM (AGLN010 and AGLN030) is new. | 1-4<br>through<br>1-5 |

|                           | The "PLL and CCC" section was revised to include information about CCC-GLs in AGLN020 and smaller devices.                                                                                                                                                                                                                              | 1-7                   |

|                           | The "I/Os with Advanced I/O Standards" section was revised to add information about IGLOO nano devices supporting double-data-rate applications.                                                                                                                                                                                        | 1-8                   |