#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 100MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SCI, SPI                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 57                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 32K x 8                                                                          |

| RAM Size                   | 24K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                      |

| Data Converters            | A/D 12x10b, 8x12b; D/A 2x10b                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP                                                                         |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f563tbedfp-v0 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Overview

# 1.1 Outline of Specifications

Table 1.1 lists the specifications in outline, and Table 1.2 lists the functions of products.

Table 1.1 shows an outline of the maximum specifications, and the available peripheral modules and number of channels differ according to the number of pins on the package and the ROM capacity. For details, see Table 1.2, Comparison of Functions for Different Packages.

| Classification      | Module/Function           | <ul> <li>Description</li> <li>Maximum operating frequency: 100 MHz</li> <li>32-bit RX CPU</li> <li>Minimum instruction execution time: One instruction per state (cycle of the system clock)</li> <li>Address space: 4-Gbyte linear</li> <li>Register set of the CPU<br/>General purpose: Sixteen 32-bit registers<br/>Control: Nine 32-bit registers</li> <li>Accumulator: One 64-bit register</li> <li>Basic instructions: 73</li> <li>Floating-point operation instructions: 8</li> <li>DSP instructions: 9</li> <li>Addressing modes: 10</li> <li>Data arrangement<br/>Instructions: Little endian<br/>Data: Selectable as little endian or big endian</li> <li>On-chip 32-bit multiplier: 32 × 32 → 64 bits</li> <li>On-chip divider: 32 / 32 → 32 bits</li> </ul> |  |  |  |  |  |

|---------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CPU                 | CPU                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                     | FPU                       | <ul> <li>Single precision floating point (32 bits)</li> <li>Data types and floating-point exceptions in conformance with the IEEE754 standard</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Memory              | ROM                       | <ul> <li>Capacity: 512 Kbytes, 384 Kbytes, 256 Kbytes, 64 Kbytes, 48 Kbytes, 32 Kbytes</li> <li>100 MHz, no-wait access</li> <li>On-board programming: Programs can be modified through SCI or USB while the MCU is mounted on the board.</li> <li>Off-board programming: Programs can be modified using parallel programmer. (only in 144-, 120-, 112- and 100-pin versions)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                     | RAM                       | <ul> <li>Capacity: 48 Kbytes, 32 Kbytes, 24 Kbytes, 8 Kbytes</li> <li>100 MHz, no-wait access</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                     | E <sup>2</sup> data flash | <ul> <li>Capacity: 32 Kbytes, 8 Kbytes</li> <li>Programming/erasing: 100,000 times</li> <li>On-board programming:<br/>Programs can be modified through SCI or USB while the MCU is mounted on the board.<br/>Programming from the user program is possible.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| MCU operating modes |                           | [144-, 120-, 112- and 100-pin versions]<br>Single-chip mode, on-chip ROM enabled extended mode, on-chip ROM disabled<br>extended mode (switchable by software)<br>[64- and 48-pin versions]<br>Single-chip mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

Table 1.1

Outline of Specifications (1/7)

| Classification Module/Function                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 12-bit A/D converter (S12ADB)<br>[64- and 48-pin versions]      | <ul> <li>12 bits (8 channels x 1 unit)</li> <li>12-bit resolution</li> <li>Conversion time <ol> <li>0 µs per channel (S12ADB clock: PCLKD (A/D conversion clock: ADCLK) = 50 MHz</li> </ol> </li> <li>Operating modes <ul> <li>Scan mode (single scan mode / continuous scan mode / group scan mode)</li> <li>Group A priority control (group scan mode only)</li> </ul> </li> <li>Sample-and-hold function <ul> <li>A common sample-and-hold circuit for units is included</li> <li>Separate sample-and-hold circuits are also included (three channels per unit)</li> </ul> </li> <li>Self-diagnosis function <ul> <li>Three analog input voltages (VREFL0, VREFH0 × 1/2, VREFH0) can be generated internally by the self-diagnosis function.</li> </ul> </li> <li>Double trigger mode (double the results of A/D conversion)</li> <li>Three ways to start A/D conversion <ul> <li>Conversion can be started by software, a conversion start trigger from a timer (MTU3 conversion)</li> </ul> </li> </ul> |  |  |  |  |  |  |

| 10-bit A/D converter (ADA)                                      | <ul> <li>Window comparators (three channels per unit)</li> <li>10 bits (20 channels × 1 unit)</li> <li>10-bit resolution</li> <li>Conversion time</li> <li>0.5 µs per channel (A/D conversion clock ADCLK = 100 MHz)</li> <li>Two operating modes</li> <li>Single mode, scan mode</li> <li>Scan mode</li> <li>Scan mode</li> <li>Scan mode</li> <li>Sample-and-hold function</li> <li>A common sample-and-hold circuit for units is included</li> <li>Three ways to start A/D conversion</li> <li>Conversion can be started by software, a conversion start trigger from a timer (MTU3 GPT), or an external trigger signal.</li> <li>8-bit precision output</li> <li>2-bit right shifting for output of conversion results is selectable.</li> <li>Self-diagnostic function</li> <li>The self-diagnostic function internally generates three analog input voltages (AVSS,</li> </ul>                                                                                                                         |  |  |  |  |  |  |

| D/A converter (DAa)                                             | <ul> <li>2 channels</li> <li>10-bit resolution</li> <li>Output voltage: 0 V to VREF</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| CRC calculator (CRC)                                            | <ul> <li>CRC code generation for arbitrary amounts of data in 8-bit units</li> <li>Select any of three generating polynomials:<br/>X<sup>8</sup> + X<sup>2</sup> + X + 1, X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1, or X<sup>16</sup> + X<sup>12</sup> + X<sup>5</sup> + 1.</li> <li>Generation of CRC codes for use with LSB-first or MSB-first communications is selectable</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Data operating circuit (DOC)                                    | Comparison, addition, and subtraction of 16-bit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Digital power supply controller (DPC)                           | <ul> <li>Control parameters calculation unit of the digital switch-mode power supply systems.</li> <li>Adopt robust control algorithm with high control stability</li> <li>Results of measurement by the 10-bit A/D converter can be used in calculating the control parameters.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Operating frequency                                             | Up to 100 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Power supply voltage<br>[144-, 120-, 112- and 100-pin versions] | <ul> <li>3-V product<br/>VCC = PLLVCC = VCC_USB = 2.7 to 3.6 V<br/>AVCC0 = AVCC = VREF = 3.0 to 3.6 V, or 4.0 to 5.5 V<br/>VREFH0 = 3.0 to AVCC0, or 4.0 to AVCC0</li> <li>5-V product<br/>VCC = PLLVCC = 4.0 to 5.5 V<br/>VCC_USB = 3.0 to 3.6 V<br/>AVCC0 = AVCC = VREF = 4.0 to 5.5 V<br/>VREFH0 = 4.0 to AVCC0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Power supply voltage<br>[64- and 48-pin versions]               | VCC = 2.7 to 3.6 V, AVCC0 = 3.0 to 3.6 V, VREFH0 = 3.0 V to AVCC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

Table 1.1

Outline of Specifications (6/7)

| Classification Mo        | dule/Function | Description                                          |

|--------------------------|---------------|------------------------------------------------------|

| Operating temperature    |               | D version: -40 to +85°C,                             |

|                          |               | G version: -40 to +105°C *1                          |

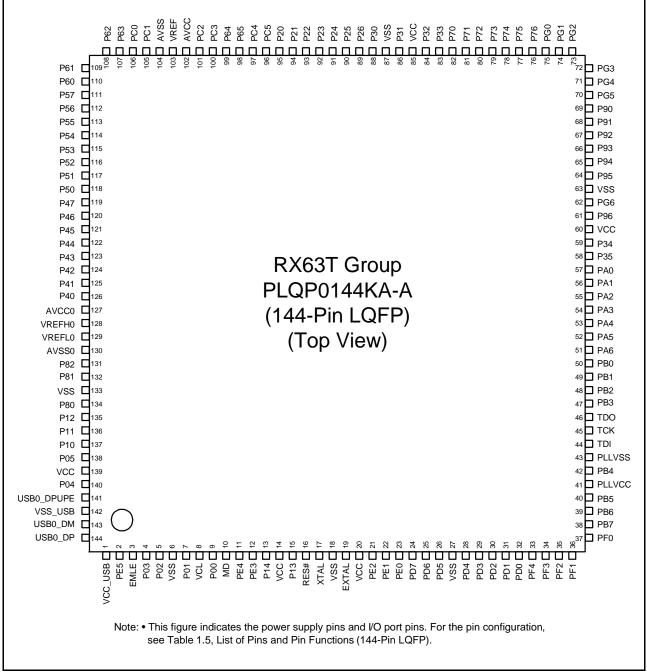

| Package                  |               | 144-pin LQFP (PLQP0144KA-A (20 × 20, 0.5-mm pitch))  |

| -                        |               | 120-pin LQFP (PLQP0120KA-A (16 × 16, 0.5-mm pitch))  |

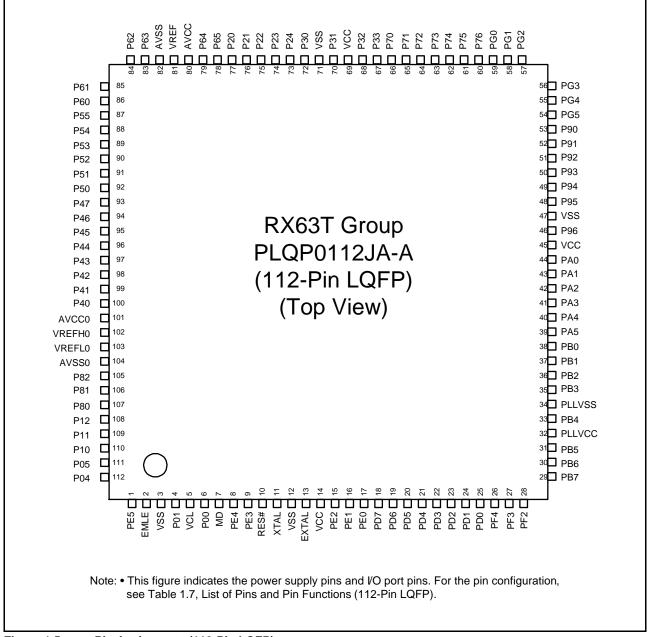

|                          |               | 112-pin LQFP (PLQP0112JA-A (20 × 20, 0.65-mm pitch)) |

|                          |               | 100-pin LQFP (PLQP0100KB-A (14 × 14, 0.5-mm pitch))  |

|                          |               | 64-pin LQFP (PLQP0064KB-A (10 × 10, 0.5-mm pitch))   |

|                          |               | 48-pin LQFP (PLQP0048KB-A (07 × 07, 0.5-mm pitch))   |

| On-chip debugging system |               | • E1 emulator (JTAG and FINE interfaces)             |

|                          |               | <ul> <li>E20 emulator (JTAG interface)</li> </ul>    |

Table 1.1Outline of Specifications (7/7)

Note 1. Please contact Renesas Electronics sales office for derating of operation under Ta = +85°C to +105°C. Derating is the systematic reduction of load for the sake of improved reliability.

## 1.4 Pin Functions

Table 1.4 lists the pin functions.

## Table 1.4Pin Functions (1/5)

| Classifications                      | Pin Name           | I/O    | Description                                                                                                                                                              |

|--------------------------------------|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply                         | VCC                | _      | Power supply pin. Connect it to the system power supply. Connect this pin to VSS via a $0.1$ - $\mu$ F capacitor. The capacitor should be placed close to the pin        |

|                                      | VCL                | _      | Connect this pin to VSS via a 0.1- $\mu$ F capacitor. The capacitor should be placed close to the pin                                                                    |

|                                      | VSS                |        | Ground pin. Connect it to the system power supply (0 V)                                                                                                                  |

|                                      | PLLVCC             | _      | Power supply pin. Connect it to the system power supply.                                                                                                                 |

|                                      | PLLVSS             | _      | Ground pin. Connect it to the system power supply (0 V)                                                                                                                  |

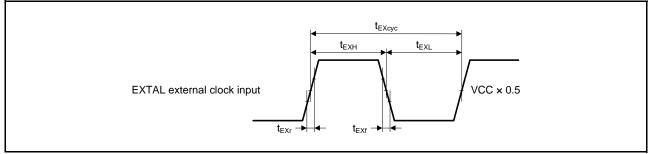

| Clock                                | XTAL               | Output | Pins for a crystal resonator. An external clock signal can be input                                                                                                      |

|                                      | EXTAL              | Input  | through the EXTAL pin                                                                                                                                                    |

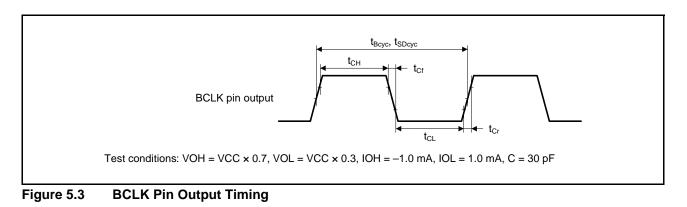

|                                      | BCLK               | Output | Outputs the external bus clock for external devices                                                                                                                      |

| Clock frequency accuracy measurement | CACREF             | Input  | Input for the trigger signal in measuring accuracy of the clock frequency                                                                                                |

| Operating mode control               | MD                 | Input  | Pin for setting the operating mode. The signal levels on these pins must not be changed during operation                                                                 |

| System control                       | RES#               | Input  | Reset signal input pin. This LSI enters the reset state when this signal goes low                                                                                        |

|                                      | EMLE               | Input  | Input pin for the on-chip emulator enable signal. When the on-chip emulator is used, this pin should be driven high. When not used, it should be driven low              |

| On-chip emulator                     | FINEC              | Input  | Fine interface clock pin                                                                                                                                                 |

|                                      | FINED              | I/O    | Fine interface pin                                                                                                                                                       |

|                                      | TRST#              | Input  | On-chip emulator pins. When the EMLE pin is driven high, these                                                                                                           |

|                                      | TMS                | Input  | pins are dedicated for the on-chip emulator.                                                                                                                             |

|                                      | TDI                | Input  | -                                                                                                                                                                        |

|                                      | ТСК                | Input  | -                                                                                                                                                                        |

|                                      | TDO                | Output | -                                                                                                                                                                        |

|                                      | TRCLK              | Output | This pin outputs the clock for synchronization with the trace data                                                                                                       |

|                                      | TRSYNC             | Output | This pin indicates that output from the TRDATA0 to TRDATA3 pins is valid                                                                                                 |

|                                      | TRDATA0 to TRDATA3 | Output | These pins output the trace information                                                                                                                                  |

| Address bus                          | A0 to A19          | Output | Output pins for the address                                                                                                                                              |

| Data bus                             | D0 to D15          | I/O    | Input and output pins for the bidirectional data bus                                                                                                                     |

| Multiplexed bus                      | A0/D0 to A15/D15   | I/O    | Address/data multiplexed bus                                                                                                                                             |

| Bus control                          | RD#                | Output | Strobe signal which indicates that reading from the external bus interface space is in progress                                                                          |

|                                      | WR#                | Output | Strobe signal which indicates that writing to the external bus interface space is in progress, in 1-write strobe mode                                                    |

|                                      | WR0# to WR1#       | Output | Strobe signals which indicate that either group of data bus pins (D7 to D0 and D15 to D8) is valid in writing to the external bus interface space, in byte strobe mode   |

|                                      | BC0# to BC1#       | Output | Strobe signals which indicate that either group of data bus pins (D7 to D0 and D15 to D8) is valid in access to the external bus interface space, in 1-write strobe mode |

|                                      | ALE                | Output | Address latch signal when address/data multiplexed bus is selected                                                                                                       |

|                                      | WAIT#              | Input  | Input pin for wait request signals in access to the external space                                                                                                       |

|                                      | CS0# to CS3#       | Output | Select signals for CS areas                                                                                                                                              |

| Classifications                   | Pin Name                                        | I/O   | Description                                                                                        |

|-----------------------------------|-------------------------------------------------|-------|----------------------------------------------------------------------------------------------------|

| Interrupt                         | NMI                                             | Input | Non-maskable interrupt request pin                                                                 |

|                                   | IRQ0 to IRQ7                                    | Input | Maskable interrupt request pin                                                                     |

| Multi-function timer pulse unit 3 | MTIOC0A, MTIOC0B<br>MTIOC0C, MTIOC0D            | I/O   | The TGRA0 to TGRD0 input capture input/output compare output/<br>PWM output pins                   |

|                                   | MTIOC1A, MTIOC1B                                | I/O   | The TGRA1 and TGRB1 input capture input/output compare output<br>PWM output pins                   |

|                                   | MTIOC2A, MTIOC2B                                | I/O   | The TGRA2 and TGRB2 input capture input/output compare output<br>PWM output pins                   |

|                                   | MTIOC3A, MTIOC3B<br>MTIOC3C, MTIOC3D            | I/O   | The TGRA3 to TGRD3 input capture input/output compare output/<br>PWM output pins                   |

|                                   | MTIOC4A, MTIOC4B<br>MTIOC4C, MTIOC4D            | I/O   | The TGRA4 to TGRD4 input capture input/output compare output/<br>PWM output pins                   |

|                                   | MTIC5U, MTIC5V<br>MTIC5W                        | Input | The TGRU5, TGRV5, and TGRW5 input capture input/dead time<br>compensation input pins               |

|                                   | MTIOC6A, MTIOC6B<br>MTIOC6C, MTIOC6D            | I/O   | The TGRA6 to TGRD6 input capture input/output compare output/<br>PWM output pins                   |

|                                   | MTIOC7A, MTIOC7B<br>MTIOC7C, MTIOC7D            | I/O   | The TGRA7 to TGRD7 input capture input/output compare output/<br>PWM output pins                   |

|                                   | MTCLKA, MTCLKB<br>MTCLKC, MTCLKD                | Input | Input pins for external clock                                                                      |

| Port output enable 3              | POE0#, POE4#<br>POE8#, POE10#<br>POE11#, POE12# | Input | Input pins for request signals to place the MTU/GPT large-current pins in the high impedance state |

| General PWM timer                 | GTIOC0A, GTIOC0B                                | I/O   | The GPT0.GTGRA and GPT0.GTGRB input capture input/output compare output/PWM output pins.           |

|                                   | GTIOC1A, GTIOC1B                                | I/O   | The GPT1.GTGRA and GPT1.GTGRB input capture input/output compare output/PWM output pins.           |

|                                   | GTIOC2A, GTIOC2B                                | I/O   | The GPT2.GTGRA and GPT2.GTGRB input capture input/output compare output/PWM output pins.           |

|                                   | GTIOC3A, GTIOC3B                                | I/O   | The GPT3.GTGRA and GPT3.GTGRB input capture input/output compare output/PWM output pins.           |

|                                   | GTETRG0                                         | Input | External trigger input pin for the GPT0 to GPT3                                                    |

|                                   | GTIOC4A, GTIOC4B                                | I/O   | The GPT4.GTGRA and GPT4.GTGRB input capture input/output compare output/PWM output pins.           |

|                                   | GTIOC5A, GTIOC5B                                | I/O   | The GPT5.GTGRA and GPT5.GTGRB input capture input/output compare output/PWM output pins.           |

|                                   | GTIOC6A, GTIOC6B                                | I/O   | The GPT6.GTGRA and GPT6.GTGRB input capture input/output compare output/PWM output pins.           |

|                                   | GTIOC7A, GTIOC7B                                | I/O   | The GPT7.GTGRA and GPT7.GTGRB input capture input/output compare output/PWM output pins.           |

|                                   | GTETRG1                                         | Input | External trigger input pin for the GPT4 to GPT7                                                    |

## Table 1.4Pin Functions (2/5)

## 1.5 Pin Assignments

Figure 1.3 to Figure 1.8 show the pin assignments. Table 1.5 to Table 1.10 show the lists of pins and pin functions.

Figure 1.5 Pin Assignment (112-Pin LQFP)

| Pin Number<br>100-Pin<br>LQFP | Power Supply<br>Clock System<br>Control | I/O Port | Bus                 | Timer<br>(MTU3, GPT, POE3, CAC) | Communications<br>(SCIc, SCId, RSPI, RIIC,<br>CAN) | Interrupt | S12ADB,<br>AD, DA |

|-------------------------------|-----------------------------------------|----------|---------------------|---------------------------------|----------------------------------------------------|-----------|-------------------|

| 1                             |                                         | PE5      | BCLK                |                                 | ,                                                  | IRQ0      |                   |

| 2                             | EMLE                                    | -        | -                   |                                 |                                                    |           |                   |

| 3                             | VSS                                     |          |                     |                                 |                                                    |           |                   |

| 4                             |                                         | P01      | RD#                 |                                 | CTS0#/RTS0#/SS0#                                   |           |                   |

| 5                             | VCL                                     |          |                     |                                 |                                                    |           |                   |

| 6                             |                                         | P00      | CS1#                | CACREF                          |                                                    |           |                   |

| 7                             | MD/FINED                                |          |                     |                                 |                                                    |           |                   |

| 8                             |                                         | PE4      | A10                 | POE10#/MTCLKC                   |                                                    | IRQ1      |                   |

| 9                             |                                         | PE3      | A11                 | POE11#/MTCLKD                   |                                                    | IRQ2-DS   |                   |

| 10                            | RES#                                    |          |                     |                                 |                                                    |           |                   |

| 11                            | XTAL                                    |          |                     |                                 |                                                    |           |                   |

| 12                            | VSS                                     |          |                     |                                 |                                                    |           |                   |

| 13                            | EXTAL                                   |          |                     |                                 |                                                    |           |                   |

| 14                            | VCC                                     |          |                     |                                 |                                                    |           |                   |

| 15                            |                                         | PE2      |                     | POE10#                          |                                                    | NMI       |                   |

| 16                            |                                         | PE1      | WR0#/WR#            |                                 | CTS12#/RTS12#/<br>SS12#/SSLA3/SSLB3                |           |                   |

| 17                            |                                         | PE0      | WR1#/BC1#/<br>WAIT# |                                 | SSLA2/SSLB2/CRX1                                   | IRQ7      |                   |

| 18                            | TRST#                                   | PD7      |                     | GTIOC0A                         | CTS0#/RTS0#/SS0#/<br>SSLA1/SSLB1/CTX1              |           |                   |

| 19                            | TMS                                     | PD6      |                     | GTIOC0B                         | SSLA0/SSLB0                                        |           |                   |

| 20                            | TDI                                     | PD5      |                     | GTIOC1A                         | RXD1/SMISO1/SSCL1                                  | IRQ6      |                   |

| 21                            | TCK/FINEC                               | PD4      |                     | GTIOC1B                         | SCK1                                               |           |                   |

| 22                            | TDO                                     | PD3      |                     | GTIOC2A                         | TXD1/SMOSI1/SSDA1                                  |           |                   |

| 23                            |                                         | PD2      | CS2#                | GTIOC2B                         | MOSIA/MOSIB                                        |           |                   |

| 24                            |                                         | PD1      | CS0#                | GTIOC3A                         | MISOA/MISOB                                        |           |                   |

| 25                            |                                         | PD0      | A12                 | GTIOC3B                         | RSPCKA/RSPCKB                                      |           |                   |

| 26                            |                                         | PB7      | A19                 |                                 | SCK12                                              |           |                   |

| 27                            |                                         | PB6      | A18                 |                                 | RXD12/SMISO12/<br>SSCL12/RXDX12/<br>CRX1           | IRQ2      |                   |

| 28                            |                                         | PB5      | A17                 |                                 | TXD12/SMOSI12/<br>SSDA12/TXDX12/<br>SIOX12/CTX1    |           |                   |

| 29                            | PLLVCC                                  |          |                     |                                 |                                                    |           |                   |

| 30                            |                                         | PB4      | A16                 | POE8#/GTETRG0                   |                                                    | IRQ3-DS   |                   |

| 31                            | PLLVSS                                  |          |                     |                                 |                                                    |           |                   |

| 32                            |                                         | PB3      | A15                 | MTIOC0A/CACREF                  | SCK0                                               |           |                   |

| 33                            |                                         | PB2      |                     | MTIOC0B                         | TXD0/SMOSI0/<br>SSDA0/SDA0                         |           |                   |

| 34                            |                                         | PB1      |                     | MTIOC0C                         | RXD0/SMISO0/<br>SSCL0/SCL0                         | IRQ4      |                   |

| 35                            |                                         | PB0      | A14                 | MTIOC0D                         | MOSIA/MOSIB                                        |           |                   |

| 36                            |                                         | PA5      |                     | MTIOC1A                         | RXD0/SMISO0/<br>SSCL0/<br>MISOA/MISOB              |           | ADTRG1            |

| Pin Number     | Power Supply<br>Clock |          | POE3   | Timer                       | Comn                                           | nunications  |           |        |

|----------------|-----------------------|----------|--------|-----------------------------|------------------------------------------------|--------------|-----------|--------|

| 64-Pin<br>LQFP | System<br>Control     | I/O Port |        | (MTU3,<br>GPT, CAC)         | (SCIc, SCId)                                   | (RSPI, RIIC) | Interrupt | S12ADB |

| 1              | EMLE                  |          |        |                             |                                                |              |           |        |

| 2              |                       | P00      |        | GTIOC3A                     | CTS0#<br>RTS0#<br>SS0#                         |              | IRQ2-DS   |        |

| 3              | VCL                   |          |        |                             |                                                |              |           |        |

| 4              |                       | P01      |        | GTIOC3B<br>CACREF           |                                                |              | IRQ4-DS   |        |

| 5              | MD<br>FINED           |          |        |                             |                                                |              |           |        |

| 6              | RES#                  |          |        |                             |                                                |              |           |        |

| 7              | XTAL                  |          |        |                             |                                                |              |           |        |

| 8              | VSS                   |          |        |                             |                                                |              |           |        |

| 9              | EXTAL                 |          |        |                             |                                                |              |           |        |

| 10             | VCC                   |          |        |                             |                                                |              |           |        |

| 11             |                       | PE2      | POE10# |                             |                                                |              | NMI       |        |

| 12             | TRST#                 | PD7      |        | GTIOC0A                     | CTS0#<br>RTS0#<br>SS0#                         |              |           |        |

| 13             | TMS                   | PD6      |        | GTIOC0B                     |                                                |              |           |        |

| 14             | TDI                   | PD5      |        | GTIOC1A                     | RXD1<br>SMISO1<br>SSCL1                        |              |           |        |

| 15             | TCK<br>FINEC          | PD4      |        | GTIOC1B                     | SCK1                                           |              |           |        |

| 16             | TDO                   | PD3      |        | GTIOC2A                     | TXD1<br>SMOSI1<br>SSDA1                        |              |           |        |

| 17             |                       | PB7      |        | GTIOC2B                     | SCK12                                          |              |           |        |

| 18             |                       | PB6      |        | GTIOC2B                     | RXD12<br>SMISO12<br>SSCL12<br>RXDX12           |              |           |        |

| 19             |                       | PB5      | POE11# |                             | TXD12<br>SMOSI12<br>SSDA12<br>TXDX12<br>SIOX12 |              | IRQ0      |        |

| 20             | VCC                   |          |        |                             |                                                |              |           |        |

| 21             |                       | PB4      | POE8#  | GTETRG                      | CTS12#<br>RTS12#<br>SS12#                      |              | IRQ3-DS   |        |

| 22             | VSS                   |          | 1      | 1                           |                                                | 1            |           |        |

| 23             |                       | PB3      |        | MTIOC0A<br>MTCLKA<br>CACREF | SCK0                                           |              |           |        |

| 24             |                       | PB2      |        | MTIOC0B<br>MTCLKB           | TXD0<br>SMOSI0<br>SSDA0                        | SDA          |           |        |

| 25             |                       | PB1      |        | MTIOC0C                     | RXD0<br>SMISO0<br>SSCL0                        | SCL          |           |        |

| 26             |                       | PB0      | 1      | MTIOC0D                     |                                                | MOSIA        |           | 1      |

Table 1.9

List of Pins and Pin Functions (64-Pin LQFP) (1/3)

|            | Module |                                        | Register | Number  | Access | Number of Access States                                                 | Module |                                                             |  |

|------------|--------|----------------------------------------|----------|---------|--------|-------------------------------------------------------------------------|--------|-------------------------------------------------------------|--|

| Address    | Symbol | Register Name                          | Symbol   | of Bits | Size   | $\textbf{ICLK} \geq \textbf{PCLK} \qquad \textbf{ICLK} < \textbf{PCLK}$ | Name   | Remarks                                                     |  |

| 0008 732C  | ICU    | Interrupt Source Priority Register 044 | IPR044   | 8       | 8      | 2 ICLK                                                                  | ICUb   | Not present in versions with 64 or 48 pins.                 |  |

| 0008 732Dh | ICU    | Interrupt Source Priority Register 045 | IPR045   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7331h | ICU    | Interrupt Source Priority Register 049 | IPR049   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7334h | ICU    | Interrupt Source Priority Register 052 | IPR052   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7336h | ICU    | Interrupt Source Priority Register 054 | IPR054   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7337h | ICU    | Interrupt Source Priority Register 055 | IPR055   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7338h | ICU    | Interrupt Source Priority Register 056 | IPR056   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7339h | ICU    | Interrupt Source Priority Register 057 | IPR057   | 8       | 8      | 2 ICLK                                                                  |        |                                                             |  |

| 0008 733Ah | ICU    | Interrupt Source Priority Register 058 | IPR058   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 733Bh | ICU    | Interrupt Source Priority Register 059 | IPR059   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 733Ch | ICU    | Interrupt Source Priority Register 060 | IPR060   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 733Dh | ICU    | Interrupt Source Priority Register 061 | IPR061   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 733Eh | ICU    | Interrupt Source Priority Register 062 | IPR062   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7340h | ICU    | Interrupt Source Priority Register 064 | IPR064   | 8       | 8      | 2 ICLK                                                                  | -      |                                                             |  |

| 0008 7341h | ICU    | Interrupt Source Priority Register 065 | IPR065   | 8       | 8      | 2 ICLK                                                                  | -      |                                                             |  |

| 0008 7342h | ICU    | Interrupt Source Priority Register 066 | IPR066   | 8       | 8      | 2 ICLK                                                                  |        |                                                             |  |

| 0008 7343h | ICU    | Interrupt Source Priority Register 067 | IPR067   | 8       | 8      | 2 ICLK                                                                  | _      |                                                             |  |

| 0008 7344h | ICU    | Interrupt Source Priority Register 068 | IPR068   | 8       | 8      | 2 ICLK                                                                  |        |                                                             |  |

| 0008 7345h | ICU    | Interrupt Source Priority Register 069 | IPR069   | 8       | 8      | 2 ICLK                                                                  |        |                                                             |  |

| 0008 7346h | ICU    | Interrupt Source Priority Register 070 | IPR070   | 8       | 8      | 2 ICLK                                                                  | _      | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7347h | ICU    | Interrupt Source Priority Register 071 | IPR071   | 8       | 8      | 2 ICLK                                                                  | -      | Not present in versions<br>with 64 or 48 pins.              |  |

| 0008 735Ah | ICU    | Interrupt Source Priority Register 090 | IPR090   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions<br>with 112, 100, 64 or 48<br>pins. |  |

| 0008 7362h | ICU    | Interrupt Source Priority Register 098 | IPR098   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7366h | ICU    | Interrupt Source Priority Register 102 | IPR102   | 8       | 8      | 2 ICLK                                                                  | _      |                                                             |  |

| 0008 7367h | ICU    | Interrupt Source Priority Register 103 | IPR103   | 8       | 8      | 2 ICLK                                                                  | _      |                                                             |  |

| 0008 7368h | ICU    | Interrupt Source Priority Register 104 | IPR104   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7369h | ICU    | Interrupt Source Priority Register 105 | IPR105   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions<br>with 64 or 48 pins.              |  |

| 0008 736Ah | ICU    | Interrupt Source Priority Register 106 | IPR106   | 8       | 8      | 2 ICLK                                                                  |        | Not present in versions with 64 or 48 pins.                 |  |

| 0008 7372h | ICU    | Interrupt Source Priority Register 114 | IPR114   | 8       | 8      | 2 ICLK                                                                  |        |                                                             |  |

| 0008 737Ah | ICU    | Interrupt Source Priority Register 122 | IPR122   | 8       | 8      | 2 ICLK                                                                  | -      |                                                             |  |

| 0008 737Eh | ICU    | Interrupt Source Priority Register 126 | IPR126   | 8       | 8      | 2 ICLK                                                                  |        |                                                             |  |

| 0008 7382h | ICU    | Interrupt Source Priority Register 130 | IPR130   | 8       | 8      | 2 ICLK                                                                  |        |                                                             |  |

| 0008 7385h | ICU    | Interrupt Source Priority Register 133 | IPR133   | 8       | 8      | 2 ICLK                                                                  | _      |                                                             |  |

| 0008 7387h | ICU    | Interrupt Source Priority Register 135 | IPR135   | 8       | 8      | 2 ICLK                                                                  | -      |                                                             |  |

| 0008 7387h | ICU    | Interrupt Source Priority Register 137 | IPR135   | 8       | 8      | 2 ICLK                                                                  | -      |                                                             |  |

|            | ICU    |                                        | IPR137   | 8       | 8      | 2 ICLK                                                                  | -      |                                                             |  |

| 0008 738Bh |        | Interrupt Source Priority Register 139 |          |         |        |                                                                         | -      |                                                             |  |

| 0008 738Dh | ICU    | Interrupt Source Priority Register 141 | IPR141   | 8       | 8      | 2 ICLK                                                                  | 4      |                                                             |  |

| 0008 7391h | ICU    | Interrupt Source Priority Register 145 | IPR145   | 8       | 8      | 2 ICLK                                                                  | -      |                                                             |  |

| 0008 7392h | ICU    | Interrupt Source Priority Register 146 | IPR146   | 8       | 8      | 2 ICLK                                                                  | 4      |                                                             |  |

| 0008 7396h | ICU    | Interrupt Source Priority Register 150 | IPR150   | 8       | 8      | 2 ICLK                                                                  |        |                                                             |  |

| 0008 7397h | ICU    | Interrupt Source Priority Register 151 | IPR151   | 8       | 8      | 2 ICLK                                                                  |        | 1                                                           |  |

## Table 4.1 List of I/O Registers (Address Order) (12/48)

|            | Module |                                                                                          | Register  | Number  | Access    | Number of A                        | ccess States | Module |                                               |

|------------|--------|------------------------------------------------------------------------------------------|-----------|---------|-----------|------------------------------------|--------------|--------|-----------------------------------------------|

| Address    | Symbol | Register Name                                                                            | Symbol    | of Bits | Size      | $\textbf{ICLK} \geq \textbf{PCLK}$ | ICLK < PCLK  | Name   | Remarks                                       |

| 000C 299Eh | GPT5   | General PWM Timer Cycle Setting Buffer<br>Register                                       | GTPBR     | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | GPT    | Not present in version with 64 or 48 pins.    |

| 000C 29A0h | GPT5   | General PWM Timer Cycle Setting Double-<br>Buffer Register                               | GTPDBR    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in versions with 64 or 48 pins.   |

| 000C 29A4h | GPT5   | A/D Converter Start Request Timing Register A                                            | GTADTRA   | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in versions with 64 or 48 pins.   |

| 000C 29A6h | GPT5   | A/D Converter Start Request Timing Buffer<br>Register A                                  | GTADTBRA  | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 29A8h | GPT5   | A/D Converter Start Request Timing Double-<br>Buffer Register A                          | GTADTDBRA | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version<br>with 64 or 48 pins. |

| 000C 29ACh | GPT5   | A/D Converter Start Request Timing Register<br>B                                         | GTADTRB   | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | -      | Not present in version with 64 or 48 pins.    |

| 000C 29AEh | GPT5   | A/D Converter Start Request Timing Buffer<br>Register B                                  | GTADTBRB  | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 29B0h | GPT5   | A/D Converter Start Request Timing Double-<br>Buffer Register B                          | GTADTDBRB | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 29B4h | GPT5   | General PWM Timer Output Negate Control Register                                         | GTONCR    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 29B6h | GPT5   | General PWM Timer Dead Time Control Register                                             | GTDTCR    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 29B8h | GPT5   | General PWM Timer Dead Time Value<br>Register U                                          | GTDVU     | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version<br>with 64 or 48 pins. |

| 000C 29BAh | GPT5   | General PWM Timer Dead Time Value<br>Register D                                          | GTDVD     | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in versions with 64 or 48 pins.   |

| 000C 29BCh | GPT5   | General PWM Timer Dead Time Buffer<br>Register U                                         | GTDBU     | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 29BEh | GPT5   | General PWM Timer Dead Time Buffer<br>Register D                                         | GTDBD     | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 29C0h | GPT5   | General PWM Timer Output Protection<br>Function Status Register                          | GTSOS     | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 29C2h | GPT5   | General PWM Timer Output Protection<br>Function Temporary Release Register               | GTSOTR    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A00h | GPT6   | General PWM Timer I/O Control Register                                                   | GTIOR     | 16      | 8, 16, 32 | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A02h | GPT6   | General PWM Timer Interrupt Output Setting Register                                      | GTINTAD   | 16      | 8, 16, 32 | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A04h | GPT6   | General PWM Timer Control Register                                                       | GTCR      | 16      | 8, 16, 32 | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A06h | GPT6   | General PWM Timer Buffer Enable Register                                                 | GTBER     | 16      | 8, 16, 32 | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A08h | GPT6   | General PWM Timer Count Direction<br>Register                                            | GTUDC     | 16      | 8, 16, 32 | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A0Ah | GPT6   | General PWM Timer Interrupt,<br>A/D Converter Start Request Skipping<br>Setting Register | GTITC     | 16      | 8, 16, 32 | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A0Ch | GPT6   | General PWM Timer Status Register                                                        | GTST      | 16      | 8, 16, 32 | 2 to 5 PCLKA                       | 2, 3 ICLK    | -      | Not present in version with 64 or 48 pins.    |

| 000C 2A0Eh | GPT6   | General PWM Timer Counter                                                                | GTCNT     | 16      | 16        | 2 to 5 PCLKA                       | 2, 3 ICLK    | -      | Not present in version with 64 or 48 pins.    |

| 000C 2A10h | GPT6   | General PWM Timer Compare Capture<br>Register A                                          | GTCCRA    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | -      | Not present in version with 64 or 48 pins.    |

| 000C 2A12h | GPT6   | General PWM Timer Compare Capture<br>Register B                                          | GTCCRB    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | -      | Not present in version with 64 or 48 pins.    |

| 000C 2A14h | GPT6   | General PWM Timer Compare Capture<br>Register C                                          | GTCCRC    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | -      | Not present in version with 64 or 48 pins.    |

| 000C 2A16h | GPT6   | General PWM Timer Compare Capture<br>Register D                                          | GTCCRD    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A18h | GPT6   | General PWM Timer Compare Capture<br>Register E                                          | GTCCRE    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    |        | Not present in version with 64 or 48 pins.    |

| 000C 2A1Ah | GPT6   | General PWM Timer Compare Capture<br>Register F                                          | GTCCRF    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | 1      | Not present in version with 64 or 48 pins.    |

| 000C 2A1Ch | GPT6   | General PWM Timer Cycle Setting Register                                                 | GTPR      | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | -      | Not present in version with 64 or 48 pins.    |

| 000C 2A1Eh | GPT6   | General PWM Timer Cycle Setting Buffer Register                                          | GTPBR     | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | -      | Not present in version with 64 or 48 pins.    |

| 000C 2A20h | GPT6   | General PWM Timer Cycle Setting Double-<br>Buffer Register                               | GTPDBR    | 16      | 16, 32    | 2 to 5 PCLKA                       | 2, 3 ICLK    | 1      | Not present in version with 64 or 48 pins.    |

## Table 4.1 List of I/O Registers (Address Order) (44/48)

### Table 5.4DC Characteristics (3)

Note: Common standard values for conditions not given in the table are listed as "Condition 1" to "Condition 3" below.

Condition 1: VCC = PLLVCC = VCC\_USB = 2.7 to 3.6 V, VSS = PLLVSS = VSS\_USB = AVSS0 = AVSS = VREFL0 = 0 V AVCC0 = AVCC = VREF = 3.0 to 3.6 V, VREFH0 = 3.0 V to AVCC0

Condition 2: VCC = PLLVCC = VCC\_USB = 2.7 to 3.6 V, VSS = PLLVSS = VSS\_USB = AVSS0 = AVSS = VREFL0 = 0 V AVCC0 = AVCC = VREF = 4.0 to 5.5 V, VREFH0 = 4.0 V to AVCC0

Condition 3: VCC = PLLVCC = 4.0 to 5.5 V, VCC\_USB = 3.0 to 3.6 V, VSS = PLLVSS = VSS\_USB = AVSS0 = AVSS = VREFL0 = 0 V AVCC0 = AVCC = VREF = 4.0 to 5.5 V, VREFH0 = 4.0 V to AVCC0

The following relation applies when the USB is in use under condition 1 or condition 2:  $Vcc = PLLVcc = Vcc_USB = 3.0$  to 3.6 V.  $T_a = T_{opr}$ ,  $T_a$  is common to conditions 1 to 3.

|                         | lte                                                | m                                | Symbol              | Min. | Тур. | Max. | Unit     | Test Conditions                   |

|-------------------------|----------------------------------------------------|----------------------------------|---------------------|------|------|------|----------|-----------------------------------|

| Supply current          | During                                             | Max. *2                          | I <sub>CC</sub> *3  | —    | —    | 70   | mA       | ICLK = 100 MHz                    |

| *1                      | operation                                          | Normal *4                        |                     | _    | 40   | —    |          | PCLKA = 100 MHz<br>PCLKB = 50 MHz |

|                         |                                                    | Increased by BGO operation *5    |                     | _    | 15   | —    |          | PCLKC = 100 MHz<br>PCLKD = 50 MHz |

|                         | Sleep mode                                         | •                                |                     |      | 40   | 55   |          | FCLK = 50 MHz                     |

|                         | All-module-cl                                      | ock-stop mode *6                 |                     |      | 20   | 30   |          |                                   |

|                         | During                                             | Software standby mode            |                     | _    | 0.10 | 3    | mA       |                                   |

|                         | standby                                            | Deep software standby mode       |                     | _    | 20   | 60   | μA       |                                   |

| Analog power            | During 12-bit                                      | AI <sub>CC0</sub>                | —                   | 1.5  | 4.2  | mA   |          |                                   |

| supply current          | Programmabl                                        |                                  | _                   | 1    | 1.5  | mA   |          |                                   |

|                         | Window comp                                        |                                  | _                   | 0.5  | 0.7  | mA   |          |                                   |

|                         | Waiting for 12                                     |                                  | _                   | 0.1  | 8    | μA   |          |                                   |

|                         | During 10-bit                                      | AI <sub>CC</sub>                 | _                   | 0.9  | 1.4  | mA   |          |                                   |

|                         | During D/A co                                      |                                  |                     | 0.1  | 4    | μA   |          |                                   |

|                         | Waiting for 10-bit A/D, D/A conversion (all units) |                                  |                     | _    | 0.1  | 4    | μA       |                                   |

| Reference               | During 12-bit                                      | A/D conversion (per unit)        | AI <sub>REFH0</sub> | _    | 1.6  | 2.5  | mA       |                                   |

| power supply<br>current | Waiting for 12                                     | P-bit A/D conversion (all units) |                     | _    | 0.1  | 1.5  | μA       |                                   |

|                         | During 10-bit                                      | A/D conversion (per channel)     | AI <sub>REF</sub>   | _    | 0.2  | 0.3  | mA       |                                   |

|                         | During D/A co                                      | During D/A conversion (per unit) |                     |      | 1    | 1.5  | mA       |                                   |

|                         | Waiting for 10-<br>units)                          |                                  | —                   | 0.1  | 1.2  | μA   |          |                                   |

| VCC rising grad         | VCC rising gradient                                |                                  |                     | —    | —    | 20   | ms/<br>V |                                   |

Note 1. Supply current values are with all output pins unloaded.

Note 2. Measured with clocks supplied to the peripheral functions. This does not include the BGO operation.

Note 3. I<sub>CC</sub> depends on f (ICLK) as follows. (ICLK: PCLK = 8:4)

$I_{CC} \max = 0.6 \times f + 10 \pmod{2}$

$I_{CC}$  typ = 0.3 × f + 10 (normal)

$I_{CC}$  max = 0.45 × f + 10 (sleep mode)

Note 4. Measured with clocks not supplied to the peripheral functions. This does not include the BGO operation.

Note 5. Incremented if data is written to or erased from the on-chip ROM or on-chip data-flash memory for data storage during the program execution.

Note 6. The values are for reference.

#### Table 5.6 Permissible Power Consumption (G version product only)

Note: Common standard values for conditions not given in the table are listed as "Condition 1" to "Condition 3" below.

Condition 1: VCC = PLLVCC = 2.7 to 3.6 V, VSS = PLLVSS = AVSS0 = AVSS = VREFL0 = 0 V AVCC0 = AVCC = 3.0 to 3.6V, VREFH0 = 3.0 V to AVCC0, VREF = 3.0 V to AVCC

Condition 2: VCC = PLLVCC = 2.7 to 3.6 V, VSS = PLLVSS = AVSS = AVSS = VREFL0 = 0V AVCC0 = AVCC = 4.0 to 5.5 V, VREFH0 = 4.0 V to AVCC0, VREF = 4.0 V to AVCC

Condition 3: VCC = PLLVCC = 4.0 to 5.5 V, VSS = PLLVSS = AVSS0 = AVSS = VREFL0 = 0V

AVCC0 = AVCC = 4.0 to 5.5V, VREFH0 = 4.0 V to AVCC0, VREF = 4.0 V to AVCC

Ta = -40 to +105°C. Ta is common to conditions 1 to 3.

| Item                                  | Symbol | Тур. | Max. | Unit | Test Conditions   |

|---------------------------------------|--------|------|------|------|-------------------|

| Total permissible power consumption*1 | Pd     | —    | 345  | mW   | 85°C < Ta ≤ 105°C |

Note: • Please contact Renesas Electronics sales office for derating of operation under Ta = +85°C to +105°C. Derating is the systematic reduction of load for the sake of improved reliability.