Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M0+                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 30MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, POR, PWM, WDT                    |

| Number of I/O              | 42                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                              |

| Data Converters            | A/D 12x12b                                                               |

| Oscillator Type            | External, Internal                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 48-HVQFN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc844m201jhi48e |

### 32-bit Arm Cortex-M0+ microcontroller

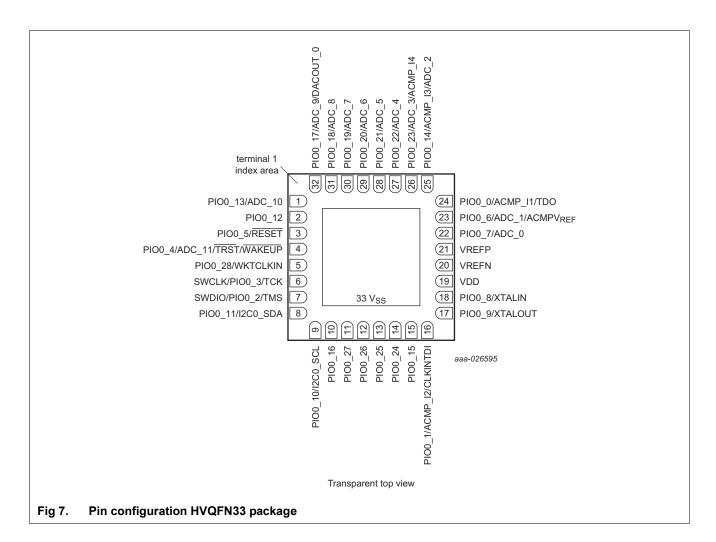

# 7.2 Pin description

The pin description table shows the pin functions that are fixed to specific pins on each package. See <u>Table 4</u>. These fixed-pin functions <u>are selectable</u> through the switch matrix between GPIO and the comparator, ADC, SWD, RESET, and the XTAL pins. By default, the GPIO function is selected except on pins PIO0\_2, PIO0\_3, and PIO0\_5. JTAG functions are available in boundary scan mode only.

Movable functions for the  $I^2C$ , USART, SPI, CTimer, SCT pins, and other peripherals can be assigned through the switch matrix to any pin that is not power or ground in place of the pin's fixed functions.

The following exceptions apply:

Do not assign more than one output to any pin. However, an output and/or one or more inputs can be assigned to a pin. Once any function is assigned to a pin, the pin's GPIO functionality is disabled.

Pin PIO0\_4 triggers a wake-up from deep power-down mode. If the part must wake up from deep power-down mode via an external pin, do not assign any movable function to this pin.

32-bit Arm Cortex-M0+ microcontroller

# Table 4. Pin description

| Table 4. Pin desc | , ipuon |        |         |         |     | <b>D</b> (                    | -    | D                                                                    |

|-------------------|---------|--------|---------|---------|-----|-------------------------------|------|----------------------------------------------------------------------|

| Symbol            | LQFP64  | LQFP48 | HVQFN48 | HVQFN33 |     | Reset<br>state <sup>[1]</sup> | Type | Description                                                          |

| PIO0_31/CAPT_X0   | 13      | 9      | 9       | -       | [5] | I; PU                         | Ю    | PIO0_31 — General-purpose port 0 input/output 31.                    |

|                   |         |        |         |         |     |                               |      | CAPT_X0 — Capacitive Touch X sensor 0.                               |

| PIO1_0/CAPT_X1    | 15      | 11     | 11      | -       | [5] | I; PU                         | Ю    | PIO1_0 — General-purpose port 1 input/output 0.                      |

|                   |         |        |         |         |     |                               |      | CAPT_X1 — Capacitive Touch X sensor 1.                               |

| PIO1_1/CAPT_X2    | 18      | 14     | 14      | -       | [5] | I; PU                         | Ю    | PIO1_1 — General-purpose port 1 input/output 1.                      |

|                   |         |        |         |         |     |                               |      | CAPT_X2 — Capacitive Touch X sensor 2.                               |

| PIO1_2/CAPT_X3    | 20      | 16     | 16      | -       | [5] | I; PU                         | Ю    | PIO1_2 — General-purpose port 1 input/output 2.                      |

|                   |         |        |         |         |     |                               |      | CAPT_X3 — Capacitive Touch X sensor 3.                               |

| PIO1_3/CAPT_X4    | 29      | 21     | 21      | -       | [5] | I; PU                         | Ю    | PIO1_3 — General-purpose port 1 input/output 3.                      |

|                   |         |        |         |         |     |                               |      | CAPT_X4 — Capacitive Touch X sensor 4.                               |

| PIO1_4/CAPT_X5    | 31      | 23     | 23      | -       | [5] | I; PU                         | Ю    | PIO1_4 — General-purpose port 1 input/output 4.                      |

|                   |         |        |         |         |     |                               |      | CAPT_X5 — Capacitive Touch X sensor 5.                               |

| PIO1_5/CAPT_X6    | 35      | 27     | 27      | -       | [5] | I; PU                         | Ю    | PIO1_5 — General-purpose port 1 input/output 5.                      |

|                   |         |        |         |         |     |                               |      | CAPT_X6 — Capacitive Touch X sensor 6.                               |

| PIO1_6/CAPT_X7    | 38      | 28     | 28      | -       | [5] | I; PU                         | Ю    | PIO1_6 — General-purpose port 1 input/output 6.                      |

|                   |         |        |         |         |     |                               |      | CAPT_X7 — Capacitive Touch X sensor 7.                               |

| PIO1_7/CAPT_X8    | 47      | 35     | 35      | -       | [5] | I; PU                         | Ю    | PIO1_7 — General-purpose port 1 input/output 7.                      |

|                   |         |        |         |         |     |                               |      | CAPT_X8 — Capacitive Touch X sensor 8.                               |

| PIO1_8/CAPT_YL    | 1       | 1      | 1       | -       | [5] | I; PU                         | Ю    | PIO1_8 — General-purpose port 1 input/output 8.                      |

|                   |         |        |         |         |     |                               |      | CAPT_YL — Capacitive Touch Y Low.                                    |

| PIO1_9/CAPT_YH    | 3       | 3      | 3       | -       | [5] | I; PU                         | Ю    | PIO1_9 — General-purpose port 1 input/output 9.                      |

|                   |         |        |         |         |     |                               |      | CAPT_YH — Capacitive Touch Y High.                                   |

| PIO1_10           | 64      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_10 — General-purpose port 1 input/output 10.                    |

| PIO1_11           | 62      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_11 — General-purpose port 1 input/output 11.                    |

| PIO1_12           | 9       | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_12 — General-purpose port 1 input/output 12.                    |

| PIO1_13           | 11      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_13 — General-purpose port 1 input/output 13.                    |

| PIO1_14           | 22      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_14 — General-purpose port 1 input/output 14.                    |

| PIO1_15           | 24      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_15 — General-purpose port 1 input/output 15.                    |

| PIO1_16           | 36      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_16 — General-purpose port 1 input/output 16.                    |

| PIO1_17           | 37      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_17 — General-purpose port 1 input/output 17.                    |

| PIO1_18           | 43      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_18 — General-purpose port 1 input/output 18.                    |

| PIO1_19           | 44      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_19 — General-purpose port 1 input/output 19.                    |

| PIO1_20           | 56      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_20 — General-purpose port 1 input/output 20.                    |

| PIO1_21           | 59      | -      | -       | -       | [5] | I; PU                         | Ю    | PIO1_21 — General-purpose port 1 input/output 21.                    |

| $V_{DD}$          | 7;26;39 | 29     | 29      | 19      |     | -                             | -    | Supply voltage for the I/O pad ring, the and core voltage regulator. |

| $V_{DDA}$         | 52      | 40     | 40      |         |     |                               |      | Analog supply voltage.                                               |

| $V_{SS}$          | 8;25;40 | 30     | 30      | 33[11]  |     | -                             | -    | Ground.                                                              |

Table 5. Movable functions (assign to pins PIO0\_0 to PIO0\_31, PIO1\_0 to PIO1\_21 through switch matrix)

| Function name | Туре | Description                                                                         |

|---------------|------|-------------------------------------------------------------------------------------|

| SPIx_SSEL0    | I/O  | Slave select 0 for SPI0 and SPI1.                                                   |

| SPIx_SSEL1    | I/O  | Slave select 1 for SPI0 and SPI1.                                                   |

| SPIx_SSEL2    | I/O  | Slave select 2 for SPI0 and SPI1.                                                   |

| SPIx_SSEL3    | I/O  | Slave select 3 for SPI0 and SPI1.                                                   |

| SCT_PIN0      | I    | Pin input 0 to the SCT input multiplexer.                                           |

| SCT_PIN1      | I    | Pin input 1 to the SCT input multiplexer.                                           |

| SCT_PIN2      | I    | Pin input 2 to the SCT input multiplexer.                                           |

| SCT_PIN3      | I    | Pin input 3 to the SCT input multiplexer.                                           |

| SCT_OUT0      | 0    | SCT output 0.                                                                       |

| SCT_OUT1      | 0    | SCT output 1.                                                                       |

| SCT_OUT2      | 0    | SCT output 2.                                                                       |

| SCT_OUT3      | 0    | SCT output 3.                                                                       |

| SCT_OUT4      | 0    | SCT output 4.                                                                       |

| SCT_OUT5      | 0    | SCT output 5.                                                                       |

| I2Cx_SDA      | I/O  | I <sup>2</sup> C1, I <sup>2</sup> C2, and I <sup>2</sup> C3 bus data input/output.  |

| I2Cx_SCL      | I/O  | I <sup>2</sup> C1, I <sup>2</sup> C2, and I <sup>2</sup> C3 bus clock input/output. |

| ACMP_O        | 0    | Analog comparator output.                                                           |

| CLKOUT        | 0    | Clock output.                                                                       |

| GPIO_INT_BMAT | 0    | Output of the pattern match engine.                                                 |

| T0_MAT0       | 0    | Timer Match channel 0.                                                              |

| T0_MAT1       | 0    | Timer Match channel 1.                                                              |

| T0_MAT2       | 0    | Timer Match channel 2.                                                              |

| T0_MAT3       | 0    | Timer Match channel 3.                                                              |

| T0_CAP0       | I    | Timer Capture channel 0.                                                            |

| T0_CAP1       | I    | Timer Capture channel 1.                                                            |

| T0_CAP2       | I    | Timer Capture channel 2.                                                            |

#### 32-bit Arm Cortex-M0+ microcontroller

# 8.13.2 DMA trigger input MUX (TRIGMUX)

Each DMA trigger is connected to a programmable multiplexer which connects the trigger input to one of multiple trigger sources. Each multiplexer supports the same trigger sources: the ADC sequence interrupts, the SCT DMA request lines, and pin interrupts PININT0 and PININT1, and the outputs of the DMA triggers 0 and 1 for chaining DMA triggers.

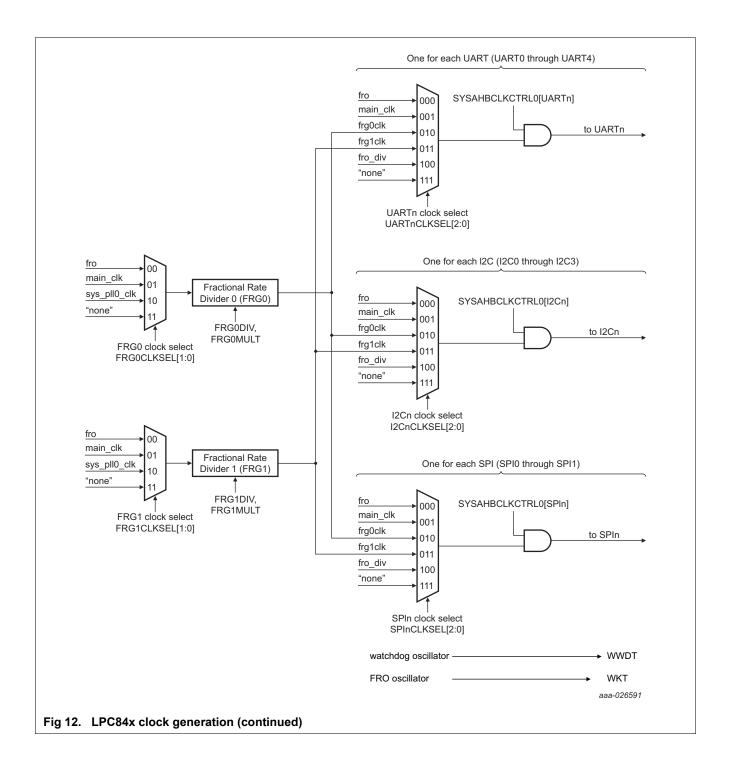

# 8.14 USART0/1/2/3/4

All USART functions are movable functions and are assigned to pins through the switch matrix.

#### 8.14.1 Features

- Maximum bit rates of 1.875 Mbit/s in asynchronous mode and 10 Mbit/s in synchronous mode for USART functions connected to all digital pins except the open-drain pins.

- 7, 8, or 9 data bits and 1 or 2 stop bits

- Synchronous mode with master or slave operation. Includes data phase selection and continuous clock option.

- Multiprocessor/multidrop (9-bit) mode with software address compare. (RS-485 possible with software address detection and transceiver direction control.)

- Parity generation and checking: odd, even, or none.

- · One transmit and one receive data buffer.

- RTS/CTS for hardware signaling for automatic flow control. Software flow control can be performed using Delta CTS detect, Transmit Disable control, and any GPIO as an RTS output.

- · Received data and status can optionally be read from a single register

- · Break generation and detection.

- Receive data is 2 of 3 sample "voting". Status flag set when one sample differs.

- Built-in Baud Rate Generator.

- A fractional rate divider is shared among all UARTs.

- Interrupts available for Receiver Ready, Transmitter Ready, Receiver Idle, change in receiver break detect, Framing error, Parity error, Overrun, Underrun, Delta CTS detect, and receiver sample noise detected.

- Separate data and flow control loopback modes for testing.

- Baud rate clock can also be output in asynchronous mode.

#### 8.15 SPI0/1

All SPI functions are movable functions and are assigned to pins through the switch matrix.

## 8.15.1 Features

Maximum data rates of up to 30 Mbit/s in master mode and up to 18 Mbit/s in slave mode for SPI functions connected to all digital pins except the open-drain pins.

#### 32-bit Arm Cortex-M0+ microcontroller

- Supports CPU PIO or DMA back-to-back transfer.

- Accept any size of data width per write: 8, 16 or 32-bit.

- 8-bit write: 1-cycle operation.

- 16-bit write: 2-cycle operation (8-bit x 2-cycle).

- 32-bit write: 4-cycle operation (8-bit x 4-cycle).

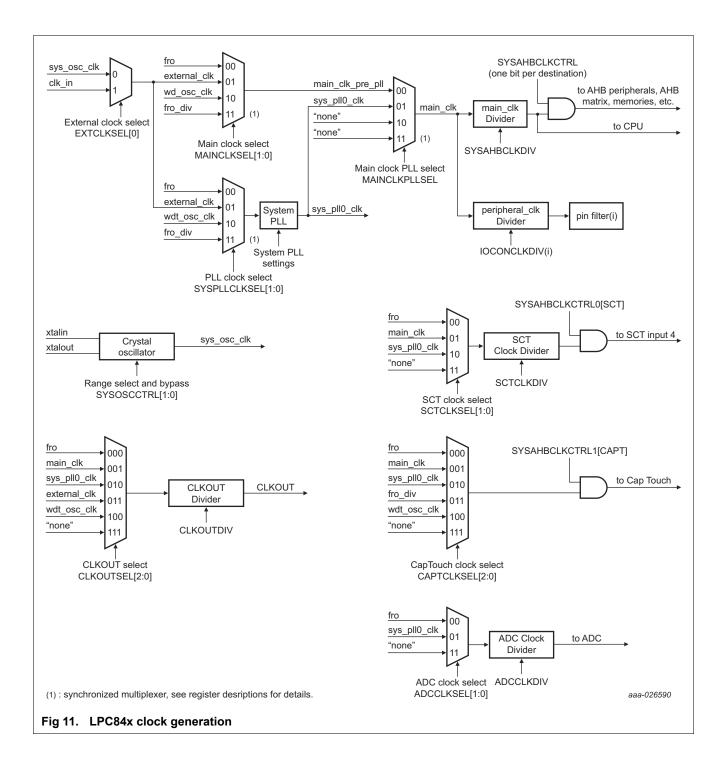

# 8.27 Clocking and power control

## 8.27.1 Crystal and internal oscillators

The LPC84x include four independent oscillators:

- 1. The crystal oscillator (SysOsc) operating at frequencies between 1 MHz and 25 MHz.

- 2. Free Running Oscillator.

- 3. Watchdog Oscillator

- 4. Low Power Oscillator

Each oscillator, except the low-frequency oscillator, can be used for more than one purpose as required in a particular application.

Following reset, the LPC84x operates from the FRO until switched by software allowing the part to run without any external crystal and the bootloader code to operate at a known frequency.

See Figure 11 for an overview of the LPC84x clock generation.

### 8.27.1.1 Free Running Oscillator (FRO)

The FRO oscillator provides the default clock at reset and provides a clean system clock shortly after the supply pins reach operating voltage.

- This oscillator provides a selectable 18 MHz, 24 MHz, and 30 MHz outputs that can be used as a system clock. Also, these outputs can be divided down to 1.125 MHz, 1.5 MHz, 1.875 MHz, 9 MHz, 12 MHz, and 15 MHz for system clock.

- The FRO is trimmed to ±1 % accuracy over the entire voltage and temperature range of 0 C to 70 C.

- By default, the fro\_oscout is 24 MHz and is divided by 2 to provide a default system (CPU) clock frequency of 12 MHz.

### 8.27.1.2 Crystal Oscillator (SysOsc)

The crystal oscillator can be used as the clock source for the CPU, with or without using the PLL.

The SysOsc operates at frequencies of 1 MHz to 25 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the system PLL.

### 8.27.1.3 Internal Low-power Oscillator and Watchdog Oscillator (WDOsc)

The nominal frequency of the WDOsc is programmable between 9.4 kHz and 2.3 MHz. The frequency spread over silicon process variations is  $\pm$  40%.

The WDOsc is a dedicated oscillator for the windowed WWDT.

**NXP Semiconductors**

### 32-bit Arm Cortex-M0+ microcontroller

### 8.27.5.1 Sleep mode

When sleep mode is entered, the clock to the core is stopped. Resumption from the sleep mode does not need any special sequence but re-enabling the clock to the Arm core.

In sleep mode, execution of instructions is suspended until either a reset or interrupt occurs. Peripheral functions continue operation during sleep mode and may generate interrupts to cause the processor to resume execution. sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

### 8.27.5.2 Deep-sleep mode

In deep-sleep mode, the LPC84x core is in sleep mode and all peripheral clocks and all clock sources are off except for the FRO and watchdog oscillator or low-power oscillator if selected. The FRO output is disabled. In addition, all analog blocks are shut down and the flash is in standby mode. In deep-sleep mode, the application can keep the watchdog oscillator and the BOD circuit running for self-timed wake-up and BOD protection.

The LPC84x can wake up from deep-sleep mode via a reset, digital pins selected as inputs to the pin interrupt block, a watchdog timer interrupt, an interrupt from Capacitive Touch, or an interrupt from the USART (if the USART is configured in synchronous slave mode), the SPI, or the I2C blocks (in slave mode).

Any interrupt used for waking up from deep-sleep mode must be enabled in one of the SYSCON wake-up enable registers and the NVIC.

Deep-sleep mode saves power and allows for short wake-up times.

#### 8.27.5.3 Power-down mode

In power-down mode, the LPC84x is in sleep mode and all peripheral clocks and all clock sources are off except for watchdog oscillator or low-power oscillator if selected. In addition, all analog blocks and the flash are shut down. In power-down mode, the application can keep the watchdog oscillator and the BOD circuit running for self-timed wake-up and BOD protection.

The LPC84x can wake up from power-down mode via a reset, digital pins selected as inputs to the pin interrupt block, a watchdog timer interrupt, an interrupt from Capacitive Touch, or an interrupt from the USART (if the USART is configured in synchronous slave mode), the SPI, or the I2C blocks (in slave mode).

Any interrupt used for waking up from power-down mode must be enabled in one of the SYSCON wake-up enable registers and the NVIC.

Power-down mode reduces power consumption compared to deep-sleep mode at the expense of longer wake-up times.

### 8.27.5.4 Deep power-down mode

In deep power-down mode, power is shut off to the entire chip except for the WAKEUP pin and the self-wake-up timer. The LPC84x can wake up from deep power-down mode via the WAKEUP pin, RESET pin, or without an external signal by using the time-out of the self-wake-up timer (see Section 8.22).

#### 32-bit Arm Cortex-M0+ microcontroller

# 8.28.3 Code security (Code Read Protection - CRP)

CRP provides different levels of security in the system so that access to the on-chip flash and use of the Serial Wire Debugger (SWD) and In-System Programming (ISP) can be restricted. Programming a specific pattern into a dedicated flash location invokes CRP. IAP commands are not affected by the CRP.

In addition, ISP entry via the ISP entry pin can be disabled without enabling CRP. For details, see the *LPC84x user manual*.

There are three levels of Code Read Protection:

- CRP1 disables access to the chip via the SWD and allows partial flash update (excluding flash sector 0) using a limited set of the ISP commands. This mode is useful when CRP is required and flash field updates are needed but all sectors cannot be erased.

- 2. CRP2 disables access to the chip via the SWD and only allows full flash erase and update using a reduced set of the ISP commands.

- 3. Running an application with level CRP3 selected, fully disables any access to the chip via the SWD pins and the ISP. This mode effectively disables ISP override using the ISP entry pin as well. If necessary, the application must provide a flash update mechanism using IAP calls or using a call to the reinvoke ISP command to enable flash update via the USART.

#### **CAUTION**

If level three Code Read Protection (CRP3) is selected, no future factory testing can be performed on the device.

In addition to the three CRP levels, sampling of the ISP entry pin for valid user code can be disabled. For details, see the *LPC84x user manual*.

## 8.28.4 APB interface

The APB peripherals are located on one APB bus.

### 8.28.5 **AHBLite**

The AHBLite connects the CPU bus of the Arm Cortex-M0+ to the flash memory, the main static RAM, the CRC, the DMA, the ROM, and the APB peripherals.

# 32-bit Arm Cortex-M0+ microcontroller

# 9. Limiting values

Table 9. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol               | Parameter                               | Conditions                                                       |               | Min  | Max      | Unit |

|----------------------|-----------------------------------------|------------------------------------------------------------------|---------------|------|----------|------|

| $V_{DD}$             | supply voltage (core and external rail) |                                                                  | [2]           | -0.5 | +4.6     | V    |

| $V_{DDA}$            | Analog supply voltage                   | on pin VDDA                                                      |               | -0.5 | +4.6     | V    |

| V <sub>ref</sub>     | reference voltage                       | on pin VREFP                                                     |               | -0.5 | $V_{DD}$ | V    |

| VI                   | input voltage                           | 5 V tolerant I/O pins; V <sub>DD</sub> ≥ 1.8 V                   | [3][4]        | -0.5 | +5.5     | V    |

|                      |                                         | on I2C open-drain pins                                           | [5]           | -0.5 | +5.5     | V    |

|                      |                                         | 3 V tolerant I/O pin ACMPV <sub>REF</sub>                        | [6]           | -0.5 | +3.6     | V    |

| V <sub>IA</sub>      | analog input voltage                    | on digital pins configured for an analog function                | [7][8]<br>[9] | -0.5 | +4.6     | V    |

| V <sub>i(xtal)</sub> | crystal input voltage                   |                                                                  | [2]           | -0.5 | +2.5     | V    |

| I <sub>DD</sub>      | supply current                          | per supply pin (LQFP64)                                          |               | -    | 100      | mA   |

| ( )                  |                                         | per supply pin (LQFP48,<br>HVQFN48)                              |               | -    | 75       |      |

|                      |                                         | per supply pin (HVQFN33)                                         |               | -    | 50       |      |

| I <sub>SS</sub>      |                                         | -                                                                | 100           | mA   |          |      |

|                      |                                         | per ground pin (LQFP48,<br>HVQFN48)                              |               | -    | 75       |      |

|                      |                                         | per ground pin (HVQFN33)                                         |               | -    | 100      |      |

| I <sub>latch</sub>   | I/O latch-up current                    | $-(0.5V_{DD}) < V_{I} < (1.5V_{DD});$<br>$T_{j} < 125 ^{\circ}C$ |               | -    | 100      | mA   |

| T <sub>stg</sub>     | storage temperature                     |                                                                  | [10]          | -65  | +150     | °C   |

| T <sub>j(max)</sub>  | maximum junction temperature            |                                                                  |               | -    | 150      | °C   |

- [3] IDD measurements were performed with all pins configured as GPIO outputs driven LOW and pull-up resistors disabled.

- [4] FRO enabled; system oscillator disabled; system PLL disabled.

- [5] BOD disabled.

- [6] All peripherals disabled in the SYSAHBCLKCTRL register. Peripheral clocks disabled in system configuration block.

- [7] All oscillators and analog blocks turned off.

- [8] WAKEUP pin pulled HIGH externally.

- [9] Tested in production, VDD = 3.6 V.

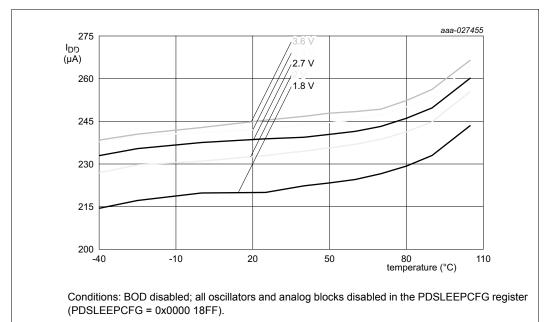

Fig 16. Deep-sleep mode: Typical supply current  $I_{DD}$  versus temperature for different supply voltages  $V_{DD}$

# 14. Application information

# 14.1 Start-up behavior

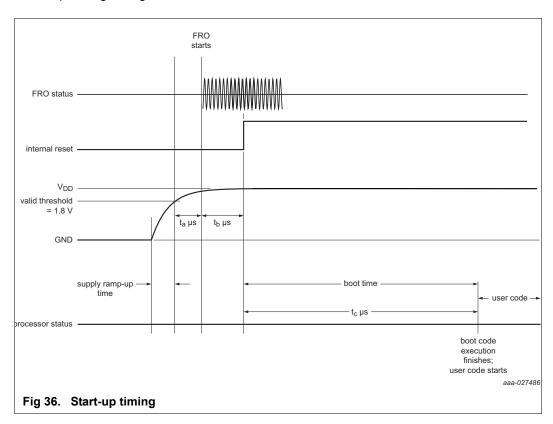

<u>Figure 36</u> shows the start-up timing after reset. The FRO 12 MHz oscillator provides the default clock at Reset and provides a clean system clock shortly after the supply pins reach operating voltage.

Table 33. Typical start-up timing parameters

| Parameter      | Description                | Value   |

|----------------|----------------------------|---------|

| t <sub>a</sub> | FRO start time             | ≤ 26 μs |

| t <sub>b</sub> | Internal reset de-asserted | 101 μs  |

| t <sub>c</sub> | Boot time                  | 51 μs   |

### 32-bit Arm Cortex-M0+ microcontroller

# 14.2 XTAL oscillator

In the XTAL oscillator circuit, only the crystal (XTAL) and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally on XTALIN and XTALOUT. See <u>Figure 37</u>.

For best results, it is very critical to select a matching crystal for the on-chip oscillator. Load capacitance (CL), series resistance (RS), and drive level (DL) are important parameters to consider while choosing the crystal. After selecting the proper crystal, the external load capacitor  $C_{X1}$  and  $C_{X2}$  values can also be generally determined by the following expression:

$$C_{X1} = C_{X2} = 2C_L - (C_{Pad} + C_{Parasitic})$$

Where:

C<sub>I</sub> - Crystal load capacitance

C<sub>Pad</sub> - Pad capacitance of the XTALIN and XTALOUT pins (~3 pF).

C<sub>Parasitic</sub> – Parasitic or stray capacitance of external circuit.

Although  $C_{\text{Parasitic}}$  can be ignored in general, the actual board layout and placement of external components influences the optimal values of external load capacitors. Therefore, it is recommended to fine tune the values of external load capacitors on actual hardware board to get the accurate clock frequency. For fine tuning, measure the clock on the XTALOUT pin and optimize the values of external load capacitors for minimum frequency deviation.

#### 32-bit Arm Cortex-M0+ microcontroller

# 14.2.1 XTAL Printed Circuit Board (PCB) design guidelines

- Connect the crystal and external load capacitors on the PCB as close as possible to the oscillator input and output pins of the chip.

- The length of traces in the oscillation circuit should be as short as possible and must not cross other signal lines.

- Ensure that the load capacitors CX1, CX2, and CX3, in case of third overtone crystal usage, have a common ground plane.

- Loops must be made as small as possible to minimize the noise coupled in through the PCB and to keep the parasitics as small as possible.

- · Lay out the ground (GND) pattern under crystal unit.

- Do not lay out other signal lines under crystal unit for multi-layered PCB.

# 14.2.2 XTAL input

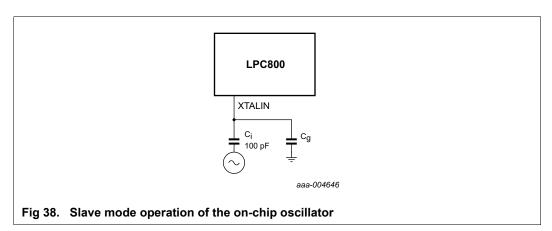

The input voltage to the on-chip oscillators is limited to 1.95 V. If the oscillator is driven by a clock in slave mode, it is recommended to couple the input through a capacitor with  $C_i$  = 100 pF. To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mV(RMS) is needed.

In slave mode the input clock signal should be coupled with a capacitor of 100 pF ( $\underline{\text{Figure 38}}$ ), with an amplitude between 200 mV (RMS) and 1000 mV (RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

# 14.3 Connecting power, clocks, and debug functions

<u>Figure 39</u> shows the basic board connections used to power the LPC84x, connect the external crystal, and provide debug capabilities via the serial wire port.

# 32-bit Arm Cortex-M0+ microcontroller

# 14.6 Pin states in different power modes

Table 35. Pin states in different power modes

| Pin                        | Active                        | Sleep                    | Deep-sleep/power-<br>down | Deep power-down                                                                                                                                 |  |

|----------------------------|-------------------------------|--------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIOn_m pins (not I2C)      | As configured in the enabled. | e IOCON∐. Defau          | lt: internal pull-up      | Floating.                                                                                                                                       |  |

| Open-drain<br>I2C-bus pins | As configured in th           | e IOCON <sup>[1]</sup> . | Floating.                 |                                                                                                                                                 |  |

| RESET                      | Reset function ena enabled.   | bled. Default: inpu      | t, internal pull-up       | Reset function disabled; floating; if the part is in deep power-down mode, the RESET pin needs an external pull-up to reduce power consumption. |  |

| WAKEUP                     | As configured in th           | e IOCON[1]. WAKE         | UP function inactive.     | Wake-up function enabled; can be disabled by software.                                                                                          |  |

<sup>[1]</sup> Default and programmed pin states are retained in sleep, deep-sleep, and power-down modes.

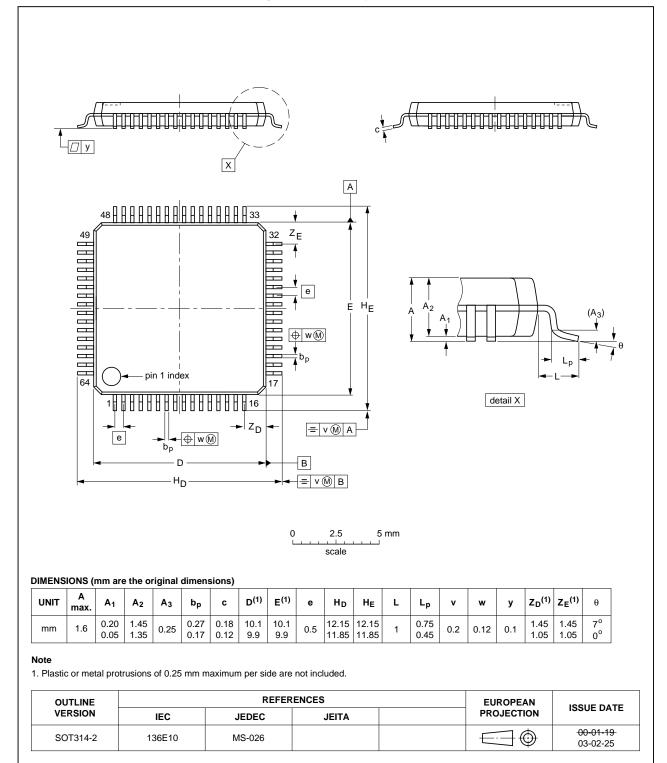

# LQFP64: plastic low profile quad flat package; 64 leads; body 10 x 10 x 1.4 mm

SOT314-2

Fig 41. Package outline SOT314-2 (LQFP64)

32-bit Arm Cortex-M0+ microcontroller

# 22. Contents

| 1              | General description                                      | . 1      | 8.20.1   | Features                                   | 27 |

|----------------|----------------------------------------------------------|----------|----------|--------------------------------------------|----|

| 2              | Features and benefits                                    |          | 8.21     | Windowed WatchDog Timer (WWDT)             |    |

|                |                                                          |          | 8.21.1   | Features                                   |    |

| 3              | Applications                                             |          | 8.22     | Self-Wake-up Timer (WKT)                   |    |

| 4              | Ordering information                                     |          | 8.22.1   | Features                                   |    |

| 4.1            | Ordering options                                         | . 4      | 8.23     | Analog comparator (ACMP)                   |    |

| 5              | Marking                                                  | . 5      | 8.23.1   | Features                                   |    |

| 6              | Block diagram                                            | . 6      | 8.24     | Analog-to-Digital Converter (ADC)          |    |

| 7              | Pinning information                                      |          | 8.24.1   | Features                                   |    |

| 7.1            | Pinning                                                  |          | 8.25     | Digital-to-Analog Converter (DAC)          |    |

| 7.2            | Pin description                                          |          | 8.25.1   | Features                                   |    |

| 8              |                                                          |          | 8.26     | CRC engine                                 |    |

| -              | Functional description                                   |          | 8.26.1   | Features                                   |    |

| 8.1            | Arm Cortex-M0+ core                                      |          | 8.27     | Clocking and power control                 | 31 |

| 8.2            | On-chip flash program memory                             |          | 8.27.1   | Crystal and internal oscillators           |    |

| 8.3            | On-chip SRAM                                             |          | 8.27.1.1 |                                            |    |

| 8.4            | FAIM memory                                              |          | 8.27.1.2 |                                            | 31 |

| 8.5            | On-chip ROM                                              |          | 8.27.1.3 |                                            |    |

| 8.6            | Memory map                                               |          |          | Oscillator (WDOsc)                         | 31 |

| 8.7            | Nested Vectored Interrupt Controller (NVIC) .            |          | 8.27.2   | Clock input                                | 32 |

| 8.7.1          | Features                                                 |          | 8.27.3   | System PLL                                 | 32 |

| 8.7.2          | Interrupt sources                                        |          | 8.27.4   | Clock output                               |    |

| 8.8            | System tick timer                                        |          | 8.27.5   | Power control                              | 35 |

| 8.9            | I/O configuration                                        |          | 8.27.5.1 | Sleep mode                                 | 36 |

| 8.9.1          | Standard I/O pad configuration                           |          | 8.27.5.2 | Deep-sleep mode                            | 36 |

| 8.10           | Switch Matrix (SWM)                                      |          | 8.27.5.3 | Power-down mode                            | 36 |

| 8.11           | Fast General-Purpose parallel I/O (GPIO)                 |          | 8.27.5.4 | Deep power-down mode                       | 36 |

| 8.11.1<br>8.12 | Features                                                 |          | 8.27.6   | Wake-up process                            | 38 |

| 8.12.1         | Pin interrupt/pattern match engine                       |          | 8.28     | System control                             | 39 |

| 8.13           | Features                                                 |          | 8.28.1   | Reset                                      | 39 |

| 8.13.1         | Features                                                 |          | 8.28.2   | Brownout detection                         | 39 |

| 8.13.2         |                                                          |          | 8.28.3   | Code security (Code Read Protection - CRP) | 40 |

| 8.14           | DMA trigger input MUX (TRIGMUX)<br>USART0/1/2/3/4        | 23<br>22 | 8.28.4   | APB interface                              | 40 |

| 8.14.1         | Features                                                 |          | 8.28.5   | AHBLite                                    |    |

| 8.15           | SPI0/1                                                   |          | 8.29     | Emulation and debugging                    | 41 |

| 8.15.1         | Features                                                 |          | 9        | Limiting values                            | 42 |

| 8.16           | I <sup>2</sup> C-bus interface (I <sup>2</sup> C0/1/2/3) |          | 10       | Thermal characteristics                    | 44 |

| 8.16.1         | Features                                                 |          |          | Static characteristics                     |    |

| 8.17           | Capacitive Touch Interface                               |          | 11.1     | General operating conditions               |    |

| 8.18           | SCTimer/PWM                                              |          | 11.1     | Power-up ramp conditions                   |    |

| 8.18.1         | Features                                                 |          | 11.3     | Power consumption                          | 40 |

| 8.18.2         | SCTimer/PWM input MUX (INPUT MUX)                        |          | 11.4     | Peripheral power consumption               |    |

| 8.19           | CTIMER                                                   |          | 11.4     | Pin characteristics                        |    |

| 8.19.1         | General-purpose 32-bit timers/external event             | 20       | 11.5.1   | Electrical pin characteristics             |    |

| 5.15.1         | counter                                                  | 26       |          |                                            |    |

| 8.19.2         | Features                                                 |          | 12       | Dynamic characteristics                    |    |

| 8.20           | Multi-Rate Timer (MRT)                                   |          | 12.1     | Flash memory                               |    |

| 5.20           |                                                          |          | 12.2     | FRO                                        | 60 |

continued >>