Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                           |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12dg128cfue |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|------------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V01.00            | 18 Jun<br>2001   | 18 June<br>2001   |        | Initial version (parent doc v2.03 dug for dp256).                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V01.01            | 23 July<br>2001  | 23 July<br>2001   |        | Updated version after review                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V01.02            | 23 Sep<br>2001   | 23 Sep<br>2001    |        | Changed Partname, added pierce mode, updated electrical<br>characteristics<br>some minor corrections                                                                                                                                                                                                                                                                                                                                                                                             |

| V01.03            | 12 Oct<br>2001   | 12 Oct<br>2001    |        | Replaced Star12 by HCS12                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V01.04            | 27 Feb<br>2002   | 27 Feb<br>2002    |        | Updated electrical spec after MC-Qualification (IOL/IOH), Data for<br>Pierce, NVM reliability<br>New document numbering. Corrected Typos                                                                                                                                                                                                                                                                                                                                                         |

| V01.05            | 4 Mar<br>2002    | 4 Mar<br>2002     |        | Increased VDD to 2.35V, removed min. oscillator startup<br>Removed Document order number except from Cover Sheet                                                                                                                                                                                                                                                                                                                                                                                 |

| V01.06            | 8 July<br>2002   | 22 July<br>2002   |        | Added:<br>Pull-up columns to signal table,<br>example for PLL Filter calculation,<br>Thermal values for junction to board and package,<br>BGND pin pull-up<br>Part Order Information<br>Global Register Table<br>Chip Configuration Summary<br>Modified:<br>Reduced Wait and Run IDD values<br>Mode of Operation chapter<br>changed leakage current for ADC inputs down to +-1uA<br>Corrected:<br>Interrupt vector table enable register inconsistencies<br>PCB layout for 80QFP VREGEN position |

| V02.00            | 11 Jan<br>2002   | 11 Jan<br>2002    |        | NEW MASKSET<br>Changed part number from DTB128 to DT128<br>Functional Changes:<br>ROMCTL changes in Emulation Mode<br>80 Pin Byteflight package Option available<br>Flash with 2 Bit Backdoor Key Enable<br>Additional CAN0 routing to PJ7,6<br>Improved BDM with sync and acknowledge capabilities<br>New Part ID number<br>Improvements:<br>Significantly improved NVM reliability data<br>Corrections:<br>Interrupt vector Table                                                              |

| V02.01            | 01 Feb<br>2002   | 01 Feb<br>2002    |        | Updated Block User Guide versions in preface<br>Updated Appendix A Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                    |

# **Derivative Differences and Document References**

## **Derivative Differences**

(**Table 0-1**) and (**Table 0-2**) show the availability of peripheral modules on the various derivatives. For details about the compatibility within the MC9S12D-Family refer also to engineering bulletin EB386.

| Modules       | MC9S12DT128E <sup>3</sup><br>MC9S12DT128<br>SC515849 <sup>4</sup><br>SC101161DT <sup>5</sup><br>SC102205 <sup>6</sup> | MC9S12DG128E <sup>3</sup><br>MC9S12DG128<br>SC515847 <sup>4</sup><br>SC101161DG <sup>5</sup><br>SC102203 <sup>6</sup> | MC9S12DJ128E <sup>3</sup><br>MC9S12DJ128<br>SC515848 <sup>4</sup><br>SC101161DJ <sup>5</sup><br>SC102204 <sup>6</sup> | MC9S12A128                            |

|---------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| # of CANs     | 3                                                                                                                     | 2                                                                                                                     | 2                                                                                                                     | 0                                     |

| CAN4          | 1                                                                                                                     | 1                                                                                                                     | 1                                                                                                                     | X                                     |

| CAN1          | 1                                                                                                                     | X                                                                                                                     | X                                                                                                                     | X                                     |

| CAN0          | 1                                                                                                                     | 1                                                                                                                     | ✓                                                                                                                     | X                                     |

| J1850/BDLC    | ×                                                                                                                     | ×                                                                                                                     | ✓                                                                                                                     | X                                     |

| IIC           | 1                                                                                                                     | ✓                                                                                                                     | ✓                                                                                                                     | 1                                     |

| Byteflight    | ×                                                                                                                     | X                                                                                                                     | X                                                                                                                     | X                                     |

| Package       | 112 LQFP                                                                                                              | 112 LQFP/80 QFP <sup>2</sup>                                                                                          | 112 LQFP/80 QFP <sup>2</sup>                                                                                          | 112 LQFP/80 QFP <sup>2</sup>          |

| Package Code  | PV                                                                                                                    | PV/FU                                                                                                                 | PV/FU                                                                                                                 | PV/FU                                 |

| Mask set      | 1L40K <sup>3</sup> , 3L40K,<br>0L94R, 4L40K <sup>4</sup> ,<br>1L59W <sup>5</sup> , 5L40K <sup>6</sup> ,<br>2L94R      | 1L40K <sup>3</sup> , 3L40K,<br>0L94R, 4L40K <sup>4</sup> ,<br>1L59W <sup>5</sup> , 5L40K <sup>6</sup> ,<br>2L94R      | 1L40K <sup>3</sup> , 3L40K,<br>0L94R, 4L40K <sup>4</sup> ,<br>1L59W <sup>5</sup> , 5L40K <sup>6</sup> ,<br>2L94R      | 3L40K, 0L94R,<br>2L94R, 1L59W         |

| Temp Options  | M, V, C                                                                                                               | M, V, C                                                                                                               | M, V, C                                                                                                               | С                                     |

| AEC qualified | Yes                                                                                                                   | Yes                                                                                                                   | Yes                                                                                                                   | No                                    |

| Notes         | An errata exists contact Sales Office                                                                                 | An errata exists contact Sales Office                                                                                 | An errata exists contact Sales Office                                                                                 | An errata exists contact Sales Office |

Table 0-1 Derivative Differences<sup>1</sup>

## Table 0-2 Derivative Differences for MC9S12DB128<sup>1</sup>

| Modules    | MC9S12DB128<br>SC515846 <sup>4</sup><br>SC102202 <sup>6</sup> | MC9S12DB128<br>SC515846 <sup>4</sup><br>SC102202 <sup>6</sup> |

|------------|---------------------------------------------------------------|---------------------------------------------------------------|

| # of CANs  | 2                                                             | 0                                                             |

| CAN4       | 1                                                             | ×                                                             |

| CAN1       | X                                                             | X                                                             |

| CAN0       | ✓                                                             | X                                                             |

| J1850/BDLC | X                                                             | X                                                             |

| liC        | X                                                             | X                                                             |

| Byteflight | $\checkmark$                                                  | ✓                                                             |

| Package    | 112 LQFP                                                      | 80 QFP <sup>2</sup>                                           |

Device User Guide — 9S12DT128DGV2/D V02.17

# **Section 1 Introduction**

# 1.1 Overview

The MC9S12DT128 microcontroller unit (MCU) is a 16-bit device composed of standard on-chip peripherals including a 16-bit central processing unit (HCS12 CPU), 128K bytes of Flash EEPROM, 8K bytes of RAM, 2K bytes of EEPROM, two asynchronous serial communications interfaces (SCI), two serial peripheral interfaces (SPI), an 8-channel IC/OC enhanced capture timer, two 8-channel, 10-bit analog-to-digital converters (ADC), an 8-channel pulse-width modulator (PWM), a digital Byte Data Link Controller (BDLC), 29 discrete digital I/O channels (Port A, Port B, Port K and Port E), 20 discrete digital I/O lines with interrupt and wakeup capability, three CAN 2.0 A, B software compatible modules (MSCAN12), a Byteflight module and an Inter-IC Bus. The MC9S12DT128 has full 16-bit data paths throughout. However, the external bus can operate in an 8-bit narrow mode so single 8-bit wide memory can be interfaced for lower cost systems. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to suit operational requirements.

# 1.2 Features

- HCS12 Core

- 16-bit HCS12 CPU

- i. Upward compatible with M68HC11 instruction set

- ii. Interrupt stacking and programmer's model identical to M68HC11

- iii.20-bit ALU

- iv. Instruction queue

- v. Enhanced indexed addressing

- MEBI (Multiplexed External Bus Interface)

- MMC (Module Mapping Control)

- INT (Interrupt control)

- BKP (Breakpoints)

- BDM (Background Debug Module)

- CRG (Clock and Reset Generator)

- Choice of low current Colpitts oscillator or standard Pierce Oscillator

- PLL

- COP watchdog

- real time interrupt

- clock monitor

- 8-bit and 4-bit ports with interrupt functionality

\$0040 - \$007F

Address

\$007C

\$007D

\$007E

\$007F

## ECT (Enhanced Capture Timer 16 Bit 8 Channels)

| Name      | [      | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| TC2H (hi) | Read:  | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

|           | Write: |        |       |       |       |       |       |       |       |

| TC2H (lo) | Read:  | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 10211(10) | Write: |        |       |       |       |       |       |       |       |

| TC3H (hi) | Read:  | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

|           | Write: |        |       |       |       |       |       |       |       |

| TC3H (lo) | Read:  | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 10311(10) | Write: |        |       |       |       |       |       |       |       |

| \$0080 | - \$009F | - |

|--------|----------|---|

|--------|----------|---|

#### ATD0 (Analog to Digital Converter 10 Bit 8 Channel)

| Address                | Name            | [               | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|------------------------|-----------------|-----------------|-------|-------|-------|---------|--------|-------|-------|-------|

| <b>\$</b> \$\$\$\$\$   |                 | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0080                 | ATD0CTL0        | Write:          |       |       |       |         |        |       |       |       |

| <b>\$0004</b>          |                 | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0081                 | ATD0CTL1        | Write:          |       |       |       |         |        |       |       |       |

| \$0082                 | ATD0CTL2        | Read:<br>Write: | ADPU  | AFFC  | AWAI  | ETRIGLE | ETRIGP | ETRIG | ASCIE | ASCIF |

| \$0083                 | ATD0CTL3        | Read:<br>Write: | 0     | S8C   | S4C   | S2C     | S1C    | FIFO  | FRZ1  | FRZ0  |

| \$0084                 | ATD0CTL4        | Read:<br>Write: | SRES8 | SMP1  | SMP0  | PRS4    | PRS3   | PRS2  | PRS1  | PRS0  |

| \$0085                 | ATD0CTL5        | Read:<br>Write: | DJM   | DSGN  | SCAN  | MULT    | 0      | СС    | СВ    | CA    |

| \$0086                 | ATD0STAT0       | Read:<br>Write: | SCF   | 0     | ETORF | FIFOR   | 0      | CC2   | CC1   | CC0   |

|                        |                 | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0087                 | Reserved        | Write:          | 0     | •     | 0     | Ŭ       | Ū      | U     | •     | Ū     |

|                        |                 | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0088                 | ATD0TEST0       | Write:          | -     | -     | -     |         |        |       | -     | -     |

| <b></b>                |                 | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     |       |

| \$0089                 | ATD0TEST1       | Write:          |       |       |       |         |        |       |       | SC    |

| <b>\$</b> 000 <b>1</b> | <b>D</b>        | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$008A                 | Reserved        | Write:          |       |       |       |         |        |       |       |       |

| ¢000D                  | ATD0STAT1       | Read:           | CCF7  | CCF6  | CCF5  | CCF4    | CCF3   | CCF2  | CCF1  | CCF0  |

| \$008B                 | AID05TAIT       | Write:          |       |       |       |         |        |       |       |       |

| \$008C                 | Reserved        | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| ψ000 <b>C</b>          | Reserved        | Write:          |       |       |       |         |        |       |       |       |

| \$008D                 | <b>ATD0DIEN</b> | Read:<br>Write: | Bit 7 | 6     | 5     | 4       | 3      | 2     | 1     | Bit 0 |

| \$008E                 | Reserved        | Read:           | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| 9000E                  | Reserved        | Write:          |       |       |       |         |        |       |       |       |

| \$008F                 | PORTAD0         | Read:           | Bit7  | 6     | 5     | 4       | 3      | 2     | 1     | BIT 0 |

| φυυυι                  |                 | Write:          |       |       |       |         |        |       |       |       |

| \$0090                 | ATD0DR0H        | Read:           | Bit15 | 14    | 13    | 12      | 11     | 10    | 9     | Bit8  |

| <b>40000</b>           |                 | Write:          |       |       |       |         |        |       |       |       |

| \$0091                 | ATD0DR0L        | Read:           | Bit7  | Bit6  | 0     | 0       | 0      | 0     | 0     | 0     |

|                        | -               | Write:          |       |       |       |         |        |       |       |       |

## \$0110 - \$011B EEPROM Control Register (eets2k)

| Address | Name    |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| \$0119  | EADDRLO | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$011A  | EDATAHI | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| \$011B  | EDATALO | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

#### \$011C - \$011F

#### **Reserved for RAM Control Register**

| Address  | Name           | 1      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$011C - | 11C - Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$011F   | Reserveu       | Write: |       |       |       |       |       |       |       |       |

#### \$0120 - \$013F

## ATD1 (Analog to Digital Converter 10 Bit 8 Channel)

| Address         | Name       | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|-----------------|------------|--------|-------|-------|-------|---------|--------|-------|-------|-------|

| \$0120          | ATD1CTL0   | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| ψ0120           | AIDICILO   | Write: |       |       |       |         |        |       |       |       |

| \$0121          | ATD1CTL1   | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| ψυτζι           | AIDICILI   | Write: |       |       |       |         |        |       |       |       |

| \$0122          | ATD1CTL2   | Read:  | ADPU  | AFFC  | AWAI  | ETRIGLE | ETRIGP | ETRIG | ASCIE | ASCIF |

| ψ0122           | AIDIOILZ   | Write: |       | AITO  |       |         |        | LINIO |       |       |

| \$0123          | ATD1CTL3   | Read:  | 0     | S8C   | S4C   | S2C     | S1C    | FIFO  | FRZ1  | FRZ0  |

| ψ0120           | AID TOTES  | Write: |       | 000   | 0+0   | 020     | 010    | 1110  | 11121 | 11120 |

| \$0124          | ATD1CTL4   | Read:  | SRES8 | SMP1  | SMP0  | PRS4    | PRS3   | PRS2  | PRS1  | PRS0  |

| ψ0121           | , abioilei | Write: | ONLOG |       |       | 11.01   |        | 11(02 |       |       |

| \$0125          | ATD1CTL5   | Read:  | DJM   | DSGN  | SCAN  | MULT    | 0      | СС    | СВ    | CA    |

| ψ0120           | /10100     | Write: | _     |       |       |         |        |       |       |       |

| \$0126          | ATD1STAT0  | Read:  | SCF   | 0     | ETORF | FIFOR   | 0      | CC2   | CC1   | CC0   |

| <b>\$0120</b>   |            | Write: |       |       |       |         |        |       |       |       |

| \$0127          | Reserved   | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| ψ0121           | 100001100  | Write: |       |       |       |         |        |       |       |       |

| \$0128          | ATD1TEST0  | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| <b>\$0120</b>   | /          | Write: |       |       |       |         |        |       |       |       |

| \$0129          | ATD1TEST1  | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | SC    |

| φ0120           | /          | Write: |       |       |       |         |        |       |       |       |

| \$012A          | Reserved   | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| φ01 <u></u> 2/( | 100001100  | Write: |       |       |       |         |        |       |       |       |

| \$012B          | ATD1STAT1  | Read:  | CCF7  | CCF6  | CCF5  | CCF4    | CCF3   | CCF2  | CCF1  | CCF0  |

| Ψ012D           |            | Write: |       |       |       |         |        |       |       |       |

| \$012C          | Reserved   | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| ψ0120           | 100001100  | Write: |       |       |       |         |        |       |       |       |

| \$012D          | ATD1DIEN   | Read:  | Bit 7 | 6     | 5     | 4       | 3      | 2     | 1     | Bit 0 |

| Ψ012D           |            | Write: |       | _     | _     | •       |        |       |       |       |

| \$012E          | Reserved   | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| WU12L           |            | Write: |       |       |       |         |        |       |       |       |

| \$012F          | PORTAD1    | Read:  | Bit7  | 6     | 5     | 4       | 3      | 2     | 1     | BIT 0 |

| ΨUIZI           |            | Write: |       |       |       |         |        |       |       |       |

#### \$0240 - \$027F

# PIM (Port Integration Module)

| Address  | Name     |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0259   | PTIP     | Read:           | PTIP7 | PTIP6 | PTIP5 | PTIP4 | PTIP3 | PTIP2 | PTIP1 | PTIP0 |

| φ0209    | FIIF     | Write:          |       |       |       |       |       |       |       |       |

| \$025A   | DDRP     | Read:<br>Write: | DDRP7 | DDRP7 | DDRP5 | DDRP4 | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| \$025B   | RDRP     | Read:<br>Write: | RDRP7 | RDRP6 | RDRP5 | RDRP4 | RDRP3 | RDRP2 | RDRP1 | RDRP0 |

| \$025C   | PERP     | Read:<br>Write: | PERP7 | PERP6 | PERP5 | PERP4 | PERP3 | PERP2 | PERP1 | PERP0 |

| \$025D   | PPSP     | Read:<br>Write: | PPSP7 | PPSP6 | PPSP5 | PPSP4 | PPSP3 | PPSP2 | PPSP1 | PPSS0 |

| \$025E   | PIEP     | Read:<br>Write: | PIEP7 | PIEP6 | PIEP5 | PIEP4 | PIEP3 | PIEP2 | PIEP1 | PIEP0 |

| \$025F   | PIFP     | Read:<br>Write: | PIFP7 | PIFP6 | PIFP5 | PIFP4 | PIFP3 | PIFP2 | PIFP1 | PIFP0 |

| \$0260   | PTH      | Read:<br>Write: | PTH7  | PTH6  | PTH5  | PTH4  | PTH3  | PTH2  | PTH1  | PTH0  |

| \$0261   | PTIH     | Read:<br>Write: | PTIH7 | PTIH6 | PTIH5 | PTIH4 | PTIH3 | PTIH2 | PTIH1 | PTIH0 |

| \$0262   | DDRH     | Read:<br>Write: | DDRH7 | DDRH7 | DDRH5 | DDRH4 | DDRH3 | DDRH2 | DDRH1 | DDRH0 |

| \$0263   | RDRH     | Read:<br>Write: | RDRH7 | RDRH6 | RDRH5 | RDRH4 | RDRH3 | RDRH2 | RDRH1 | RDRH0 |

| \$0264   | PERH     | Read:<br>Write: | PERH7 | PERH6 | PERH5 | PERH4 | PERH3 | PERH2 | PERH1 | PERH0 |

| \$0265   | PPSH     | Read:<br>Write: | PPSH7 | PPSH6 | PPSH5 | PPSH4 | PPSH3 | PPSH2 | PPSH1 | PPSH0 |

| \$0266   | PIEH     | Read:<br>Write: | PIEH7 | PIEH6 | PIEH5 | PIEH4 | PIEH3 | PIEH2 | PIEH1 | PIEH0 |

| \$0267   | PIFH     | Read:<br>Write: | PIFH7 | PIFH6 | PIFH5 | PIFH4 | PIFH3 | PIFH2 | PIFH1 | PIFH0 |

| \$0268   | PTJ      | Read:<br>Write: | PTJ7  | PTJ6  | 0     | 0     | 0     | 0     | PTJ1  | PTJ0  |

| \$0269   | PTIJ     | Read:<br>Write: | PTIJ7 | PTIJ6 | 0     | 0     | 0     | 0     | PTIJ1 | PTIJ0 |

| \$026A   | DDRJ     | Read:<br>Write: | DDRJ7 | DDRJ7 | 0     | 0     | 0     | 0     | DDRJ1 | DDRJ0 |

| \$026B   | RDRJ     | Read:<br>Write: | RDRJ7 | RDRJ6 | 0     | 0     | 0     | 0     | RDRJ1 | RDRJ0 |

| \$026C   | PERJ     | Read:<br>Write: | PERJ7 | PERJ6 | 0     | 0     | 0     | 0     | PERJ1 | PERJ0 |

| \$026D   | PPSJ     | Read:<br>Write: | PPSJ7 | PPSJ6 | 0     | 0     | 0     | 0     | PPSJ1 | PPSJ0 |

| \$026E   | PIEJ     | Read:<br>Write: | PIEJ7 | PIEJ6 | 0     | 0     | 0     | 0     | PIEJ1 | PIEJ0 |

| \$026F   | PIFJ     | Read:<br>Write: | PIFJ7 | PIFJ6 | 0     | 0     | 0     | 0     | PIFJ1 | PIFJ0 |

| \$0270 - | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$027F   |          | Write:          |       |       |       |       |       |       |       |       |

\$0280 - \$02BF

## CAN4 (Motorola Scalable CAN - MSCAN)

| Address                      | Name                     |                           | Bit 7  | Bit 6  | Bit 5   | Bit 4     | Bit 3    | Bit 2             | Bit 1  | Bit 0  |

|------------------------------|--------------------------|---------------------------|--------|--------|---------|-----------|----------|-------------------|--------|--------|

| \$0280                       | CAN4CTL0                 | Read:<br>Write:           | RXFRM  | RXACT  | CSWAI   | SYNCH     | TIME     | WUPE              | SLPRQ  | INITRQ |

| \$0281                       | CAN4CTL1                 | Read:<br>Write:           | CANE   | CLKSRC | LOOPB   | LISTEN    | 0        | WUPM              | SLPAK  | INITAK |

| \$0282                       | CAN4BTR0                 | Read:<br>Write:           | SJW1   | SJW0   | BRP5    | BRP4      | BRP3     | BRP2              | BRP1   | BRP0   |

| \$0283                       | CAN4BTR1                 | Read:<br>Write:           | SAMP   | TSEG22 | TSEG21  | TSEG20    | TSEG13   | TSEG12            | TSEG11 | TSEG10 |

| \$0284                       | CAN4RFLG                 | Read:<br>Write:           | WUPIF  | CSCIF  | RSTAT1  | RSTAT0    | TSTAT1   | TSTAT0            | OVRIF  | RXF    |

| \$0285                       | CAN4RIER                 | Read:<br>Write:           | WUPIE  | CSCIE  | RSTATE1 | RSTATE0   | TSTATE1  | TSTATE0           | OVRIE  | RXFIE  |

| \$0286                       | CAN4TFLG                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | TXE2              | TXE1   | TXE0   |

| \$0287                       | CAN4TIER                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | TXEIE2            | TXEIE1 | TXEIE0 |

| \$0288                       | CAN4TARQ                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | ABTRQ2            | ABTRQ1 | ABTRQ0 |

| \$0289                       | CAN4TAAK                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | ABTAK2            | ABTAK1 | ABTAK0 |

| \$028A                       | CAN4TBSEL                | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | TX2               | TX1    | TX0    |

| \$028B                       | CAN4IDAC                 | Read:<br>Write:           | 0      | 0      | IDAM1   | IDAM0     | 0        | IDHIT2            | IDHIT1 | IDHIT0 |

| \$028C                       | Reserved                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | 0                 | 0      | 0      |

| \$028D                       | Reserved                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | 0                 | 0      | 0      |

| \$028E                       | CAN4RXERR                | Read:<br>Write:           | RXERR7 | RXERR6 | RXERR5  | RXERR4    | RXERR3   | RXERR2            | RXERR1 | RXERR0 |

| \$028F                       | CAN4TXERR                | Read:<br>Write:           | TXERR7 | TXERR6 | TXERR5  | TXERR4    | TXERR3   | TXERR2            | TXERR1 | TXERR0 |

| \$0290 -<br>\$0293           | CAN0IDAR0 -<br>CAN0IDAR3 | Read:<br>Write:           | AC7    | AC6    | AC5     | AC4       | AC3      | AC2               | AC1    | AC0    |

| \$0294 -<br>\$0297           | CANOIDMR0 -<br>CANOIDMR3 | Read:<br>Write:           | AM7    | AM6    | AM5     | AM4       | AM3      | AM2               | AM1    | AM0    |

| \$0298 -<br>\$029B           | CANOIDAR4 -<br>CANOIDAR7 | Read:<br>Write:           | AC7    | AC6    | AC5     | AC4       | AC3      | AC2               | AC1    | AC0    |

| \$029C -<br>\$029F           | CANOIDMR4 -<br>CANOIDMR7 | Read:                     | AM7    | AM6    | AM5     | AM4       | AM3      | AM2               | AM1    | AM0    |

| \$02A0 -                     | CAN4RXFG                 | Read:                     |        | FOR    | EGROUNI | D RECEIVE | BUFFER   | see <b>(Table</b> | 1-2)   |        |

| \$02AF<br>\$02B0 -<br>\$02BF | CAN4TXFG                 | Write:<br>Read:<br>Write: |        | FOR    | EGROUND | TRANSMI   | T BUFFER | see <b>(Table</b> | e 1-2) |        |

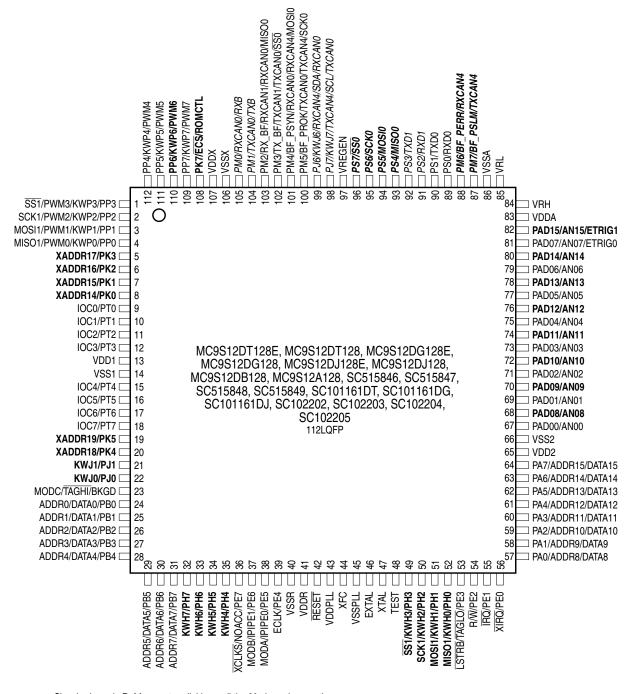

Signals shown in **Bold** are not available on all the 80 pin package options Signals shown in **Bold-Italics** are not available on the MC9S12DJ128E, MC9S12DJ128, MC9S12DG128E, MC9S12DG128, MC9S12A128, SC515847, SC515848, SC101161DG, SC101161DJ, SC102203, and SC102204 80 pin package options Signals shown in *Italics* are not available on the MC9S12DB128, SC515846, and SC102202 80 pin package options

Figure 2-1 Pin assignments 112 LQFP for MC9S12DT128E, MC9S12DT128, MC9S12DG128E, MC9S12DG128, MC9S12DJ128E, MC9S12DJ128, MC9S12DB128 MC9S12A128, SC515846, SC515847, SC515848, SC515849, SC101161DT, SC101161DG, SC101161DJ, SC102202, SC102203, SC102204, and SC102205

| Mnemonic  | Pin Number  | Nominal | Description                                                                                                                                    |  |

|-----------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| winemonic | 112-pin QFP | Voltage | Description                                                                                                                                    |  |

| VDDR      | 41          | 5.0V    | External power and ground, supply to pin drivers and internal                                                                                  |  |

| VSSR      | 40          | 0V      | voltage regulator.                                                                                                                             |  |

| VDDX      | 107         | 5.0V    | External power and ground, supply to pin drivers.                                                                                              |  |

| VSSX      | 106         | 0V      | External power and ground, supply to pin unvers.                                                                                               |  |

| VDDA      | 83          | 5.0V    | Operating voltage and ground for the analog-to-digital                                                                                         |  |

| VSSA      | 86          | 0V      | converters and the reference for the internal voltage regulator,<br>allows the supply voltage to the A/D to be bypassed<br>independently.      |  |

| VRL       | 85          | 0V      | Reference voltages for the analog-to-digital converter.                                                                                        |  |

| VRH       | 84          | 5.0V    | Thereference voltages for the analog-to-digital converter.                                                                                     |  |

| VDDPLL    | 43          | 2.5V    | Provides operating voltage and ground for the Phased-Locked                                                                                    |  |

| VSSPLL    | 45          | 0V      | Loop. This allows the supply voltage to the PLL to be<br>bypassed independently. Internal power and ground<br>generated by internal regulator. |  |

| VREGEN    | 97          | 5V      | Internal Voltage Regulator enable/disable                                                                                                      |  |

**NOTE:** All VSS pins must be connected together in the application.

# 2.4.1 VDDX,VSSX — Power & Ground Pins for I/O Drivers

External power and ground for I/O drivers. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

# 2.4.2 VDDR, VSSR — Power & Ground Pins for I/O Drivers & for Internal Voltage Regulator

External power and ground for I/O drivers and input to the internal voltage regulator. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

## 2.4.3 VDD1, VDD2, VSS1, VSS2 — Internal Logic Power Supply Pins

Power is supplied to the MCU through VDD and VSS. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. This 2.5V supply is derived from the internal voltage regulator. There is no static load on those pins allowed. The internal voltage regulator is turned off, if VREGEN is tied to ground.

#### **NOTE:** No load allowed except for bypass capacitors.

# 2.4.4 VDDA, VSSA — Power Supply Pins for ATD and VREG

VDDA, VSSA are the power supply and ground input pins for the voltage regulator and the analog to digital converter. It also provides the reference for the internal voltage regulator. This allows the supply voltage to the ATD and the reference voltage to be bypassed independently.

## 2.4.5 VRH, VRL — ATD Reference Voltage Input Pins

VRH and VRL are the reference voltage input pins for the analog to digital converter.

## 2.4.6 VDDPLL, VSSPLL — Power Supply Pins for PLL

Provides operating voltage and ground for the Oscillator and the Phased-Locked Loop. This allows the supply voltage to the Oscillator and PLL to be bypassed independently. This 2.5V voltage is generated by the internal voltage regulator.

**NOTE:** No load allowed except for bypass capacitors.

## 2.4.7 VREGEN — On Chip Voltage Regulator Enable

Enables the internal 5V to 2.5V voltage regulator. If this pin is tied low, VDD1,2 and VDDPLL must be supplied externally.

# **Section 4 Modes of Operation**

# 4.1 Overview

Eight possible modes determine the operating configuration of the MC9S12DT128. Each mode has an associated default memory map and external bus configuration controlled by a further pin.

Three low power modes exist for the device.

# 4.2 Chip Configuration Summary

The operating mode out of reset is determined by the states of the MODC, MODB, and MODA pins during reset (**(Table 4-1)**). The MODC, MODB, and MODA bits in the MODE register show the current operating mode and provide limited mode switching during operation. The states of the MODC, MODB, and MODA pins are latched into these bits on the rising edge of the reset signal. The ROMCTL signal allows the setting of the ROMON bit in the MISC register thus controlling whether the internal Flash is visible in the memory map. ROMON = 1 mean the Flash is visible in the memory map. The state of the ROMCTL pin is latched into the ROMON bit in the MISC register on the rising edge of the reset signal.

| BKGD =<br>MODC | PE6 =<br>MODB | PE5 =<br>MODA | PK7 =<br>ROMCTL | ROMON<br>Bit | Mode Description                                                                                                                    |

|----------------|---------------|---------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0              | 0             | 0             | x               | 1            | Special Single Chip, BDM allowed and ACTIVE. BDM is allowed in all other modes but a serial command is required to make BDM active. |

| 0              | 0             | 1             | 0               | 1            | Emulation Expanded Narrow, PDM allowed                                                                                              |

| 0              | 0             | 1             | 1               | 0            | Emulation Expanded Narrow, BDM allowed                                                                                              |

| 0              | 1             | 0             | Х               | 0            | Special Test (Expanded Wide), BDM allowed                                                                                           |

| 0              | 4             | 4             | 0               | 1            | Emulation Expanded Wide DDM allowed                                                                                                 |

| 0              | I             | I             | 1               | 0            | Emulation Expanded Wide, BDM allowed                                                                                                |

| 1              | 0             | 0             | Х               | 1            | Normal Single Chip, BDM allowed                                                                                                     |

| 1              | 0             | 4             | 0               | 0            | Normal Expanded Nerrow, BDM allowed                                                                                                 |

| 1              | 0             | I             | 1               | 1            | Normal Expanded Narrow, BDM allowed                                                                                                 |

| 1              | 1             | 0             | х               | 1            | Special Peripheral; BDM allowed but bus operations would cause bus conflicts (must not be used)                                     |

| 1              | 1             | 1             | 0               | 0            | Normal Expanded Wide, BDM allowed                                                                                                   |

|                |               |               | 1               | 1            | - Normai Expanded Wide, BDM allowed                                                                                                 |

Table 4-1 Mode Selection

For further explanation on the modes refer to the HCS12 Multiplexed External Bus Interface Block Guide.

| PE7 = XCLKS | Description                               |

|-------------|-------------------------------------------|

| 1           | Colpitts Oscillator selected              |

| 0           | Pierce Oscillator/external clock selected |

Table 4-2 Clock Selection Based on PE7

# Section 5 Resets and Interrupts

# 5.1 Overview

Consult the Exception Processing section of the CPU Reference Manual for information on resets and interrupts.

# 5.2 Vectors

# 5.2.1 Vector Table

(Table 5-1) lists interrupt sources and vectors in default order of priority.

| Vector Address | Interrupt Source                   | CCR<br>Mask | Local Enable                         | HPRIO Value<br>to Elevate |

|----------------|------------------------------------|-------------|--------------------------------------|---------------------------|

| \$FFFE, \$FFFF | Reset                              | None        | None                                 | -                         |

| \$FFFC, \$FFFD | Clock Monitor fail reset           | None        | COPCTL (CME, FCME)                   | -                         |

| \$FFFA, \$FFFB | COP failure reset                  | None        | COP rate select                      | -                         |

| \$FFF8, \$FFF9 | Unimplemented instruction trap     | None        | None                                 | -                         |

| \$FFF6, \$FFF7 | SWI                                | None        | None                                 | -                         |

| \$FFF4, \$FFF5 | XIRQ / BF High Priority Sync Pulse | X-Bit       | None / BFRIER (XSYNIE)               | -                         |

| \$FFF2, \$FFF3 | IRQ                                | I-Bit       | INTCR (IRQEN)                        | \$F2                      |

| \$FFF0, \$FFF1 | Real Time Interrupt                | I-Bit       | CRGINT (RTIE)                        | \$F0                      |

| \$FFEE, \$FFEF | Enhanced Capture Timer channel 0   | I-Bit       | TIE (COI)                            | \$EE                      |

| \$FFEC, \$FFED | Enhanced Capture Timer channel 1   | I-Bit       | TIE (C1I)                            | \$EC                      |

| \$FFEA, \$FFEB | Enhanced Capture Timer channel 2   | I-Bit       | TIE (C2I)                            | \$EA                      |

| \$FFE8, \$FFE9 | Enhanced Capture Timer channel 3   | I-Bit       | TIE (C3I)                            | \$E8                      |

| \$FFE6, \$FFE7 | Enhanced Capture Timer channel 4   | I-Bit       | TIE (C4I)                            | \$E6                      |

| \$FFE4, \$FFE5 | Enhanced Capture Timer channel 5   | I-Bit       | TIE (C5I)                            | \$E4                      |

| \$FFE2, \$FFE3 | Enhanced Capture Timer channel 6   | I-Bit       | TIE (C6I)                            | \$E2                      |

| \$FFE0, \$FFE1 | Enhanced Capture Timer channel 7   | I-Bit       | TIE (C7I)                            | \$E0                      |

| \$FFDE, \$FFDF | Enhanced Capture Timer overflow    | I-Bit       | TSCR2 (TOF)                          | \$DE                      |

| \$FFDC, \$FFDD | Pulse accumulator A overflow       | I-Bit       | PACTL (PAOVI)                        | \$DC                      |

| \$FFDA, \$FFDB | Pulse accumulator input edge       | I-Bit       | PACTL (PAI)                          | \$DA                      |

| \$FFD8, \$FFD9 | SPI0                               | I-Bit       | SPICR1 (SPIE, SPTIE)                 | \$D8                      |

| \$FFD6, \$FFD7 | SCI0                               | I-Bit       | SCICR2<br>(TIE, TCIE, RIE, ILIE)     | \$D6                      |

| \$FFD4, \$FFD5 | SCI1                               | I-Bit       | SCICR2<br>(TIE, TCIE, RIE, ILIE)     | \$D4                      |

| \$FFD2, \$FFD3 | ATD0                               | I-Bit       | ATDCTL2 (ASCIE)                      | \$D2                      |

| \$FFD0, \$FFD1 | ATD1                               | I-Bit       | ATDCTL2 (ASCIE)                      | \$D0                      |

| \$FFCE, \$FFCF | Port J                             | I-Bit       | PIEJ<br>(PIEJ7, PIEJ6, PIEJ1, PIEJ0) | \$CE                      |

| \$FFCC, \$FFCD | Port H                             | I-Bit       | PIEH (PIEH7-0)                       | \$CC                      |

| Table 5-1 | Interrupt | Vector | Locations |

|-----------|-----------|--------|-----------|

|           | mitor apt |        |           |

| Num | С | Rating                                                                           | Symbol          | Min | Тур | Max | Unit |

|-----|---|----------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| 1   | Т | Thermal Resistance LQFP112, single sided PCB <sup>2</sup>                        | θ <sub>JA</sub> | -   | -   | 54  | °C/W |

| 2   | т | Thermal Resistance LQFP112, double sided PCB with 2 internal planes <sup>3</sup> | $\theta_{JA}$   | -   | -   | 41  | °C/W |

| 3   | т | Junction to Board LQFP112                                                        | $\theta_{JB}$   | -   | -   | 31  | °C/W |

| 4   | т | Junction to Case LQFP112                                                         | θ <sub>JC</sub> | -   | -   | 11  | °C/W |

| 5   | т | Junction to Package Top LQFP112                                                  | $\Psi_{JT}$     | -   | -   | 2   | °C/W |

| 6   | т | Thermal Resistance QFP 80, single sided PCB                                      | $\theta_{JA}$   | -   | -   | 51  | °C/W |

| 7   | т | Thermal Resistance QFP 80, double sided PCB with 2 internal planes               | $\theta_{JA}$   | -   | -   | 41  | °C/W |

| 8   | т | Junction to Board QFP80                                                          | $\theta_{JB}$   | -   | -   | 27  | °C/W |

| 9   | Т | Junction to Case QFP80                                                           | θ <sub>JC</sub> | -   | -   | 14  | °C/W |

| 10  | т | Junction to Package Top QFP80                                                    | $\Psi_{JT}$     | -   | -   | 3   | °C/W |

Table A-5 Thermal Package Characteristics<sup>1</sup>

NOTES:

1. The values for thermal resistance are achieved by package simulations

2. PC Board according to EIA/JEDEC Standard 51-3

3. PC Board according to EIA/JEDEC Standard 51-7

## A.1.9 I/O Characteristics

This section describes the characteristics of all 5V I/O pins. All parameters are not always applicable, e.g. not all pins feature pull up/down resistances.

## A.1.10.1 Measurement Conditions

All measurements are without output loads. Unless otherwise noted the currents are measured in single chip mode, internal voltage regulator enabled and at 25MHz bus frequency using a 4MHz oscillator in Colpitts mode. Production testing is performed using a square wave signal at the EXTAL input.

#### A.1.10.2 Additional Remarks

In expanded modes the currents flowing in the system are highly dependent on the load at the address, data and control signals as well as on the duty cycle of those signals. No generally applicable numbers can be given. A very good estimate is to take the single chip currents and add the currents due to the external loads.

| Conditions are shown in (Table A-4) unless otherwise noted |                   |                                                                                                                                                                                          |                   |     |                                                              |                             |      |  |

|------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|--------------------------------------------------------------|-----------------------------|------|--|

| Num                                                        | С                 | Rating                                                                                                                                                                                   | Symbol            | Min | Тур                                                          | Max                         | Unit |  |

| 1                                                          | Р                 | Run supply currents<br>Single Chip, Internal regulator enabled                                                                                                                           | I <sub>DD5</sub>  |     |                                                              | 55                          | mA   |  |

| 2                                                          | P<br>P            | Wait Supply current<br>All modules enabled, PLL on<br>only RTI enabled <sup>(1)</sup>                                                                                                    | I <sub>DDW</sub>  |     |                                                              | 30<br>5                     | mA   |  |

| 3                                                          | C P C C P C P C P | Pseudo Stop Current (RTI and COP disabled) <sup>1, 2</sup><br>-40°C<br>27°C<br>70°C<br>85°C<br>"C" Temp Option 100°C<br>105°C<br>"V" Temp Option 120°C<br>125°C<br>"M" Temp Option 140°C | I <sub>DDPS</sub> |     | 370<br>400<br>450<br>550<br>600<br>650<br>800<br>850<br>1200 | 500<br>1600<br>2100<br>5000 | μΑ   |  |

| 4                                                          | 0000000           | Pseudo Stop Current (RTI and COP enabled) <sup>(1), (2)</sup><br>-40°C<br>27°C<br>70°C<br>85°C<br>105°C<br>125°C<br>140°C                                                                | I <sub>DDPS</sub> |     | 570<br>600<br>650<br>750<br>850<br>1200<br>1500              |                             | μΑ   |  |

| 5                                                          | C P C C P C P C P | Stop Current <sup>(2)</sup><br>-40°C<br>27°C<br>70°C<br>85°C<br>"C" Temp Option 100°C<br>105°C<br>"V" Temp Option 120°C<br>125°C<br>"M" Temp Option 140°C                                | I <sub>DDS</sub>  |     | 12<br>25<br>100<br>130<br>160<br>200<br>350<br>400<br>600    | 100<br>1200<br>1700<br>5000 | μΑ   |  |

## Table A-7 Supply Current Characteristics

#### Device User Guide — 9S12DT128DGV2/D V02.17

NOTES:

- 1. PLL off, Oscillator in Colpitts Mode 2. At those low power dissipation levels  $T_J = T_A$  can be assumed

Clock Monitor Failure is asserted if the frequency of the incoming clock signal is below the Assert Frequency  $\rm f_{CMFA.}$

| Num | С | Rating                                                   | Symbol                 | Min                      | Тур            | Мах                      | Unit |

|-----|---|----------------------------------------------------------|------------------------|--------------------------|----------------|--------------------------|------|

| 1a  | C | Crystal oscillator range (Colpitts)                      | f <sub>OSC</sub>       | 0.5                      | - 76           | 16                       | MHz  |

|     | - |                                                          |                        |                          |                | _                        |      |

| 1b  | С | Crystal oscillator range (Pierce) <sup>1</sup>           | fosc                   | 0.5                      |                | 40                       | MHz  |

| 2   | Ρ | Startup Current                                          | iosc                   | 100                      |                |                          | μA   |

| 3   | С | Oscillator start-up time (Colpitts)                      | t <sub>UPOSC</sub>     |                          | 8 <sup>2</sup> | 100 <sup>3</sup>         | ms   |

| 4   | D | Clock Quality check time-out                             | t <sub>CQOUT</sub>     | 0.45                     |                | 2.5                      | S    |

| 5   | Ρ | Clock Monitor Failure Assert Frequency                   | f <sub>CMFA</sub>      | 50                       | 100            | 200                      | KHz  |

| 6   | Ρ | External square wave input frequency <sup>4</sup>        | f <sub>EXT</sub>       | 0.5                      |                | 50                       | MHz  |

| 7   | D | External square wave pulse width low                     | t <sub>EXTL</sub>      | 9.5                      |                |                          | ns   |

| 8   | D | External square wave pulse width high                    | t <sub>EXTH</sub>      | 9.5                      |                |                          | ns   |

| 9   | D | External square wave rise time                           | t <sub>EXTR</sub>      |                          |                | 1                        | ns   |

| 10  | D | External square wave fall time                           | t <sub>EXTF</sub>      |                          |                | 1                        | ns   |

| 11  | D | Input Capacitance (EXTAL, XTAL pins)                     | C <sub>IN</sub>        |                          | 7              |                          | pF   |

| 12  | с | DC Operating Bias in Colpitts Configuration on EXTAL Pin | V <sub>DCBIAS</sub>    |                          | 1.1            |                          | V    |

| 13  | Ρ | EXTAL Pin Input High Voltage <sup>4</sup>                | V <sub>IH,EXTAL</sub>  | 0.75*V <sub>DDPLL</sub>  |                |                          | V    |

|     | Т | EXTAL Pin Input High Voltage <sup>4</sup>                | V <sub>IH,EXTAL</sub>  |                          |                | V <sub>DDPLL</sub> + 0.3 | V    |

| 14  | Р | EXTAL Pin Input Low Voltage <sup>4</sup>                 | V <sub>IL,EXTAL</sub>  |                          |                | 0.25*V <sub>DDPLL</sub>  | V    |

|     | т | EXTAL Pin Input Low Voltage <sup>4</sup>                 | VIL,EXTAL              | V <sub>SSPLL</sub> - 0.3 |                |                          | V    |

| 15  | С | EXTAL Pin Input Hysteresis <sup>4</sup>                  | V <sub>HYS,EXTAL</sub> |                          | 250            |                          | mV   |

| Table A-15 | Oscillator | Characteristics |

|------------|------------|-----------------|

|            |            |                 |

NOTES:

1. Depending on the crystal a damping series resistor might be necessary

2.  $f_{osc} = 4MHz$ , C = 22pF.

3. Maximum value is for extreme cases using high Q, low frequency crystals

4. XCLKS =0 during reset

# A.5.3 Phase Locked Loop

The oscillator provides the reference clock for the PLL. The PLL's Voltage Controlled Oscillator (VCO) is also the system clock source in self clock mode.

## A.5.3.1 XFC Component Selection

This section describes the selection of the XFC components to achieve a good filter characteristics.

1.If configured as output

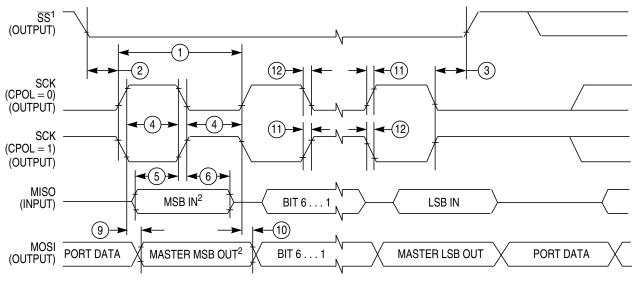

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure A-7 SPI Master Timing (CPHA =1)

| Table A-18 | SPI Master | Mode | Timing | Characteristics <sup>1</sup> |

|------------|------------|------|--------|------------------------------|

|------------|------------|------|--------|------------------------------|

| Condit | Conditions are shown in <b>(Table A-4)</b> unless otherwise noted, C <sub>LOAD</sub> = 200pF on all outputs |                                                  |                   |                       |     |                       |                  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------|-----------------------|-----|-----------------------|------------------|--|--|

| Num    | С                                                                                                           | Rating                                           | Symbol            | Min                   | Тур | Max                   | Unit             |  |  |

| 1      | Ρ                                                                                                           | Operating Frequency                              | f <sub>op</sub>   | DC                    |     | 1/2                   | f <sub>bus</sub> |  |  |

| 1      | Ρ                                                                                                           | SCK Period t <sub>sck</sub> = 1./f <sub>op</sub> | t <sub>sck</sub>  | 4                     |     | 2048                  | t <sub>bus</sub> |  |  |

| 2      | D                                                                                                           | Enable Lead Time                                 | t <sub>lead</sub> | 1/2                   |     | —                     | t <sub>sck</sub> |  |  |

| 3      | D                                                                                                           | Enable Lag Time                                  | t <sub>lag</sub>  | 1/2                   |     |                       | t <sub>sck</sub> |  |  |

| 4      | D                                                                                                           | Clock (SCK) High or Low Time                     | t <sub>wsck</sub> | t <sub>bus</sub> – 30 |     | 1024 t <sub>bus</sub> | ns               |  |  |

| 5      | D                                                                                                           | Data Setup Time (Inputs)                         | t <sub>su</sub>   | 25                    |     |                       | ns               |  |  |

| 6      | D                                                                                                           | Data Hold Time (Inputs)                          | t <sub>hi</sub>   | 0                     |     |                       | ns               |  |  |

| 9      | D                                                                                                           | Data Valid (after SCK Edge)                      | t <sub>v</sub>    |                       |     | 25                    | ns               |  |  |

| 10     | D                                                                                                           | Data Hold Time (Outputs)                         | t <sub>ho</sub>   | 0                     |     |                       | ns               |  |  |

| 11     | D                                                                                                           | Rise Time Inputs and Outputs                     | t <sub>r</sub>    |                       |     | 25                    | ns               |  |  |

| 12     | D                                                                                                           | Fall Time Inputs and Outputs                     | t <sub>f</sub>    |                       |     | 25                    | ns               |  |  |

NOTES:

1. The numbers 7, 8 in the column labeled "Num" are missing. This has been done on purpose to be consistent between the Master and the Slave timing shown in **(Table A-19)**.

# Appendix B Package Information

# **B.1 General**

This section provides the physical dimensions of the MC9S12DT128 packages.

# **User Guide End Sheet**