Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                           |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12dg128vfue |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|------------------|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V02.07            | 29 Jan<br>2003   | 29 Jan<br>2003    |        | Added 3L40K mask set in section 1.6<br>Corrected register entries in section 1.5.1 "Detailed Memory Map"<br>Updated description for ROMCTL in section 2.3.31<br>Updated section 4.3.3 "Unsecuring the Microcontroller"<br>Corrected and updated device-specific information for OSC<br>(section 8.1) & Byteflight (section 15.1)<br>Updated footnote in Table A-4 "Operating Conditions"<br>Changed reference of VDDM to VDDR in section A.1.8<br>Removed footnote on input leakage current in Table A-6 "5V I/O<br>Characteristics"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V02.08            | 26 Feb<br>2003   | 26 Feb<br>2003    |        | Added part numbers MC9S12DT128E, MC9S12DG128E, and<br>MC9S12DJ128E in "Preface" and related part number references<br>Removed mask sets 0L40K and 2L40K from Table 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V02.09            | 15 Oct<br>2003   | 15 Oct<br>2003    |        | <ul> <li>Replaced references to HCS12 Core Guide by the individual<br/>HCS12 Block guides in Table 0-2, section 1.5.1, and section 6;<br/>updated Fig.3-1 "Clock Connections" to show the individual HCS12<br/>blocks</li> <li>Corrected PIM module name and document order number in Table<br/>0-2 "Document References"</li> <li>Corrected ECT pulse accumulators description in section 1.2<br/>"Features"</li> <li>Corrected KWP5 pin name in Fig 2-1 112LQFP pin assignments</li> <li>Corrected pull resistor CTRL/reset states for PE7 and PE4-PE0 in<br/>Table 2.1 "Signal Properties"</li> <li>Mentioned "S12LRAE" bootloader in Flash section 17</li> <li>Corrected footnote on clamp of TEST pin under Table A-1</li> <li>"Absolute Maximum Ratings"</li> <li>Corrected minimum bus frequency to 0.25MHz in Table A-4</li> <li>"Operating Conditions"</li> <li>Replaced "burst programming" by "row programming" in A.3 "NVM,<br/>Flash and EEPROM"</li> <li>Corrected plank check time for EEPROM in Table A-11 "NVM<br/>Timing Characteristics"</li> </ul> |

| V02.10            | 6 Feb<br>2004    | 6 Feb<br>2004     |        | <ul> <li>Added A128 information in "Derivative Differences", 2.1 "Device<br/>Pinout", 2.2 "Signal Properties Summary", Fig 23-2 &amp; Fig 23-4</li> <li>Added lead-free package option (PVE) in Table 0-2 "Derivative<br/>Differences for MC9S12DB128" and Fig 0-1 "Order Partnumber<br/>Example"</li> <li>Added an "AEC qualified" row in the "Derivative Differences" tables<br/>0-1 &amp; 0-2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V02.11            | 3 May<br>2004    | 3 May<br>2004     |        | Added part numbers SC515846, SC515847, SC515848, and<br>SC515849 in "Derivative Differences" tables 0-1 & 0-2, section 2,<br>and section 23.<br>Corrected and added maskset 4L40K in tables 0-1 & 0-2 and<br>section 1.6.<br>Corrected BDLC module availability in DB128 80QFP part in<br>"Derivative Differences" table 0-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.1.1 | Device-specific information                                       | 85 |

|-------|-------------------------------------------------------------------|----|

| 6.2   | HCS12 Module Mapping Control (MMC) Block Description              | 85 |

| 6.2.1 | Device-specific information                                       | 85 |

| 6.3   | HCS12 Multiplexed External Bus Interface (MEBI) Block Description | 85 |

| 6.3.1 | Device-specific information                                       | 85 |

| 6.4   | HCS12 Interrupt (INT) Block Description                           | 86 |

| 6.5   | HCS12 Background Debug Module (BDM) Block Description             | 86 |

| 6.5.1 | Device-specific information                                       |    |

| 6.6   | HCS12 Breakpoint (BKP) Block Description                          | 86 |

| Sect  | ion 7 Clock and Reset Generator (CRG) Block Description           |    |

| 7.1   | Device-specific information.                                      | 86 |

| Sect  | ion 8 Oscillator (OSC) Block Description                          |    |

| 8.1   | Device-specific information.                                      | 86 |

| Sect  | ion 9 Enhanced Capture Timer (ECT) Block Description              |    |

| Sect  | tion 10 Analog to Digital Converter (ATD) Block Description       |    |

| Sect  | ion 11 Inter-IC Bus (IIC) Block Description                       |    |

| Sect  | ion 12 Serial Communications Interface (SCI) Block Description    |    |

| Sect  | ion 13 Serial Peripheral Interface (SPI) Block Description        |    |

| Sect  | ion 14 J1850 (BDLC) Block Description                             |    |

| Sect  | ion 15 Byteflight (BF) Block Description                          |    |

| 15.1  | Device-specific information.                                      | 88 |

| Sect  | ion 16 Pulse Width Modulator (PWM) Block Description              |    |

| Sect  | ion 17 Flash EEPROM 128K Block Description                        |    |

| Sect  | ion 18 EEPROM 2K Block Description                                |    |

| Sect  | ion 19 RAM Block Description                                      |    |

| Figure A-10 | General External Bus Timing                       | 134 |

|-------------|---------------------------------------------------|-----|

| Figure 23-6 | 112-pin LQFP mechanical dimensions (case no. 987) | 138 |

# **Section 1 Introduction**

# 1.1 Overview

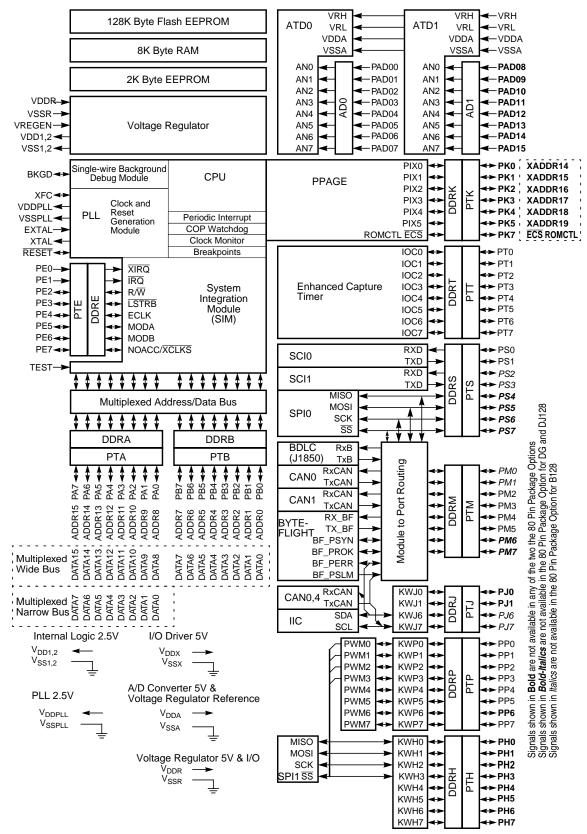

The MC9S12DT128 microcontroller unit (MCU) is a 16-bit device composed of standard on-chip peripherals including a 16-bit central processing unit (HCS12 CPU), 128K bytes of Flash EEPROM, 8K bytes of RAM, 2K bytes of EEPROM, two asynchronous serial communications interfaces (SCI), two serial peripheral interfaces (SPI), an 8-channel IC/OC enhanced capture timer, two 8-channel, 10-bit analog-to-digital converters (ADC), an 8-channel pulse-width modulator (PWM), a digital Byte Data Link Controller (BDLC), 29 discrete digital I/O channels (Port A, Port B, Port K and Port E), 20 discrete digital I/O lines with interrupt and wakeup capability, three CAN 2.0 A, B software compatible modules (MSCAN12), a Byteflight module and an Inter-IC Bus. The MC9S12DT128 has full 16-bit data paths throughout. However, the external bus can operate in an 8-bit narrow mode so single 8-bit wide memory can be interfaced for lower cost systems. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to suit operational requirements.

# 1.2 Features

- HCS12 Core

- 16-bit HCS12 CPU

- i. Upward compatible with M68HC11 instruction set

- ii. Interrupt stacking and programmer's model identical to M68HC11

- iii.20-bit ALU

- iv. Instruction queue

- v. Enhanced indexed addressing

- MEBI (Multiplexed External Bus Interface)

- MMC (Module Mapping Control)

- INT (Interrupt control)

- BKP (Breakpoints)

- BDM (Background Debug Module)

- CRG (Clock and Reset Generator)

- Choice of low current Colpitts oscillator or standard Pierce Oscillator

- PLL

- COP watchdog

- real time interrupt

- clock monitor

- 8-bit and 4-bit ports with interrupt functionality

Figure 1-1 MC9S12DT128 Block Diagram

#### 1.5.1 Detailed Register Map

#### \$0000 - \$000F

#### MEBI map 1 of 3 (HCS12 Multiplexed External Bus Interface)

| Address | Name     |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| \$0000  | PORTA    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0001  | PORTB    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0002  | DDRA     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0003  | DDRB     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0004  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0005  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0006  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0007  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0008  | PORTE    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | Bit 1 | Bit 0 |

| \$0009  | DDRE     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | Bit 2 | 0     | 0     |

| \$000A  | PEAR     | Read:<br>Write: | NOACCE | 0     | PIPOE | NECLK | LSTRE | RDWE  | 0     | 0     |

| \$000B  | MODE     | Read:<br>Write: | MODC   | MODB  | MODA  | 0     | IVIS  | 0     | EMK   | EME   |

| \$000C  | PUCR     | Read:<br>Write: | PUPKE  | 0     | 0     | PUPEE | 0     | 0     | PUPBE | PUPAE |

| \$000D  | RDRIV    | Read:<br>Write: | RDPK   | 0     | 0     | RDPE  | 0     | 0     | RDPB  | RDPA  |

| \$000E  | EBICTL   | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | ESTR  |

| \$000F  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          |                 |        |       |       |       |       |       |       |       |

#### \$0010 - \$0014

#### MMC map 1 of 4 (HCS12 Module Mapping Control)

| Address        | Name       |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0  |

|----------------|------------|-----------------|-------|-------|-------|-------|--------|--------|-------|--------|

| \$0010         | INITRM     | Read:<br>Write: | RAM15 | RAM14 | RAM13 | RAM12 | RAM11  | 0      | 0     | RAMHAL |

| ¢0011          | INITRG     | Read:           | 0     | REG14 | REG13 | REG12 | REG11  | 0      | 0     | 0      |

| \$0011         | INTRG      | Write:          |       | REG14 | REGIS | REGIZ | REGII  |        |       |        |

| \$0012         | INITEE     | Read:           | EE15  | EE14  | EE13  | EE12  | EE11   | 0      | 0     | EEON   |

| <b>\$00</b> .  |            | Write:          |       |       |       |       |        |        |       |        |

| \$0013         | MISC       | Read:           | 0     | 0     | 0     | 0     | EXSTR1 | EXSTR0 | ROMHM | ROMON  |

| φ0013          | MISC       | Write:          |       |       |       |       | ENSIKI | ENGINU |       | ROMON  |

| <b>©</b> 004.4 | Percentred | Read:           | 0     | 0     | 0     | 0     | 0      | 0      | 0     | 0      |

| \$0014         | Reserved   | Write:          |       |       |       |       |        |        |       |        |

#### \$0080 - \$009F ATD0 (Analog to Digital Converter 10 Bit 8 Channel)

| Address             | Name       | [               | Bit 7          | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------------|------------|-----------------|----------------|-------|-------|-------|-------|-------|-------|-------|

| \$0092              | ATD0DR1H   | Read:           | Bit15          | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

| \$009Z              | AIDUDKIN   | Write:          |                |       |       |       |       |       |       |       |

| \$0093              | ATD0DR1L   | Read:           | Bit7           | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

| φ0093               | AIDODITIE  | Write:          |                |       |       |       |       |       |       |       |

| \$0094              | ATD0DR2H   | Read:           | Bit15          | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

| ψ003 <del>-</del>   | AIDODINZII | Write:          |                |       |       |       |       |       |       |       |

| \$0095              | ATD0DR2L   | Read:           | Bit7           | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

| φυυυυ               | A BOBILE   | Write:          |                |       |       |       |       |       |       |       |

| \$0096              | ATD0DR3H   | Read:           | Bit15          | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

| <i><b>QUUUU</b></i> | /          | Write:          |                |       |       |       |       |       |       |       |

| \$0097 ATD0DR3L     | ATD0DR3L   | Read:           | Bit7           | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

|                     |            | Write:          |                |       |       |       |       |       | _     |       |

| \$0098              | ATD0DR4H   | Read:           | Bit15          | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

|                     |            | Write:          |                | 2110  | -     |       |       |       |       | -     |

| \$0099              | ATD0DR4L   | Read:           | Bit7           | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

|                     |            | Write:          | <b>D</b> 1:4 = |       | 4.0   | 1.0   |       | 1.0   | -     | Dia   |

| \$009A              | ATD0DR5H   | Read:           | Bit15          | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

|                     |            | Write:          | D:17           | Dito  | 0     | 0     | 0     | 0     | 0     |       |

| \$009B              | ATD0DR5L   | Read:           | Bit7           | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

|                     |            | Write:          | Ditte          | 4.4   | 40    | 10    | 4.4   | 10    | 0     | D:40  |

| \$009C              | ATD0DR6H   | Read:           | Bit15          | 14    | 13    | 12    | 11    | 10    | 9     | Bit8  |

|                     |            | Write:          | DH7            | DitC  | 0     | 0     | 0     | 0     | 0     | 0     |

| \$009D              | ATD0DR6L   | Read:           | Bit7           | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

|                     |            | Write:          | Di+15          | 14    | 13    | 10    | 11    | 10    | 9     | Bit8  |

| \$009E              | ATD0DR7H   | Read:<br>Write: | Bit15          | 14    | 13    | 12    | 11    | 10    | 9     | DILO  |

|                     |            |                 | Bit7           | Bit6  | 0     | 0     | 0     | 0     | 0     | 0     |

| \$009F              | ATD0DR7L   | Read:<br>Write: | DILI           | DILU  | 0     | U     | U     | U     | U     | 0     |

|                     |            | write.[         |                |       |       |       |       |       |       |       |

#### \$00A0 - \$00C7

#### PWM (Pulse Width Modulator 8 Bit 8 Channel)

| Address | Name      |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                                         | Bit 0 |

|---------|-----------|-----------------|-------|-------|-------|-------|-------|-------|-----------------------------------------------|-------|

| \$00A0  | PWME      | Read:<br>Write: | PWME7 | PWME6 | PWME5 | PWME4 | PWME3 | PWME2 | PWME1                                         | PWME0 |

| \$00A1  | PWMPOL    | Read:<br>Write: | PPOL7 | PPOL6 | PPOL5 | PPOL4 | PPOL3 | PPOL2 | PPOL1                                         | PPOL0 |

| \$00A2  | PWMCLK    | Read:<br>Write: | PCLK7 | PCLK6 | PCLK5 | PCLK4 | PCLK3 | PCLK2 | PCLK1                                         | PCLK0 |

| \$00A3  | PWMPRCLK  | Read:<br>Write: | 0     | PCKB2 | PCKB1 | PCKB0 | 0     | PCKA2 | PCKA1                                         | PCKA0 |

| \$00A4  | PWMCAE    | Read:<br>Write: | CAE7  | CAE6  | CAE5  | CAE4  | CAE3  | CAE2  | CAE1                                          | CAE0  |

| \$00A5  | PWMCTL    | Read:<br>Write: | CON67 | CON45 | CON23 | CON01 | PSWAI | PFRZ  | 0                                             | 0     |

| ¢0046   | PWMTST    | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0                                             | 0     |

| \$00A6  | Test Only | Write:          |       |       |       |       |       |       | PWME1<br>PPOL1<br>PCLK1<br>PCKA1<br>CAE1<br>0 |       |

| ¢0047   | PWMPRSC   | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0                                             | 0     |

| \$00A7  | Test Only | Write:          |       |       |       |       |       |       |                                               |       |

| \$00A8  | PWMSCLA   | Read:<br>Write: | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1                                             | Bit 0 |

\$0280 - \$02BF

#### CAN4 (Motorola Scalable CAN - MSCAN)

| Address                      | Name                     |                           | Bit 7  | Bit 6  | Bit 5   | Bit 4     | Bit 3    | Bit 2             | Bit 1  | Bit 0  |

|------------------------------|--------------------------|---------------------------|--------|--------|---------|-----------|----------|-------------------|--------|--------|

| \$0280                       | CAN4CTL0                 | Read:<br>Write:           | RXFRM  | RXACT  | CSWAI   | SYNCH     | TIME     | WUPE              | SLPRQ  | INITRQ |

| \$0281                       | CAN4CTL1                 | Read:<br>Write:           | CANE   | CLKSRC | LOOPB   | LISTEN    | 0        | WUPM              | SLPAK  | INITAK |

| \$0282                       | CAN4BTR0                 | Read:<br>Write:           | SJW1   | SJW0   | BRP5    | BRP4      | BRP3     | BRP2              | BRP1   | BRP0   |

| \$0283                       | CAN4BTR1                 | Read:<br>Write:           | SAMP   | TSEG22 | TSEG21  | TSEG20    | TSEG13   | TSEG12            | TSEG11 | TSEG10 |

| \$0284                       | CAN4RFLG                 | Read:<br>Write:           | WUPIF  | CSCIF  | RSTAT1  | RSTAT0    | TSTAT1   | TSTAT0            | OVRIF  | RXF    |

| \$0285                       | CAN4RIER                 | Read:<br>Write:           | WUPIE  | CSCIE  | RSTATE1 | RSTATE0   | TSTATE1  | TSTATE0           | OVRIE  | RXFIE  |

| \$0286                       | CAN4TFLG                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | TXE2              | TXE1   | TXE0   |

| \$0287                       | CAN4TIER                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | TXEIE2            | TXEIE1 | TXEIE0 |

| \$0288                       | CAN4TARQ                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | ABTRQ2            | ABTRQ1 | ABTRQ0 |

| \$0289                       | CAN4TAAK                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | ABTAK2            | ABTAK1 | ABTAK0 |

| \$028A                       | CAN4TBSEL                | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | TX2               | TX1    | TX0    |

| \$028B                       | CAN4IDAC                 | Read:<br>Write:           | 0      | 0      | IDAM1   | IDAM0     | 0        | IDHIT2            | IDHIT1 | IDHIT0 |

| \$028C                       | Reserved                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | 0                 | 0      | 0      |

| \$028D                       | Reserved                 | Read:<br>Write:           | 0      | 0      | 0       | 0         | 0        | 0                 | 0      | 0      |

| \$028E                       | CAN4RXERR                | Read:<br>Write:           | RXERR7 | RXERR6 | RXERR5  | RXERR4    | RXERR3   | RXERR2            | RXERR1 | RXERR0 |

| \$028F                       | CAN4TXERR                | Read:<br>Write:           | TXERR7 | TXERR6 | TXERR5  | TXERR4    | TXERR3   | TXERR2            | TXERR1 | TXERR0 |

| \$0290 -<br>\$0293           | CAN0IDAR0 -<br>CAN0IDAR3 | Read:<br>Write:           | AC7    | AC6    | AC5     | AC4       | AC3      | AC2               | AC1    | AC0    |

| \$0294 -<br>\$0297           | CANOIDMR0 -<br>CANOIDMR3 | Read:<br>Write:           | AM7    | AM6    | AM5     | AM4       | AM3      | AM2               | AM1    | AM0    |

| \$0298 -<br>\$029B           | CAN0IDAR4 -<br>CAN0IDAR7 | Read:<br>Write:           | AC7    | AC6    | AC5     | AC4       | AC3      | AC2               | AC1    | AC0    |

| \$029C -<br>\$029F           | CANOIDMR4 -<br>CANOIDMR7 | Read:                     | AM7    | AM6    | AM5     | AM4       | AM3      | AM2               | AM1    | AM0    |

| \$02A0 -                     | CAN4RXFG                 | Read:                     |        | FOR    | EGROUNI | D RECEIVE | BUFFER   | see <b>(Table</b> | 1-2)   |        |

| \$02AF<br>\$02B0 -<br>\$02BF | CAN4TXFG                 | Write:<br>Read:<br>Write: |        | FOR    | EGROUND | TRANSMI   | T BUFFER | see <b>(Table</b> | e 1-2) |        |

# **Section 2 Signal Description**

This section describes signals that connect off-chip. It includes a pinout diagram, a table of signal properties, and detailed discussion of signals. It is built from the signal description sections of the Block User Guides of the individual IP blocks on the device.

# 2.1 Device Pinout

The MC9S12DT128 and its derivatives are available in a 112-pin low profile quad flat pack (LQFP) and in a 80-pin quad flat pack (QFP). Most pins perform two or more functions, as described in the Signal Descriptions. **Figure 2-1**, **Figure 2-2**, and **Figure 2-3** show the pin assignments for different packages.

| Pin Name   | Pin Name         | Pin Name   | Pin Name   | Pin Name   | Powered |                | al Pull<br>sistor | Description                                                                                |

|------------|------------------|------------|------------|------------|---------|----------------|-------------------|--------------------------------------------------------------------------------------------|

| Function 1 | Function 2       | Function 3 | Function 4 | Function 5 | by      | CTRL           | Reset<br>State    | Description                                                                                |

| PH6        | KWH6             |            | _          | _          | VDDR    | PERH/<br>PPSH  | Disabled          | Port H I/O, Interrupt                                                                      |

| PH5        | KWH5             |            | _          | _          | VDDR    | PERH/<br>PPSH  | Disabled          | Port H I/O, Interrupt                                                                      |

| PH4        | KWH4             |            | _          | _          | VDDR    | PERH/<br>PPSH  | Disabled          | Port H I/O, Interrupt                                                                      |

| PH3        | кwнз             | SS1        | _          | _          | VDDR    | PERH/<br>PPSH  | Disabled          | Port H I/O, Interrupt,<br>SS of SPI1                                                       |

| PH2        | KWH2             | SCK1       | —          | —          | VDDR    | PERH/<br>PPSH  | Disabled          | Port H I/O, Interrupt,<br>SCK of SPI1                                                      |

| PH1        | KWH1             | MOSI1      | —          | —          | VDDR    | PERH/<br>PPSH  | Disabled          | Port H I/O, Interrupt,<br>MOSI of SPI1                                                     |

| PH0        | КЖНО             | MISO1      | —          | —          | VDDR    | PERH/<br>PPSH  | Disabled          | Port H I/O, Interrupt,<br>MISO of SPI1                                                     |

| PJ7        | KWJ7             | TXCAN4     | SCL        | TXCAN0     | VDDX    | PERJ/<br>PPSJ  | Up                | Port J I/O, Interrupt,<br>TX of CAN4, SCL of<br>IIC                                        |

| PJ6        | KWJ6             | RXCAN4     | SDA        | RXCAN0     | VDDX    | PERJ/<br>PPSJ  | Up                | Port J I/O, Interrupt,<br>RX of CAN4, SDA of<br>IIC                                        |

| PJ[1:0]    | KWJ[1:0]         | _          | _          | —          | VDDX    | PERJ/<br>PPSJ  | Up                | Port J I/O, Interrupts                                                                     |

| PK7        | ECS              | ROMCTL     | _          | _          | VDDX    | PUCR/<br>PUPKE | Up                | Port K I/O,<br>Emulation Chip<br>Select, ROM Control                                       |

| PK[5:0]    | XADDR[19:<br>14] | _          | _          | _          | VDDX    | PUCR/<br>PUPKE | Up                | Port K I/O, Extended<br>Addresses                                                          |

| PM7        | BF_PSLM          | TXCAN4     | _          | _          | VDDX    | PERM/<br>PPSM  | Disabled          | Port M I/O, BF slot<br>mismatch pulse, TX<br>of CAN4                                       |

| РМ6        | BF_PERR          | RXCAN4     | _          | _          | VDDX    | PERM/<br>PPSM  | Disabled          | Port M I/O, BF illegal<br>pulse/message<br>format error pulse,<br>RX of CAN4               |

| PM5        | BF_PROK          | TXCAN0     | TXCAN4     | SCK0       | VDDX    | PERM/<br>PPSM  | Disabled          | Port M I/O, BF<br>reception ok pulse,<br>TX of CAN0, CAN4,<br>SCK of SPI0                  |

| PM4        | BF_PSYN          | RXCAN0     | RXCAN4     | MOSI0      | VDDX    | PERM/<br>PPSM  | Disabled          | Port M I/O, BF sync<br>pulse (Rx/Tx) OK<br>pulse o/p, RX of<br>CAN0, CAN4, MOSI<br>of SPI0 |

| PM3        | TX_BF            | TXCAN1     | TXCAN0     | <u>SS0</u> | VDDX    | PERM/<br>PPSM  | Disabled          | Port M I/O, TX of BF,<br>CAN1, CAN0, SS of<br>SPI0                                         |

| PM2        | RX_BF            | RXCAN1     | RXCAN0     | MISO0      | VDDX    | PERM/<br>PPSM  | Disabled          | Port M I/O, RX of BF,<br>CAN1, CAN0, MISO<br>of SPI0                                       |

## 2.3.43 PP5 / KWP5 / PWM5 — Port P I/O Pin 5

PP5 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 5 output.

## 2.3.44 PP4 / KWP4 / PWM4 — Port P I/O Pin 4

PP4 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 4 output.

## 2.3.45 PP3 / KWP3 / PWM3 / SS1 — Port P I/O Pin 3

PP3 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 3 output. It can be configured as slave select pin  $\overline{SS}$  of the Serial Peripheral Interface 1 (SPI1).

## 2.3.46 PP2 / KWP2 / PWM2 / SCK1 — Port P I/O Pin 2

PP2 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 2 output. It can be configured as serial clock pin SCK of the Serial Peripheral Interface 1 (SPI1).

## 2.3.47 PP1 / KWP1 / PWM1 / MOSI1 — Port P I/O Pin 1

PP1 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 1 output. It can be configured as master output (during master mode) or slave input pin (during slave mode) MOSI of the Serial Peripheral Interface 1 (SPI1).

## 2.3.48 PP0 / KWP0 / PWM0 / MISO1 — Port P I/O Pin 0

PP0 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 0 output. It can be configured as master input (during master mode) or slave output (during slave mode) pin MISO of the Serial Peripheral Interface 1 (SPI1).

## 2.3.49 PS7 / SS0 — Port S I/O Pin 7

PS7 is a general purpose input or output pin. It can be configured as the slave select pin  $\overline{SS}$  of the Serial Peripheral Interface 0 (SPI0).

## 2.3.50 PS6 / SCK0 — Port S I/O Pin 6

PS6 is a general purpose input or output pin. It can be configured as the serial clock pin SCK of the Serial Peripheral Interface 0 (SPI0).

| VREGEN | Description                                                                                  |  |  |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1      | Internal Voltage Regulator enabled                                                           |  |  |  |  |  |  |  |

|        | Internal Voltage Regulator disabled, VDD1,2 and VDDPLL must be supplied externally with 2.5V |  |  |  |  |  |  |  |

#### Table 4-3 Voltage Regulator VREGEN

# 4.3 Security

The device will make available a security feature preventing the unauthorized read and write of the memory contents. This feature allows:

- Protection of the contents of FLASH,

- Protection of the contents of EEPROM,

- Operation in single-chip mode, No BDM possible

- Operation from external memory with internal FLASH and EEPROM disabled.

The user must be reminded that part of the security must lie with the user's code. An extreme example would be user's code that dumps the contents of the internal program. This code would defeat the purpose of security. At the same time the user may also wish to put a back door in the user's program. An example of this is the user downloads a key through the SCI which allows access to a programming routine that updates parameters stored in EEPROM.

### 4.3.1 Securing the Microcontroller

Once the user has programmed the FLASH and EEPROM (if desired), the part can be secured by programming the security bits located in the FLASH module. These non-volatile bits will keep the part secured through resetting the part and through powering down the part.

The security byte resides in a portion of the Flash array.

Check the Flash Block User Guide for more details on the security configuration.

### 4.3.2 Operation of the Secured Microcontroller

#### 4.3.2.1 Normal Single Chip Mode

This will be the most common usage of the secured part. Everything will appear the same as if the part was not secured with the exception of BDM operation. The BDM operation will be blocked.

#### 4.3.2.2 Executing from External Memory

The user may wish to execute from external space with a secured microcontroller. This is accomplished by resetting directly into expanded mode. The internal FLASH and EEPROM will be disabled. BDM operations will be blocked.

Consult the ECT\_16B8C Block User Guide for information about the Enhanced Capture Timer module. When the ECT\_16B8C Block User Guide refers to *freeze mode* this is equivalent to *active BDM mode*.

# Section 10 Analog to Digital Converter (ATD) Block Description

There are two Analog to Digital Converters (ATD1 and ATD0) implemented on the MC9S12DT128. Consult the ATD\_10B8C Block User Guide for information about each Analog to Digital Converter module. When the ATD\_10B8C Block User Guide refers to *freeze mode* this is equivalent to *active BDM mode*.

# Section 11 Inter-IC Bus (IIC) Block Description

Consult the IIC Block User Guide for information about the Inter-IC Bus module.

# Section 12 Serial Communications Interface (SCI) Block Description

There are two Serial Communications Interfaces (SCI1 and SCI0) implemented on the MC9S12DT128 device. Consult the SCI Block User Guide for information about each Serial Communications Interface module.

# Section 13 Serial Peripheral Interface (SPI) Block Description

There are two Serial Peripheral Interfaces (SPI1 and SPI0) implemented on MC9S12DT128. Consult the SPI Block User Guide for information about each Serial Peripheral Interface module.

# Section 14 J1850 (BDLC) Block Description

Consult the BDLC Block User Guide for information about the J1850 module.

# Section 15 Byteflight (BF) Block Description

Consult the BF Block User Guide for information about the 10 Mbps Byteflight module.

# **Appendix A Electrical Characteristics**

# A.1 General

This introduction is intended to give an overview on several common topics like power supply, current injection etc.

## A.1.1 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate.

P:

Those parameters are guaranteed during production testing on each individual device.

C:

Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations. They are regularly verified by production monitors.

T:

Those parameters are achieved by design characterization on a small sample size from typical devices. All values shown in the typical column are within this category.

D:

Those parameters are derived mainly from simulations.

## A.1.2 Power Supply

The MC9S12DT128 utilizes several pins to supply power to the I/O ports, A/D converter, oscillator, PLL and internal logic.

The VDDA, VSSA pair supplies the A/D converter and the resistor ladder of the internal voltage regulator.

The VDDX, VSSX, VDDR and VSSR pairs supply the I/O pins, VDDR supplies also the internal voltage regulator.

VDD1, VSS1, VDD2 and VSS2 are the supply pins for the digital logic, VDDPLL, VSSPLL supply the oscillator and the PLL.

VSS1 and VSS2 are internally connected by metal.

VDDA, VDDX, VDDR as well as VSSA, VSSX, VSSR are connected by anti-parallel diodes for ESD protection.

## A.2.3 ATD accuracy

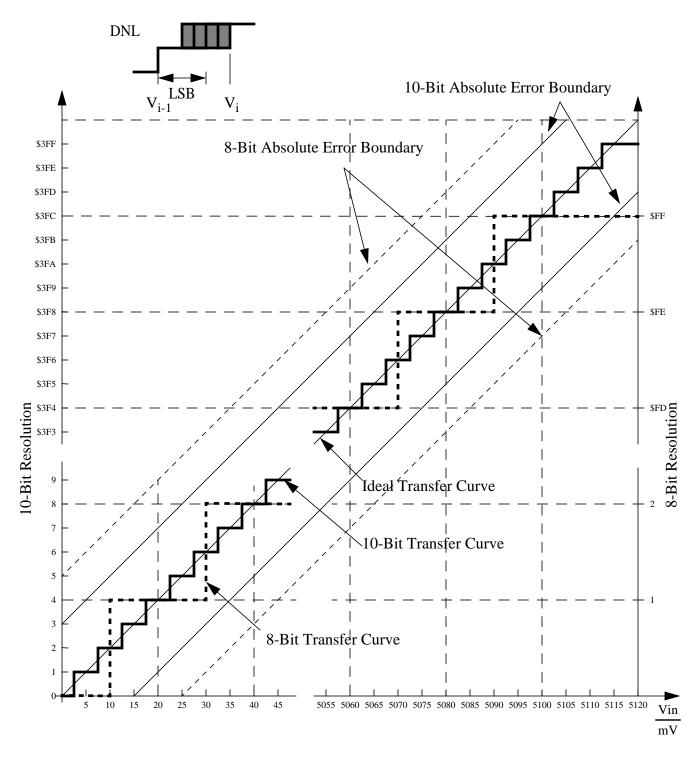

**(Table A-10)** specifies the ATD conversion performance excluding any errors due to current injection, input capacitance and source resistance.

| V <sub>REF</sub> = | Conditions are shown in <b>(Table A-4)</b> unless otherwise noted<br>$V_{REF} = V_{RH} - V_{RL} = 5.12V$ . Resulting to one 8 bit count = 20mV and one 10 bit count = 5mV<br>ATDCLK = 2.0MHz |                                     |        |      |      |     |        |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|------|------|-----|--------|--|--|--|--|

| Num                | С                                                                                                                                                                                            | Rating                              | Symbol | Min  | Тур  | Max | Unit   |  |  |  |  |

| 1                  | Ρ                                                                                                                                                                                            | 10-Bit Resolution                   | LSB    |      | 5    |     | mV     |  |  |  |  |

| 2                  | Ρ                                                                                                                                                                                            | 10-Bit Differential Nonlinearity    | DNL    | -1   |      | 1   | Counts |  |  |  |  |

| 3                  | Ρ                                                                                                                                                                                            | 10-Bit Integral Nonlinearity        | INL    | -2.5 | ±1.5 | 2.5 | Counts |  |  |  |  |

| 4                  | Ρ                                                                                                                                                                                            | 10-Bit Absolute Error <sup>1</sup>  | AE     | -3   | ±2.0 | 3   | Counts |  |  |  |  |

| 5                  | Ρ                                                                                                                                                                                            | 8-Bit Resolution                    | LSB    |      | 20   |     | mV     |  |  |  |  |

| 6                  | Ρ                                                                                                                                                                                            | 8-Bit Differential Nonlinearity     | DNL    | -0.5 |      | 0.5 | Counts |  |  |  |  |

| 7                  | Ρ                                                                                                                                                                                            | 8-Bit Integral Nonlinearity         | INL    | -1.0 | ±0.5 | 1.0 | Counts |  |  |  |  |

| 8                  | Ρ                                                                                                                                                                                            | 8-Bit Absolute Error <sup>(1)</sup> | AE     | -1.5 | ±1.0 | 1.5 | Counts |  |  |  |  |

#### Table A-10 ATD Conversion Performance

NOTES:

1. These values include the quantization error which is inherently 1/2 count for any A/D converter.

For the following definitions see also Figure A-1.

Differential Non-Linearity (DNL) is defined as the difference between two adjacent switching steps.

$$\mathsf{DNL}(i) = \frac{\mathsf{V}_i - \mathsf{V}_{i-1}}{\mathsf{1LSB}} - \mathsf{1}$$

The Integral Non-Linearity (INL) is defined as the sum of all DNLs:

$$INL(n) = \sum_{i=1}^{n} DNL(i) = \frac{V_n - V_0}{1LSB} - n$$

Figure A-1 ATD Accuracy Definitions

Clock Monitor Failure is asserted if the frequency of the incoming clock signal is below the Assert Frequency  $\rm f_{CMFA.}$

| Num | С | Rating                                                   | Symbol                 | Min                      | Тур            | Max                      | Unit |

|-----|---|----------------------------------------------------------|------------------------|--------------------------|----------------|--------------------------|------|

| 1a  | C | Crystal oscillator range (Colpitts)                      | f <sub>osc</sub>       | 0.5                      | - 76           | 16                       | MHz  |

|     | - |                                                          |                        |                          |                |                          |      |

| 1b  | С | Crystal oscillator range (Pierce) <sup>1</sup>           | fosc                   | 0.5                      |                | 40                       | MHz  |

| 2   | Ρ | Startup Current                                          | iosc                   | 100                      |                |                          | μA   |

| 3   | С | Oscillator start-up time (Colpitts)                      | t <sub>UPOSC</sub>     |                          | 8 <sup>2</sup> | 100 <sup>3</sup>         | ms   |

| 4   | D | Clock Quality check time-out                             | t <sub>CQOUT</sub>     | 0.45                     |                | 2.5                      | S    |

| 5   | Ρ | Clock Monitor Failure Assert Frequency                   | f <sub>CMFA</sub>      | 50                       | 100            | 200                      | KHz  |

| 6   | Ρ | External square wave input frequency <sup>4</sup>        | f <sub>EXT</sub>       | 0.5                      |                | 50                       | MHz  |

| 7   | D | External square wave pulse width low                     | t <sub>EXTL</sub>      | 9.5                      |                |                          | ns   |

| 8   | D | External square wave pulse width high                    | t <sub>EXTH</sub>      | 9.5                      |                |                          | ns   |

| 9   | D | External square wave rise time                           | t <sub>EXTR</sub>      |                          |                | 1                        | ns   |

| 10  | D | External square wave fall time                           | t <sub>EXTF</sub>      |                          |                | 1                        | ns   |

| 11  | D | Input Capacitance (EXTAL, XTAL pins)                     | C <sub>IN</sub>        |                          | 7              |                          | pF   |

| 12  | с | DC Operating Bias in Colpitts Configuration on EXTAL Pin | V <sub>DCBIAS</sub>    |                          | 1.1            |                          | V    |

| 13  | Ρ | EXTAL Pin Input High Voltage <sup>4</sup>                | V <sub>IH,EXTAL</sub>  | 0.75*V <sub>DDPLL</sub>  |                |                          | V    |

|     | Т | EXTAL Pin Input High Voltage <sup>4</sup>                | V <sub>IH,EXTAL</sub>  |                          |                | V <sub>DDPLL</sub> + 0.3 | V    |

| 14  | Р | EXTAL Pin Input Low Voltage <sup>4</sup>                 | V <sub>IL,EXTAL</sub>  |                          |                | 0.25*V <sub>DDPLL</sub>  | V    |

|     | Т | EXTAL Pin Input Low Voltage <sup>4</sup>                 | VIL,EXTAL              | V <sub>SSPLL</sub> - 0.3 |                |                          | V    |

| 15  | С | EXTAL Pin Input Hysteresis <sup>4</sup>                  | V <sub>HYS,EXTAL</sub> |                          | 250            |                          | mV   |

| Table A-15 | Oscillator | Characteristics |

|------------|------------|-----------------|

|            |            |                 |

NOTES:

1. Depending on the crystal a damping series resistor might be necessary

2.  $f_{osc} = 4MHz$ , C = 22pF.

3. Maximum value is for extreme cases using high Q, low frequency crystals

4. XCLKS =0 during reset

## A.5.3 Phase Locked Loop

The oscillator provides the reference clock for the PLL. The PLL's Voltage Controlled Oscillator (VCO) is also the system clock source in self clock mode.

#### A.5.3.1 XFC Component Selection

This section describes the selection of the XFC components to achieve a good filter characteristics.

This is very important to notice with respect to timers, serial modules where a pre-scaler will eliminate the effect of the jitter to a large extent.

| Condit | ions | s are shown in (Table A-4) unless otherwise noted          |                    |     |      |      |                  |

|--------|------|------------------------------------------------------------|--------------------|-----|------|------|------------------|

| Num    | С    | Rating                                                     | Symbol             | Min | Тур  | Max  | Unit             |

| 1      | Ρ    | Self Clock Mode frequency                                  | f <sub>SCM</sub>   | 1   |      | 5.5  | MHz              |

| 2      | D    | VCO locking range                                          | f <sub>VCO</sub>   | 8   |      | 50   | MHz              |

| 3      | D    | Lock Detector transition from Acquisition to Tracking mode | $ \Delta_{trk} $   | 3   |      | 4    | % <sup>1</sup>   |

| 4      | D    | Lock Detection                                             | $ \Delta_{Lock} $  | 0   |      | 1.5  | % <sup>(1)</sup> |

| 5      | D    | Un-Lock Detection                                          | $ \Delta_{unl} $   | 0.5 |      | 2.5  | % <sup>(1)</sup> |

| 6      | D    | Lock Detector transition from Tracking to Acquisition mode | $ \Delta_{unt} $   | 6   |      | 8    | % <sup>(1)</sup> |

| 7      | С    | PLLON Total Stabilization delay (Auto Mode) <sup>2</sup>   | t <sub>stab</sub>  |     | 0.5  |      | ms               |

| 8      | D    | PLLON Acquisition mode stabilization delay <sup>(2)</sup>  | t <sub>acq</sub>   |     | 0.3  |      | ms               |

| 9      | D    | PLLON Tracking mode stabilization delay <sup>(2)</sup>     | t <sub>al</sub>    |     | 0.2  |      | ms               |

| 10     | D    | Fitting parameter VCO loop gain                            | K <sub>1</sub>     |     | -100 |      | MHz/V            |

| 11     | D    | Fitting parameter VCO loop frequency                       | f <sub>1</sub>     |     | 60   |      | MHz              |

| 12     | D    | Charge pump current acquisition mode                       | ∣i <sub>ch</sub> ∣ |     | 38.5 |      | μA               |

| 13     | D    | Charge pump current tracking mode                          | ∣i <sub>ch</sub> ∣ |     | 3.5  |      | μA               |

| 14     | С    | Jitter fit parameter 1 <sup>(2)</sup>                      | j <sub>1</sub>     |     |      | 1.1  | %                |

| 15     | С    | Jitter fit parameter 2 <sup>(2)</sup>                      | j <sub>2</sub>     |     |      | 0.13 | %                |

**Table A-16 PLL Characteristics**

NOTES:

% deviation from target frequency

f<sub>OSC</sub> = 4MHz, f<sub>BUS</sub> = 25MHz equivalent f<sub>VCO</sub> = 50MHz: REFDV = #\$03, SYNR = #\$018, Cs = 4.7nF, Cp = 470pF, Rs = 10KΩ.