Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 91                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                           |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 112-LQFP                                                                |

| Supplier Device Package    | 112-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12dt128cpve |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

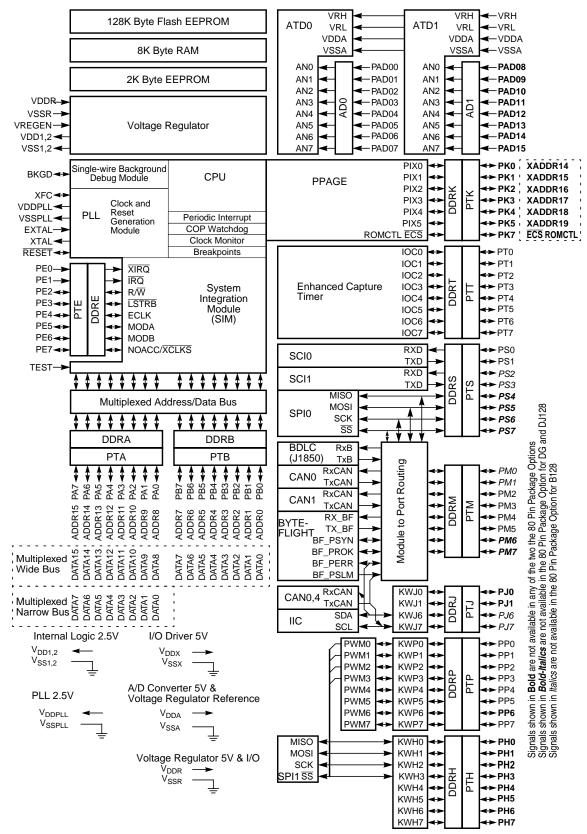

#### Device User Guide — 9S12DT128DGV2/D V02.17

- Digital filtering

- Programmable rising or falling edge trigger

- Memory

- 128K Flash EEPROM

- 2K byte EEPROM

- 8K byte RAM

- Two 8-channel Analog-to-Digital Converters

- 10-bit resolution

- External conversion trigger capability

- Three 1M bit per second, CAN 2.0 A, B software compatible modules

- Five receive and three transmit buffers

- Flexible identifier filter programmable as 2 x 32 bit, 4 x 16 bit or 8 x 8 bit

- Four separate interrupt channels for Rx, Tx, error and wake-up

- Low-pass filter wake-up function

- Loop-back for self test operation

- Enhanced Capture Timer

- 16-bit main counter with 7-bit prescaler

- 8 programmable input capture or output compare channels

- Four 8-bit or two 16-bit pulse accumulators

- 8 PWM channels

- Programmable period and duty cycle

- 8-bit 8-channel or 16-bit 4-channel

- Separate control for each pulse width and duty cycle

- Center-aligned or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

- Fast emergency shutdown input

- Usable as interrupt inputs

- Serial interfaces

- Two asynchronous Serial Communications Interfaces (SCI)

- Two Synchronous Serial Peripheral Interface (SPI)

- Byteflight

- Byte Data Link Controller (BDLC)

Figure 1-1 MC9S12DT128 Block Diagram

### \$0140 - \$017F CAN0 (Motorola Scalable CAN - MSCAN)

| Address            | Name                     |                 | Bit 7   | Bit 6  | Bit 5   | Bit 4      | Bit 3  | Bit 2             | Bit 1  | Bit 0  |

|--------------------|--------------------------|-----------------|---------|--------|---------|------------|--------|-------------------|--------|--------|

| \$0146             | <b>CAN0TFLG</b>          | Read:           | 0       | 0      | 0       | 0          | 0      | TXE2              | TXE1   | TXE0   |

| φ01 <del>4</del> 0 | CANOTFLO                 | Write:          |         |        |         |            |        | INEZ              | IVEI   | TAEU   |

| \$0147             | <b>CAN0TIER</b>          | Read:           | 0       | 0      | 0       | 0          | 0      | TXEIE2            | TXEIE1 | TXEIE0 |

| φστη               | O, a to HEIT             | Write:          |         |        |         |            |        |                   |        | IXEIEO |

| \$0148             | <b>CAN0TARQ</b>          | Read:           | 0       | 0      | 0       | 0          | 0      | ABTRQ2            | ABTRQ1 | ABTRQ0 |

| ·                  |                          | Write:          | 0       | 0      | 0       | 0          | 0      |                   |        |        |

| \$0149             | <b>CAN0TAAK</b>          | Read:           | 0       | 0      | 0       | 0          | 0      | ABTAK2            | ABTAK1 | ABTAK0 |

|                    |                          | Write:<br>Read: | 0       | 0      | 0       | 0          | 0      |                   |        |        |

| \$014A             | CAN0TBSEL                | Write:          | 0       | 0      | 0       | 0          | 0      | TX2               | TX1    | TX0    |

|                    |                          | Read:           | 0       | 0      |         |            | 0      | IDHIT2            | IDHIT1 | IDHIT0 |

| \$014B             | CAN0IDAC                 | Write:          |         |        | IDAM1   | IDAM0      |        |                   |        |        |

| <b>00440</b>       |                          | Read:           | 0       | 0      | 0       | 0          | 0      | 0                 | 0      | 0      |

| \$014C             | Reserved                 | Write:          |         |        |         |            |        |                   |        |        |

| \$014D             | Reserved                 | Read:           | 0       | 0      | 0       | 0          | 0      | 0                 | 0      | 0      |

| ψ014D              | Reserved                 | Write:          |         |        |         |            |        |                   |        |        |

| \$014E             | CANORXERR                | Read:           | RXERR7  | RXERR6 | RXERR5  | RXERR4     | RXERR3 | RXERR2            | RXERR1 | RXERR0 |

| φor i Ε            | e, a ter e ter e         | Write:          |         |        |         |            |        |                   |        |        |

| \$014F             | CAN0TXERR                | Read:           | TXERR7  | TXERR6 | TXERR5  | TXERR4     | TXERR3 | TXERR2            | TXERR1 | TXERR0 |

|                    |                          | Write:          |         |        |         |            |        |                   |        |        |

| \$0150 -<br>\$0153 | CAN0IDAR0 -<br>CAN0IDAR3 | Read:           | AC7     | AC6    | AC5     | AC4        | AC3    | AC2               | AC1    | AC0    |

| \$0153<br>\$0154 - | CANOIDARS                | Write:<br>Read: |         |        |         |            |        |                   |        |        |

| \$0154 -<br>\$0157 | CANOIDMR0                | Write:          | AM7     | AM6    | AM5     | AM4        | AM3    | AM2               | AM1    | AM0    |

| \$0158 -           | CANOIDAR4 -              | Read:           |         |        |         |            |        |                   |        |        |

| \$015B             | CAN0IDAR7                | Write:          | AC7     | AC6    | AC5     | AC4        | AC3    | AC2               | AC1    | AC0    |

| \$015C -           | CAN0IDMR4 -              | Read:           | A N 4 7 | 4140   | A.N.4.5 | A. N. 4. 4 | 4140   | 4140              | A      | 4140   |

| \$015F             | CAN0IDMR7                | Write:          | AM7     | AM6    | AM5     | AM4        | AM3    | AM2               | AM1    | AM0    |

| \$0160 -           | CANORXFG                 | Read:           |         | FOR    | EGROUN  | O RECEIVE  | BUFFER | see <b>(Table</b> | 1-2)   |        |

| \$016F             | GANOIXAFG                | Write:          |         |        |         |            |        |                   |        |        |

| \$0170 -<br>\$017F | CAN0TXFG                 | Read:<br>Write: |         |        |         |            |        |                   |        |        |

| φστη               |                          | wine.           | · · ·   |        |         |            |        |                   |        |        |

### Table 1-2 Detailed MSCAN Foreground Receive and Transmit Buffer Layout

|         |             |        |       | -     |       |       |       |       |       |       |

|---------|-------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Name        |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|         | Extended ID | Read:  | ID28  | ID27  | ID26  | ID25  | ID24  | ID23  | ID22  | ID21  |

| \$xxx0  | Standard ID | Read:  | ID10  | ID9   | ID8   | ID7   | ID6   | ID5   | ID4   | ID3   |

|         | CANxRIDR0   | Write: |       |       |       |       |       |       |       |       |

|         | Extended ID | Read:  | ID20  | ID19  | ID18  | SRR=1 | IDE=1 | ID17  | ID16  | ID15  |

| \$xxx1  | Standard ID | Read:  | ID2   | ID1   | ID0   | RTR   | IDE=0 |       |       |       |

|         | CANxRIDR1   | Write: |       |       |       |       |       |       |       |       |

|         | Extended ID | Read:  | ID14  | ID13  | ID12  | ID11  | ID10  | ID9   | ID8   | ID7   |

| \$xxx2  | Standard ID | Read:  |       |       |       |       |       |       |       |       |

|         | CANxRIDR2   | Write: |       |       |       |       |       |       |       |       |

|         | Extended ID | Read:  | ID6   | ID5   | ID4   | ID3   | ID2   | ID1   | ID0   | RTR   |

| \$xxx3  | Standard ID | Read:  |       |       |       |       |       |       |       |       |

|         | CANxRIDR3   | Write: |       |       |       |       |       |       |       |       |

| \$xxx4- | CANxRDSR0 - | Read:  | DB7   | DB6   | DB5   | DB4   | DB3   | DB2   | DB1   | DB0   |

| \$xxxB  | CANxRDSR7   | Write: |       |       |       |       |       |       |       |       |

#### \$0180 - \$01BF CAN1

CAN1 (Motorola Scalable CAN - MSCAN)

| Address                | Name                     | 1               | Bit 7                                      | Bit 6     | Bit 5   | Bit 4     | Bit 3   | Bit 2             | Bit 1     | Bit 0   |

|------------------------|--------------------------|-----------------|--------------------------------------------|-----------|---------|-----------|---------|-------------------|-----------|---------|

| \$0185                 | CAN1RIER                 | Read:<br>Write: | WUPIE                                      | CSCIE     | RSTATE1 | RSTATE0   | TSTATE1 | TSTATE0           | OVRIE     | RXFIE   |

| \$0186                 | CAN1TFLG                 | Read:           | 0                                          | 0         | 0       | 0         | 0       | TXE2              | TXE1      | TXE0    |

|                        |                          | Write:          | 0                                          | 0         |         | 0         | 0       |                   |           |         |

| \$0187                 | CAN1TIER                 | Read:<br>Write: | 0                                          | 0         | 0       | 0         | 0       | TXEIE2            | TXEIE1    | TXEIE0  |

|                        |                          | Read:           | 0                                          | 0         | 0       | 0         | 0       |                   |           |         |

| \$0188                 | CAN1TARQ                 | Write:          | -                                          | -         | -       | -         | -       | ABTRQ2            | ABTRQ1    | ABTRQ0  |

| \$0189                 | CAN1TAAK                 | Read:           | 0                                          | 0         | 0       | 0         | 0       | ABTAK2            | ABTAK1    | ABTAK0  |

| ψ0103                  | OANTIAAN                 | Write:          |                                            |           |         |           |         |                   |           |         |

| \$018A                 | CAN1TBSEL                | Read:           | 0                                          | 0         | 0       | 0         | 0       | TX2               | TX1       | TX0     |

|                        |                          | Write:<br>Read: | 0                                          | 0         |         |           | 0       | IDHIT2            | IDHIT1    | IDHIT0  |

| \$018B                 | CAN1IDAC                 | Write:          | 0                                          | 0         | IDAM1   | IDAM0     | 0       |                   |           |         |

| <b>\$</b> 040 <b>0</b> |                          | Read:           | 0                                          | 0         | 0       | 0         | 0       | 0                 | 0         | 0       |

| \$018C                 | Reserved                 | Write:          |                                            |           |         |           |         |                   |           |         |

| \$018D                 | Reserved                 | Read:           | 0                                          | 0         | 0       | 0         | 0       | 0                 | 0         | 0       |

| <b>40.02</b>           |                          | Write:          |                                            |           | DVEDDE  |           | DVEDDO  |                   |           |         |

| \$018E                 | CAN1RXERR                | Read:<br>Write: | RXERR7                                     | RXERR6    | RXERR5  | RXERR4    | RXERR3  | RXERR2            | RXERR1    | RXERR0  |

|                        |                          | Read:           | TXERR7                                     | TXERR6    | TXERR5  | TXERR4    | TXERR3  | TXERR2            | TXERR1    | TXERR0  |

| \$018F                 | CAN1TXERR                | Write:          | T/LETCI CI                                 | T/LET (10 | TALITIO | TALLAR    | TALITIE | TYTE THE          | T/LET(IT) | INEITIO |

| \$0190 -<br>\$0193     | CAN1IDAR0 -<br>CAN1IDAR3 | Read:<br>Write: | AC7                                        | AC6       | AC5     | AC4       | AC3     | AC2               | AC1       | AC0     |

| \$0194 -<br>\$0197     | CAN1IDMR0 -<br>CAN1IDMR3 | Read:<br>Write: | AM7                                        | AM6       | AM5     | AM4       | AM3     | AM2               | AM1       | AM0     |

| \$0198 -<br>\$019B     | CAN1IDAR4 -<br>CAN1IDAR7 | Read:<br>Write: | AC7                                        | AC6       | AC5     | AC4       | AC3     | AC2               | AC1       | AC0     |

| \$019C -<br>\$019F     | CAN1IDMR4 -<br>CAN1IDMR7 | Read:<br>Write: | AM7                                        | AM6       | AM5     | AM4       | AM3     | AM2               | AM1       | AM0     |

| \$01A0 -               | CAN0RXFG                 | Read:           |                                            | FOR       | EGROUNI | O RECEIVE | BUFFER  | see <b>(Table</b> | 1-2)      |         |

| \$01AF                 | CANUKAFG                 | Write:          |                                            |           |         |           |         |                   |           |         |

| \$01B0 -<br>\$01BF     | CAN0TXFG                 | Read:<br>Write: | EOREGROUND TRANSMIT BUFFER see (Table 1-2) |           |         |           |         |                   |           |         |

#### \$01C0 - \$01FF

#### Reserved

| Address  | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$01C0 - | Basarvad | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$01FF   | Reserved | Write: |       |       |       |       |       |       |       |       |

#### \$0200 - \$023F

#### Reserved

| Address  | Name      |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$020C - | Percented | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$023F   | Reserved  | Write: |       |       |       |       |       |       |       |       |

\$0240 - \$027F

### **PIM (Port Integration Module)**

| Address       | Name     |                 | Bit 7   | Bit 6   | Bit 5  | Bit 4      | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|---------------|----------|-----------------|---------|---------|--------|------------|---------|---------|--------|--------|

| \$0240        | PTT      | Read:<br>Write: | PTT7    | PTT6    | PTT5   | PTT4       | PTT3    | PTT2    | PTT1   | PTT0   |

| \$0241        | PTIT     | Read:           | PTIT7   | PTIT6   | PTIT5  | PTIT4      | PTIT3   | PTIT2   | PTIT1  | PTIT0  |

| <i>фо</i> 211 |          | Write:<br>Read: |         |         |        |            |         |         |        |        |

| \$0242        | DDRT     | Write:          | DDRT7   | DDRT7   | DDRT5  | DDRT4      | DDRT3   | DDRT2   | DDRT1  | DDRT0  |

| \$0243        | RDRT     | Read:<br>Write: | RDRT7   | RDRT6   | RDRT5  | RDRT4      | RDRT3   | RDRT2   | RDRT1  | RDRT0  |

| \$0244        | PERT     | Read:<br>Write: | PERT7   | PERT6   | PERT5  | PERT4      | PERT3   | PERT2   | PERT1  | PERT0  |

| \$0245        | PPST     | Read:<br>Write: | PPST7   | PPST6   | PPST5  | PPST4      | PPST3   | PPST2   | PPST1  | PPST0  |

| \$0246        | Reserved | Read:           | 0       | 0       | 0      | 0          | 0       | 0       | 0      | 0      |

|               |          | Write:          | 0       | 0       | 0      | 0          | 0       | 0       | 0      | 0      |

| \$0247        | Reserved | Read:<br>Write: | 0       | 0       | 0      | 0          | 0       | 0       | 0      | 0      |

| \$0248        | PTS      | Read:<br>Write: | PTS7    | PTS6    | PTS5   | PTS4       | PTS3    | PTS2    | PTS1   | PTS0   |

| \$0249        | PTIS     | Read:           | PTIS7   | PTIS6   | PTIS5  | PTIS4      | PTIS3   | PTIS2   | PTIS1  | PTIS0  |

|               |          | Write:<br>Read: |         |         |        |            |         |         |        |        |

| \$024A        | DDRS     | Write:          | DDRS7   | DDRS7   | DDRS5  | DDRS4      | DDRS3   | DDRS2   | DDRS1  | DDRS0  |

| \$024B        | RDRS     | Read:<br>Write: | RDRS7   | RDRS6   | RDRS5  | RDRS4      | RDRS3   | RDRS2   | RDRS1  | RDRS0  |

| \$024C        | PERS     | Read:<br>Write: | PERS7   | PERS6   | PERS5  | PERS4      | PERS3   | PERS2   | PERS1  | PERS0  |

| \$024D        | PPSS     | Read:<br>Write: | PPSS7   | PPSS6   | PPSS5  | PPSS4      | PPSS3   | PPSS2   | PPSS1  | PPSS0  |

| \$024E        | WOMS     | Read:<br>Write: | WOMS7   | WOMS6   | WOMS5  | WOMS4      | WOMS3   | WOMS2   | WOMS1  | WOMS0  |

| \$024F        | Reserved | Read:<br>Write: | 0       | 0       | 0      | 0          | 0       | 0       | 0      | 0      |

| \$0250        | PTM      | Read:           | PTM7    | PTM6    | PTM5   | PTM4       | PTM3    | PTM2    | PTM1   | PTM0   |

| <b>\$0200</b> | 1 1101   | Write:<br>Read: | PTIM7   | PTIM6   | PTIM5  | PTIM4      | PTIM3   | PTIM2   | PTIM1  | PTIM0  |

| \$0251        | PTIM     | Write:          | 1 11117 | 1 11110 | 1 1100 | 1 1 1111-1 | 1 11010 | 1 11112 |        | TTIMO  |

| \$0252        | DDRM     | Read:<br>Write: | DDRM7   | DDRM7   | DDRM5  | DDRM4      | DDRM3   | DDRM2   | DDRM1  | DDRM0  |

| \$0253        | RDRM     | Read:<br>Write: | RDRM7   | RDRM6   | RDRM5  | RDRM4      | RDRM3   | RDRM2   | RDRM1  | RDRM0  |

| \$0254        | PERM     | Read:<br>Write: | PERM7   | PERM6   | PERM5  | PERM4      | PERM3   | PERM2   | PERM1  | PERM0  |

| \$0255        | PPSM     | Read:<br>Write: | PPSM7   | PPSM6   | PPSM5  | PPSM4      | PPSM3   | PPSM2   | PPSM1  | PPSM0  |

| \$0256        | WOMM     | Read:<br>Write: | WOMM7   | WOMM6   | WOMM5  | WOMM4      | WOMM3   | WOMM2   | WOMM1  | WOMM0  |

| \$0257        | MODRR    | Read:           | 0       | 0       | MODRR5 | MODRR4     | MODRR3  | MODRR2  | MODRR1 | MODRR0 |

|               |          | Write:<br>Read: |         |         |        |            |         |         |        |        |

| \$0258        | PTP      | Write:          | PTP7    | PTP6    | PTP5   | PTP4       | PTP3    | PTP2    | PTP1   | PTP0   |

### \$0240 - \$027F

## PIM (Port Integration Module)

| Address  | Name     |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0259   | PTIP     | Read:           | PTIP7 | PTIP6 | PTIP5 | PTIP4 | PTIP3 | PTIP2 | PTIP1 | PTIP0 |

| φ0209    | FIIF     | Write:          |       |       |       |       |       |       |       |       |

| \$025A   | DDRP     | Read:<br>Write: | DDRP7 | DDRP7 | DDRP5 | DDRP4 | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| \$025B   | RDRP     | Read:<br>Write: | RDRP7 | RDRP6 | RDRP5 | RDRP4 | RDRP3 | RDRP2 | RDRP1 | RDRP0 |

| \$025C   | PERP     | Read:<br>Write: | PERP7 | PERP6 | PERP5 | PERP4 | PERP3 | PERP2 | PERP1 | PERP0 |

| \$025D   | PPSP     | Read:<br>Write: | PPSP7 | PPSP6 | PPSP5 | PPSP4 | PPSP3 | PPSP2 | PPSP1 | PPSS0 |

| \$025E   | PIEP     | Read:<br>Write: | PIEP7 | PIEP6 | PIEP5 | PIEP4 | PIEP3 | PIEP2 | PIEP1 | PIEP0 |

| \$025F   | PIFP     | Read:<br>Write: | PIFP7 | PIFP6 | PIFP5 | PIFP4 | PIFP3 | PIFP2 | PIFP1 | PIFP0 |

| \$0260   | PTH      | Read:<br>Write: | PTH7  | PTH6  | PTH5  | PTH4  | PTH3  | PTH2  | PTH1  | PTH0  |

| \$0261   | PTIH     | Read:<br>Write: | PTIH7 | PTIH6 | PTIH5 | PTIH4 | PTIH3 | PTIH2 | PTIH1 | PTIH0 |

| \$0262   | DDRH     | Read:<br>Write: | DDRH7 | DDRH7 | DDRH5 | DDRH4 | DDRH3 | DDRH2 | DDRH1 | DDRH0 |

| \$0263   | RDRH     | Read:<br>Write: | RDRH7 | RDRH6 | RDRH5 | RDRH4 | RDRH3 | RDRH2 | RDRH1 | RDRH0 |

| \$0264   | PERH     | Read:<br>Write: | PERH7 | PERH6 | PERH5 | PERH4 | PERH3 | PERH2 | PERH1 | PERH0 |

| \$0265   | PPSH     | Read:<br>Write: | PPSH7 | PPSH6 | PPSH5 | PPSH4 | PPSH3 | PPSH2 | PPSH1 | PPSH0 |

| \$0266   | PIEH     | Read:<br>Write: | PIEH7 | PIEH6 | PIEH5 | PIEH4 | PIEH3 | PIEH2 | PIEH1 | PIEH0 |

| \$0267   | PIFH     | Read:<br>Write: | PIFH7 | PIFH6 | PIFH5 | PIFH4 | PIFH3 | PIFH2 | PIFH1 | PIFH0 |

| \$0268   | PTJ      | Read:<br>Write: | PTJ7  | PTJ6  | 0     | 0     | 0     | 0     | PTJ1  | PTJ0  |

| \$0269   | PTIJ     | Read:<br>Write: | PTIJ7 | PTIJ6 | 0     | 0     | 0     | 0     | PTIJ1 | PTIJ0 |

| \$026A   | DDRJ     | Read:<br>Write: | DDRJ7 | DDRJ7 | 0     | 0     | 0     | 0     | DDRJ1 | DDRJ0 |

| \$026B   | RDRJ     | Read:<br>Write: | RDRJ7 | RDRJ6 | 0     | 0     | 0     | 0     | RDRJ1 | RDRJ0 |

| \$026C   | PERJ     | Read:<br>Write: | PERJ7 | PERJ6 | 0     | 0     | 0     | 0     | PERJ1 | PERJ0 |

| \$026D   | PPSJ     | Read:<br>Write: | PPSJ7 | PPSJ6 | 0     | 0     | 0     | 0     | PPSJ1 | PPSJ0 |

| \$026E   | PIEJ     | Read:<br>Write: | PIEJ7 | PIEJ6 | 0     | 0     | 0     | 0     | PIEJ1 | PIEJ0 |

| \$026F   | PIFJ     | Read:<br>Write: | PIFJ7 | PIFJ6 | 0     | 0     | 0     | 0     | PIFJ1 | PIFJ0 |

| \$0270 - | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$027F   |          | Write:          |       |       |       |       |       |       |       |       |

Device User Guide — 9S12DT128DGV2/D V02.17

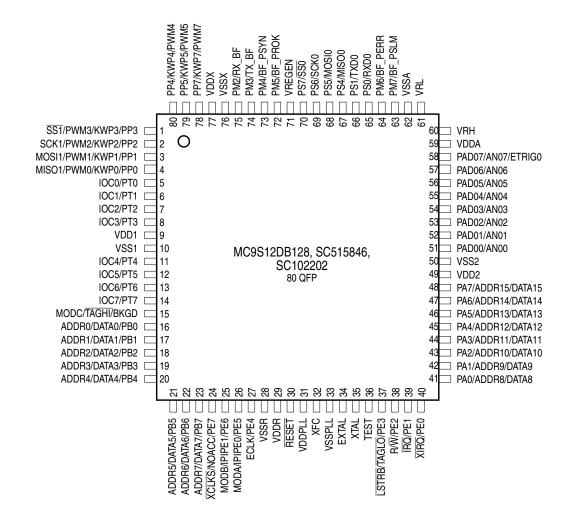

Figure 2-3 Pin Assignments in 80 QFP for MC9S12DB128, SC515846, and SC102202 Bondout

## 2.2 Signal Properties Summary

(Table 2-1) summarizes the pin functionality. Signals shown in Bold are not available on all the 80-pin package options. Signals shown in *Bold-Italics* are not available on the MC9S12DG128E, MC9S12DG128, MC9S12DJ128E, MC9S12DJ128, MC9S12A128, SC515847, SC515848, SC101161DG, SC101161DJ, SC102203, and SC102204 80-pin package options. Signals shown in *Italics* are not available on MC9S12DB128, SC515846, and SC102202 80-pin package options.

## 2.3.6 PAD[15] / AN1[7] / ETRIG1 — Port AD Input Pin [15]

PAD15 is a general purpose input pin and analog input of the analog to digital converter ATD1. It can act as an external trigger input for the ATD1.

## 2.3.7 PAD[14:8] / AN1[6:0] — Port AD Input Pins [14:8]

PAD14 - PAD8 are general purpose input pins and analog inputs of the analog to digital converter ATD1.

### 2.3.8 PAD[7] / AN0[7] / ETRIG0 — Port AD Input Pin [7]

PAD7 is a general purpose input pin and analog input of the analog to digital converter ATD0. It can act as an external trigger input for the ATD0.

## 2.3.9 PAD[6:0] / AN0[6:0] — Port AD Input Pins [6:0]

PAD6 - PAD8 are general purpose input pins and analog inputs of the analog to digital converter ATD0.

### 2.3.10 PA[7:0] / ADDR[15:8] / DATA[15:8] - Port A I/O Pins

PA7-PA0 are general purpose input or output pins. In MCU expanded modes of operation, these pins are used for the multiplexed external address and data bus.

### 2.3.11 PB[7:0] / ADDR[7:0] / DATA[7:0] - Port B I/O Pins

PB7-PB0 are general purpose input or output pins. In MCU expanded modes of operation, these pins are used for the multiplexed external address and data bus.

## 2.3.12 PE7 / NOACC / XCLKS - Port E I/O Pin 7

PE7 is a general purpose input or output pin. During MCU expanded modes of operation, the NOACC signal, when enabled, is used to indicate that the current bus cycle is an unused or "free" cycle. This signal will assert when the CPU is not using the bus.

The  $\overline{\text{XCLKS}}$  is an input signal which controls whether a crystal in combination with the internal Colpitts (low power) oscillator is used or whether Pierce oscillator/external clock circuitry is used. The state of this pin is latched at the rising edge of  $\overline{\text{RESET}}$ . If the input is a logic low the EXTAL pin is configured for an external clock drive. If input is a logic high an oscillator circuit is configured on EXTAL and XTAL. Since this pin is an input with a pull-up device during reset, if the pin is left floating, the default configuration is an oscillator circuit on EXTAL and XTAL.

# **Appendix A Electrical Characteristics**

## A.1 General

This introduction is intended to give an overview on several common topics like power supply, current injection etc.

### A.1.1 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate.

P:

Those parameters are guaranteed during production testing on each individual device.

C:

Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations. They are regularly verified by production monitors.

T:

Those parameters are achieved by design characterization on a small sample size from typical devices. All values shown in the typical column are within this category.

D:

Those parameters are derived mainly from simulations.

### A.1.2 Power Supply

The MC9S12DT128 utilizes several pins to supply power to the I/O ports, A/D converter, oscillator, PLL and internal logic.

The VDDA, VSSA pair supplies the A/D converter and the resistor ladder of the internal voltage regulator.

The VDDX, VSSX, VDDR and VSSR pairs supply the I/O pins, VDDR supplies also the internal voltage regulator.

VDD1, VSS1, VDD2 and VSS2 are the supply pins for the digital logic, VDDPLL, VSSPLL supply the oscillator and the PLL.

VSS1 and VSS2 are internally connected by metal.

VDDA, VDDX, VDDR as well as VSSA, VSSX, VSSR are connected by anti-parallel diodes for ESD protection.

### A.1.5 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside those maxima is not guaranteed. Stress beyond those limits may affect the reliability or cause permanent damage of the device.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either  $V_{SS5}$  or  $V_{DD5}$ ).

| Num | Rating                                                                                  | Symbol                           | Min   | Max  | Unit |

|-----|-----------------------------------------------------------------------------------------|----------------------------------|-------|------|------|

| 1   | I/O, Regulator and Analog Supply Voltage                                                | V <sub>DD5</sub>                 | -0.3  | 6.0  | V    |

| 2   | Digital Logic Supply Voltage <sup>2</sup>                                               | V <sub>DD</sub>                  | -0.3  | 3.0  | V    |

| 3   | PLL Supply Voltage (2)                                                                  | V <sub>DDPLL</sub>               | -0.3  | 3.0  | V    |

| 4   | Voltage difference VDDX to VDDR and VDDA                                                | $\Delta_{VDDX}$                  | -0.3  | 0.3  | V    |

| 5   | Voltage difference VSSX to VSSR and VSSA                                                | Δ <sub>VSSX</sub>                | -0.3  | 0.3  | V    |

| 6   | Digital I/O Input Voltage                                                               | V <sub>IN</sub>                  | -0.3  | 6.0  | V    |

| 7   | Analog Reference                                                                        | V <sub>RH,</sub> V <sub>RL</sub> | -0.3  | 6.0  | V    |

| 8   | XFC, EXTAL, XTAL inputs                                                                 | V <sub>ILV</sub>                 | -0.3  | 3.0  | V    |

| 9   | TEST input                                                                              | V <sub>TEST</sub>                | -0.3  | 10.0 | V    |

| 10  | Instantaneous Maximum Current<br>Single pin limit for all digital I/O pins <sup>3</sup> | I <sub>D</sub>                   | -25   | +25  | mA   |

| 11  | Instantaneous Maximum Current<br>Single pin limit for XFC, EXTAL, XTAL <sup>4</sup>     | I <sub>DL</sub>                  | -25   | +25  | mA   |

| 12  | Instantaneous Maximum Current<br>Single pin limit for TEST <sup>5</sup>                 | I <sub>DT</sub>                  | -0.25 | 0    | mA   |

| 13  | Storage Temperature Range                                                               | T <sub>stg</sub>                 | - 65  | 155  | °C   |

| Table A-1 Absolute Maximum Ratings | Table A-1 | Absolute | Maximum | Ratings <sup>1</sup> |

|------------------------------------|-----------|----------|---------|----------------------|

|------------------------------------|-----------|----------|---------|----------------------|

NOTES:

1. Beyond absolute maximum ratings device might be damaged.

2. The device contains an internal voltage regulator to generate the logic and PLL supply out of the I/O supply. The absolute maximum ratings apply when the device is powered from an external source.

3. All digital I/O pins are internally clamped to  $V_{SSX}$  and  $V_{DDX}$ ,  $V_{SSR}$  and  $V_{DDR}$  or  $V_{SSA}$  and  $V_{DDA}$ . 4. Those pins are internally clamped to  $V_{SSPLL}$  and  $V_{DDPLL}$ . 5. This pin is clamped low to  $V_{SSX}$ , but not clamped high. This pin must be tied low in applications.

### A.1.6 ESD Protection and Latch-up Immunity

All ESD testing is in conformity with CDF-AEC-Q100 Stress test qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model.

Device User Guide — 9S12DT128DGV2/D V02.17

$P_{D}$  = Total Chip Power Dissipation, [W]

$\Theta_{IA}$  = Package Thermal Resistance, [°C/W]

The total power dissipation can be calculated from:

$$P_D = P_{INT} + P_{IO}$$

P<sub>INT</sub> = Chip Internal Power Dissipation, [W]

Two cases with internal voltage regulator enabled and disabled must be considered:

1. Internal Voltage Regulator disabled

$$P_{INT} = I_{DD} \cdot V_{DD} + I_{DDPLL} \cdot V_{DDPLL} + I_{DDA} \cdot V_{DDA}$$

$$P_{IO} = \sum_{i} R_{DSON} \cdot I_{IO}^{2}_{i}$$

Which is the sum of all output currents on I/O ports associated with VDDX and VDDR.

For R<sub>DSON</sub> is valid:

$$R_{DSON} = \frac{V_{OL}}{I_{OL}}$$

; for outputs driven low

respectively

$$R_{DSON} = \frac{V_{DD5} - V_{OH}}{I_{OH}}$$

; for outputs driven high

2. Internal voltage regulator enabled

$$P_{INT} = I_{DDR} \cdot V_{DDR} + I_{DDA} \cdot V_{DDA}$$

$I_{DDR}$  is the current shown in **(Table A-7)** and not the overall current flowing into VDDR, which additionally contains the current flowing into the external loads with output high.

$$P_{IO} = \sum_{i} R_{DSON} \cdot I_{IO_{i}}^{2}$$

Which is the sum of all output currents on I/O ports associated with VDDX and VDDR.

$$t_{era} \approx 4000 \cdot \frac{1}{f_{NVMOP}}$$

The setup time can be ignored for this operation.

#### A.3.1.4 Mass Erase

Erasing a NVM block takes:

$$t_{mass} \approx 20000 \cdot \frac{1}{f_{NVMOP}}$$

The setup time can be ignored for this operation.

### A.3.1.5 Blank Check

The time it takes to perform a blank check on the Flash or EEPROM is dependent on the location of the first non-blank word starting at relative address zero. It takes one bus cycle per word to verify plus a setup of the command.

$$t_{check} \approx location \cdot t_{cyc} + 10 \cdot t_{cyc}$$

| Condit | ions | s are shown in (Table A-4) unless otherwise noted   |                     |                      |     |                       |                  |

|--------|------|-----------------------------------------------------|---------------------|----------------------|-----|-----------------------|------------------|

| Num    | С    | Rating                                              | Symbol              | Min                  | Тур | Max                   | Unit             |

| 1      | D    | External Oscillator Clock                           | f <sub>NVMOSC</sub> | 0.5                  |     | 50 <sup>1</sup>       | MHz              |

| 2      | D    | Bus frequency for Programming or Erase Operations   | f <sub>NVMBUS</sub> | 1                    |     |                       | MHz              |

| 3      | D    | Operating Frequency                                 | f <sub>NVMOP</sub>  | 150                  |     | 200                   | kHz              |

| 4      | Ρ    | Single Word Programming Time                        | t <sub>swpgm</sub>  | 46 <sup>2</sup>      |     | 74.5 <sup>3</sup>     | μs               |

| 5      | D    | Flash Row Programming consecutive word <sup>4</sup> | t <sub>bwpgm</sub>  | 20.4 <sup>(2)</sup>  |     | 31 <sup>(3)</sup>     | μs               |

| 6      | D    | Flash Row Programming Time for 32 Words $^{(4)}$    | t <sub>brpgm</sub>  | 678.4 <sup>(2)</sup> |     | 1035.5 <sup>(3)</sup> | μs               |

| 7      | Ρ    | Sector Erase Time                                   | t <sub>era</sub>    | 20 <sup>5</sup>      |     | 26.7 <sup>(3)</sup>   | ms               |

| 8      | Ρ    | Mass Erase Time                                     | t <sub>mass</sub>   | 100 <sup>(5)</sup>   |     | 133 <sup>(3)</sup>    | ms               |

| 9      | D    | Blank Check Time Flash per block                    | t <sub>check</sub>  | 11 <sup>6</sup>      |     | 32778 <sup>7</sup>    | t <sub>cyc</sub> |

| 10     | D    | Blank Check Time EEPROM per block                   | t <sub>check</sub>  | 11 <sup>(6)</sup>    |     | 1034 <sup>(7)</sup>   | t <sub>cyc</sub> |

#### Table A-11 NVM Timing Characteristics

NOTES:

1. Restrictions for oscillator in crystal mode apply!

2. Minimum Programming times are achieved under maximum NVM operating frequency f<sub>NVMOP</sub> and maximum bus frequency f<sub>bus</sub>.

3. Maximum Erase and Programming times are achieved under particular combinations of f<sub>NVMOP</sub> and bus frequency f<sub>bus</sub>. Refer to formulae in Sections Section A.3.1.1 Single Word Programming- Section A.3.1.4 Mass Erasefor guidance.

4. Row Programming operations are not applicable to EEPROM

5. Minimum Erase times are achieved under maximum NVM operating frequency f<sub>NVMOP</sub>.

6. Minimum time, if first word in the array is not blank

7. Maximum time to complete check on an erased block

| Condit | tions | s are shown in (Table A-4) unless otherwise noted                                                                        |                    |         |                      |     |         |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------|--------------------|---------|----------------------|-----|---------|

| Num    | С     | Rating                                                                                                                   | Symbol             | Min     | Тур                  | Max | Unit    |

|        |       | Flash Reliability Cha                                                                                                    | racteristics       |         |                      |     | •       |

| 1      | с     | Data retention after 10,000 program/erase cycles at an average junction temperature of $T_{Javg} \le 85^{\circ}C$        | teloer             | 15      | 100 <sup>2</sup>     | _   | Years   |

| 2      | с     | Data retention with <100 program/erase cycles at an average junction temperature $T_{Javg} \le 85^{\circ}C$              | t <sub>FLRET</sub> | 20      | 100 <sup>2</sup>     | —   | Tears   |

| 3      | с     | Number of program/erase cycles $(-40^{\circ}C \le T_{J} \le 0^{\circ}C)$                                                 | n                  | 10,000  | _                    | —   | Civelaa |

| 4      | с     | Number of program/erase cycles<br>( $0^{\circ}C \leq T_{J} \leq 140^{\circ}C$ )                                          | n <sub>FL</sub>    | 10,000  | 100,000 <sup>3</sup> | _   | Cycles  |

|        |       | EEPROM Reliability Ch                                                                                                    | aracteristic       | S       |                      |     | •       |

| 5      | с     | Data retention after up to 100,000 program/erase cycles at an average junction temperature of $T_{Javg} \le 85^{\circ}C$ | teroper            | 15      | 100 <sup>2</sup>     | _   | Years   |

| 6      | с     | Data retention with <100 program/erase cycles at an average junction temperature $T_{Javg} \le 85^{\circ}C$              | teepret            | 20      | 100 <sup>2</sup>     | _   | Tears   |

| 7      | с     | Number of program/erase cycles<br>(-40°C $\leq$ T <sub>J</sub> $\leq$ 0°C)                                               | n                  | 10,000  |                      |     | Cycles  |

| 8      | с     | Number of program/erase cycles<br>( $0^{\circ}C < T_{J} \le 140^{\circ}C$ )                                              | N <sub>EEP</sub>   | 100,000 | 300,000 <sup>3</sup> |     | Cycles  |

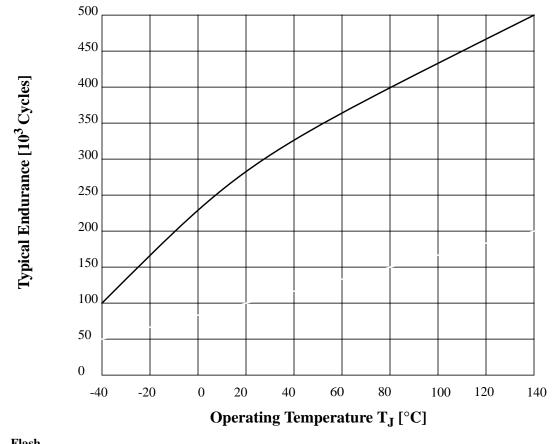

#### Table A-12 NVM Reliability Characteristics<sup>1</sup>

NOTES:

1. T<sub>Javg</sub> will not exeed 85°C considering a typical temperature profile over the lifetime of a consumer, industrial or automotive application.

Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines Typical Data Retention, please refer to Engineering Bulletin EB618.

3. Spec table quotes typical endurance evaluated at 25°C for this product family, typical endurance at various temperature can be estimated using the graph below. For additional information on how Freescale defines Typical Endurance, please refer to Engineering Bulletin EB619.

Figure A-2 Typical Endurance vs Temperature

Flash ----- EEPROM

## A.4 Voltage Regulator

The on-chip voltage regulator is intended to supply the internal logic and oscillator circuits. No external DC load is allowed.

### Table A-13 Voltage Regulator Recommended Load Capacitances

| Rating                      | Symbol                 | Min | Тур | Мах | Unit |

|-----------------------------|------------------------|-----|-----|-----|------|

| Load Capacitance on VDD1, 2 | C <sub>LVDD</sub>      |     | 220 |     | nF   |

| Load Capacitance on VDDPLL  | C <sub>LVDDfcPLL</sub> |     | 220 |     | nF   |

### A.5.1.5 Pseudo Stop and Wait Recovery

The recovery from Pseudo STOP and Wait are essentially the same since the oscillator was not stopped in both modes. The controller can be woken up by internal or external interrupts. After  $t_{wrs}$  the CPU starts fetching the interrupt vector.

### A.5.2 Oscillator

The device features an internal Colpitts and Pierce oscillator. The selection of Colpitts oscillator or Pierce oscillator/external clock depends on the XCLKS signal which is sampled during reset. By asserting the  $\overline{\text{XCLKS}}$  input during reset this oscillator can be bypassed allowing the input of a square wave. Before asserting the oscillator to the internal system clocks the quality of the oscillation is checked for each start from either power-on, STOP or oscillator fail. t<sub>CQOUT</sub> specifies the maximum time before switching to the internal self clock mode after POR or STOP if a proper oscillation is not detected. The quality check also determines the minimum oscillator start-up time t<sub>UPOSC</sub>. The device also features a clock monitor. A

And finally the frequency relationship is defined as

$$n = \frac{f_{VCO}}{f_{ref}} = 2 \cdot (synr + 1) = 50$$

With the above values the resistance can be calculated. The example is shown for a loop bandwidth  $f_{C}=10$ KHz:

$$R = \frac{2 \cdot \pi \cdot n \cdot f_{C}}{K_{\Phi}} = 2^{*} \pi^{*} 50^{*} 10 \text{kHz} / (316.7 \text{Hz}/\Omega) = 9.9 \text{k}\Omega = -10 \text{k}\Omega$$

The capacitance C<sub>s</sub> can now be calculated as:

$$C_s = \frac{2 \cdot \zeta^2}{\pi \cdot f_C \cdot R} \approx \frac{0.516}{f_C \cdot R}; (\zeta = 0.9) = 5.19 \text{nF} = -4.7 \text{nF}$$

The capacitance C<sub>p</sub> should be chosen in the range of:

$$C_{s}/20 \le C_{p} \le C_{s}/10$$

$C_{p} = 470 pF$

#### A.5.3.2 Jitter Information

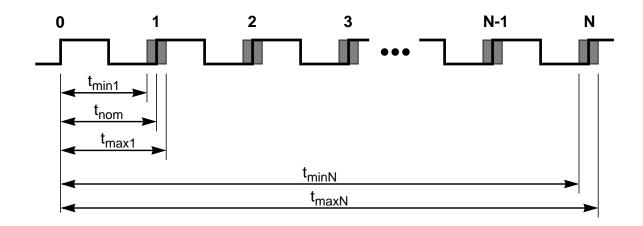

The basic functionality of the PLL is shown in **Figure A-3**. With each transition of the clock  $f_{cmp}$ , the deviation from the reference clock  $f_{ref}$  is measured and input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the clock output frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in **Figure A-4**.

**Figure A-4 Jitter Definitions**

The relative deviation of  $t_{nom}$  is at its maximum for one clock period, and decreases towards zero for larger number of clock periods (N).

Defining the jitter as:

$$J(N) = max\left(\left|1 - \frac{t_{max}(N)}{N \cdot t_{nom}}\right|, \left|1 - \frac{t_{min}(N)}{N \cdot t_{nom}}\right|\right)$$

For N < 100, the following equation is a good fit for the maximum jitter:

$$J(N) = \frac{j_1}{\sqrt{N}} + j_2$$

# **User Guide End Sheet**