Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

# **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                      |

|---------------------------------|----------------------------------------------------------------------|

| Product Status                  | Obsolete                                                             |

| Core Processor                  | PowerPC e500mc                                                       |

| Number of Cores/Bus Width       | 4 Core, 32-Bit                                                       |

| Speed                           | 1.5GHz                                                               |

| Co-Processors/DSP               | Security; SEC 4.2                                                    |

| RAM Controllers                 | DDR3, DDR3L                                                          |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10/100/1000Mbps (5), 10Gbps (1)                                      |

| SATA                            | SATA 3Gbps (2)                                                       |

| USB                             | USB 2.0 + PHY (2)                                                    |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V, 3.3V                                               |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                     |

| Security Features               | Boot Security, Cryptography, Random Number Generator, Secure Fusebox |

| Package / Case                  | 1295-BBGA, FCBGA                                                     |

| Supplier Device Package         | 1295-FCPBGA (37.5x37.5)                                              |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=p3041nse1pnb            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**QorlQ Communications Platform**

# P3 Series

# P3041 optimized quad-core processor

#### Overview

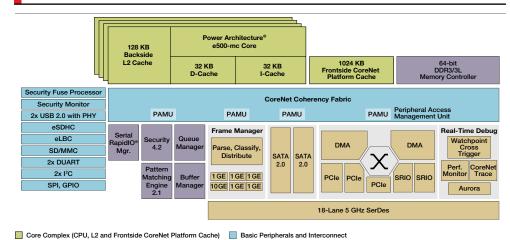

The QorlQ P3041 processor is an optimized, quad-core device that leverages architectural features pioneered in the P4 platform. Built on Power Architecture® technology, the P3041 fits into many of the same applications as the P4 platform processors, yet is designed to offer a more power- and cost-efficient solution.

The P3041 includes P4 platform features such as the three-level cache hierarchy for low latencies, hardware hypervisor for robust virtualization support, data path acceleration architecture (DPAA) for offloading packet handling tasks from the core and the CoreNet switch fabric which eliminates internal bottlenecks. This enables architectural compatibility across multiple products that all

Accelerators and Memory Control Networking Elements

use the same architecture, including the P2040, P2041, P4040, P4080, P5010 and P5020.

The P3041 processor uses the same 37.5 mm x 37.5 mm 1295-pin package as the P4 and P5 processors, resulting in pin compatibility across a broad range of performance levels. Between the architectural similarity and the pin-compatible package, developers can leverage the same software and printed circuit board (PCB) across many applications with a variety of requirements:

- Low-power, mid-range mixed control and data plane (P3 platform)

- High-performance data path performance (P4 platform)

- High-performance control plane application (P5 platform)

# QorIQ P3041 Communications Processor

### **Key Architectural Features**

- Three-level cache hierarchy: The low-latency 32 KB L1 instruction and data caches are augmented by a unified 128 KB private backside L2 cache per core. The L2 is 8-way set associative and is ECC protected. When instructions are locked in the L2, the per-packet "hot" code is always readily available, improving application performance. A shared 1 MB CoreNet platform cache (L3) facilitates core-to-core communications and minimizes accesses to main memory.

- Hardware hypervisor: The e500mc supports a hardware hypervisor that is designed to enable each core to run its own operating system completely independent of the other core. The hypervisor facilitates resource sharing and partitioning in a multicore environment, and provides protection in the event that a core, driven by malicious or improperly programmed code, tries to access memory it does not have permission to read or write. It also allows the sharing and partitioning of various I/Os across the cores and it helps ensure that incoming memory mapped transactions are written only into appropriate ranges of the memory map.

- DPAA: This offloads the cores from the need to perform routine packet-handling tasks. For instance, the DPAA will extract headers from incoming packets, police them, classify them and manage their data buffers. The work is assigned to cores with a three-level scheduling hierarchy, which can also facilitate sharing of packet workload over multiple cores.

- CoreNet switch fabric: The fabric-based interface provides scalable on-chip, pointto-point connectivity supporting concurrent traffic to and from multiple resources connected to the fabric, eliminating singlepoint bottlenecks for non-competing resources. This is designed to eliminate bus contention and latency issues associated with scaling shared bus architectures that are common in other multicore approaches.

# **Target Applications**

The P3 family is targeted at mixed control plane and data plane applications, where in previous generations separate devices would implement each function. Typically, one or two cores would implement the control plane, while the remaining cores implement the data plane. The hardware hypervisor facilitates this, with its capability to safely provision flexible core allocations into groups running SMP, one core running alone, separate cores running in parallel or a core running end-user applications. There are many applications that look similar to this, including:

- Integrated access router (IAD): Dual SATA ports provide high-speed, cost-effective storage options for statistics or large databases. Compared to SGMII, 2.5 Gbps Ethernet enables the next step in performance connectivity to switches.

- Base station network interface card (NIC):

Dual Serial RapidIO® ports (up to 5 GHz)

can be used for redundancy or multiple

connections, both to the backplane or

to the DSP farm. With improved Type 11

messaging and new support for Type 9 data

streaming, the Serial RapidIO interconnect

can now be used not only as a control plane

interface, but can also achieve its intended

potential as a highly efficient data path.

#### **Features**

# Four e500mc cores, built on Power Architecture technology

- Up to 1.5 GHz

- Each with 128 KB backside L2 cache

#### Memory controller

- DDR3, 3L up to 1.3 GHz

- 32/64-bit data bus with ECC

#### High-speed interconnects

- 18x 5 GHz SerDes lanes

- 4x PCI Express<sup>®</sup> 2.0 controllers at up to 5 GHz

- 2x Serial RapidIO 1.3/2.1 controllers at up to 5 GHz

- 2x SATA 2.0 at 3 Gbps

- 2x USB 2.0 with PHY

#### CoreNet switch fabric

1 MB shared CoreNet platform cache (L3) with ECC

#### **Ethernet**

- 5x 10/100/1000 Ethernet controller

- 1x 10 Gigabit Ethernet controllers

- All with classification, hardware queueing, policing, buffer management, checksum offload, QoS, lossless flow control, IEEE® 1588

- Up to 1x XAUI, 4x SGMII or 2.5 Gbps SGMII, 2x RGMII

#### Data path acceleration

- SEC 4.2: public key accelerator, DES, AES, message digest accelerator, random number generator, ARC4, SNOW 3G F8 and F9, CRC, Kasumi

- PME 2.1: searches for 128 byte text strings in 32 KB patterns in 128M sessions

- RapidIO messaging: Type 9 and 11

#### **Device**

- 45 nm SOI process technology

- 1295-pin FCPBGA package, 37.5 mm x 37.5 mm

#### Enablement

- Enea®: Real-time operating system support

- Green Hills®: Complete portfolio of software and hardware development tools, trace tools and real-time operating systems

- Mentor Graphics<sup>®</sup>: Commercial grade Linux<sup>®</sup> solution

- CodeSourcery: Tool chain support for new core technology

- WindRiver®: Simics® model

- Development system: Four PCI Express slots, one Serial RapidIO slot, one XAUI slot, one SGMII slot, SATA disk, Aurora debug port

# To learn more about Freescale QorlQ communications platforms, please visit freescale.com/QorlQ

Freescale, the Freescale logo and QorlQ are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. CoreNet is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2011 Freescale Semiconductor, Inc.

Document Number: QP3041FS REV 3