Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | -                                                            |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 12MHz                                                        |

| Connectivity               | SIO, UART/USART                                              |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 18                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                  |

| Data Converters            | A/D 7x12b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 24-LFSOP (0.173", 4.40mm Width)                              |

| Supplier Device Package    | 24-SSOP                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/onsemi/lc87f0g08auja-zh |

|                            |                                                              |

## **Function Details**

### ■Flash ROM

- Capable of on-board programming with a wide range of supply voltages: 2.2 to 5.5V

- Block-erasable in 128 byte units

- Writes data in 2-byte units

- 8192 × 8 bits

#### **■**RAM

• 256 × 9 bits

#### ■Bus Cycle Time

- 83.3ns (12MHz, V<sub>DD</sub>=2.7V to 5.5V, Ta=-40°C to 85°C)

- 125ns (8MHz, VDD=2.0V to 5.5V, Ta=-40°C to 85°C)

- 250ns (4MHz, V<sub>DD</sub>=1.8V to 5.5V, Ta=-40°C to 85°C)

Note: The bus cycle time here refers to the ROM read speed.

## ■Minimum Instruction Cycle Time (tCYC)

- 250ns (12MHz, V<sub>DD</sub>=2.7V to 5.5V, Ta=-40°C to 85°C)

- 375ns (8MHz, VDD=2.0V to 5.5V, Ta=-40°C to 85°C)

- 750ns (4MHz, V<sub>DD</sub>=1,8V to 5.5V, Ta=-40°C to 85°C)

#### **■**Potrs

• Normal withstand voltage I/O ports whose I/O direction can be designated in 1-bit units

18(P0n, P1n, P70, CF1, CF2)

• Reset pins 1(RES)

• Power supply pins 3(VSS1, VSS2, VDD1)

• Reference voltage outputs 1(VREF)

• Dedicated debugger port 1(OWP0)

#### ■Timers

• Timer 0 : 16-bit timer/counter with 2 capture registers.

Mode 0 : 8-bit timer with an 8-bit programmable prescaler (with two 8-bit capture registers) × 2 channels

Mode 1: 8-bit timer with an 8-bit programmable prescaler (with two 8-bit capture registers)

+ 8-bit counter (with two 8-bit capture registers)

Mode 2:16-bit timer with an 8-bit programmable prescaler (with two 16-bit capture registers)

Mode 3: 16-bit counter (with two 16-bit capture registers)

• Timer 1: 16-bit timer/counter that supports PWM/toggle outputs

Mode 0: 8-bit timer with an 8-bit prescaler (with toggle outputs) + 8-bit timer/

counter with an 8-bit prescaler (with toggle outputs)

Mode 1: 8-bit PWM with an 8-bit prescaler × 2 channels

Mode 2: 16-bit timer/counter with an 8-bit prescaler (with toggle outputs)

(toggle outputs also possible from lower-order 8 bits)

Mode 3: 16-bit timer with an 8-bit prescaler (with toggle outputs)

(lower-order 8 bits may be used as a PWM output)

#### • Base timer

- (1) The clock is selectable from the subclock (32.768kHz crystal oscillation), the low speed RC, system clock, and timer 0 prescaler output.

- (2) with an 8-bit programmable prescaler

- (3) Interrupts programmable in 5 different time schemes

#### **■**SIO

• SIO1 : 8-bit asynchronous/synchronous serial interface

Mode 0 : Synchronous 8-bit serial I/O (2- or 3-wire configuration, 2 to 512 tCYC transfer clocks)

Mode 1: Asynchronous serial I/O (half-duplex, 8 data bits, 1 stop bit, 8 to 2048 tCYC baudrates)

Mode 2: Bus mode 1 (start bit, 8 data bits, 2 to 512 tCYC transfer clocks)

Mode 3: Bus mode 2 (start detect, 8 data bits, stop detect)

#### ■AD Converter:

- AD converter input port with  $10 \times /20 \times$  amplifier (1channel)

- AD converter input port (7channel)

12-/8-bit resolution selectable AD converter

• Selectable reference voltage source for an AD converter (Selectable from VDD, Internal Reference Voltage Generator Circuit(VREF).)

#### ■Internal Reference Voltage Generator Circuit(VREF)

• Generates 2.0V/4.0V for AD converter.

## **■**Comparator

Comparator input pin (1 channel)

Comparator output pin (1 channel)

Comparator output set high when (comparator input level) < 1.22V

Comparator output set low when (comparator input level) > 1.22V

### ■Clock Output Function

• Generates clocks with a clock rate of 1/1, 1/2, 1/4, 1/8, 1/16, 1/32, or 1/64 of the source oscillation clock that is selected as the system clock.

### ■Watchdog Timer

- Generates an internal reset on an overflow occurring in the timer running on the low-speed RC oscillator clock (approx. 30kHz) or subclock.

- Operating mode at standby is selectable from 3 modes (continue counting/suspend operation/suspend counting with the count value retained)

#### ■Interrupts

- 15 sources, 10 vectors

- 1) Provides three levels (low (L), high (H), and highest (X)) of multiplex interrupt control. Any interrupt requests of the level equal to or lower than the current interrupt are not accepted.

- 2) When interrupt requests to two or more vector addresses occur at the same time, the interrupt of the highest level takes precedence over the other interrupts. For interrupts of the same level, the interrupt into the smallest vector address is given priority.

| No. | Vector Address | Level  | Interrupt Source |

|-----|----------------|--------|------------------|

| 1   | 00003H         | X or L | INT0             |

| 2   | 0000BH         | X or L | INT1             |

| 3   | 00013H         | H or L | INT2/T0L/INT4    |

| 4   | 0001BH         | H or L | INT3/BT          |

| 5   | 00023H         | H or L | ТОН              |

| 6   | 0002BH         | H or L | T1L/T1H          |

| 7   | 00033H         | H or L | HPWM2            |

| 8   | 0003BH         | H or L | SIO1             |

| 9   | 00043H         | H or L | ADC              |

| 10  | 0004BH         | H or L | P0/VCPWM         |

- Priority levels X > H > L

- Of interrupts of the same level, the one with the smallest vector address takes precedence.

- ■Subroutine Stack Levels: Up to 128levels (the stack is allocated in RAM.)

- ■High-speed Multiplication/Division Instructions

16 bits × 8 bits

24 bits × 16 bits

16 bits ÷ 8 bits

24 bits ÷ 16 bits

24 bits ÷ 16 bits

16 bits ÷ 8 bits

25 tCYC execution time

26 tCYC execution time

27 tCYC execution time

28 tCYC execution time

29 tcYC execution time

21 tcYC execution time

### ■Oscillation Circuits

• Internal oscillation circuits

Low-speed RC oscillation circuit:

Medium-speed RC oscillation circuit:

For system clock (approx.30kHz)

Hi-speed RC oscillation circuit1:

Hi-speed RC oscillation circuit2:

For system clock (8MHz)

For High speed PWM (40MHz)

## ■System Clock Divider Function

- Can run on low consumption current.

- Minimum instruction cycle selectable from 375ns, 750ns, 1.5μs, 3.0μs, 6.0μs, 12.0μs, 24.0μs, 48.0μs, and 96.0μs (at 8MHz main clock)

#### ■Internal Reset Circuit

- Power-on reset (POR) function

- 1) POR reset is generated only at power-on time.

- 2) The POR release level is 1.67V.

- Low-voltage detection reset (LVD) function

- 1) LVD and POR functions are combined to generate resets when power is turned on and when power voltage falls below a certain level.

- 2) The use/disuse of the LVD function and the low voltage threshold level can be selected from 7 levels (1.91V, 2.01V, 2.31V, 2.51V, 2.81V, 3.79V and 4.28V), through option configuration.

#### ■Standby Function

- HALT mode: Halts instruction execution while allowing the peripheral circuits to continue operation.

- 1) Oscillation is not halted automatically.

- 2) There are three ways of resetting the HALT mode.

- (1) Setting the reset pin to the low level

- (2) Having the watchdog timer or LVD function generate a reset

- (3) Having an interrupt generated

- HOLD mode: Suspends instruction execution and the operation of the peripheral circuits.

- 1) The CF, RC and crystal oscillators automatically stop operation.

Note: The low-speed RC oscillator is controlled directly by the watchdog timer; its oscillation in the standby mode is also controlled by the watchdog timer.

- 2) There are four ways of resetting the HOLD mode:

- (1) Setting the reset pin to the lower level

- (2) Having the watchdog timer or LVD function generate a reset

- (3) Having an interrupt source established at one of the INT0, INT1, INT2 and INT4 pins

- \* INTO and INT1 can be used in the level sense mode only.

- (4) Having an interrupt source established at port 0.

- X'tal HOLD mode: Suspends instruction execution and the operation of the peripheral circuits except the base timer. (when X'tal oscillation or low-speed RC oscillation is selected).

- 1) The CF, low-speed, and medium-speed RC oscillators automatically stop operation.

Note: The low-speed RC oscillator is controlled directly by the watchdog timer; its oscillation in the standby mode is also controlled by the watchdog timer.

Note: If the base timer is run with low-speed RC oscillation selected as the base timer input clock source and the X'tal HOLD mode is entered, the low-speed RC oscillator retains the state that is established when the X'tal HOLD mode is entered.

- 2) The state of crystal oscillation established when the X'tal HOLD mode is entered is retained.

- 3) There are five ways of resetting the X'tal HOLD mode.

- (1) Setting the reset pin to the low level

- (2) Having the watchdog timer or LVD function generate a reset

- (3) Having an interrupt source established at one of the INT0, INT1, INT2, and INT4 pins \* INT0 and INT1 can be used in the level sense mode only.

- (4) Having an interrupt source established at port 0

- (5) Having an interrupt source established in the base timer circuit

- ■VCPWM: Frequency tunable 12-bit PWM × 2ch

- ■High speed PWM (HPWM2)

8-/10- bits PWM ×1ch

- 1) The PWM clock is selectable from system clock and Hi-speed RC2 (40MHz)

- 2) The PWM type is selectable from 8 bits(Normal mode) and 10 bits( additive puls mode).

#### ■Temperature sensor

• Senseor voltage can be comapred by the AD converter.

## ■On-chip Debugger Function

- Supports software debugging with the IC mounted on the target board.

- Provides 1 channel of on-chip debugger pin. OWP0

#### ■Data Security Function

• Protects the program data stored in flash memory from unauthorized read or copy. Note: This data security function does not necessarily provide absolute data security.

### ■Package Form

• SSOP24 (225mil): Lead-free and halogen-free type

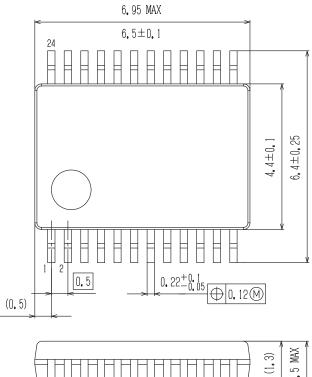

## **Package Dimensions**

unit: mm

## SSOP24 (225mil)

CASE 565AR ISSUE A

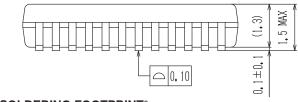

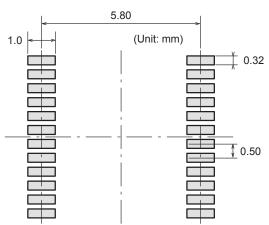

#### **SOLDERING FOOTPRINT\***

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code Y = Year

M = Month

DDD = Additional Traceability Data

\*This information is generic. Please refer to device data sheet for actual part marking. Pb−Free indicator, "G" or microdot " ■", may or may not be present.

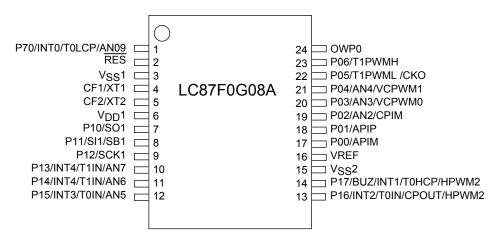

## **Pin Assignment**

SSOP24(225mil) "Lead-/Halogen-free Type"

| SSOP24 | NAME                |

|--------|---------------------|

| 1      | P70/INT0/T0LCP/AN09 |

| 2      | RES                 |

| 3      | V <sub>SS</sub> 1   |

| 4      | CF1/XT1             |

| 5      | CF2/XT2             |

| 6      | V <sub>DD</sub> 1   |

| 7      | P10/SO1             |

| 8      | P11/SI1/SB1         |

| 9      | P12/SCK1            |

| 10     | P13/INT4/T1IN/AN7   |

| 11     | P14/INT4/T1IN/AN6   |

| 12     | P15/INT3/T0IN/AN5   |

| SSOP24 | NAME                      |

|--------|---------------------------|

| 13     | P16/INT2/T0IN/CPOUT/HPWM2 |

| 14     | P17/BUZ/INT1/T0HCP/HPWM2  |

| 15     | V <sub>SS</sub> 2         |

| 16     | VREF                      |

| 17     | P00/APIM                  |

| 18     | P01/APIP                  |

| 19     | P02/AN2/CPIM              |

| 20     | P03/AN3/VCPWM0            |

| 21     | P04/AN4/VCPWM1            |

| 22     | P05/T1PWML/CKO            |

| 23     | P06/T1PWMH                |

| 24     | OWP0                      |

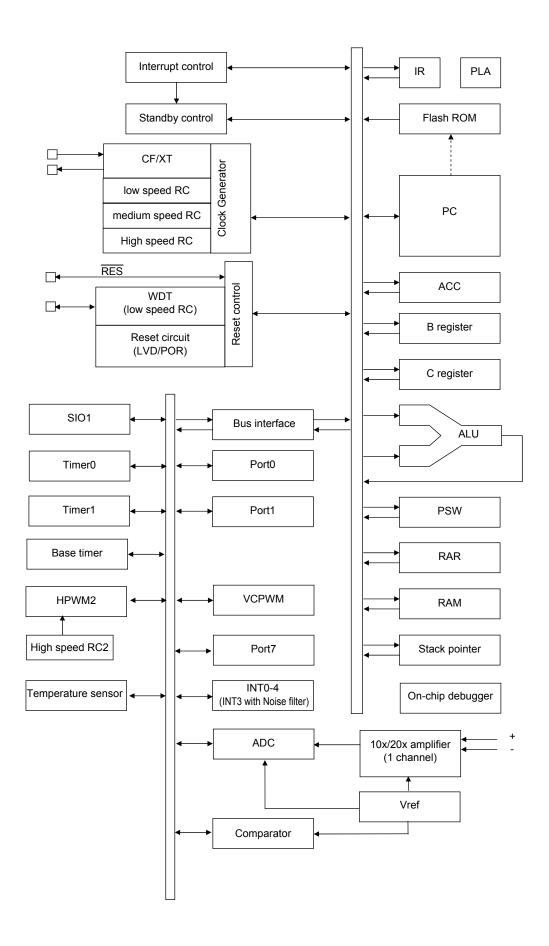

## **System Block Diagram**

Continued from preceding page.

| Pin Name      | I/O |                                  | Description                |                    |                          |                    |                 |                            |  |

|---------------|-----|----------------------------------|----------------------------|--------------------|--------------------------|--------------------|-----------------|----------------------------|--|

| Port 7<br>P70 | I/O | Pin functi                       | fiable<br>esistors can be  | turned on and of   | f.<br>er 0L capture inpu | ıt/AD converter iı | nput port (AN9) | No                         |  |

|               |     | Interrupt ac                     | cknowledge typ             | e                  |                          |                    |                 |                            |  |

|               |     |                                  | Rising                     | Falling            | Rising &<br>Falling      | H level            | L level         |                            |  |

|               |     | INT0                             | enable                     | enable             | disable                  | enable             | enable          |                            |  |

| RES           | I   | External re                      | eset input/interna         | al reset output pi | n                        |                    |                 | Yes Internal pullup ON/OFF |  |

| CF1/XT1       | I/O | Pin functi 1-bit I/O p I/O speci | ions<br>port               | 8kHz crystal osc   | illator input pin        |                    |                 | No                         |  |

| CF2/XT2       | I/O | 1                                | oscillator/32.76 ions port | 8kHz crystal osc   | illator output pin       |                    |                 | No                         |  |

| OWP0          | I/O | On-chip de                       |                            |                    |                          |                    |                 | No                         |  |

## Absolute Maximum Ratings at Ta = 25°C, $V_{SS}1 = V_{SS}2 = 0V$

|                           | Davasastas                        | O: week al          | Dia /Danasala                    | Constitution of                                                   |                     |      | Specifi | cation               |      |

|---------------------------|-----------------------------------|---------------------|----------------------------------|-------------------------------------------------------------------|---------------------|------|---------|----------------------|------|

|                           | Parameter                         | Symbol              | Pin/Remarks                      | Conditions                                                        | V <sub>DD</sub> [V] | min  | typ     | max                  | unit |

|                           | iximum supply<br>tage             | V <sub>DD</sub> MAX | V <sub>DD</sub> 1                |                                                                   |                     | -0.3 | to      | +6.5                 |      |

| Inp                       | out/output voltage                | VIO                 | Port0,1<br>Port7<br>CF1,CF2, RES |                                                                   |                     | -0.3 | to      | V <sub>DD</sub> +0.3 | V    |

| t current                 | Peak output current               | IOPH(1)             | Port0<br>Port1<br>CF2            | When CMOS output type is selected Per 1 applicable pin            |                     | -10  |         |                      |      |

| High level output current | Average output current (Note 1-1) | IOMH(1)             | Port0<br>Port1<br>CF2            | When CMOS output<br>type is selected     Per 1 applicable pin     |                     | -7.5 |         |                      |      |

| High                      | Total output current              | ΣΙΟΑΗ(1)            | Port0,1,<br>CF2                  | Total current of all applicable pins                              |                     | -30  |         |                      |      |

|                           | Peak output                       | IOPL(1)             | Port0                            | Per 1 applicable pin                                              |                     |      |         | 20                   | mA   |

| rent                      | current                           | IOPL(2)             | Port1                            | Per 1 applicable pin                                              |                     |      |         | 20                   |      |

| Low level output current  |                                   | IOPL(3)             | Port7,CF1,CF2                    | Per 1 applicable pin                                              |                     |      |         | 10                   |      |

| utbui                     | Average                           | IOML(1)             | Port0                            | Per 1 applicable pin                                              |                     |      |         | 15                   |      |

| e o                       | output current                    | IOML(2)             | Port1                            | Per 1 applicable pin                                              |                     |      |         | 15                   |      |

| v lev                     | (Note 1-1)                        | IOML(3)             | Port7,CF1,CF2                    | Per 1 applicable pin                                              |                     |      |         | 7.5                  |      |

| Lov                       | Total output current              | ΣIOAL(1)            | Port0,1,7,<br>CF1,CF2            | Total current of all applicable pins                              |                     |      |         | 80                   |      |

|                           | owable power<br>esipation         | Pdmax(1)            | SSOP24(225mil)                   | Ta=-40 to + 85°C Package with thermal resistance board (Note 1-2) |                     |      |         | 260                  | mW   |

|                           | erating ambient                   | ambient Topr        |                                  | -40                                                               |                     | +85  | 20      |                      |      |

| Sto                       | orage ambient<br>nperature        | Tstg                |                                  |                                                                   |                     | -55  |         | +125                 | °C   |

Note 1-1: The average output current is an average of current values measured over 100ms intervals.

Note 1-2: SEMI standards thermal resistance board (size: 76.1×114.3×1.6tmm, glass epoxy) is used.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## Allowable Operating Conditions at Ta = -40 °C to +85 °C, $V_{SS}1 = V_{SS}2 = 0$ V

| Parameter                              | Symbol               | Pin/Remarks     | Conditions                                                                             |                     |                            | Speci  | fication                |      |

|----------------------------------------|----------------------|-----------------|----------------------------------------------------------------------------------------|---------------------|----------------------------|--------|-------------------------|------|

|                                        |                      |                 |                                                                                        | V <sub>DD</sub> [V] | min                        | typ    | max                     | unit |

| Operating                              | VDD(1)               | VDD1            | 0.245μs ≤ tCYC ≤ 200μs                                                                 |                     | 2.7                        |        | 5.5                     |      |

| supply voltage                         | VDD(2)               |                 | 0.367μs ≤ tCYC ≤ 200μs                                                                 |                     | 2.0                        |        | 5.5                     |      |

| (Note 2-1)                             | VDD(3)               |                 | $0.735 \mu s \le tCYC \le 200 \mu s$                                                   |                     | 1.8                        |        | 5.5                     |      |

| Memory<br>sustaining<br>supply voltage | VHD                  | VDD1            | RAM and register contents sustained in HOLD mode.                                      |                     | 1.6                        |        |                         | V    |

| High level input voltage               | VIH(1)               | Port 0,1<br>P70 |                                                                                        | 1.8 to 5.5          | 0.3V <sub>DD</sub><br>+0.7 |        | V <sub>DD</sub>         | V    |

|                                        | VIH(4)               | CF1,CF2, RES    |                                                                                        | 1.8 to 5.5          | 0.75V <sub>DD</sub>        |        | $V_{DD}$                |      |

| Low level                              | VIL(1)               | Port 0,1        |                                                                                        | 4.0 to 5.5          | $V_{SS}$                   |        | 0.1V <sub>DD</sub> +0.4 |      |

| input voltage                          |                      | P70             |                                                                                        | 1.8 to 4.0          | $V_{SS}$                   |        | 0.2V <sub>DD</sub>      |      |

|                                        | VIL(4)               | CF1,CF2, RES    |                                                                                        | 1.8 to 5.5          | $V_{SS}$                   |        | 0.25V <sub>DD</sub>     |      |

| Instruction                            | tCYC                 |                 |                                                                                        | 2.7 to 5.5          | 0.245                      |        | 200                     |      |

| cycle time                             | (Note 2-2)           |                 |                                                                                        | 2.0 to 5.5          | 0.367                      |        | 200                     | μS   |

| (Note 2-2)                             |                      |                 |                                                                                        | 1.8 to 5.5          | 0.735                      |        | 200                     |      |

| External                               | FEXCF                | CF1             | CF2 pin open                                                                           | 2.7 to 5.5          | 0.1                        |        | 12                      |      |

| system clock<br>frequency              |                      |                 | System clock frequency<br>division ratio=1/1     External system clock<br>duty=50 ± 5% | 2.2 to 5.5          | 0.1                        |        | 8                       | MHz  |

| Oscillation frequency                  | FmCF(1)              | CF1,CF2         | When 12MHz ceramic oscillation See Fig. 1.                                             | 2.7 to 5.5          |                            | 12     |                         |      |

| range<br>(Note 2-3)                    | FmCF(2)              | CF1,CF2         | When 8MHz ceramic oscillation See Fig. 1.                                              | 2.2 to 5.5          |                            | 8      |                         |      |

|                                        | FmCF(3)              | CF1,CF2         | When 4MHz ceramic oscillation See Fig. 1.                                              | 1.8 to 5.5          |                            | 4      |                         |      |

|                                        | FmFRC(1)             |                 | Internal high-speed RC oscillation Ta=-10°C to +85°C (Note 2-4)                        | 1.8 to 5.5          | 7.76                       | 8.0    | 8.24                    | MHz  |

|                                        | FmFRC(2)             |                 | Internal high-speed RC oscillation Ta=-40°C to +85°C (Note 2-4)                        | 1.8 to 5.5          | 7.60                       | 8.0    | 8.40                    |      |

|                                        | FmRC                 |                 | Internal medium-speed RC oscillation                                                   | 1.8 to 5.5          | 0.5                        | 1.0    | 2.0                     |      |

|                                        | FmSRC                |                 | Internal low-speed RC oscillation (Note 2-5)                                           | 1.8 to 5.5          | 27                         | 30     | 33                      | kHz  |

|                                        | FsX'tal              | XT1,XT2         | 32.768kHz crystal oscillation<br>See Fig. 2.                                           | 1.8 to 5.5          |                            | 32.768 |                         | kHz  |

|                                        | FmPWMRC              |                 | Internal high-speed RC oscillation for HPWM2                                           | 2.7 to 5.5          | 38                         | 40     | 42                      | MHz  |

| Oscillation                            | tmsCF                | CF1,CF2         | When oscillation circuit is                                                            |                     | See Tab                    | le 1   |                         |      |

| Stabilization<br>Time                  | tmsFRC<br>(Note 2-4) |                 | switched from "oscillation stopped" to "oscillation                                    | 1.8 to 5.5          |                            |        | 100                     | μS   |

|                                        | tmsPWMR<br>C         |                 | enabled" .                                                                             | 1.8 to 5.5          |                            |        | 100                     | μο   |

|                                        | tmsRC                |                 | • See Fig. 3.                                                                          | 1.8 to 5.5          |                            | 0      | ļ                       |      |

|                                        | tmsSRC<br>(Note2-5)  |                 |                                                                                        | 1.8 to 5.5          |                            |        | 1                       | ms   |

|                                        | tmsX'tal             | XT1,XT2         |                                                                                        |                     | See Tab                    | le 2   |                         |      |

- Note 2-1: VDD must be held greater than or equal to 2.7V in the flash ROM onboard programming mode.

- Note 2-2: Relationship between tCYC and oscillation frequency is 3/FmCF at a division ratio of 1/1 and 6/FmCF at a division ratio of 1/2.

- Note 2-3: See Tables 1 and 2 for the oscillation constants.

- Note 2-4: An oscillation stabilization time of  $100\mu s$  or longer must be provided before switching the system clock source after the state of the high-speed RC oscillation circuit is switched from "oscillation stopped" to "oscillation enabled".

- Note 2-5: An oscillation stabilization time of 1ms or longer must be provided before switching the system clock source after the state of the low-speed RC oscillation circuit is switched from "oscillation stopped" to "oscillation enabled".

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## Electrical Characteristics at Ta = -40°C to +85°C, $V_{SS}1$ = $V_{SS}2$ = 0V

| Description              | O. made ad          | Dia/Damania                 | O and distance                                                                                                    |                     |                      | Specifica           | ation |      |

|--------------------------|---------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|---------------------|-------|------|

| Parameter                | Symbol              | Pin/Remarks                 | Conditions                                                                                                        | V <sub>DD</sub> [V] | min                  | typ                 | max   | unit |

| High level input current | l <sub>IH</sub> (1) | Port 0,1,<br>Port 7,<br>RES | Output disabled Pull-up resistor off V <sub>IN</sub> =V <sub>DD</sub> (Including output Tr's off leakage current) | 1.8 to 5.5          |                      |                     | 1     |      |

|                          | I <sub>IH</sub> (2) | CF1                         | V <sub>IN</sub> =V <sub>DD</sub>                                                                                  | 1.8 to 5.5          |                      |                     | 15    |      |

| Low level input current  | I <sub>IL</sub> (1) | Port 0,1,<br>Port 7,<br>RES | Output disabled Pull-up resistor off VIN=VSS (Including output Tr's off leakage current)                          | 1.8 to 5.5          | -1                   |                     |       | μА   |

|                          | I <sub>IL</sub> (2) | CF1                         | V <sub>IN</sub> =V <sub>SS</sub>                                                                                  | 1.8 to 5.5          | -15                  |                     |       |      |

| High level output        | V <sub>OH</sub> (1) | Port 0,1,                   | I <sub>OH</sub> =-1mA                                                                                             | 4.5 to 5.5          | V <sub>DD</sub> -1   |                     |       | V    |

| voltage                  | V <sub>OH</sub> (2) | CF2                         | I <sub>OH</sub> =-0.2mA                                                                                           | 1.8 to 5.5          | V <sub>DD</sub> -0.4 |                     |       | V    |

| Low level output         | V <sub>OL</sub> (1) | Port 0,1,                   | I <sub>OL</sub> =10mA                                                                                             | 4.5 to 5.5          |                      |                     | 1.5   |      |

| voltage                  | V <sub>OL</sub> (2) | P70,CF1,CF2                 | I <sub>OL</sub> =1.0mA                                                                                            | 1.8 to 5.5          |                      |                     | 0.4   |      |

| Pull-up resistance       | Rpu(1)              | Port 0,1,                   | V <sub>OH</sub> =0.9V <sub>DD</sub>                                                                               | 4.5 to 5.5          | 15                   | 35                  | 80    |      |

|                          | Rpu(2)              | P70                         |                                                                                                                   | 1.8 to 4.5          | 18                   | 50                  | 230   | kΩ   |

|                          | Rpu(3)              | RES                         |                                                                                                                   | 1.8 to 5.5          | 300                  | 400                 | 500   |      |

| Hysteresis voltage       | VHYS(1)             | Port 0,1,                   |                                                                                                                   | 2.7 to 5.5          |                      | 0.1V <sub>DD</sub>  |       | V    |

|                          |                     | P70<br>RES                  |                                                                                                                   | 1.8 to 5.5          |                      | 0.07V <sub>DD</sub> |       |      |

| Pin capacitance          | СР                  | All pins                    | For pins other than that under test:  VIN=VSS f=1MHz Ta=25°C                                                      | 1.8 to 5.5          |                      | 10                  |       | pF   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### < Recommended Operating Conditions >

| External oscillation | Operating supply voltage range | System division ratio | Cycle time | AD division ratio | AD conversion time<br>(TCAD) |          |  |

|----------------------|--------------------------------|-----------------------|------------|-------------------|------------------------------|----------|--|

| (FmCF)               | (V <sub>DD</sub> )             | (SYSDIV)              | (tCYC)     | (ADDIV)           | 12bit AD                     | 8bit AD  |  |

| CF-8MHz              | 2.7V to 5.5V                   | 1/1                   | 375ns      | 1/8               | 52.25μs                      | 32.25μs  |  |

| CF-OIVITIZ           | 2.2V to 5.5V                   | 1/1                   | 375ns      | 1/32              | 208.25μs                     | 128.25µs |  |

|                      | 2.7V to 5.5V                   | 1/1                   | 750ns      | 1/8               | 104.5μs                      | 64.5μs   |  |

| CF-4MHz              | 2.2V to 5.5V                   | 1/1                   | 750ns      | 1/16              | 208.5μs                      | 128.5µs  |  |

|                      | 1.8V to 5.5V                   | 1/1                   | 750ns      | 1/32              | 416.5μs                      | 256.5μs  |  |

- Note 6-1: The quantization error ( $\pm 1/2$ LSB) is excluded from the absolute accuracy. The absolute accuracy is measured when no change occurs in the I/O state of the pins that are adjacent to the analog input channel during AD conversion processing.

- Note 6-2: The conversion time refers to the interval from the time a conversion starting instruction is issued till the time the complete digital value against the analog input value is loaded in the result register.

The conversion time is twice the normal value when one of the following conditions occurs:

- The first AD conversion executed in the 12-bit AD conversion mode after a system reset

- The first AD conversion executed after the AD conversion mode is switched from 8-bit to 12-bit AD conversion mode

Note 6-3: See section 8, " $10 \times /20 \times$  amplifier characteristics", for analog channel 0 ( $10 \times /20 \times$  amplifier output).

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## Reference Voltage Generator Circuit (VREF) Characteristics

at  $Ta = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{SS}1 = V_{SS}2 = 0V$

| Parameter                                     | Symbol  | Pin/Remarks  | Conditions |                     |                      | Specific | ation    |      |

|-----------------------------------------------|---------|--------------|------------|---------------------|----------------------|----------|----------|------|

| Parameter                                     | Symbol  | Fill/Remarks |            | V <sub>DD</sub> [V] | min                  | typ      | max      | unit |

| VREF=2V voltage                               | VREF2VO | VREF         |            | 1.8 to 2.0          | V <sub>DD</sub> -0.1 |          | $V_{DD}$ |      |

| accuracy                                      |         | (Note 7-2)   |            | 2.0 to 5.5          | 1.90                 |          | 2.02     |      |

|                                               |         |              |            | 2.3 to 5.5          | 1.98                 |          | 2.02     | .,   |

| VREF=4V voltage                               | VREF4VO |              |            | 1.8 to 4.0          | V <sub>DD</sub> -0.1 |          | $V_{DD}$ | V    |

| accuracy                                      |         |              |            | 4.0 to 5.5          | 3.90                 |          | 4.04     |      |

|                                               |         |              |            | 4.3 to 5.5          | 3.96                 |          | 4.04     |      |

| VREFoutput current                            | VREFIO  |              |            | 1.8 to 5.5          | V <sub>SS</sub>      |          | 0.5      | mA   |

| Operation<br>stabilization time<br>(Note 7-1) | tVREFW  |              |            | 1.8 to 5.5          |                      |          | 5        | ms   |

Note 7-1: Refers to the interval between the time VR12ON and VR24ON are set to 1 and the time operation gets stabilized.

Note 7-2: An external 4.7μF capacitor must be connected to the VREF pin to stabilize the VREF voltage.

## Power-on Reset (POR) Characteristics at Ta = -40°C to +85°C, $V_{SS}1 = V_{SS}2 = 0V$

|                                      |        |               |                                        |                            | Specification |     |      |      |

|--------------------------------------|--------|---------------|----------------------------------------|----------------------------|---------------|-----|------|------|

| Parameter                            | Symbol | Pin / Remarks | Conditions                             | Option Selected<br>Voltage | min           | typ | max  | unit |

| POR release voltage                  | PORRL  |               | Option selected (Note 11-1)            | 1.67V                      | 1.10          |     | 1.79 |      |

| Detection voltage unpredictable area | POUKS  |               | See Fig. 8.<br>(Note 11-2)             |                            |               | 0.7 | 0.95 | V    |

| Power supply rise time               | PORIS  |               | Power startup time from VDD=0V to 1.6V |                            |               |     | 100  | ms   |

Note 11-1: The POR release voltage can be selected when the low-voltage detection feature is deselected.

Note 11-2: There is an unpredictable area before the transistor starts to turn on.

## Low Voltage Detection Reset (LVD) Characteristics at Ta = -40 °C to +85 °C, $V_{SS}1 = V_{SS}2 = 0$ V

|                                                                     |                   |               |                            |                            |      | Specific | ation |      |

|---------------------------------------------------------------------|-------------------|---------------|----------------------------|----------------------------|------|----------|-------|------|

| Parameter                                                           | Symbol            | Pin / Remarks | ks Conditions              | Option Selected<br>Voltage | min  | typ      | max   | unit |

| LVD reset voltage                                                   | LVDET             |               | Option selected            | 1.91V                      | 1.81 | 1.91     | 2.01  |      |

| (Note 12-2)                                                         |                   |               | See Fig. 9.                | 2.01V                      | 1.91 | 2.01     | 2.11  |      |

|                                                                     |                   |               | (Note 12-1)                | 2.31V                      | 2.21 | 2.31     | 2.41  |      |

|                                                                     |                   |               | (Note 12-3)                | 2.51V                      | 2.41 | 2.51     | 2.61  | V    |

|                                                                     |                   |               |                            | 2.81V                      | 2.71 | 2.81     | 2.93  |      |

|                                                                     |                   |               |                            | 3.79V                      | 3.69 | 3.79     | 3.92  |      |

|                                                                     |                   |               |                            | 4.28V                      | 4.18 | 4.28     | 4.41  |      |

| LVD voltage                                                         | LVD voltage LVHYS |               |                            | 1.91V                      |      | 55       |       | mV   |

| hysteresis                                                          |                   |               |                            | 2.01V                      |      | 55       |       |      |

|                                                                     |                   |               |                            | 2.31V                      |      | 55       |       |      |

|                                                                     |                   |               |                            | 2.51V                      |      | 55       |       |      |

|                                                                     |                   |               |                            | 2.81V                      |      | 60       |       |      |

|                                                                     |                   |               |                            | 3.79V                      |      | 65       |       |      |

|                                                                     |                   |               |                            | 4.28V                      |      | 65       |       |      |

| Detection voltage unpredictable area                                | LVUKS             |               | See Fig. 9.<br>(Note 12-4) |                            |      | 0.7      | 0.95  | ٧    |

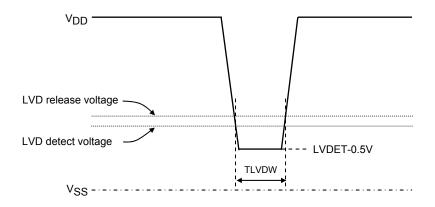

| Minimum low<br>voltage detection<br>width (response<br>sensitivity) | TLVDW             |               | LVDET-0.5V<br>See Fig. 10. |                            | 0.2  |          |       | ms   |

Note 12-1: The LVD reset voltage can be selected from 7 levels when the low-voltage detection feature is selected.

Note 12-2: The hysteresis voltage is not included in the LVD reset voltage specification value.

Note 12-3: There are cases when the LVD reset voltage specification value is exceeded when a greater change in the output level or large current is applied to the port.

Note 12-4: There is an unpredictable area before the transistor starts to turn on.

## Consumption Current Characteristics at $Ta = -40^{\circ}C$ to $+85^{\circ}C,~V_{SS}1 = V_{SS}2 = 0V$

| Danamatan                       | O. mah al | Pin /                                                                                            | Conditions                                                                                                                                |            | Specification |      |      |    |  |

|---------------------------------|-----------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|------|------|----|--|

| Parameter                       | Symbol    | Remarks                                                                                          | Conditions                                                                                                                                | min        | typ           | max  | unit |    |  |

| Normal mode consumption current | IDDOP(1)  | V <sub>DD</sub> 1                                                                                | FmCF=8MHz ceramic oscillation mode     System clock set to 8MHz mode     Internal low-/medium-speed RC oscillation                        | 2.2 to 5.5 |               | 3.8  | 5.2  |    |  |

| (Note 13-1)<br>(Note 13-2)      |           |                                                                                                  | stopped Internal high-speed RC oscillation stopped Frequency division ratio set to 1/1                                                    | 2.2 to 3.6 |               | 2.2  | 2.9  |    |  |

|                                 | IDDOP(2)  |                                                                                                  | FmCF=4MHz ceramic oscillation mode     System clock set to 4MHz mode     Internal low-/medium-speed RC oscillation                        | 1.8 to 5.5 |               | 2.1  | 3.5  |    |  |

|                                 |           |                                                                                                  | stopped Internal high-speed RC oscillation stopped Frequency division ratio set to 1/1                                                    | 1.8 to 3.6 |               | 1.1  | 1.7  |    |  |

|                                 | IDDOP(3)  |                                                                                                  | FsX'tal=32.768kHz crystal oscillation mode     Internal low-speed RC oscillation stopped     System clock set to internal medium-speed RC | 1.8 to 5.5 |               | 0.23 | 0.39 | mA |  |

|                                 |           |                                                                                                  | oscillation mode  Internal high-speed RC oscillation stopped Frequency division ratio set to 1/2                                          | 1.8 to 3.6 |               | 0.13 | 0.19 |    |  |

| Internal low-/medium-sp         |           | FsX'tal=32.768kHz crystal oscillation mode     Internal low-/medium-speed RC oscillation stopped | 1.8 to 5.5                                                                                                                                |            | 2.7           | 3.6  |      |    |  |

|                                 |           |                                                                                                  | System clock set to internal high-speed RC oscillation mode     Frequency division ratio set to 1/1                                       | 1.8 to 3.6 |               | 1.7  | 2.3  |    |  |

|                                 | IDDOP(5)  |                                                                                                  | External oscillation FsX'tal/FmCF stopped     System clock set to internal low-speed RC oscillation mode                                  | 1.8 to 5.5 |               | 10   | 42   |    |  |

|                                 |           |                                                                                                  | Internal medium-speed RC oscillation stopped     Internal high-speed RC oscillation stopped     Frequency division ratio set to 1/1       | 1.8 to 3.6 |               | 6    | 21   |    |  |

|                                 | IDDOP(6)  |                                                                                                  | FsX'tal=32.768kHz crystal oscillation mode     System clock set to 32.768kHz mode     Internal low-/medium-speed RC oscillation           | 1.8 to 5.5 |               | 46   | 101  | μА |  |

|                                 |           |                                                                                                  | stopped Internal high-speed RC oscillation stopped Frequency division ratio set to 1/2                                                    | 1.8 to 3.6 |               | 16   | 40   |    |  |

Continued on next page.

## F-ROM Programming Characteristics at $Ta = +10^{\circ}C$ to $+55^{\circ}C$ , $V_{SS}1 = V_{SS}2 = 0V$

| Damanatan                   | O. made ad | Dia /Danasala     | Conditions                                                     |                     | Specification |     |     |      |

|-----------------------------|------------|-------------------|----------------------------------------------------------------|---------------------|---------------|-----|-----|------|

| Parameter                   | Symbol     | Pin/Remarks       | Conditions                                                     | V <sub>DD</sub> [V] | min           | typ | max | unit |

| Onboard programming current | IDDFW(1)   | V <sub>DD</sub> 1 | Excluding power<br>dissipation in the<br>microcontroller block | 2.2 to 5.5          |               | 5   | 10  | mA   |

| Programming                 | tFW(1)     |                   | Erasing time                                                   | 0.04.55             |               | 20  | 30  | ms   |

| time                        | tFW(2)     |                   | Programming time                                               | 2.2 to 5.5          |               | 40  | 60  | μS   |

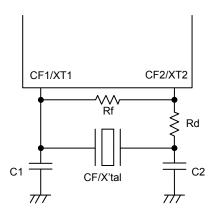

## **Characteristics of a Sample Main System Clock Oscillation Circuit**

Given below are the characteristics of a sample main system clock oscillation circuit that are measured using a SANYO-designated oscillation characteristics evaluation board and external components with circuit constant values with which the oscillator vendor confirmed normal and stable oscillation.

Table 1 Characteristics of a Sample Main System Clock Oscillator Circuit with a Ceramic Oscillator

■MURATA Manufacturing Co., Ltd.

| Nominal   | _    |                 | Circuit Constant |      |      |      | Operating            | Oscillation Stabilization Time |      |            |

|-----------|------|-----------------|------------------|------|------|------|----------------------|--------------------------------|------|------------|

| Frequency | Туре | Oscillator Name | C1               | C2   | Rf   | Rd   | Voltage Range<br>[V] | typ                            | max  | Remarks    |

|           |      |                 | [pF]             | [pF] | [Ω]  | [Ω]  |                      | [ms]                           | [ms] |            |

| 12MHz     | SMD  | CSTCE12M0G52-R0 | (10)             | (10) | Open | 680  | 2.6 to 5.5           | 0.02                           | 0.3  | C1 and C2  |

| 8MHz      | SMD  | CSTCE8M00G52-R0 | (10)             | (10) | Open | 1k   | 2.1 to 5.5           | 0.02                           | 0.3  | integrated |

| 4MHz      | SMD  | CSTCR4M00G53-R0 | (15)             | (15) | Open | 1.5k | 1.8 to 5.5           | 0.03                           | 0.45 | type       |

## **Characteristics of a Sample Subsystem Clock Oscillation Circuit**

Given below are the characteristics of a sample subsystem clock oscillation circuit that are measured using a SANYO-designated oscillation characteristics evaluation board and external components with circuit constant values with which the oscillator vendor confirmed normal and stable oscillation.

Table 2 Characteristics of a Sample Subsystem Clock Oscillator Circuit that Uses a Crystal Oscillator

#### ■EPSON TOYOCOM

| Nominal   | _    | Oscillator Name | Circuit Constant |            |           |           | Operating            | Oscillation Stabilization Time |             |                             |

|-----------|------|-----------------|------------------|------------|-----------|-----------|----------------------|--------------------------------|-------------|-----------------------------|

| Frequency | Туре |                 | C1<br>[pF]       | C2<br>[pF] | Rf<br>[Ω] | Rd<br>[Ω] | Voltage Range<br>[V] | typ<br>[ms]                    | max<br>[ms] | Remarks                     |

| 32.768kHz | SMD  | MC-306          | 9                | 9          | Open      | 330k      | 1.8 to 5.5           | 1.4                            | 4.0         | Applicable CL value = 7.0pF |

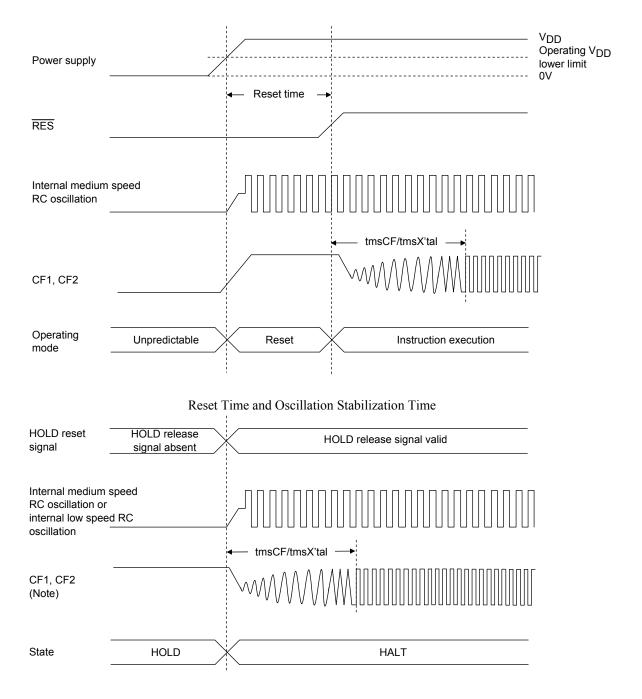

The oscillation stabilization time refers to the time interval that is required for the oscillation to get stabilized in the following cases (see Figure 3):

- Till the oscillation gets stabilized after the instruction for starting the subclock oscillation circuit is executed

- Till the oscillation gets stabilized after the HOLD mode is released.

Note: The components that are involved in oscillation should be placed as close to the IC and to one another as possible because they are vulnerable to the influences of the circuit pattern.

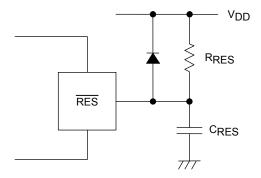

Figure 1 CF/XT Oscillator Circuit

Figure 2 AC Timing Measurement Point

HOLD Release Signal and Oscillation Stabilization Time

Note: When an external oscillation circuit is selected.

Figure 3 Oscillation Stabilization Time

### Note:

The external circuit for reset may vary depending on the usage of POR and LVD. See "Reset Function" in the user's manual.

Figure 4 Sample Reset Circuit

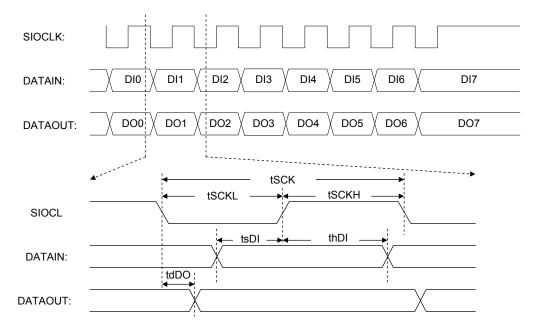

Figure 5 Serial I/O Waveform

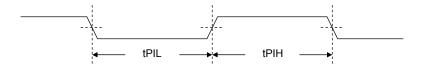

Figure 6 Pulse Input Timing Signal Waveform

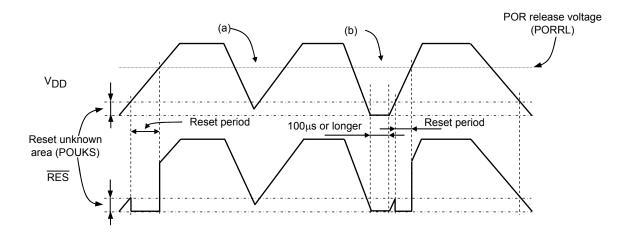

Figure 8 Example of POR Only (LVD Deselected) Mode Waveforms (at Reset Pin with RRES Pull-up Resistor Only)

- $\bullet$  The POR function generates a reset only when the power voltage goes up from the  $V_{\mbox{\footnotesize{NS}}}$  level.

- No stable reset will be generated if power is turned on again when the power level does not go down to the V<sub>SS</sub> level

as shown in (a). If such a case is anticipated, use the LVD function together with the POR function or implement an

external reset circuit as shown below.

- A reset is generated only when the power level goes down to the V<sub>SS</sub> level as shown in (b) and power is turned on again after this condition continues for 100µs or longer.

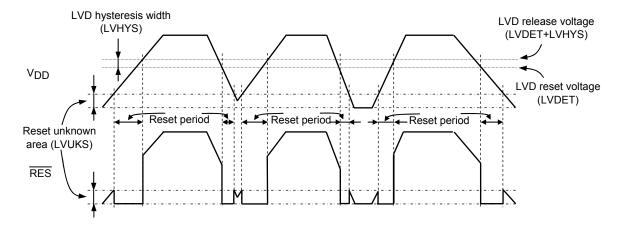

Figure 9 Example of POR + LVD Mode Waveforms (at Reset Pin with RRES Pull-up Resistor Only)

- Resets are generated both when power is turned on and when the power level lowers.

- A hysteresis width (LVHYS) is provided to prevent the repetitions of reset release and entry cycles near the detection level.

Figure 10 Minimum Low Voltage Detection Width (Example of Voltage Sag/Fluctuation Waveform)

## ORDERING INFORMATION

| Device           | Package                                    | Shipping (Qty / Packing) |  |  |  |  |

|------------------|--------------------------------------------|--------------------------|--|--|--|--|

| LC87F0G08AUJA-AH | SSOP24(225mil)<br>(Pb-Free / Halogen Free) | 2000 / Tape & Reel       |  |  |  |  |

| LC87F0G08AUJA-FH | SSOP24(225mil)<br>(Pb-Free / Halogen Free) | 2000 / Tape & Reel       |  |  |  |  |

| LC87F0G08AUJA-ZH | SSOP24(225mil)<br>(Pb-Free / Halogen Free) | 1400 / Fan-Fold          |  |  |  |  |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa