Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>Details</b> Product Status | Obsolete                                                                   |

|-------------------------------|----------------------------------------------------------------------------|

|                               |                                                                            |

| Core Processor                | F <sup>2</sup> MC-16LX                                                     |

| Core Size                     | 16-Bit                                                                     |

| Speed                         | 16MHz                                                                      |

| Connectivity                  | CANbus, EBI/EMI, SCI, Serial I/O, UART/USART                               |

| Peripherals                   | POR, PWM, WDT                                                              |

| Number of I/O                 | 78                                                                         |

| Program Memory Size           | 384KB (384K x 8)                                                           |

| Program Memory Type           | FLASH                                                                      |

| EEPROM Size                   | -                                                                          |

| RAM Size                      | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd)    | 3V ~ 5.25V                                                                 |

| Data Converters               | A/D 8x8/10b                                                                |

| Oscillator Type               | External                                                                   |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                          |

| Mounting Type                 | Surface Mount                                                              |

| Package / Case                | 100-BQFP                                                                   |

| Supplier Device Package       | 100-QFP (14x20)                                                            |

| Purchase URL                  | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f591gpf-ge1 |

# MB90590G Series

# Contents

| Product Lineup             | 3  |

|----------------------------|----|

| Pin Assignment             | 5  |

| Pin Description            |    |

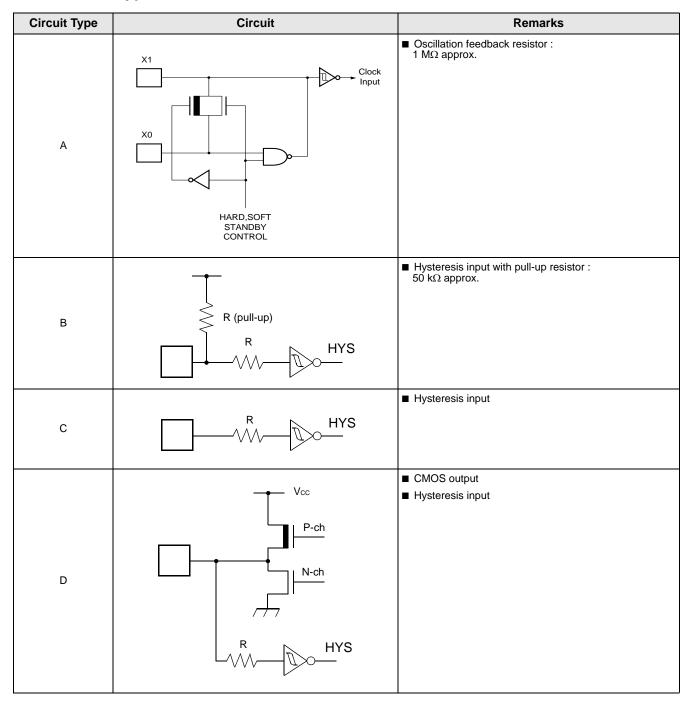

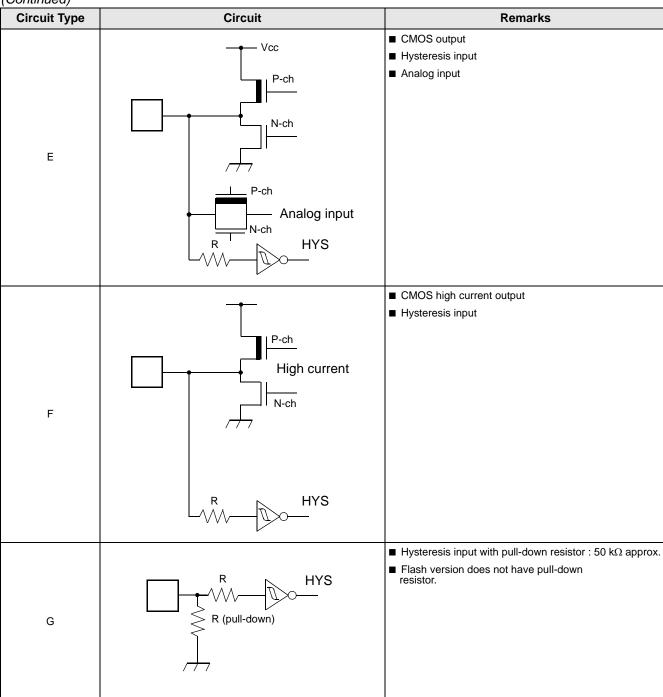

| I/O Circuit Type           | 10 |

| Handling Devices           | 12 |

| Block Diagram              | 16 |

| Memory Space               | 17 |

| I/O Map                    |    |

| CAN Controllers            |    |

| Interrupt Map              | 33 |

| Electrical Characteristics |    |

| Absolute Maximum Ratings   | 35 |

| Recommended Conditions     |    |

| DC Characteristics         | 38 |

| . 40 |

|------|

| . 47 |

| . 48 |

| . 49 |

| . 50 |

| . 51 |

| . 52 |

| . 53 |

| . 54 |

| . 55 |

|      |

# 4. I/O Circuit Type

## (9) N.C. Pin

The N.C. (internally connected) pin must be opened for use.

#### (10) Notes on Energization

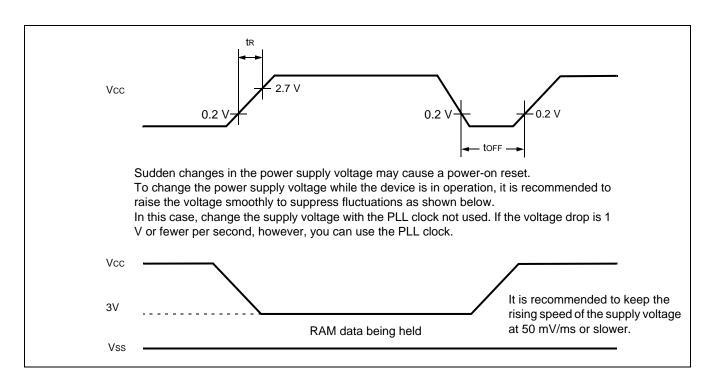

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at  $50 \mu s$  or more (0.2 V to 2.7 V).

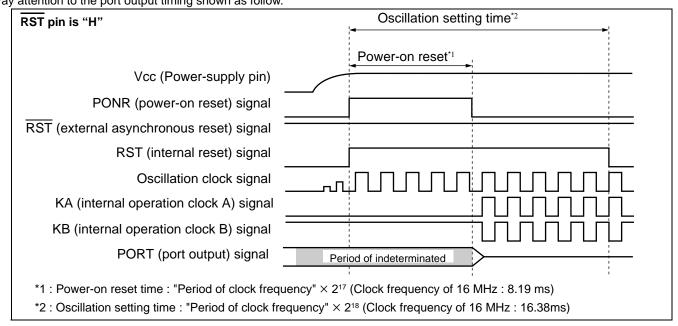

## (11) Indeterminate outputs from ports 0 and 1 (without MB90F591G/591G, MB90F594G)

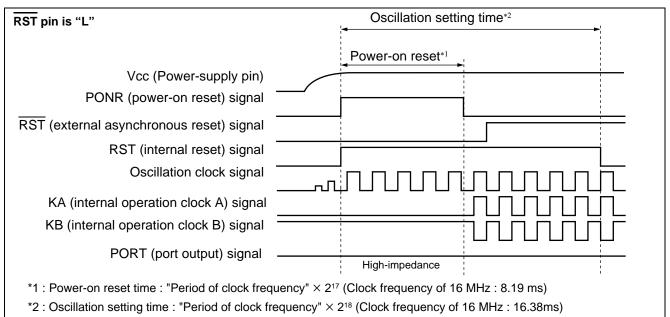

During oscillation setting time of step-down circuit (during a power-on reset) after the power is turned on, the outputs from ports 0 and 1 become following state.

- If RST pin is "H", the outputs become indeterminate.

- If RST pin is "L", the outputs become high-impedance. Pay attention to the port output timing shown as follow.

## (12) Initialization

The device contains internal registers which are initialized only by a power-on reset. To initialize these registers, please turn on the power again.

#### (13) Directions of "DIV A, Ri" and "DIVW A, RWi" instructions

In the Signed multiplication and division instructions ("DIV A, Ri" and "DIVW A, RWi"), the value of the corresponding bank register (DTB, ADB, USB, SSB) is set in "00 H".

If the values of the corresponding bank registers (DTB,ADB,USB,SSB) are set to other than "00 H", the remainder by the execution result of the instruction is not stored in the register of the instruction operand.

#### (14) Using REALOS

The use of El<sup>2</sup>OS is not possible with the REALOS real time operating system.

## (15) Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected in the microcontroller, it may attempt to continue the operation using the free-running frequency of the automatic oscillating circuit in the PLL circuitry even if the oscillator is out of place or the clock input is stopped. Performance of this operation, however, cannot be guaranteed.

Document Number: 002-07698 Rev. \*A Page 15 of 55

# 8. I/O Map

| Address    | Register                            | Abbreviation | Access | Peripheral  | Initial value     |

|------------|-------------------------------------|--------------|--------|-------------|-------------------|

| 00н        | Port 0 Data Register                | PDR0         | R/W    | Port 0      | XXXXXXXXB         |

| 01н        | Port 1 Data Register                | PDR1         | R/W    | Port 1      | XXXXXXXXB         |

| 02н        | Port 2 Data Register                | PDR2         | R/W    | Port 2      | XXXXXXXXB         |

| 03н        | Port 3 Data Register                | PDR3         | R/W    | Port 3      | XXXXXXXXB         |

| 04н        | Port 4 Data Register                | PDR4         | R/W    | Port 4      | XXXXXXXXB         |

| 05н        | Port 5 Data Register                | PDR5         | R/W    | Port 5      | XXXXXXXXB         |

| 06н        | Port 6 Data Register                | PDR6         | R/W    | Port 6      | XXXXXXXXB         |

| 07н        | Port 7 Data Register                | PDR7         | R/W    | Port 7      | XXXXXXXXB         |

| 08н        | Port 8 Data Register                | PDR8         | R/W    | Port 8      | XXXXXXXXB         |

| 09н        | Port 9 Data Register                | PDR9         | R/W    | Port 9      | XXXXXXB           |

| 0Ан to 0Fн |                                     | Reser        | ved    |             |                   |

| 10н        | Port 0 Direction Register           | DDR0         | R/W    | Port 0      | 0 0 0 0 0 0 0 0в  |

| 11н        | Port 1 Direction Register           | DDR1         | R/W    | Port 1      | 0 0 0 0 0 0 0 0 В |

| 12н        | Port 2 Direction Register           | DDR2         | R/W    | Port 2      | 0 0 0 0 0 0 0 0 В |

| 13н        | Port 3 Direction Register           | DDR3         | R/W    | Port 3      | 0 0 0 0 0 0 0 0 В |

| 14н        | Port 4 Direction Register           | DDR4         | R/W    | Port 4      | 0 0 0 0 0 0 0 0 В |

| 15н        | Port 5 Direction Register           | DDR5         | R/W    | Port 5      | 0 0 0 0 0 0 0 0 В |

| 16н        | Port 6 Direction Register           | DDR6         | R/W    | Port 6      | 0 0 0 0 0 0 0 0в  |

| 17н        | Port 7 Direction Register           | DDR7         | R/W    | Port 7      | 0 0 0 0 0 0 0 0 В |

| 18н        | Port 8 Direction Register           | DDR8         | R/W    | Port 8      | 0 0 0 0 0 0 0 0 В |

| 19н        | Port 9 Direction Register           | DDR9         | R/W    | Port 9      | 000000            |

| 1Ан        |                                     | Reser        | ved    |             |                   |

| 1Вн        | Analog Input Enable Register        | ADER         | R/W    | Port 6, A/D | 11111111          |

| 1Сн to 1Fн |                                     | Reser        | ved    |             | •                 |

| 20н        | Serial Mode Control Register 0      | UMC0         | R/W    |             | 0 0 0 0 0 1 0 0в  |

| 21н        | Serial Status Register 0            | USR0         | R/W    | LIADTO      | 0 0 0 1 0 0 0 0в  |

| 22н        | Serial Input/Output Data Register 0 | UIDR0/UODR0  | R/W    | UART0       | XXXXXXXXB         |

| 23н        | Rate and Data Register 0            | URD0         | R/W    |             | 0 0 0 0 0 0 0 Хв  |

| 24н        | Serial Mode Control Register 1      | UMC1         | R/W    |             | 0 0 0 0 0 1 0 0в  |

| 25н        | Serial Status Register 1            | USR1         | R/W    |             | 0 0 0 1 0 0 0 0в  |

| 26н        | Serial Input/Output Data Register 1 | UIDR1/UODR1  | R/W    | UART1       | XXXXXXXX          |

| 27н        | Rate and Data Register 1            | URD1         | R/W    |             | 0 0 0 0 0 0 0 Хв  |

| Address     | Register                                                                           | Abbreviation         | Access           | Peripheral                          | Initial value            |  |  |  |  |  |  |

|-------------|------------------------------------------------------------------------------------|----------------------|------------------|-------------------------------------|--------------------------|--|--|--|--|--|--|

| 60н         | Watch Timer Control Register (low-or-<br>der)                                      | WTCR                 | R/W              | Watch Timer                         | 0 0 0 0 0 Ов             |  |  |  |  |  |  |

| 61н         | Watch Timer Control Register (high-or-<br>der)                                     | WTCR                 | R/W              | watch Timer                         | 0 0 0 0 0 0 0 0 0в       |  |  |  |  |  |  |

| 62н         | PWM Control Register 0                                                             | PWC0                 | R/W              | Stepping Motor<br>Controller 0      | 0 0 0 0 0 Ов             |  |  |  |  |  |  |

| 63н         |                                                                                    | Reserved             |                  |                                     |                          |  |  |  |  |  |  |

| 64н         | PWM Control Register 1                                                             | PWC1                 | R/W              | Stepping Motor<br>Controller 1      | 0 0 0 0 0 Ов             |  |  |  |  |  |  |

| 65н         |                                                                                    | Re                   | served           |                                     | •                        |  |  |  |  |  |  |

| 66н         | PWM Control Register 2                                                             | PWC2                 | R/W              | Stepping Motor<br>Controller 2      | 0 0 0 0 0 Ов             |  |  |  |  |  |  |

| 67н         |                                                                                    | Re                   | served           |                                     |                          |  |  |  |  |  |  |

| 68н         | PWM Control Register 3                                                             |                      | R/W              | Stepping Motor<br>Controller 3      | 0 0 0 0 0 Ов             |  |  |  |  |  |  |

| 69н to 6Cн  |                                                                                    | Re                   | served           |                                     |                          |  |  |  |  |  |  |

| 6Dн         | Serial I/O Prescaler Register                                                      | CDCR                 | R/W              | Prescaler (Serial I/O)              | 0 XXX 1 1 1 1в           |  |  |  |  |  |  |

| 6Ен         | Timer Control Status Register                                                      | TCCS                 | R/W              | 16-bit Free-run Timer               | 0 0 0 0 0 0 0 0 В        |  |  |  |  |  |  |

| 6Fн         | ROM Mirror Function Select Register                                                | ROMM                 | W                | ROM Mirror                          | XXXXXXX1 <sub>B</sub>    |  |  |  |  |  |  |

| 70н to 8Fн  | Reserved for                                                                       | CAN Interface 0/1. F | Refer to section | on about CAN Controller             |                          |  |  |  |  |  |  |

| 90н to 9Dн  |                                                                                    | Re                   | served           |                                     |                          |  |  |  |  |  |  |

| 9Ен         | Program Address Detection Control<br>Status Register                               | PACSR                | R/W              | Address Match<br>Detection Function | 0 0 0 0 0 0 0 0 0в       |  |  |  |  |  |  |

| 9Fн         | Delayed Interrupt/Release Register                                                 | DIRR                 | R/W              | Delayed Interrupt                   | Ов                       |  |  |  |  |  |  |

| А0н         | Low Power Mode Control Register                                                    | LPMCR                | R/W              | Low Power Controller                | 00011000в                |  |  |  |  |  |  |

| А1н         | Clock Selection Register                                                           | CKSCR                | R/W              | Low Power Controller                | 11111100в                |  |  |  |  |  |  |

| A2н to A7н  |                                                                                    | Re                   | served           |                                     |                          |  |  |  |  |  |  |

| А8н         | Watchdog Timer Control Register                                                    | WDTC                 | R/W              | Watchdog Timer                      | XXXXX 1 1 1 <sub>B</sub> |  |  |  |  |  |  |

| А9н         | Time Base Timer Control Register                                                   | TBTC                 | R/W              | Time Base Timer                     | 1 0 0 1 0 Ов             |  |  |  |  |  |  |

| AAн to ADн  |                                                                                    | Re                   | served           |                                     |                          |  |  |  |  |  |  |

| <b>АЕ</b> н | Flash Memory Control Status Register (Flash product only. Otherwise reserved) FMCS |                      | R/W              | Flash Memory                        | 0 0 0 Х 0 0 0 0в         |  |  |  |  |  |  |

| АГн         |                                                                                    | Re                   | served           |                                     |                          |  |  |  |  |  |  |

| Address        | Register                                  | Abbreviation                                       | Access | Peripheral             | Initial value |

|----------------|-------------------------------------------|----------------------------------------------------|--------|------------------------|---------------|

| 1930н          | Output Compare Register 0 (low-order)     | OCCP0                                              | R/W    |                        | XXXXXXXXB     |

| 1931н          | Output Compare Register 0 (high-order)    | egister 0 (high-order) OCCP0 R/W Output Compare 0/ |        |                        | XXXXXXXXB     |

| 1932н          | Output Compare Register 1 (low-order)     | OCCP1                                              | R/W    | Output Compare 0/1     | XXXXXXXXB     |

| 1933н          | Output Compare Register 1 (high-order)    | OCCP1                                              | R/W    |                        | XXXXXXXXB     |

| 1934н          | Output Compare Register 2 (low-order)     | OCCP2                                              | R/W    |                        | XXXXXXXXB     |

| 1935н          | Output Compare Register 2 (high-order)    | OCCP2                                              | R/W    | 0.45.4 0.55.5 0/0      | XXXXXXXXB     |

| 1936н          | Output Compare Register 3 (low-order)     | OCCP3                                              | R/W    | Output Compare 2/3     | XXXXXXXX      |

| 1937н          | Output Compare Register 3 (high-order)    | OCCP3                                              | R/W    |                        | XXXXXXXX      |

| 1938н          | Output Compare Register 4 (low-order)     | OCCP4                                              | R/W    |                        | XXXXXXXX      |

| 1939н          | Output Compare Register 4 (high-order)    | OCCP4                                              | R/W    | 0.4                    | XXXXXXXXB     |

| 193Ан          | Output Compare Register 5 (low-order)     | OCCP5                                              | R/W    | Output Compare 4/5     | XXXXXXXXB     |

| 193Вн          | Output Compare Register 5 (high-order)    | OCCP5                                              | R/W    |                        | XXXXXXXXB     |

| 193Сн to 193Fн |                                           | Reserve                                            | ed     |                        |               |

| 1940н          | Timer 0/Reload Register 0<br>(low-order)  | TMR0/TMRLR0                                        | R/W    | 40 hit Daland Timon 0  | XXXXXXXXB     |

| 1941н          | Timer 0/Reload Register 0<br>(high-order) | TMR0/TMRLR0                                        | R/W    | 16-bit Reload Timer 0  | XXXXXXXXB     |

| 1942н          | Timer 1/Reload Register 1<br>(low-order)  | TMR1/TMRLR1                                        | R/W    | 40 kii Dalaad Tirran 4 | XXXXXXXXB     |

| 1943н          | Timer 1/Reload Register 1<br>(high-order) | TMR1/TMRLR1                                        | R/W    | 16-bit Reload Timer 1  | XXXXXXXXB     |

| 1944н          | Timer Data Register (low-order)           | TCDT                                               | R/W    | 40 L'I F T'            | 00000000      |

| 1945н          | Timer Data Register (high-order)          | TCDT                                               | R/W    | 16-bit Free-run Timer  | 00000000      |

| 1946н          | Frequency Data Register                   | SGFR                                               | R/W    |                        | XXXXXXXXB     |

| 1947н          | Amplitude Data Register                   | SGAR                                               | R/W    | 010                    | XXXXXXXXB     |

| 1948н          | Decrement Grade Register                  | SGDR                                               | R/W    | Sound Generator        | XXXXXXXX      |

| 1949н          | Tone Count Register                       | SGTR                                               | R/W    |                        | XXXXXXXX      |

| Address        | Register                                | Abbreviation             | Access      | Peripheral          | Initial value     |

|----------------|-----------------------------------------|--------------------------|-------------|---------------------|-------------------|

| 194Ан          | Sub-second Data Register (low-order)    | WTBR                     | R/W         |                     | XXXXXXX           |

| 194Вн          | Sub-second Data Register (middle-order) | WTBR                     | R/W         | Watch Timer         | XXXXXXX           |

| 194Сн          | Sub-second Data Register (high-order)   | WTBR                     | R/W         |                     | XXXXXB            |

| 194Dн          | Second Data Register                    | WTSR                     | R/W         |                     | 000000в           |

| 194Ен          | Minute Data Register                    | WTMR                     | R/W         | Watch Timer         | 000000в           |

| 194Fн          | Hour Data Register                      | WTHR                     | R/W         | vvatch filler       | 00000в            |

| 1950н          | PWM1 Compare Register 0                 | PWC10                    | R/W         |                     | XXXXXXXXB         |

| 1951н          | PWM2 Compare Register 0                 | PWC20                    | R/W         | Stepping Motor Con- | XXXXXXXXB         |

| 1952н          | PWM1 Select Register 0                  | PWS10                    | R/W         | troller 0           | 000000в           |

| 1953н          | PWM2 Select Register 0                  | PWS20                    | R/W         |                     | _ 0 0 0 0 0 0 0 в |

| 1954н          | PWM1 Compare Register 1                 | PWC11                    | R/W         |                     | XXXXXXXXB         |

| 1955н          | PWM2 Compare Register 1                 | PWC21                    | R/W         | Stepping Motor Con- | XXXXXXXXB         |

| 1956н          | PWM1 Select Register 1                  | PWS11                    | R/W         | troller 1           | 000000в           |

| 1957н          | PWM2 Select Register 1                  | PWS21                    | R/W         |                     | _ 0 0 0 0 0 0 0 в |

| 1958н          | PWM1 Compare Register 2                 | PWC12                    | R/W         |                     | XXXXXXXXB         |

| 1959н          | PWM2 Compare Register 2                 | PWC22                    | R/W         | Stepping Motor Con- | XXXXXXXXB         |

| 195Ан          | PWM1 Select Register 2                  | PWS12                    | R/W         | troller 2           | 000000в           |

| 195Вн          | PWM2 Select Register 2                  | PWS22                    | R/W         |                     | _ 0 0 0 0 0 0 0 в |

| 195Сн          | PWM1 Compare Register 3                 | PWC13                    | R/W         |                     | XXXXXXXXB         |

| 195Dн          | PWM2 Compare Register 3                 | PWC23                    | R/W         | Stepping Motor Con- | XXXXXXXXB         |

| 195Ен          | PWM1 Select Register 3                  | PWS13                    | R/W         | troller 3           | 000000в           |

| 195Fн          | PWM2 Select Register 3                  | PWS23                    | R/W         |                     | _0 0 0 0 0 0 0 в  |

| 1960н to 19FFн |                                         | Reserve                  | ed          |                     |                   |

| 1A00н to 1AFFн | CAN Inte                                | erface 0. Refer to secti | on about CA | AN Controller       |                   |

| 1В00н to 1ВFFн | CAN Inte                                | erface 1. Refer to secti | on about CA | AN Controller       |                   |

| 1С00н to 1СFFн | CAN Inte                                | erface 0. Refer to secti | on about CA | AN Controller       |                   |

| 1D00н to 1DFFн | CAN Inte                                | erface 1. Refer to secti | on about CA | AN Controller       |                   |

| 1E00н to 1EFFн |                                         | Reserve                  | ed          |                     |                   |

## 9. CAN Controllers

The CAN controller has the following features: Conforms to CAN Specification Version 2.0 Part A and B

- Supports transmission/reception in standard frame and extended frame formats

- Supports transmission of data frames by receiving remote frames

- 16 transmitting/receiving message buffers

- 29-bit ID and 8-byte data

- Multi-level message buffer configuration

- Provides full-bit comparison, full-bit mask, acceptance register 0/acceptance register 1 for each message buffer as 1D acceptance mask

- ☐ Two acceptance mask registers in either standard frame format or extended frame formats

- Bit rate programmable from 10 Kbit/s to 2 Mbit/s (when input clock is at 16 MHz)

## **List of Control Registers**

| Add     | ress    | Register                            | Abbreviation | Access | Initial Value      |  |

|---------|---------|-------------------------------------|--------------|--------|--------------------|--|

| CAN0    | CAN1    | Register                            | Abbreviation | Access | illitial value     |  |

| 000070н | 000080н | Message buffer valid register       | BVALR        | R/W    | 0000000 00000000   |  |

| 000071н | 000081н | Wessage buller valid register       | DVALK        | IX/VV  | 0000000 0000000B   |  |

| 000072н | 000082н | Transmit request register           | TREQR        | R/W    | 00000000 00000000в |  |

| 000073н | 000083н | Transmitrequest register            | IKEQK        | FC/ VV | 0000000 0000000B   |  |

| 000074н | 000084н | Transmit cancel register            | TCANR        | W      | 00000000 00000000в |  |

| 000075н | 000085н | Transmit cancer register            | TOANK        | VV     | OUUUUUU UUUUUUUB   |  |

| 000076н | 000086н | Transmit complete register          | TCR          | R/W    | 00000000 00000000  |  |

| 000077н | 000087н | Transmit complete register          | TOK          | IX/ VV | 00000000 00000000B |  |

| 000078н | 000088н | Receive complete register           | RCR          | R/W    | 00000000 00000000  |  |

| 000079н | 000089н | Receive complete register           | KCK          | IX/VV  | 00000000 0000000B  |  |

| 00007Ан | 00008Ан | Remote request receiving register   | RRTRR        | R/W    | 00000000 00000000  |  |

| 00007Вн | 00008Вн | Remote request receiving register   | KKIKK        | IX/VV  | 00000000 000000000 |  |

| 00007Сн | 00008Сн | Receive overrun register            | ROVRR        | R/W    | 00000000 00000000  |  |

| 00007Dн | 00008Дн | Neceive overruit register           | ROVER        | IT/VV  | 00000000 00000000  |  |

| 00007Ен | 00008Ен | Receive interrupt enable register   | RIER         | R/W    | 00000000 00000000  |  |

| 00007Fн | 00008Fн | Receive iliterrupt errable register | RIER         | IT/VV  | 00000000 00000000B |  |

(Continued)

Document Number: 002-07698 Rev. \*A Page 27 of 55

List of Message Buffers (DLC Registers and Data Registers)

| Address                  |                          | (DLC Registers and Data Registers) |              |          |                            |  |

|--------------------------|--------------------------|------------------------------------|--------------|----------|----------------------------|--|

|                          |                          | Register                           | Abbreviation | Access   | Initial Value              |  |

| CAN0                     | CAN1                     |                                    |              |          |                            |  |

| 001А60н                  | 001В60н                  | DLC register 0                     | DLCR0        | R/W      | XXXX <sub>B</sub>          |  |

| 001А61н                  | 001В61н                  | -                                  |              |          |                            |  |

| 001А62н                  | 001В62н                  | DLC register 1                     | DLCR1        | R/W      | XXXX <sub>B</sub>          |  |

| 001А63н                  | 001В63н                  | · ·                                |              |          |                            |  |

| 001А64н                  | 001В64н                  | DLC register 2                     | DLCR2        | R/W      | XXXX <sub>B</sub>          |  |

| 001А65н                  | 001В65н                  | ŭ                                  |              |          |                            |  |

| 001А66н                  | 001В66н                  | DLC register 3                     | DLCR3        | R/W      | XXXX <sub>B</sub>          |  |

| 001А67н                  | 001В67н                  |                                    |              |          |                            |  |

| 001А68н                  | 001В68н                  | DLC register 4                     | DLCR4        | R/W      | ХХХХв                      |  |

| 001А69н                  | 001В69н                  | - 13                               |              |          |                            |  |

| 001А6Ан                  | 001В6Ан                  | DLC register 5                     | DLCR5        | R/W      | XXXX <sub>B</sub>          |  |

| 001А6Вн                  | 001В6Вн                  |                                    | 220.00       |          |                            |  |

| 001А6Сн                  | 001В6Сн                  | DLC register 6                     | DLCR6        | R/W      | XXXX <sub>B</sub>          |  |

| 001А6Dн                  | 001В6Он                  | DEG register o                     | BEOING       | 10,00    | 77776                      |  |

| 001А6Ен                  | 001В6Ен                  | DLC register 7                     | DLCR7        | R/W      | XXXX <sub>B</sub>          |  |

| 001А6Гн                  | 001В6Гн                  | DEC register 1                     | DECKY        | TX/VV    |                            |  |

| 001А70н                  | 001В70н                  | DLC register 8                     | DLCR8        | R/W      | XXXX                       |  |

| 001А71н                  | 001В71н                  | DEC register o                     | DECINO       | TX/VV    | 70001                      |  |

| 001А72н                  | 001В72н                  | DLC register 9                     | DLCR9        | R/W      | XXXX <sub>B</sub>          |  |

| 001А73н                  | 001В73н                  | DEC register 9                     | DECKS        | IN/VV    | VVVR                       |  |

| 001А74н                  | 001В74н                  | DLC register 10                    | DLCR10       | R/W      | YYYY <sub>2</sub>          |  |

| 001А75н                  | 001В75н                  | DEC register 10                    | DECKTO       | IN/VV    | XXXX <sub>B</sub>          |  |

| 001А76н                  | 001В76н                  | DI C register 11                   | DLCR11       | R/W      | XXXX <sub>B</sub>          |  |

| 001А77н                  | 001В77н                  | DLC register 11                    | DECKTI       | IN/VV    | XXXXB                      |  |

| 001А78н                  | 001В78н                  | DLC register 12                    | DLCR12       | R/W      | XXXX <sub>B</sub>          |  |

| 001А79н                  | 001В79н                  | DLO register 12                    | DLORIZ       | ITA/ V V | <b>^</b> ^^                |  |

| 001А7Ан                  | 001В7Ан                  | DLC register 13                    | DI CB12      | R/W      | VVV-                       |  |

| 001А7Вн                  | 001В7Вн                  | DLC register 13                    | DLCR13       | Ft./ VV  | XXXX <sub>B</sub>          |  |

| 001А7Сн                  | 001В7Сн                  | DI C register 14                   | DI CD44      | D // /   | VVV-                       |  |

| 001А7Dн                  | 001В7Дн                  | DLC register 14                    | DLCR14       | R/W      | XXXX <sub>B</sub>          |  |

| 001А7Ен                  | 001В7Ен                  | DI C register 15                   | DI CD45      | DAM      | VVVV                       |  |

| 001А7Fн                  | 001В7Гн                  | DLC register 15                    | DLCR15       | R/W      | XXXX <sub>B</sub>          |  |

| 001A80н<br>to<br>001A87н | 001B80н<br>to<br>001B87н | Data register 0 (8 bytes)          | DTR0         | R/W      | XXXXXXXB<br>to<br>XXXXXXXB |  |

#### 11. Electrical Characteristics

# 11.1 Absolute Maximum Ratings

(Vss = AVss = 0.0 V)

| Davamatav                             | Cumahad           | Rat                   | ting        | l lm!4 | Domestic                                 |    |  |

|---------------------------------------|-------------------|-----------------------|-------------|--------|------------------------------------------|----|--|

| Parameter                             | Symbol            | Min                   | Max         | Unit   | Remarks                                  |    |  |

|                                       | Vcc               | Vss - 0.3             | Vss + 6.0   | V      |                                          |    |  |

|                                       | AVcc              | Vss - 0.3             | Vss + 6.0   | V      | Vcc = AVcc                               | *1 |  |

| Power supply voltage                  | AVRH,<br>AVRL     | V <sub>SS</sub> — 0.3 | Vss + 6.0   | V      | AVcc ≥ AVRH/L, AVRH ≥ AVRL               | *1 |  |

|                                       | DVcc              | $V_{SS} - 0.3$        | Vss + 6.0   | V      | Vcc ≥ DVcc                               |    |  |

| Input voltage                         | Vı                | $V_{SS} - 0.3$        | Vss + 6.0   | V      |                                          | *2 |  |

| Output voltage                        | Vo                | $V_{SS} - 0.3$        | Vss + 6.0   | V      |                                          | *2 |  |

| Max clamp current                     | ICLAMP            | -2.0                  | + 2.0       | mA     |                                          | *6 |  |

| Total Max clamp current               | $\Sigma$   ICLAMP | 1                     | 20          | mA     |                                          | *6 |  |

| "L" level Max output current          | l <sub>OL1</sub>  | ı                     | 15          | mA     | Normal output                            | *3 |  |

| "L" level avg. output current         | lolav1            | 1                     | 4           | mA     | Normal output, average value             | *4 |  |

| "L" level Max output current          | lol2              | ı                     | 40          | mA     | High current output                      | *3 |  |

| "L" level avg. output current         | lolav2            | ı                     | 30          | mA     | High current output, average value       | *4 |  |

| "L" level Max overall output current  | ∑lol1             | _                     | 100         | mA     | Total normal output                      |    |  |

| "L" level Max overall output current  | ∑lol2             |                       | 330         | mA     | Total high current output                |    |  |

| "L" level avg. overall output current | ∑lolav1           | _                     | 50          | mA     | Total normal output, average value       | *5 |  |

| "L" level avg. overall output current | ∑lolav2           |                       | 250         | mA     | Total high current output, average value | *5 |  |

| "H" level Max output current          | Іон1              | _                     | -15         | mA     | Normal output                            | *3 |  |

| "H" level avg. output current         | IOHAV1            | _                     | -4          | mA     | Normal output, average value             | *4 |  |

| "H" level Max output current          | Іон2              | _                     | -40         | mA     | High current output                      | *3 |  |

| "H" level avg. output current         | IOHAV2            | _                     | -30         | mA     | High current output, average value       | *4 |  |

| "H" level Max overall output current  | ∑Іон1             | _                     | -100        | mA     | Total normal output                      |    |  |

| "H" level Max overall output current  | ∑Іон2             | _                     | -330        | mA     | Total high current output                |    |  |

| "H" level avg. overall output current | ∑IOHAV1           | _                     | <b>-</b> 50 | mA     | Total normal output, average value       | *5 |  |

| "H" level avg. overall output current | ∑IOHAV2           | _                     | -250        | mA     | Total high current output, average value | *5 |  |

| Power consumption                     | Pp                | _                     | 500         | mW     | MB90F594G, MB90F591G                     |    |  |

| 1 ower consumption                    | טו                | _                     | 400         | mW     | MB90594G, MB90591G                       |    |  |

| Operating temperature                 | TA                | -40                   | +85         | °C     |                                          |    |  |

| Storage temperature                   | Tstg              | <b>-</b> 55           | +150        | °C     |                                          |    |  |

<sup>\*1 :</sup> AVcc, AVRH, AVRL and DVcc shall not exceed Vcc. AVRH and AVRL shall not exceed AVcc. Also, AVRL shall not exceed AVRH.

\*6 :

- Use within recommended operating conditions.

- Use at DC voltage (current)

- The +B signal should always be applied with a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pins does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

<sup>\*2:</sup> V<sub>I</sub> and V<sub>O</sub> should not exceed V<sub>CC</sub> + 0.3V. V<sub>I</sub> should not exceed the specified ratings. However if the maximum current to/from an input is limited by some means with external components, the I<sub>CLAMP</sub> rating supersedes the V<sub>I</sub> rating.

<sup>\*3 :</sup> The maximum output current is a peak value for a corresponding pin.

<sup>\*4 :</sup> Average output current is an average current value observed for a 100 ms period for a corresponding pin.

<sup>\*5 :</sup> Total average current is an average current value observed for a 100 ms period for all corresponding pins.

Applicable to pins: P00 to P07, P10 to P17, P20 to P27, P30 to P37, P40 to P47, P50 to P57, P60 to P67, P70 to P77, P80 to P87, P90 to P95

(MB90F591G, MB90591G :  $Vcc = 5.0 \text{ V}\pm5 \text{ %, Vss} = \text{AVss} = 0.0 \text{ V, T}_{A} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}$ )

| Parameter            | Symbol | Pin name                                                                                 | Condition |     | Value |     | Unit  | Remarks   |

|----------------------|--------|------------------------------------------------------------------------------------------|-----------|-----|-------|-----|-------|-----------|

| Farameter            | Symbol | Fill liaille                                                                             | Condition | Min | Тур   | Max | Oilit | Keillaiks |

| Input capacity       | Cin    | Other than C,<br>AVcc, AVss,<br>AVRH,<br>AVRL, Vcc,<br>Vss, DVcc,<br>DVss,<br>P70 to P87 | I         | _   | 5     | 15  | pF    |           |

|                      |        | P70 to P87                                                                               |           | _   | 15    | 30  | pF    |           |

| Pull-up resistance   | Rup    | RST                                                                                      | _         | 25  | 50    | 100 | kΩ    |           |

| Pull-down resistance | RDOWN  | MD2                                                                                      | _         | 25  | 50    | 100 | kΩ    |           |

## 11.4 AC Characteristics

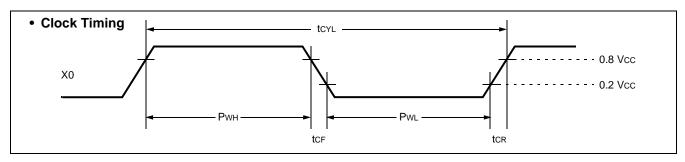

# 11.4.1 Clock Timing

(MB90V590G, MB90F594G, MB90594G :  $Vcc = 5.0 \text{ V}\pm10 \text{ %, Vss} = \text{AVss} = 0.0 \text{ V, T}_{A} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$  (MB90F591G, MB90591G :  $Vcc = 5.0 \text{ V}\pm5 ^{\circ}\text{K, Vss} = \text{AVss} = 0.0 \text{ V, T}_{A} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

| Parameter                      | Symbol         | Pin    | Value |       |     | Unit  | Remarks                        |

|--------------------------------|----------------|--------|-------|-------|-----|-------|--------------------------------|

| Farameter                      | Syllibol       | name   | Min   | Тур   | Max | Offic | Remarks                        |

| Oscillation frequency          | fc             | X0, X1 | 3     | _     | 16  | MHz   |                                |

| Oscillation cycle time         | <b>t</b> cyL   | X0, X1 | 62.5  | _     | 333 | ns    |                                |

| Input clock pulse width        | Pwh, PwL       | X0     | 10    | _     | _   | ns    | Duty ratio is about 30 to 70%. |

| Input clock rise and fall time | tcr, tcr       | X0     | _     | _     | 5   | ns    | When using external clock      |

| Machine clock frequency        | fcp            | _      | 1.5   | _     | 16  | MHz   |                                |

| Machine clock cycle time       | <b>t</b> cp    | _      | 62.5  | _     | 666 | ns    |                                |

| Flash read cycle time          | <b>t</b> CYCFL | _      | _     | 2 tcp | _   | ns    | When Flash is accessed by CPU  |

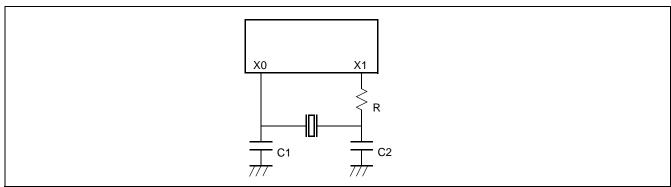

# Example of Oscillation circuit

Document Number: 002-07698 Rev. \*A

#### 11.4.3 Power On Reset

(MB90V590G, MB90F594G, MB90594G :  $V_{CC} = 5.0 \text{ V} \pm 10 \text{ %}$ ,  $V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}$ ,  $T_{A} = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ ) (MB90F591G, MB90591G :  $V_{CC} = 5.0 \text{ V} \pm 5 ^{\circ}\text{K}$ ,  $V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}$ ,  $T_{A} = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ )

| Parameter          | Symbol     | Pin name | Condition | Value   |    | Unit | Remarks                     |  |

|--------------------|------------|----------|-----------|---------|----|------|-----------------------------|--|

| raiailletei        | Min Max    |          | Oilit     | Nemarks |    |      |                             |  |

| Power on rise time | <b>t</b> R | Vcc      |           | 0.05    | 30 | ms   |                             |  |

| Power off time     | toff       | Vcc      | _         | 50      | _  | ms   | Due to repetitive operation |  |

#### Notes:

- Vcc must be kept lower than 0.2 V before power-on.

- The above values are used for creating a power-on reset.

- Some registers in the device are initialized only upon a power-on reset. To initialize these register, turn on the power supply using the above values.

Document Number: 002-07698 Rev. \*A Page 43 of 55

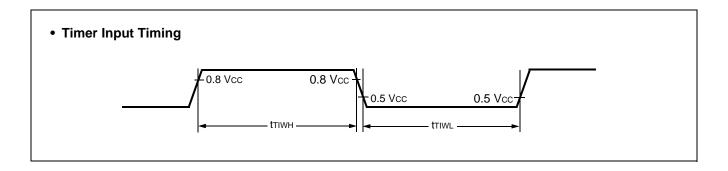

11.4.5 Timer Input Timing

(MB90V590G, MB90F594G, MB90594G :  $Vcc = 5.0 \text{ V} \pm 10 \text{ %}$ , Vss = AVss = 0.0 V,  $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ ) (MB90F591G, MB90591G :  $Vcc = 5.0 \text{ V} \pm 5 ^{\circ}$  %, Vss = AVss = 0.0 V,  $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ )

| Parameter         | Symbol        | Pin name   | Condition | Value |     | Unit  | Remarks                |  |

|-------------------|---------------|------------|-----------|-------|-----|-------|------------------------|--|

| Faranielei        | Syllibol      | riii name  |           | Min   | Max | Offic | Remarks                |  |

| Input pulse width | <b>t</b> тıwн | TIN0       |           | 4 tcp | _   | ns    | Under normal operation |  |

|                   | <b>t</b> TIWL | IN0 to IN5 | 1 -       | 1     | _   | μs    | In stop mode           |  |

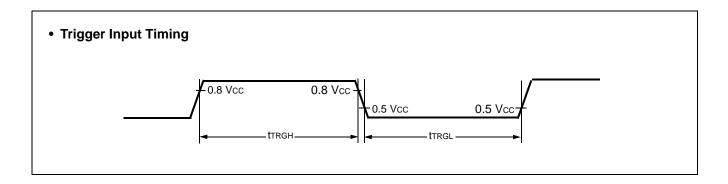

11.4.6 Trigger Input Timing

(MB90V590G, MB90F594G, MB90594G :  $Vcc = 5.0 \text{ V} \pm 10 \text{ %}$ , Vss = AVss = 0.0 V,  $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ ) (MB90F591G, MB90591G :  $Vcc = 5.0 \text{ V} \pm 5 ^{\circ}$ , Vss = AVss = 0.0 V,  $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ )

| Parameter         | Symbol         | Pin name              | Condition | Va    | lue | Unit | Remarks |

|-------------------|----------------|-----------------------|-----------|-------|-----|------|---------|

|                   | Symbol         |                       |           | Min   | Max |      |         |

| Input pulse width | ttrgh<br>ttrgl | INT0 to INT7,<br>ADTG | _         | 5 tcp | _   | ns   |         |

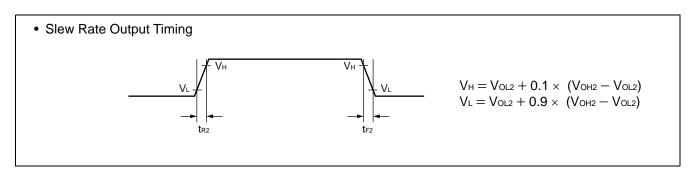

11.4.7 Slew Rate High Current Outputs (MB90F591G, MB90591G, MB90594G and MB90F594G only)

(MB90F594G, MB90594G :  $V_{CC} = 5.0 \text{ V} \pm 10 \text{ %}$ ,  $V_{SS} = AV_{SS} = 0.0 \text{ V}$ ,  $T_{A} = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ )

(MB90F591G, MB90591G :  $Vcc = 5.0 \text{ V}\pm5 \text{ %}$ , Vss = AVss = 0.0 V,  $TA = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ )

| Parameter             | Symbol          | Pin name                            | Condition | Va  | lue | Unit | Remarks |

|-----------------------|-----------------|-------------------------------------|-----------|-----|-----|------|---------|

|                       | Symbol          |                                     |           | Min | Max |      |         |

| Output Rise/Fall time | t <sub>R2</sub> | Port P70 to P77,<br>Port P80 to P87 | _         | 15  | 40  | ns   |         |

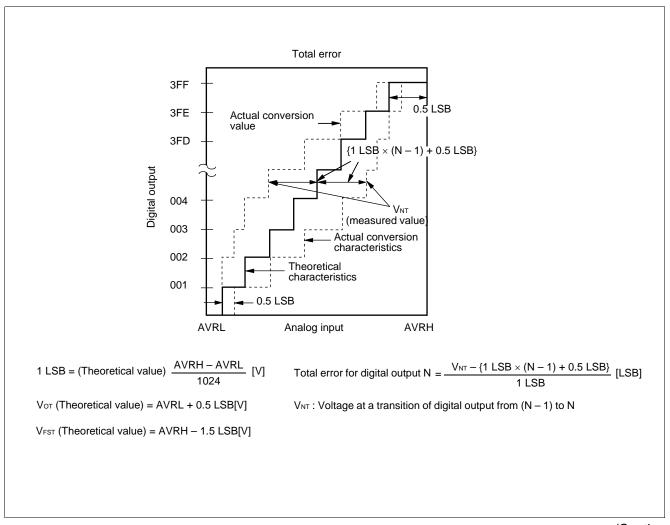

## 11.6 A/D Converter Glossary

Resolution: Analog changes that are identifiable with the A/D converter

Linearity error : The deviation of the straight line connecting the zero transition point ("00 0000 0000"  $\leftrightarrow$  "00 0000 0001") with the full-scale transition point ("11 1111 1110"  $\leftrightarrow$  "11 1111 1111") from actual conversion characteristics

Differential linearity error: The deviation of input voltage needed to change the output code by 1 LSB from the theoretical value

Total error: The total error is defined as a difference between the actual value and the theoretical value, which includes zero-transition error/full-scale transition error and linearity error.

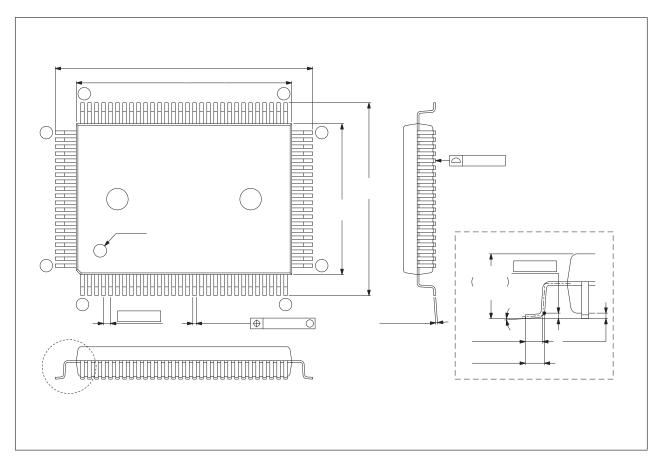

# 14. Package Dimension

# Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Lighting & Power Control cypress.com/powerpsoc Memory cypress.com/memory **PSoC** cypress.com/psoc Touch Sensing cypress.com/touch **USB** Controllers cypress.com/usb Wireless/RF cypress.com/wireless

## PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2008-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the aliure of the device or system (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the aliure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-07698 Rev. \*A Revised November 30, 2016 Page 55 of 55