Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

XE

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 20                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 13x8/12b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-WFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-WQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10flcana-w0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3. 16 | Interrupt Functions                                                                                | 193 |

|-------|----------------------------------------------------------------------------------------------------|-----|

|       | 3. 16. 1 Interrupt function types                                                                  | 193 |

|       | 3. 16. 2 Interrupt sources and configuration                                                       | 193 |

|       | 3. 16. 3 Registers controlling interrupt functions                                                 | 199 |

|       | 3. 16. 3. 1 Interrupt request flag register (IF0L, IF0H, IF1L, IF1H, IF2L, IF2H)                   | 204 |

|       | 3. 16. 3. 2 Interrupt mask flag register (MK0L, MK0H, MK1L, MK1H, MK2L, MK2H)                      | 206 |

|       | 3. 16. 3. 3 Priority specification flag registers (PR00L, PR00H, PR01L, PR01H, PR10L, PR10H,       |     |

|       | PR11L, PR11H, PR12L, PR12H, PR02L, PR02H)                                                          | 208 |

|       | 3. 16. 3. 4 External interrupt rising edge enable register (EGP0), External interrupt falling edge |     |

|       | enable register (EGN0)                                                                             | 212 |

|       | 3. 16. 3. 5 Program status word (PSW)                                                              | 213 |

|       | 3. 16. 4 Interrupt servicing operations                                                            | 213 |

| 3. 17 | Key Interrupt Function                                                                             | 214 |

|       | 3. 17. 1 Functions of key interrupt                                                                | 214 |

|       | 3. 17. 2 Configuration of key interrupt                                                            | 215 |

|       | 3. 17. 3 Register controlling key interrupt                                                        | 217 |

|       | 3. 17. 3. 1 Key return control register (KRCTL)                                                    | 217 |

|       | 3. 17. 3. 2 Key return mode register 0 (KRM0)                                                      | 217 |

|       | 3. 17. 3. 3 Key return flag register (KRF)                                                         | 217 |

|       | 3. 17. 3. 4 Port mode registers 0 to 2, 7 (PM0 to PM2, PM7)                                        | 218 |

|       | 3. 17. 3. 5 Peripheral I/O redirection register (PIOR)                                             | 219 |

|       | 3. 17. 4 Key interrupt operation                                                                   | 219 |

| 3. 18 | Standby Function                                                                                   | 220 |

| 3. 19 | Reset Function                                                                                     | 221 |

| 3. 20 | Power-On-Reset Circuit                                                                             | 222 |

| 3. 21 | Voltage Detector                                                                                   | 223 |

|       | 3. 21. 1 Functions of voltage detector                                                             | 223 |

|       | 3. 21. 2 Configuration of voltage detector                                                         | 224 |

|       | 3. 21. 3 Registers controlling voltage detector                                                    | 225 |

|       | 3. 21. 3. 1 Voltage detection register (LVIM)                                                      | 225 |

|       | 3. 21. 3. 2 Voltage detection level register (LVIS)                                                | 225 |

|       | 3. 21. 4 Operation of voltage detector                                                             | 228 |

|       | 3. 21. 5 Cautions for voltage detector                                                             | 228 |

| 3. 22 | Safety Functions                                                                                   | 229 |

|       | 3. 22. 1 Overview of safety functions                                                              | 229 |

|       | 3. 22. 2 Registers used by safety functions                                                        | 230 |

|       | 3. 22. 3 Operation of safety functions                                                             | 230 |

|       | 3. 22. 3. 1 Flash memory CRC operation function (high-speed CRC)                                   | 230 |

|       | 3. 22. 3. 2 CRC operation function (general-purpose CRC)                                           | 230 |

|       | 3. 22. 3. 3 RAM parity error detection function                                                    | 230 |

|       | 3. 22. 3. 4 RAM guard function                                                                     | 230 |

| Item                            |                      | 64-pin products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80-pin products            |  |  |

|---------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

|                                 |                      | R5F10FLx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R5F10FMx                   |  |  |

| Serial interface                | I <sup>2</sup> C bus | <ul> <li>64-pin products</li> <li>CSI: 1 channel / simplified l<sup>2</sup>C: 1 channel / UART: 1 channel</li> <li>UART: 1 channel</li> <li>CSI: 1 channel / UART (LIN-bus supported): 1 channel</li> <li>80-pin products</li> <li>CSI: 1 channel / simplified l<sup>2</sup>C: 1 channel / UART: 1 channel</li> <li>CSI: 1 channel / simplified l<sup>2</sup>C: 1 channel / UART: 1 channel</li> <li>CSI: 2 channels / simplified l<sup>2</sup>C: 1 channel / UART (LIN-bus supported): 1 channel</li> </ul> |                            |  |  |

| Multiplier and divider / multip |                      | Multiplier: 16 bits $\times$ 16 bits (Unsigned or signed                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ))                         |  |  |

| accumulator                     | .,                   | Divider: 32 bits ÷ 32 bits (Unsigned)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                          |  |  |

|                                 |                      | Multiply accumulator: 16 bits $\times$ 16 bits + 32 bits (Unsigned or signed)                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |  |  |

| DMA controller                  |                      | 2 cha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 channels                 |  |  |

| Vectored interrupt sources      | Internal             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |  |  |

|                                 | External             | 2 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |  |  |

| Key interrupt                   |                      | 4 ch (7) <sup>Note 1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4 ch (8) <sup>Note 1</sup> |  |  |

| Reset                           |                      | <ul> <li>Reset by RESET pin</li> <li>Internal reset by watchdog timer</li> <li>Internal reset by power-on-reset</li> <li>Internal reset by voltage detector</li> <li>Internal reset by illegal instruction execution <sup>Note 2</sup></li> <li>Internal reset by RAM parity error</li> <li>Internal reset by illegal-memory access</li> </ul>                                                                                                                                                               |                            |  |  |

| Power-on-reset circuit          |                      | Power-on-reset: 1.51 ±0.03 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |  |  |

|                                 |                      | Power-down-reset: 1.50 ±0.03 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |  |  |

| Voltage detector                |                      | Detection level: 3 stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |  |  |

| On-chip debug function          |                      | Provided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |  |  |

| Table 1-1 Outline of Functions | (Microcontroller Block) (2/2) |

|--------------------------------|-------------------------------|

|--------------------------------|-------------------------------|

<R>

**Notes 1.** The number in parentheses is the channels of key interrupt when using the peripheral I/O redirection register (PIOR).

**2.** The illegal instruction is generated when instruction code FFH is executed. Rest by the illegal instruction execution is not issued by emulation with the in-circuit emulator or on-chip debug emulator.

<R>

|               |              |              | (2/3)        |

|---------------|--------------|--------------|--------------|

| Function Name | RL78/G1E     | RL78/G1E     | RL78/G1A     |

|               | (64-pin)     | (80-pin)     | (64-pin)     |

| KR0           | $\checkmark$ |              | $\checkmark$ |

| KR1           | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| KR2           | $\checkmark$ |              | $\checkmark$ |

| KR3           | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| KR4           | (√)          | (√)          | $\checkmark$ |

| KR5           | (√)          | (√)          | $\checkmark$ |

| KR6           | (√)          | (√)          | $\checkmark$ |

| KR7           | _            | (√)          | $\checkmark$ |

| KR8           | _            | _            | $\checkmark$ |

| KR9           | -            | _            | $\checkmark$ |

| PCLBUZ0       | _            |              | $\checkmark$ |

| PCLBUZ1       | _            | _            |              |

| REGC          | $\checkmark$ |              |              |

| RTC1HZ        | _            | _            | $\checkmark$ |

| RESET         | $\checkmark$ |              |              |

| RXD0          | $\checkmark$ |              |              |

| RXD1          | $\checkmark$ |              |              |

| RXD2          | $\checkmark$ |              |              |

| SCK00         | $\checkmark$ |              |              |

| SCK01         | _            | _            |              |

| SCK10         | _            |              |              |

| SCK11         | _            | _            |              |

| SCK20         | _            |              |              |

| SCK21         |              |              |              |

| SCLA0         | _            | _            |              |

| SCL00         |              |              |              |

| SCL01         | _            | _            |              |

| SCL10         | _            |              |              |

| SCL11         | _            | _            |              |

| SCL20         | _            |              |              |

| SCL21         | _            | _            |              |

| SDAA0         | _            | _            |              |

| SDA00         |              |              |              |

| SDA01         | _            | _            |              |

| SDA10         | _            |              |              |

| SDA11         | _            | _            |              |

| SDA20         | _            |              |              |

| SDA21         | _            | _            |              |

| SI00          | $\checkmark$ |              |              |

| SI01          | _            | _            |              |

| SI10          | _            | √            |              |

| SI11          | _            | _            |              |

| SI20          | _            |              |              |

| SI21          |              | √            | ,<br>√       |

| 0121          | Y            | , v          | 1            |

<R> Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR).

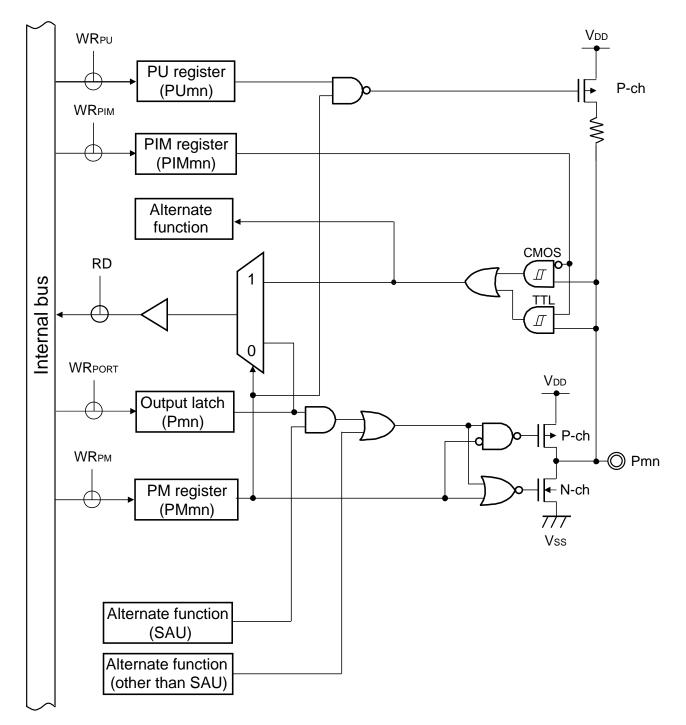

Figure 2-10. Pin Block Diagram for Pin Type 8-1-1

Remarks 1. For alternate functions, see 2. 1. 1 Port functions.

2. SAU: Serial array unit

<R>

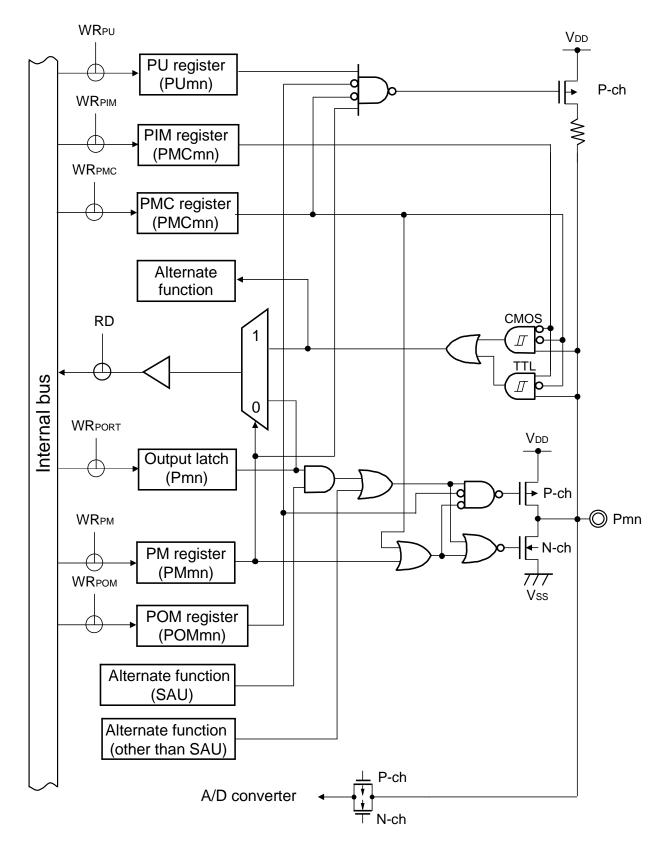

Figure 2-12. Pin Block Diagram for Pin Type 8-3-2

Remarks 1. For alternate functions, see 2. 1. 1 Port functions.

2. SAU: Serial array unit

#### 2. 5. 8 Port 13 (P130, P137)

#### (1) Port mode

P130 functions as an output port.

P137 functions as an input port.

## (2) Control mode

P137 functions as external interrupt request input.

#### (a) INTP0

This is an external interrupt request input pin for which the valid edge (rising edge, falling edge, or both rising and falling edges) can be specified.

#### 3. 4. 3. 1 Port mode register (PMxx)

#### (1) 64-pin products

| Symbol | 7    | 6    | 5    | 4     | 3     | 2     | 1     | 0     | Address | After Reset | R/W |

|--------|------|------|------|-------|-------|-------|-------|-------|---------|-------------|-----|

| PM0    | 1    | PM06 | PM05 | PM04  | PM03  | PM02  | PM01  | PM00  | FFF20H  | FFH         | R/W |

| PM1    | 1    | PM16 | 1    | PM14  | PM13  | PM12  | PM11  | PM10  | FFF21H  | FFH         | R/W |

| PM2    | PM27 | PM26 | PM25 | PM24  | PM23  | PM22  | PM21  | PM20  | FFF22H  | FFH         | R/W |

| PM4    | 1    | 1    | 1    | 1     | PM43  | PM42  | PM41  | PM40  | FFF24H  | FFH         | R/W |

| PM6    | 1    | 1    | 1    | 1     | PM63  | PM62  | PM61  | PM60  | FFF26H  | FFH         | R/W |

| PM7    | PM77 | PM76 | PM75 | PM74  | PM73  | PM72  | PM71  | PM70  | FFF27H  | FFH         | R/W |

| PM14   | 1    | 1    | 1    | 1     | 1     | 1     | PM141 | PM140 | FFF2EH  | FFH         | R/W |

| PM15   | 1    | 1    | 1    | PM154 | PM153 | PM152 | PM151 | PM150 | FFF2FH  | FFH         | R/W |

Cautions 1. Be sure to clear bits 4 to 6 of the PM0 register, bit 6 of the PM1 register, bits 4 to 7 of the PM2 register, bit 3 of the PM4 register, bits 0 to 3 of the PM6 register, bits 4 to 7 of the PM7 register, bits 0 and 1 of the PM14 register, and bits 0 to 4 of the PM15 register to "0".

2. Be sure to set bit 7 of the PM0 register, bits 5 and 7 of the PM1 register, bits 4 to 7 of the PM4 register, bits 4 to 7 of the PM6 register, bits 2 to 7 of the PM14 register, and bits 5 to 7 of the PM15 register to "1".

|         | Symbol | 7    | 6    | 5    | 4     | 3     | 2     | 1     | 0     | Address | After Reset | R/W |

|---------|--------|------|------|------|-------|-------|-------|-------|-------|---------|-------------|-----|

|         | PM0    | 1    | PM06 | PM05 | PM04  | PM03  | PM02  | PM01  | PM00  | FFF20H  | FFH         | R/W |

|         | PM1    | 1    | PM16 | PM15 | PM14  | PM13  | PM12  | PM11  | PM10  | FFF21H  | FFH         | R/W |

|         | PM2    | PM27 | PM26 | PM25 | PM24  | PM23  | PM22  | PM21  | PM20  | FFF22H  | FFH         | R/W |

|         | PM4    | 1    | 1    | 1    | 1     | PM43  | PM42  | PM41  | PM40  | FFF24H  | FFH         | R/W |

| <r></r> | PM5    | 1    | 1    | 1    | 1     | 1     | 1     | PM51  | PM50  | FFF25H  | FFH         | R/W |

|         | PM6    | 1    | 1    | 1    | 1     | PM63  | PM62  | PM61  | PM60  | FFF26H  | FFH         | R/W |

|         | PM7    | PM77 | PM76 | PM75 | PM74  | PM73  | PM72  | PM71  | PM70  | FFF27H  | FFH         | R/W |

|         | PM14   | 1    | 1    | 1    | 1     | 1     | 1     | PM141 | PM140 | FFF2EH  | FFH         | R/W |

|         | PM15   | 1    | 1    | 1    | PM154 | PM153 | PM152 | PM151 | PM150 | FFF2FH  | FFH         | R/W |

#### (2) 80-pin products

Cautions 1. Be sure to clear bits 5 and 6 of the PM0 register, bit 6 of the PM1 register, bits 5 to 7 of the PM2 register, bit 3 of the PM4 register, bits 0 to 3 of the PM6 register, bits 4 to 7 of the PM7 register, bit 1 of the PM14 register, and bits 0 to 4 of the PM15 register to "0".

<R>

2. Be sure to set bit 7 of the PM0 register, bit 7 of the PM1 register, bits 4 to 7 of the PM4 register, bits 2 to 7 of the PM5 register, bits 4 to 7 of the PM6 register, bits 2 to 7 of the PM14 register, and bits 5 to 7 of the PM15 register to "1".

#### 3.6 Timer Array Unit

In this section, the differences of the functions and registers from RL78/G1A (64-pin products) are described. For details, see CHAPTER 6 TIMER ARRAY UNIT in RL78/G1A Hardware User's Manual (R01UH0305E).

The timer array unit is provided in all products (Unit 0, Channels 0 to 7).

| Units  | Channels  | 64-pin products, 80-pin products |

|--------|-----------|----------------------------------|

| Unit 0 | Channel 0 | $\checkmark$                     |

|        | Channel 1 | $\checkmark$                     |

|        | Channel 2 | $\checkmark$                     |

|        | Channel 3 | $\checkmark$                     |

|        | Channel 4 | $\checkmark$                     |

|        | Channel 5 | $\checkmark$                     |

|        | Channel 6 | $\checkmark$                     |

|        | Channel 7 | $\checkmark$                     |

Caution Most of the following descriptions in this section use the case of 80-pin products as an example.

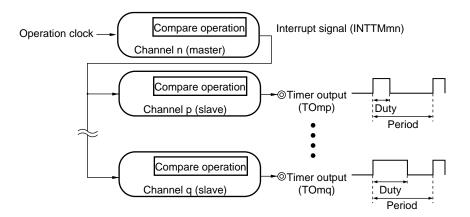

#### <3> Multiple PWM (Pulse Width Modulation) output

By extending the PWM function and using one master channel and two or more slave channels, up to seven types of PWM signals that have a specific period and a specified duty factor can be generated.

# Caution For details about the rules of simultaneous channel operation function, see 3. 6. 4 Basic rules of timer array unit.

**Remark** m: Unit number (m = 0), n: Channel number (n = 0 to 7 (however, timer input pin (TImn), timer output pin (TOmn) : n = 0, 4, 7), p, q: Slave channel number (4, 7)

#### 3. 6. 1. 3 8-bit timer operation function (channels 1 and 3 only)

The 8-bit timer operation function makes it possible to use a 16-bit timer channel in a configuration consisting of two 8-bit timer channels. This function can only be used for channels 1 and 3.

Caution There are several rules for using 8-bit timer operation function. For details, see 3. 6. 4 Basic rules of timer array unit.

#### 3. 6. 2 Configuration of timer array unit

Timer array unit includes the following hardware.

#### Table 3-8. Configuration of Timer Array Unit

| Item              | Configuration                                             |  |  |  |  |

|-------------------|-----------------------------------------------------------|--|--|--|--|

| Timer/counter     | Timer count register mn (TCRmn)                           |  |  |  |  |

| Register          | Timer data register mn (TDRmn)                            |  |  |  |  |

| Timer input       | TI00, TI04, TI07, RxD2 pin (for LIN-bus)                  |  |  |  |  |

| Timer output      | TO00, TO04, TO07, output controller                       |  |  |  |  |

| Control registers | <registers block="" of="" setting="" unit=""></registers> |  |  |  |  |

|                   | Peripheral enable register 0 (PER0)                       |  |  |  |  |

|                   | Timer clock select register m (TPSm)                      |  |  |  |  |

|                   | Timer channel enable status register m (TEm)              |  |  |  |  |

|                   | Timer channel start register m (TSm)                      |  |  |  |  |

|                   | • Timer channel stop register m (TTm)                     |  |  |  |  |

|                   | • Timer input select register 0 (TIS0)                    |  |  |  |  |

|                   | • Timer output enable register m (TOEm)                   |  |  |  |  |

|                   | • Timer output register m (TOm)                           |  |  |  |  |

|                   | Timer output level register m (TOLm)                      |  |  |  |  |

|                   | Timer output mode register m (TOMm)                       |  |  |  |  |

|                   | <registers channel="" each="" of=""></registers>          |  |  |  |  |

|                   | Timer mode register mn (TMRmn)                            |  |  |  |  |

|                   | Timer status register mn (TSRmn)                          |  |  |  |  |

|                   | Input switch control register (ISC)                       |  |  |  |  |

|                   | Noise filter enable register 1 (NFEN1)                    |  |  |  |  |

|                   | Port mode control register (PMCxx)                        |  |  |  |  |

|                   | Port mode register (PMxx)                                 |  |  |  |  |

|                   | Port register (Pxx)                                       |  |  |  |  |

**Remark** m: Unit number (m = 0), n: Channel number (n = 0 to 7)

The presence or absence of timer I/O pins in each timer array unit channel is as follows.

| Tir    | mer array unit channels | 64-pin products, 80-pin products |

|--------|-------------------------|----------------------------------|

| Unit 0 | Channel 0               | P00/TI00, P01/TO00               |

|        | Channel 1               | _                                |

|        | Channel 2               | -                                |

|        | Channel 3               | -                                |

|        | Channel 4               | P42/TI04/TO04                    |

|        | Channel 5               | -                                |

|        | Channel 6               | -                                |

|        | Channel 7               | P41/TI07/TO07                    |

Table 3-9. Timer I/O Pins provided in Each Product

- **Remarks 1.** When timer input and timer output are shared by the same pin, either only timer input or only timer output can be used.

- 2. -: here is no timer I/O pin, but the channel is available. (However, the channel can only be used as an interval timer.)

Figures 3-3 show the block diagrams of the timer array unit of the 80-pin products.

#### 3. 12. 1 Functions of serial array unit

Each serial interface supported by the RL78/G1E (64-pin products, 80-pin products) has the following features.

#### 3. 12. 1. 1 3-wire serial I/O (CSI00, CSI10, CSI20, CSI21)

Data is transmitted or received in synchronization with the serial clock (SCK) output from the master channel.

3-wire serial communication is clocked communication performed by using three communication lines: one for the serial clock (SCK), one for transmitting serial data (SO), one for receiving serial data (SI).

For details about the settings, see **3. 12. 5** Operation of 3-Wire serial I/O (CSI00, CSI10, CSI20, CSI21) Communication.

[Data transmission/reception]

- Data length of 7 or 8 bits

- Phase control of transmit/receive data

- MSB/LSB first selectable

- Level setting of transmit/receive data

[Clock control]

- Master/slave selection

- Phase control of I/O clock

- Setting of transfer period by prescaler and internal counter of each channel

- Maximum transfer rate During master communication (CSI00): Max. fcLK/2<sup>Note</sup>

During master communication (other than CSI00): Max. fcLk/4<sup>Note</sup>

During slave communication: Max. fmck/6<sup>Note</sup>

[Interrupt function]

• Transfer end interrupt/buffer empty interrupt

[Error detection flag]

• Overrun error

In addition, CSI00 of following channels supports the SNOOZE mode. When SCK input is detected while in the STOP mode, the SNOOZE mode makes data reception that does not require the CPU possible. Only CSI00 can be specified for asynchronous reception.

Note Use the clocks within a range satisfying the SCK cycle time (tkcr) characteristics (see CHAPTER 5 ELECTRICAL SPECIFICATIONS).

### 3.17 Key Interrupt Function

The number of key interrupt input channels differs, depending on the product.

|                | 64-pin products | 80-pin products |

|----------------|-----------------|-----------------|

| Key interrupt  | 4 ob (7 ob)     | 4  ob (9  ob)   |

| input channels | 4 ch (7 ch)     | 4 ch (8 ch)     |

**Remarks 1.** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR).

2. Most of the following descriptions in this section use the case of 80-pin products as an example.

#### 3. 17. 1 Functions of key interrupt

A key interrupt (INTKR) can be generated by inputting a rising/falling edge to the key interrupt input pins (KR0 to KR7). There are two ways to identify the channel(s) to which a valid edge has been input:

- · Identify the channel(s) (KR0 to KR7) by using the port input level.

- · Identify the channel(s) (KR0 to KR5) by using the key interrupt flag.

| Key Interrupt Pins | Key return mode register (KRM0) | Key return flag register (KRF) |

|--------------------|---------------------------------|--------------------------------|

| KR0                | KRM00                           | KRF0                           |

| KR1                | KRM01                           | KRF1                           |

| KR2                | KRM02                           | KRF2                           |

| KR3                | KRM03                           | KRF3                           |

| KR4                | KRM04                           | KRF4                           |

| KR5                | KRM05                           | KRF5                           |

| KR6                | KRM06                           | -                              |

| KR7                | KRM07                           | -                              |

#### Table 3-16. Assignment of Key Interrupt Detection Pins

Remark KR0 to KR3 (KR0 to KR6): 64-pin products

KR0 to KR3 (KR0 to KR7): 80-pin products

Functions in parentheses can be assigned via settings in the peripheral I/O redirection register (PIOR)

# (5) Gain control register 1 (GC1)

This register is used to specify the gain and feedback resistance of configurable amplifier Ch1.

The value to specify depends on the configuration of configurable amplifier Ch1.

When using configurable amplifiers Ch1 to Ch3 together as an instrumentation amplifier, be sure to set gain control register 1 (GC1) to 03H.

Reset signal input clears this register to 00H.

Address: 06H After reset: 00H R/W

|     | 7 | 6 | 5 | 4      | 3      | 2      | 1      | 0      |

|-----|---|---|---|--------|--------|--------|--------|--------|

| GC1 | 0 | 0 | 0 | AMPG14 | AMPG13 | AMPG12 | AMPG11 | AMPG10 |

# Table 4-1. Gain of Configurable Amplifier Ch1 (Non-Inverting Amplifier)

| AMPG14 | AMPG13 | AMPG12          | AMPG11 | AMPG10 | Gain of Configurable Amplifier Ch1 (Typ.) |

|--------|--------|-----------------|--------|--------|-------------------------------------------|

| 0      | 0      | 0               | 0      | 0      | 9.5 dB                                    |

| 0      | 0      | 0               | 0      | 1      | 10.9 dB                                   |

| 0      | 0      | 0               | 1      | 0      | 12.4 dB                                   |

| 0      | 0      | 0               | 1      | 1      | 14.0 dB                                   |

| 0      | 0      | 1               | 0      | 0      | 15.6 dB                                   |

| 0      | 0      | 1               | 0      | 1      | 17.3 dB                                   |

| 0      | 0      | 1               | 1      | 0      | 19.0 dB                                   |

| 0      | 0      | 1               | 1      | 1      | 20.8 dB                                   |

| 0      | 1      | 0               | 0      | 0      | 22.7 dB                                   |

| 0      | 1      | 0               | 0      | 1      | 24.5 dB                                   |

| 0      | 1      | 0               | 1      | 0      | 26.4 dB                                   |

| 0      | 1      | 0               | 1      | 1      | 28.3 dB                                   |

| 0      | 1      | 1               | 0      | 0      | 30.3 dB                                   |

| 0      | 1      | 1               | 0      | 1      | 32.2 dB                                   |

| 0      | 1      | 1               | 1      | 0      | 34.2 dB                                   |

| 0      | 1      | 1               | 1      | 1      | 36.1 dB                                   |

| 1      | 0      | 0               | 0      | 0      | 38.1 dB                                   |

| 1      | 0      | 0               | 0      | 1      | 40.1 dB                                   |

|        | C      | Other than abov | e      |        | Setting prohibited                        |

<R> **Remark** Bits 7 to 5 are fixed at 0 of read only.

#### **CHAPTER 5 ELECTRICAL SPECIFICATIONS**

In this capter, the electrical specification is described for the target products shown below.

| Target products | A: Consumer applications | $T_A = -40$ to $+85^{\circ}C$ |

|-----------------|--------------------------|-------------------------------|

|                 | R5F10FLCANA, R5F10FLCAN  | A, R5F10FLDANA, R5F10FLDANA,  |

|                 | R5F10FLEANA, R5F10FLEANA | A, R5F10FMCAFB, R5F10FMCAFB,  |

|                 | R5F10FMDAFB, R5F10FMDAF  | B, R5F10FMEAFB, R5F10FMEAFB   |

- Target productsD: Industrial applicationsTA = -40 to +85°CR5F10FLCDNA, R5F10FLCDNA, R5F10FLDDNA, R5F10FLDDNA, R5F10FLDDNA, R5F10FLEDNA, R5F10FMCDFB, R5F10FMCDFB, R5F10FMCDFB, R5F10FMEDFB, R5F10FMEDFB

- Cautions 1. The RL78/G1E microcontrollers have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- 2. The pins mounted depend on the product, so that refer to CHAPTER 2 PIN FUNCTIONS. In this Chapter, most of the descriptions use the case of 80-pin products as an example.

- **Notes 1.** Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD or VSS. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, LVD circuit, I/O port, on-chip pullup/pull-down resistors, and data flash rewriting.

- 2. When the HALT instruction is executed for the flash memory.

- **3.** When the high-speed on-chip oscillator is stopped.

- **4.** When the high-speed system clock is stopped.

- 5. Not including the current flowing into 12-bit interval timer, watchdog timer.

- **6.** The relationship between the operation voltage range, CPU operating frequency, and operating mode is as below.

| HS (High-speed main) mode:  | VDD = 2.7 to 5.5 V @ 1 MHz to 32 MHz             |

|-----------------------------|--------------------------------------------------|

|                             | $V_{\text{DD}}$ = 2.4 to 5.5 V @ 1 MHz to 16 MHz |

| LS (Low-speed main) mode:   | $V_{DD}$ = 1.8 to 5.5 V @ 1 MHz to 8 MHz         |

| LV (Low-voltage main) mode: | VDD = 1.6 to 5.5 V @ 1 MHz to 4 MHz              |

- **Remarks 1.** f<sub>MX</sub>: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. fin: High-speed on-chip oscillator clock frequency

- 3. The TYP. temperature condition in modes other than STOP mode is  $T_A = 25^{\circ}C$ .

#### <R> 5. 2. 4 Peripheral functions characteristics

#### **AC Timing Test Points**

#### <R> 5. 2. 4. 1 Serial array unit

#### (1) Communication between devices at same potential (UART mode) (dedicated baud rate generator output)

```

(T_A = -40 \text{ to } +85^{\circ}C, 1.6 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})

```

| Paramete    | Symbol | Conditions                                                                    | HS ' | Note 1        | LS   | lote 2        | LV   | Unit   |      |

|-------------|--------|-------------------------------------------------------------------------------|------|---------------|------|---------------|------|--------|------|

| r           |        |                                                                               | MIN. | MAX.          | MIN. | MAX.          | MIN. | MAX.   |      |

| Transfer    |        | $2.4 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$                    |      | fмск/6        |      | fмск/6        |      | fмск/6 | bps  |

| rate Note 4 |        | Theoretical value of the maximum transfer rate:<br>$f_{MCK} = f_{CLK}$ Note 6 |      | 5.3<br>Note 5 |      | 1.3           |      | 0.6    | Mbps |

|             |        | $1.8 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$                  |      | fмск/6        |      | fмск/6        |      | fмск/6 | bps  |

|             |        | Theoretical value of the maximum transfer rate:<br>$f_{MCK} = f_{CLK}$ Note 6 |      | 5.3<br>Note 5 |      | 1.3           |      | 0.6    | Mbps |

|             |        | $1.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$                  |      | fмск/6        |      | fмск/6        |      | fмск/6 | bps  |

|             |        | Theoretical value of the maximum transfer rate:<br>$f_{MCK} = f_{CLK}$ Note 6 |      | 5.3<br>Note 5 |      | 1.3<br>Note 5 |      | 0.6    | Mbps |

|             |        | $1.6 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$                  |      | _             |      | fмск/6        |      | fмск/6 | bps  |

|             |        | Theoretical value of the maximum transfer rate:<br>$f_{MCK} = f_{CLK}$ Note 6 |      | _             |      | 1.3<br>Note 5 |      | 0.6    | Mbps |

Notes 1. HS is condition of HS (high-speed main) mode.

- 2. LS is condition of LS (low-speed main) mode.

- 3. LV is condition of LV (low-voltage main) mode.

- 4. Transfer rate in the SNOOZE mode is 4800 bps.

- 5. The following conditions are required for low voltage interface.

- 2.4 V  $\leq$  VDD < 2.7 V: 2.6 Mbps max.

- $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.4 \text{ V}$ : 1.3 Mbps max.

- 1.6 V  $\leq$  VDD < 1.8 V: 0.6 Mbps max.

- **6.**  $f_{CLK}$  in each operating mode is as below.

- HS (high-speed main) mode : f<sub>CLK</sub> = 32 MHz

- LS (low-speed main) mode : f<sub>CLK</sub> = 8 MHz

- LV (low-voltage main) mode : f<sub>CLK</sub> = 4 MHz

- Caution Select the normal input buffer for the RxDq pin and the normal output mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

# <R> (10) Communication between devices at different potential (1.8 V, 2.5 V or 3 V) (simplified I<sup>2</sup>C mode) (1/2)

| Parameter     | Symbol            | Conditions                                                       | HS   | Note 1     | LS   | Note 2     | LV Note 3 |            | Unit |

|---------------|-------------------|------------------------------------------------------------------|------|------------|------|------------|-----------|------------|------|

| SCI r clock   |                   |                                                                  | MIN. | MAX.       | MIN. | MAX.       | MIN.      | MAX.       |      |

| SCLr clock    | f <sub>SCL</sub>  | $4.0 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V},$    |      | 1000       |      | 300 Note 4 |           | 300 Note 4 | kHz  |

| frequency     |                   | $2.7 \text{ V} \le \text{Vb} \le 4.0 \text{ V},$                 |      | Note 4     |      |            |           |            |      |

|               |                   | $Cb = 50 \text{ pF}, \text{Rb} = 2.7 \text{ k}\Omega$            |      |            |      |            |           |            |      |

|               |                   | $2.7 \text{ V} \leq V_{\text{DD}} \leq 4.0 \text{ V},$           |      | 1000       |      | 300 Note 4 |           | 300 Note 4 | kHz  |

|               |                   | $2.3 V \le Vb \le 2.7 V$ ,                                       |      | Note 4     |      |            |           |            |      |

|               |                   | Cb = 50 pF, Rb = 2.7 k $\Omega$                                  |      |            |      |            |           |            |      |

|               |                   | $4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$      |      | 400 Note 4 |      | 300 Note 4 |           | 300 Note 4 | kHz  |

|               |                   | $2.7 V \le Vb \le 4.0 V$ ,                                       |      |            |      |            |           |            |      |

|               |                   | $Cb = 100 \text{ pF}, \text{Rb} = 2.8 \text{ k}\Omega$           |      |            |      |            |           |            |      |

|               |                   | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 4.0 \text{ V},$      |      | 400 Note 4 |      | 300 Note 4 |           | 300 Note 4 | kHz  |

|               |                   | $2.3 V \le Vb \le 2.7 V$ ,                                       |      |            |      |            |           |            |      |

|               |                   | Cb = 100 pF, Rb = $2.7 \text{ k}\Omega$                          |      |            |      |            |           |            |      |

|               |                   | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 3.3 \text{ V},$        |      | 300 Note 4 |      | 300 Note 4 |           | 300 Note 4 | kHz  |

|               |                   | $1.6 \text{ V} \le \text{Vb} \le 2.0 \text{ V}^{\text{Note 5}},$ |      |            |      |            |           |            |      |

|               |                   | Cb = 100 pF, Rb = 5.5 k $\Omega$                                 |      |            |      |            |           |            |      |

| Hold time     | t <sub>LOW</sub>  | $4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$      | 475  |            | 1550 |            | 1550      |            | ns   |

| when SCLr = L | -2011             | $2.7 V \le Vb \le 4.0 V,$                                        |      |            |      |            |           |            |      |

|               |                   | $Cb = 50 \text{ pF}, Rb = 2.7 \text{ k}\Omega$                   |      |            |      |            |           |            |      |

|               |                   | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 4.0 \text{ V},$      | 475  |            | 1550 |            | 1550      |            | ns   |

|               |                   | $2.3 V \le Vb \le 2.7 V,$                                        |      |            |      |            |           |            |      |

|               |                   | $Cb = 50 \text{ pF}, Rb = 2.7 \text{ k}\Omega$                   |      |            |      |            |           |            |      |

|               |                   | $4.0 V \le V_{DD} \le 5.5 V$ ,                                   | 1150 |            | 1550 |            | 1550      |            | ns   |

|               |                   | $2.7 V \le Vb \le 4.0 V,$                                        |      |            |      |            |           |            |      |

|               |                   | $Cb = 100 \text{ pF}, Rb = 2.8 \text{ k}\Omega$                  |      |            |      |            |           |            |      |

|               |                   | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 4.0 \text{ V},$      | 1150 |            | 1550 |            | 1550      |            | ns   |

|               |                   | $2.3 V \le Vb \le 2.7 V$ ,                                       |      |            | 1000 |            | 1000      |            |      |

|               |                   | $Cb = 100 \text{ pF}, Rb = 2.7 \text{ k}\Omega$                  |      |            |      |            |           |            |      |

|               |                   | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 3.3 \text{ V},$        | 1550 |            | 1550 |            | 1550      |            | ns   |

|               |                   | $1.6 V \le Vb \le 2.0 V^{Note 5}$ ,                              |      |            |      |            |           |            |      |

|               |                   | $Cb = 100 \text{ pF}, Rb = 5.5 \text{ k}\Omega$                  |      |            |      |            |           |            |      |

| Hold time     | t <sub>ніGH</sub> | $4.0 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V},$      | 245  |            | 610  |            | 610       |            | ns   |

| when SCLr = H | 4 IIGH            | $2.7 V \le Vb \le 4.0 V$ ,                                       | 2.0  |            | 0.0  |            | 0.0       |            |      |

|               |                   | $Cb = 50 \text{ pF}, Rb = 2.7 \text{ k}\Omega$                   |      |            |      |            |           |            |      |

|               |                   | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 4.0 \text{ V},$      | 200  |            | 610  |            | 610       |            | ns   |

|               |                   | $2.3 V \le Vb \le 2.7 V,$                                        |      |            |      |            |           |            |      |

|               |                   | $Cb = 50 \text{ pF}, Rb = 2.7 \text{ k}\Omega$                   |      |            |      |            |           |            |      |

|               |                   | $4.0 V \le V_{DD} \le 5.5 V,$                                    | 675  |            | 610  |            | 610       |            | ns   |

|               |                   | $2.7 V \le Vb \le 4.0 V,$                                        |      |            |      |            |           |            |      |

|               |                   | $Cb = 100 \text{ pF}, Rb = 2.8 \text{ k}\Omega$                  |      |            |      |            |           |            |      |

|               |                   | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 4.0 \text{ V},$      | 600  |            | 610  |            | 610       |            | ns   |

|               |                   | $2.3 V \le Vb \le 2.7 V,$                                        |      |            | 0.0  |            | 0.0       |            |      |

|               |                   | $Cb = 100 \text{ pF}, Rb = 2.7 \text{ k}\Omega$                  |      |            |      |            |           |            |      |

|               |                   | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 3.3 \text{ V},$        | 610  |            | 610  |            | 610       |            | ns   |

|               |                   | $1.6 V \le Vb \le 2.0 V^{Note 5}$ ,                              |      |            |      |            |           |            |      |

|               |                   | $Cb = 100 \text{ pF}, Rb = 5.5 \text{ k}\Omega$                  |      |            |      |            |           |            |      |

(TA = -40 to +85°C, 1.8 V  $\leq$  VDD  $\leq$  5.5 V, Vss = 0 V) (1/2)

(Notes are listed on the next page.)

**Note** Total current flowing to internal power supply pins AV<sub>DD1</sub>, AV<sub>DD2</sub>, AV<sub>DD3</sub>, and DV<sub>DD</sub>. Current flowing through the pull-up resistor is not included. The input leakage current flowing when the level of the input pin is fixed to AV<sub>DD1</sub>, AV<sub>DD2</sub>, AV<sub>DD3</sub> or DV<sub>DD</sub>, or AGND1, AGND2, AGND3, AGND4, or DGND is included. See the table below to check the definition of those symbols of the current flowing.

|           | Symbol                  |                           | Analog function with power on |      |                         |     |     |     |      |                |                |                    |                      |  |

|-----------|-------------------------|---------------------------|-------------------------------|------|-------------------------|-----|-----|-----|------|----------------|----------------|--------------------|----------------------|--|

| Parameter |                         | Configurable<br>amplifier |                               | Gain | D/A converter           |     |     |     | Low- | High-          | Temperature    | Variable<br>output |                      |  |

|           |                         | Ch1                       | Ch2                           | Ch3  | adjustment<br>amplifier | Ch1 | Ch2 | Ch3 | Ch4  | pass<br>filter | pass<br>filter | sensor             | voltage<br>regulator |  |

|           | Im111 <sup>Note 1</sup> | ON                        | ON                            | ON   | _                       | -   | _   | ON  | -    | -              | -              | _                  | _                    |  |

|           | Im112 <sup>Note 1</sup> | ON                        | ON                            | ON   | ON                      | ON  | ON  | ON  | ON   | -              | _              | ON                 | ON                   |  |

|           | Im113 <sup>Note 1</sup> | ON                        | ON                            | ON   | _                       | ON  | ON  | ON  | ON   | ON             | ON             | ON                 | ON                   |  |

| Supply    | Im114 <sup>Note1</sup>  | ON                        | ON                            | ON   | ON                      | ON  | ON  | ON  | ON   | ON             | ON             | ON                 | ON                   |  |

| current   | Im121 <sup>Note 2</sup> | ON                        | ON                            | ON   | _                       | -   | _   | ON  | _    | -              | -              | _                  | _                    |  |

|           | Im122 Note 2            | ON                        | ON                            | ON   | ON                      | ON  | ON  | ON  | ON   | -              | _              | ON                 | ON                   |  |

|           | Im123 <sup>Note 2</sup> | ON                        | ON                            | ON   | -                       | ON  | ON  | ON  | ON   | ON             | ON             | ON                 | ON                   |  |

|           | Im124 <sup>Note 2</sup> | ON                        | ON                            | ON   | ON                      | ON  | ON  | ON  | ON   | ON             | ON             | ON                 | ON                   |  |

**Notes 1.** CC1, CC0 = 0, 0

**2.** CC1, CC0 = 1, 1

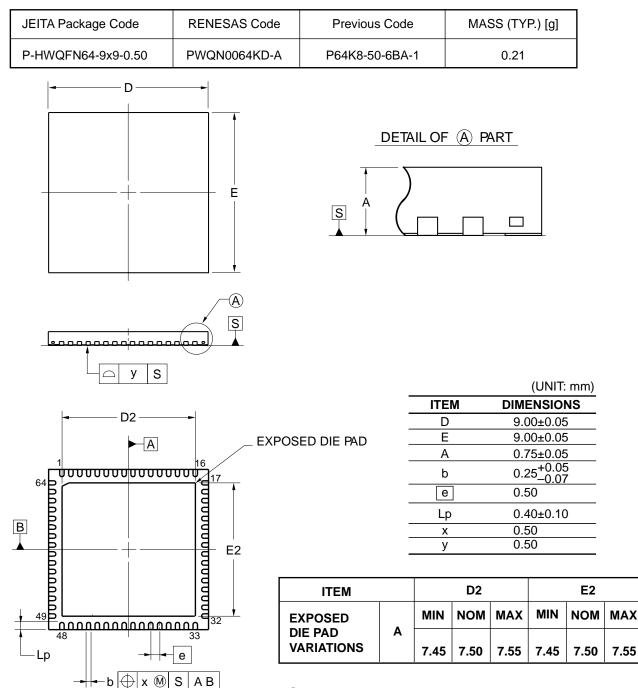

# CHAPTER 6 PACKAGE DRAWINGS

R5F10FLCANA, R5F10FLDANA, R5F10FLEANA, R5F10FLCDNA, R5F10FLDDNA, R5F10FLEDNA

# 64-PIN PLASTIC WQFN (9 x 9)

© 2012 Renesas Electronics Corporation. All rights reserved.