Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are analyzared to

### Details

| Detalls                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                    |

| Applications            | USB Microcontroller                                                         |

| Core Processor          | 8051                                                                        |

| Program Memory Type     | ROMIess                                                                     |

| Controller Series       | CY7C647xx                                                                   |

| RAM Size                | 16K x 8                                                                     |

| Interface               | I²C, USB, USART                                                             |

| Number of I/O           | 40                                                                          |

| Voltage - Supply        | 3.15V ~ 3.45V                                                               |

| Operating Temperature   | 0°C ~ 70°C                                                                  |

| Mounting Type           | Surface Mount                                                               |

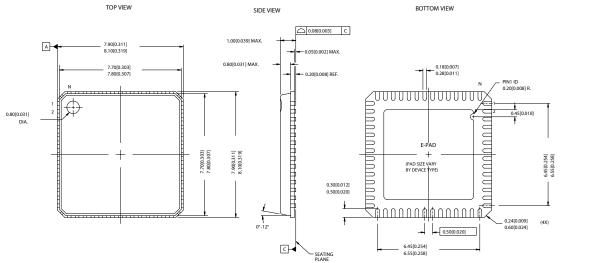

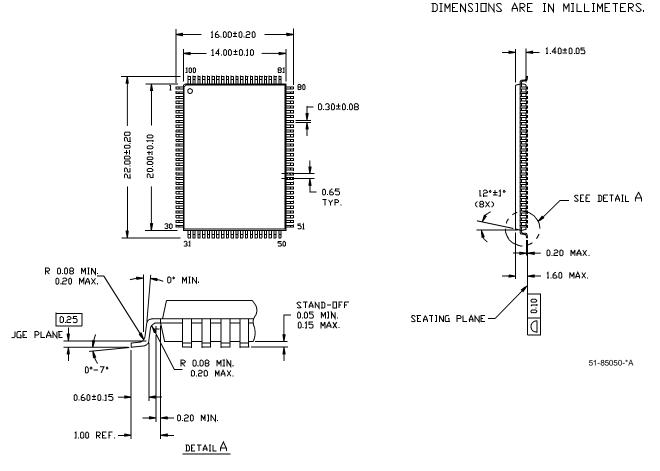

| Package / Case          | 100-LQFP                                                                    |

| Supplier Device Package | 100-TQFP (14x20)                                                            |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c64714-100axc |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 4-1.

Special Function Registers

| x | 8x    | 9x        | Ax           | Bx             | Сх     | Dx    | Ex  | Fx  |

|---|-------|-----------|--------------|----------------|--------|-------|-----|-----|

| 0 | IOA   | IOB       | IOC          | IOD            | SCON1  | PSW   | ACC | В   |

| 1 | SP    | EXIF      | INT2CLR      | IOE            | SBUF1  |       |     |     |

| 2 | DPL0  | MPAGE     | INT4CLR      | OEA            |        |       |     |     |

| 3 | DPH0  |           |              | OEB            |        |       |     |     |

| 4 | DPL1  |           |              | OEC            |        |       |     |     |

| 5 | DPH1  |           |              | OED            |        |       |     |     |

| 6 | DPS   |           |              | OEE            |        |       |     |     |

| 7 | PCON  |           |              |                |        |       |     |     |

| 8 | TCON  | SCON0     | IE           | IP             | T2CON  | EICON | EIE | EIP |

| 9 | TMOD  | SBUF0     |              |                |        |       |     |     |

| A | TL0   | AUTOPTRH1 | EP2468STAT   | EP01STAT       | RCAP2L |       |     |     |

| В | TL1   | AUTOPTRL1 | EP24FIFOFLGS | GPIFTRIG       | RCAP2H |       |     |     |

| С | TH0   | reserved  | EP68FIFOFLGS |                | TL2    |       |     |     |

| D | TH1   | AUTOPTRH2 |              | GPIFSGLDATH    | TH2    |       |     |     |

| E | CKCON | AUTOPTRL2 |              | GPIFSGLDATLX   |        |       |     |     |

| F |       | reserved  | AUTOPTRSETUP | GPIFSGLDATLNOX |        |       |     |     |

# 4.3 I<sup>2</sup>C Bus

FX1 supports the I<sup>2</sup>C bus as a master only at 100/400 KHz. SCL and SDA pins have open-drain outputs and hysteresis inputs. These signals must be pulled up to 3.3V, even if no I<sup>2</sup>C device is connected.

### 4.4 Buses

All packages: 8- or 16-bit "FIFO" bidirectional data bus, multiplexed on I/O ports B and D. 128-pin package: adds 16-bit output-only 8051 address bus, 8-bit bidirectional data bus.

### 4.5 USB Boot Methods

During the power-up sequence, internal logic checks the  $I^2C$  port for the connection of an EEPROM whose first byte is either 0xC0 or 0xC2. If found, it uses the VID/PID/DID values in the EEPROM in place of the internally stored values (0xC0), or it boot-loads the EEPROM contents into internal RAM (0xC2). If no EEPROM is detected, FX1 enumerates using internally stored descriptors. The default ID values for FX1 are VID/PID/DID (0x04B4, 0x6473, 0xAxxx where xxx=Chip revision).<sup>[2]</sup>

### Table 4-2. Default ID Values for FX1

| Default VID/PID/DID |        |                                                                          |  |  |  |  |  |

|---------------------|--------|--------------------------------------------------------------------------|--|--|--|--|--|

| Vendor ID           | 0x04B4 | Cypress Semiconductor                                                    |  |  |  |  |  |

| Product ID          | 0x6473 | EZ-USB FX1                                                               |  |  |  |  |  |

| Device<br>release   | 0xAnnn | Depends chip revision (nnn = chip<br>revision where first silicon = 001) |  |  |  |  |  |

### 4.6 ReNumeration<sup>™</sup>

Because the FX1's configuration is soft, one chip can take on the identities of multiple distinct USB devices.

When first plugged into USB, the FX1 enumerates automatically and downloads firmware and USB descriptor tables over the USB cable. Next, the FX1 enumerates again, this time as a device defined by the downloaded information. This patented two-step process, called ReNumeration<sup>™</sup>, happens instantly when the device is plugged in, with no hint that the initial download step has occurred.

Two control bits in the USBCS (USB Control and Status) register control the ReNumeration process: DISCON and RENUM. To simulate a USB disconnect, the firmware sets DISCON to 1. To reconnect, the firmware clears DISCON to 0.

Before reconnecting, the firmware sets or clears the RENUM bit to indicate whether the firmware or the Default USB Device will handle device requests over endpoint zero: if RENUM = 0, the Default USB Device will handle device requests; if RENUM = 1, the firmware will.

### 4.7 Bus-powered Applications

The FX1 fully supports bus-powered designs by enumerating with less than 100 mA as required by the USB specification.

### 4.8 Interrupt System

### 4.8.1 INT2 Interrupt Request and Enable Registers

FX1 implements an autovector feature for INT2 and INT4. There are 27 INT2 (USB) vectors, and 14 INT4 (FIFO/GPIF) vectors. See EZ-USB Technical Reference Manual (TRM) for more details.

### Note:

2. The I<sup>2</sup>C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly.

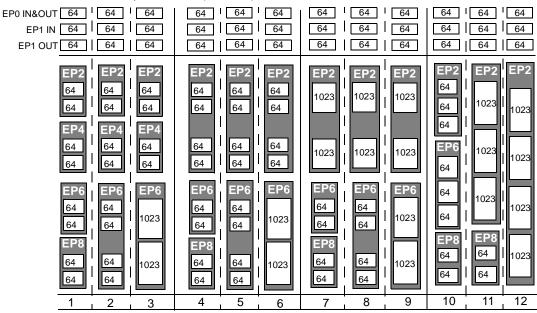

#### 4.12 Endpoint RAM

### 4.12.1 Size

- 3 × 64 bytes (Endpoints 0 and 1)

- 8 × 512 bytes (Endpoints 2, 4, 6, 8)

### 4.12.2 Organization

- EP0—Bidirectional endpoint zero, 64-byte buffer

- EP1IN, EP1OUT—64-byte buffers, bulk or interrupt

- EP2,4,6,8—Eight 512-byte buffers, bulk, interrupt, or isochronous, of which only the transfer size is available. EP4 and EP8 can be double buffered, while EP2 and 6 can be either double, triple, or quad buffered. Regardless of the physical size of the buffer, each endpoint buffer accommodates only one full-speed packet. For bulk endpoints the maximum number of bytes it can accommodate is 64, even though the physical buffer size is 512 or 1024. For an ISOCHRONOUS endpoint the maximum number of bytes it can accommodate is 1023. For endpoint configuration options, see Figure 4-5.

### 4.12.3 Setup Data Buffer

A separate 8-byte buffer at 0xE6B8-0xE6BF holds the Setup data from a CONTROL transfer.

### 4.12.4 Endpoint Configurations

Endpoints 0 and 1 are the same for every configuration. Endpoint 0 is the only CONTROL endpoint, and endpoint 1 can be either BULK or INTERRUPT. The endpoint buffers can be configured in any 1 of the 12 configurations shown in the vertical columns. In full-speed, BULK mode uses only the first 64 bytes of each buffer, even though memory exists for the allocation of the isochronous transfers in BULK mode the unused endpoint buffer space is not available for other operations. An example endpoint configuration would be:

EP2—1023 double buffered; EP6—64 guad buffered (column 8).

### 4.12.5 Default Alternate Settings

| Table 4-6. | Default | Alternate | Settings <sup>[4, 5]</sup> |

|------------|---------|-----------|----------------------------|

|------------|---------|-----------|----------------------------|

| Alternate<br>Setting | 0  | 1                | 2                | 3                |

|----------------------|----|------------------|------------------|------------------|

| ep0                  | 64 | 64               | 64               | 64               |

| ep1out               | 0  | 64 bulk          | 64 int           | 64 int           |

| ep1in                | 0  | 64 bulk          | 64 int           | 64 int           |

| ep2                  | 0  | 64 bulk out (2×) | 64 int out (2×)  | 64 iso out (2×)  |

| ep4                  | 0  | 64 bulk out (2×) | 64 bulk out (2×) | 64 bulk out (2×) |

| ep6                  | 0  | 64 bulk in (2×)  | 64 int in (2×)   | 64 iso in (2×)   |

| ep8                  | 0  | 64 bulk in (2×)  | 64 bulk in (2×)  | 64 bulk in (2×)  |

#### 4.13 **External FIFO Interface**

#### 4.13.1 Architecture

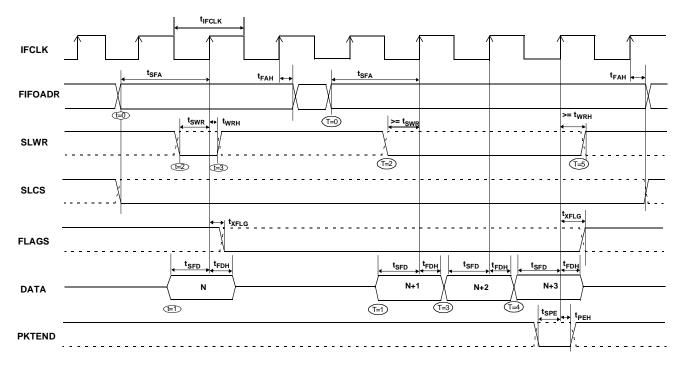

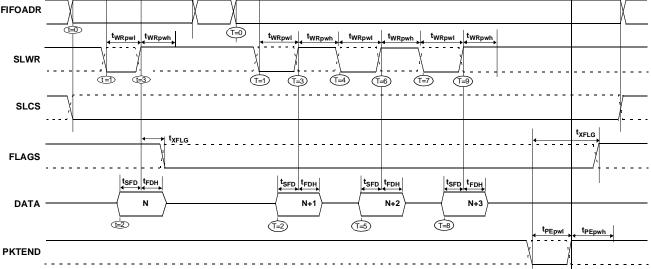

The FX1 slave FIFO architecture has eight 512-byte blocks in the endpoint RAM that directly serve as FIFO memories, and are controlled by FIFO control signals (such as IFCLK, SLCS#, SLRD, SLWR, SLOE, PKTEND, and flags). The usable size of these buffers depend on the USB transfer mode as described in Section 4.12.2.

In operation, some of the eight RAM blocks fill or empty from the SIE, while the others are connected to the I/O transfer logic. The transfer logic takes two forms, the GPIF for internally generated control signals, or the slave FIFO interface for externally controlled transfers.

### 4.13.2 Master/Slave Control Signals

The FX1 endpoint FIFOS are implemented as eight physically distinct 256x16 RAM blocks. The 8051/SIE can switch any of the RAM blocks between two domains, the USB (SIE) domain and the 8051-I/O Unit domain. This switching is done virtually

Figure 4-5. Endpoint Configuration

### Notes:

- "0" means "not implemented." "2x" means "double buffered."

- 5

instantaneously, giving essentially zero transfer time between "USB FIFOS" and "Slave FIFOS." Since they are physically the same memory, no bytes are actually transferred between buffers.

At any given time, some RAM blocks are filling/emptying with USB data under SIE control, while other RAM blocks are available to the 8051 and/or the I/O control unit. The RAM blocks operate as single-port in the USB domain, and dualport in the 8051-I/O domain. The blocks can be configured as single, double, triple, or quad buffered as previously shown.

The I/O control unit implements either an internal-master (M for master) or external-master (S for Slave) interface.

In Master (M) mode, the GPIF internally controls FIFOADR[1..0] to select a FIFO. The RDY pins (two in the 56pin package, six in the 100-pin and 128-pin packages) can be used as flag inputs from an external FIFO or other logic if desired. The GPIF can be run from either an internally derived clock or externally supplied clock (IFCLK), at a rate that transfers data up to 96 Megabytes/s (48-MHz IFCLK with 16bit interface).

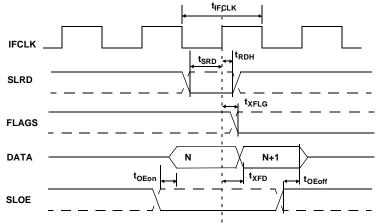

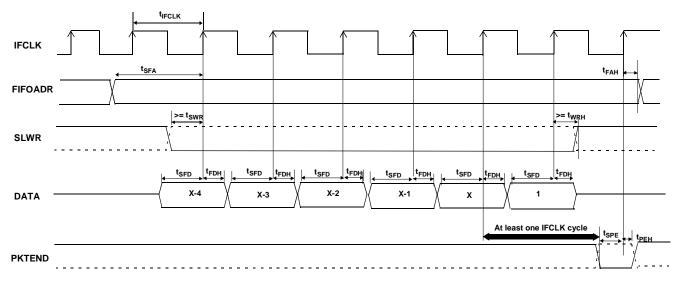

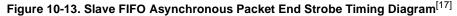

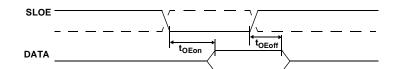

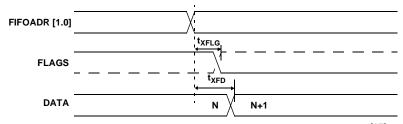

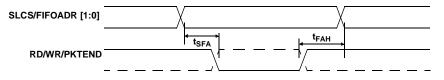

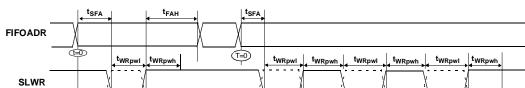

In Slave (S) mode, the FX1 accepts either an internally derived clock or externally supplied clock (IFCLK, max. frequency 48 MHz) and SLCS#, SLRD, SLWR, SLOE, PKTEND signals from external logic. When using an external IFCLK, the external clock must be present before switching to the external clock with the IFCLKSRC bit. Each endpoint can individually be selected for byte or word operation by an internal configuration bit, and a Slave FIFO Output Enable signal SLOE enables data of the selected width. External logic must insure that the output enable signal is inactive when writing data to a slave FIFO. The slave interface can also operate asynchronously, where the SLRD and SLWR signals act directly as strobes, rather than a clock qualifier as in synchronous mode. The signals SLRD, SLWR, SLOE and PKTEND are gated by the signal SLCS#.

### 4.13.3 GPIF and FIFO Clock Rates

An 8051 register bit selects one of two frequencies for the internally supplied interface clock: 30 MHz and 48 MHz. Alternatively, an externally supplied clock of 5 MHz–48 MHz feeding the IFCLK pin can be used as the interface clock. IFCLK can be configured to function as an output clock when the GPIF and FIFOs are internally clocked. An output enable bit in the IFCONFIG register turns this clock output off, if desired. Another bit within the IFCONFIG register will invert the IFCLK signal whether internally or externally sourced.

### 4.14 GPIF

The GPIF is a flexible 8- or 16-bit parallel interface driven by a user-programmable finite state machine. It allows the CY7C64713/4 to perform local bus mastering, and can implement a wide variety of protocols such as ATA interface, printer parallel port, and Utopia.

The GPIF has six programmable control outputs (CTL), nine address outputs (GPIFADRx), and six general-purpose ready inputs (RDY). The data bus width can be 8 or 16 bits. Each GPIF vector defines the state of the control outputs, and determines what state a ready input (or multiple inputs) must be before proceeding. The GPIF vector can be programmed to advance a FIFO to the next data value, advance an address, etc. A sequence of the GPIF vectors make up a single waveform that will be executed to perform the desired data move between the FX1 and the external device.

### 4.14.1 Six Control OUT Signals

The 100- and 128-pin packages bring out all six Control Output pins (CTL0-CTL5). The 8051 programs the GPIF unit to define the CTL waveforms. The 56-pin package brings out three of these signals, CTL0–CTL2. CTLx waveform edges can be programmed to make transitions as fast as once per clock (20.8 ns using a 48-MHz clock).

### 4.14.2 Six Ready IN Signals

The 100- and 128-pin packages bring out all six Ready inputs (RDY0–RDY5). The 8051 programs the GPIF unit to test the RDY pins for GPIF branching. The 56-pin package brings out two of these signals, RDY0–1.

### 4.14.3 Nine GPIF Address OUT Signals

Nine GPIF address lines are available in the 100- and 128-pin packages, GPIFADR[8..0]. The GPIF address lines allow indexing through up to a 512-byte block of RAM. If more address lines are needed, I/O port pins can be used.

### 4.14.4 Long Transfer Mode

In master mode, the 8051 appropriately sets GPIF transaction count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers of up to  $2^{32}$  transactions. The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions complete. The GPIF decrements the value in these registers to represent the current status of the transaction.

### 4.15 ECC Generation

The EZ-USB FX1 can calculate ECCs (Error-Correcting Codes) on data that passes across its GPIF or Slave FIFO interfaces. There are two ECC configurations: Two ECCs, each calculated over 256 bytes (SmartMedia<sup>™</sup> Standard); and one ECC calculated over 512 bytes.

The ECC can correct any one-bit error or detect any two-bit error.

**Note:** To use the ECC logic, the GPIF or Slave FIFO interface must be configured for byte-wide operation.

### 4.15.1 ECC Implementation

The two ECC configurations are selected by the ECCM bit:

### 4.15.1.1 ECCM = 0

Two 3-byte ECCs, each calculated over a 256-byte block of data. This configuration conforms to the SmartMedia Standard.

Write any value to ECCRESET, then pass data across the GPIF or Slave FIFO interface. The ECC for the first 256 bytes of data will be calculated and stored in ECC1. The ECC for the next 256 bytes will be stored in ECC2. After the second ECC is calculated, the values in the ECCx registers will not change until ECCRESET is written again, even if more data is subsequently passed across the interface.

### 4.15.1.2 ECCM = 1

One 3-byte ECC calculated over a 512-byte block of data.

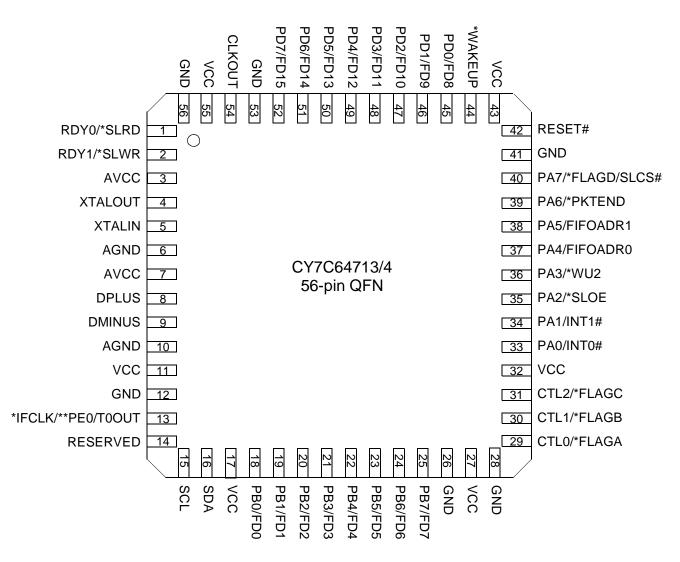

\* denotes programmable polarity

# Table 5-1. FX1 Pin Definitions (continued)<sup>[8]</sup>

| 128<br>TQFP | 100<br>TQFP | 56<br>QFN | Name               | Туре   | Default    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-------------|-----------|--------------------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 99          | 77          | 42        | RESET#             | Input  | N/A        | Active LOW Reset. Resets the entire chip. See section 4.9 "Reset and Wakeup" on page 5 for more details.                                                                                                                                                                                                                                                                                                                                                                                         |

| 35          |             |           | EA                 | Input  | N/A        | <b>External Access</b> . This pin determines where the 8051 fetches code between addresses 0x0000 and 0x3FFF. If EA = 0 the 8051 fetches this code from its internal RAM. IF EA = 1 the 8051 fetches this code from external memory.                                                                                                                                                                                                                                                             |

| 12          | 11          | 5         | XTALIN             | Input  | N/A        | <b>Crystal Input</b> . Connect this signal to a 24-MHz parallel-resonant, funda-<br>mental mode crystal and load capacitor to GND.<br>It is also correct to drive XTALIN with an external 24 MHz square wave<br>derived from another clock source. When driving from an external source,<br>the driving signal should be a 3.3V square wave.                                                                                                                                                     |

| 11          | 10          | 4         | XTALOUT            | Output | N/A        | <b>Crystal Output</b> . Connect this signal to a 24-MHz parallel-resonant, funda-<br>mental mode crystal and load capacitor to GND.<br>If an external clock is used to drive XTALIN, leave this pin open.                                                                                                                                                                                                                                                                                        |

| 1           | 100         | 54        | CLKOUT             | O/Z    | 12<br>MHz  | <b>CLKOUT:</b> 12-, 24- or 48-MHz clock, phase locked to the 24-MHz input clock.<br>The 8051 defaults to 12-MHz operation. The 8051 may three-state this output by setting CPUCS.1 = 1.                                                                                                                                                                                                                                                                                                          |

| Port A      |             |           |                    |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 82          | 67          | 33        | PA0 or<br>INT0#    | I/O/Z  | І<br>(РА0) | Multiplexed pin whose function is selected by PORTACFG.0<br><b>PA0</b> is a bidirectional IO port pin.<br><b>INT0#</b> is the active-LOW 8051 INT0 interrupt input signal, which is either<br>edge triggered (IT0 = 1) or level triggered (IT0 = 0).                                                                                                                                                                                                                                             |

| 83          | 68          | 34        | PA1 or<br>INT1#    | I/O/Z  | І<br>(РА1) | Multiplexed pin whose function is selected by:<br>PORTACFG.1<br><b>PA1</b> is a bidirectional IO port pin.<br><b>INT1#</b> is the active-LOW 8051 INT1 interrupt input signal, which is either<br>edge triggered (IT1 = 1) or level triggered (IT1 = 0).                                                                                                                                                                                                                                         |

| 84          | 69          | 35        | PA2 or<br>SLOE     | I/O/Z  | I<br>(PA2) | Multiplexed pin whose function is selected by two bits:<br>IFCONFIG[1:0].<br><b>PA2</b> is a bidirectional IO port pin.<br><b>SLOE</b> is an input-only output enable with programmable polarity (FIFOPIN-<br>POLAR.4) for the slave FIFOs connected to FD[70] or FD[150].                                                                                                                                                                                                                       |

| 85          | 70          | 36        | PA3 or<br>WU2      | I/O/Z  | I<br>(PA3) | Multiplexed pin whose function is selected by:<br>WAKEUP.7 and OEA.3<br><b>PA3</b> is a bidirectional I/O port pin.<br><b>WU2</b> is an alternate source for <b>USB Wakeup</b> , enabled by WU2EN bit<br>(WAKEUP.1) and polarity set by WU2POL (WAKEUP.4). If the 8051 is in<br>suspend and WU2EN = 1, a transition on this pin starts up the oscillator and<br>interrupts the 8051 to allow it to exit the suspend mode. Asserting this pin<br>inhibits the chip from suspending, if WU2EN = 1. |

| 89          | 71          | 37        | PA4 or<br>FIFOADR0 | I/O/Z  | I<br>(PA4) | Multiplexed pin whose function is selected by:<br>IFCONFIG[10].<br><b>PA4</b> is a bidirectional I/O port pin.<br><b>FIFOADR0</b> is an input-only address select for the slave FIFOs connected<br>to FD[70] or FD[150].                                                                                                                                                                                                                                                                         |

| 90          | 72          | 38        | PA5 or<br>FIFOADR1 | I/O/Z  | l<br>(PA5) | Multiplexed pin whose function is selected by:<br>IFCONFIG[10].<br><b>PA5</b> is a bidirectional I/O port pin.<br><b>FIFOADR1</b> is an input-only address select for the slave FIFOs connected<br>to FD[70] or FD[150].                                                                                                                                                                                                                                                                         |

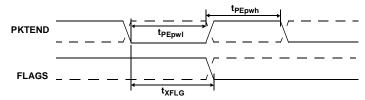

| 91          | 73          | 39        | PA6 or<br>PKTEND   | I/O/Z  | I<br>(PA6) | Multiplexed pin whose function is selected by the IFCONFIG[1:0] bits.<br><b>PA6</b> is a bidirectional I/O port pin.<br><b>PKTEND</b> is an input used to commit the FIFO packet data to the endpoint<br>and whose polarity is programmable via FIFOPINPOLAR.5.                                                                                                                                                                                                                                  |

# Table 5-1. FX1 Pin Definitions (continued)<sup>[8]</sup>

| 128<br>TQFP | 100<br>TQFP | 56<br>QFN | Name               | Туре  | Default    | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------|-----------|--------------------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 77          | 62          |           | PC5 or<br>GPIFADR5 | I/O/Z | l<br>(PC5) | Multiplexed pin whose function is selected by PORTCCFG.5<br>PC5 is a bidirectional I/O port pin.<br>GPIFADR5 is a GPIF address output pin.                                                                                                                                                                                                                                                          |

| 78          | 63          |           | PC6 or<br>GPIFADR6 | I/O/Z | l<br>(PC6) | Multiplexed pin whose function is selected by PORTCCFG.6<br>PC6 is a bidirectional I/O port pin.<br>GPIFADR6 is a GPIF address output pin.                                                                                                                                                                                                                                                          |

| 79          | 64          |           | PC7 or<br>GPIFADR7 | I/O/Z | l<br>(PC7) | Multiplexed pin whose function is selected by PORTCCFG.7<br><b>PC7</b> is a bidirectional I/O port pin.<br><b>GPIFADR7</b> is a GPIF address output pin.                                                                                                                                                                                                                                            |

| PORT        | D           |           |                    |       |            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 102         | 80          | 45        | PD0 or<br>FD[8]    | I/O/Z | l<br>(PD0) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[8]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                           |

| 103         | 81          | 46        | PD1 or<br>FD[9]    | I/O/Z | l<br>(PD1) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[9]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                           |

| 104         | 82          | 47        | PD2 or<br>FD[10]   | I/O/Z | l<br>(PD2) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[10]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                          |

| 105         | 83          | 48        | PD3 or<br>FD[11]   | I/O/Z | l<br>(PD3) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[11]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                          |

| 121         | 95          | 49        | PD4 or<br>FD[12]   | I/O/Z | l<br>(PD4) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[12]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                          |

| 122         | 96          | 50        | PD5 or<br>FD[13]   | I/O/Z | l<br>(PD5) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[13]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                          |

| 123         | 97          | 51        | PD6 or<br>FD[14]   | I/O/Z | l<br>(PD6) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[14]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                          |

| 124         | 98          | 52        | PD7 or<br>FD[15]   | I/O/Z | l<br>(PD7) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[15]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                          |

| Port E      |             |           |                    |       |            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 108         | 86          |           | PE0 or<br>T0OUT    | I/O/Z | l<br>(PE0) | Multiplexed pin whose function is selected by the PORTECFG.0 bit.<br><b>PE0</b> is a bidirectional I/O port pin.<br><b>TOOUT</b> is an active-HIGH signal from 8051 Timer-counter0. TOOUT outputs<br>a high level for one CLKOUT clock cycle when Timer0 overflows. If Timer0<br>is operated in Mode 3 (two separate timer/counters), TOOUT is active when<br>the low byte timer/counter overflows. |

| 109         | 87          |           | PE1 or<br>T1OUT    | I/O/Z | I<br>(PE1) | Multiplexed pin whose function is selected by the PORTECFG.1 bit.<br><b>PE1</b> is a bidirectional I/O port pin.<br><b>T1OUT</b> is an active-HIGH signal from 8051 Timer-counter1. T1OUT outputs<br>a high level for one CLKOUT clock cycle when Timer1 overflows. If Timer1<br>is operated in Mode 3 (two separate timer/counters), T1OUT is active when<br>the low byte timer/counter overflows. |

| 110         | 88          |           | PE2 or<br>T2OUT    | I/O/Z | l<br>(PE2) | Multiplexed pin whose function is selected by the PORTECFG.2 bit.<br><b>PE2</b> is a bidirectional I/O port pin.<br><b>T2OUT</b> is the active-HIGH output signal from 8051 Timer2. T2OUT is active<br>(HIGH) for one clock cycle when Timer/Counter 2 overflows.                                                                                                                                   |

# Table 5-1. FX1 Pin Definitions (continued)<sup>[8]</sup>

| 128<br>TQFP | 100<br>TQFP | 56<br>QFN | Name     | Туре    | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------|-----------|----------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32          | 26          | 13        | IFCLK    | I/O/Z   | Z       | Interface Clock, used for synchronously clocking data into or out of the slave FIFOs. IFCLK also serves as a timing reference for all slave FIFO control signals and GPIF. When internal clocking is used (IFCONFIG.7 = 1) the IFCLK pin can be configured to output 30/48 MHz by bits IFCONFIG.5 and IFCONFIG.6. IFCLK may be inverted, whether internally or externally sourced, by setting the bit IFCONFIG.4 = 1. |

| 28          | 22          |           | INT4     | Input   | N/A     | <b>INT4</b> is the 8051 INT4 interrupt request input signal. The INT4 pin is edge-<br>sensitive, active HIGH.                                                                                                                                                                                                                                                                                                         |

| 106         | 84          |           | INT5#    | Input   | N/A     | <b>INT5#</b> is the 8051 INT5 interrupt request input signal. The INT5 pin is edge-<br>sensitive, active LOW.                                                                                                                                                                                                                                                                                                         |

| 31          | 25          |           | T2       | Input   | N/A     | <b>T2</b> is the active-HIGH T2 input signal to 8051 Timer2, which provides the input to Timer2 when $C/T2 = 1$ . When $C/T2 = 0$ , Timer2 does not use this pin.                                                                                                                                                                                                                                                     |

| 30          | 24          |           | T1       | Input   | N/A     | <b>T1</b> is the active-HIGH T1 signal for 8051 Timer1, which provides the input to Timer1 when C/T1 is 1. When C/T1 is 0, Timer1 does not use this bit.                                                                                                                                                                                                                                                              |

| 29          | 23          |           | Т0       | Input   | N/A     | <b>T0</b> is the active-HIGH T0 signal for 8051 Timer0, which provides the input to Timer0 when C/T0 is 1. When C/T0 is 0, Timer0 does not use this bit.                                                                                                                                                                                                                                                              |

| 53          | 43          |           | RXD1     | Input   | N/A     | <b>RXD1</b> is an active-HIGH input signal for 8051 UART1, which provides data to the UART in all modes.                                                                                                                                                                                                                                                                                                              |

| 52          | 42          |           | TXD1     | Output  | Н       | <b>TXD1</b> is an active-HIGH output pin from 8051 UART1, which provides the output clock in sync mode, and the output data in async mode.                                                                                                                                                                                                                                                                            |

| 51          | 41          |           | RXD0     | Input   | N/A     | <b>RXD0</b> is the active-HIGH RXD0 input to 8051 UART0, which provides data to the UART in all modes.                                                                                                                                                                                                                                                                                                                |

| 50          | 40          |           | TXD0     | Output  | Н       | <b>TXD0</b> is the active-HIGH TXD0 output from 8051 UART0, which provides the output clock in sync mode, and the output data in async mode.                                                                                                                                                                                                                                                                          |

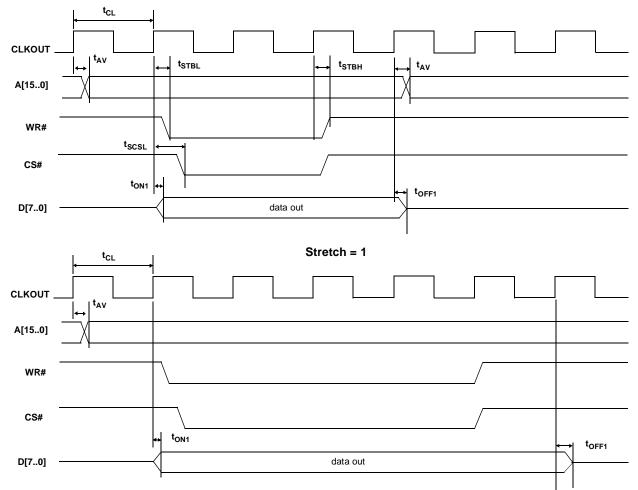

| 42          |             |           | CS#      | Output  | Н       | CS# is the active-LOW chip select for external memory.                                                                                                                                                                                                                                                                                                                                                                |

| 41          | 32          |           | WR#      | Output  | Н       | WR# is the active-LOW write strobe output for external memory.                                                                                                                                                                                                                                                                                                                                                        |

| 40          | 31          |           | RD#      | Output  | Н       | RD# is the active-LOW read strobe output for external memory.                                                                                                                                                                                                                                                                                                                                                         |

| 38          |             |           | OE#      | Output  | Н       | OE# is the active-LOW output enable for external memory.                                                                                                                                                                                                                                                                                                                                                              |

| 33          | 27          | 14        | Reserved | Input   | N/A     | Reserved. Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                          |

|             |             |           |          | -<br>T- |         |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 101         | 79          | 44        | WAKEUP   | Input   | N/A     | <b>USB Wakeup</b> . If the 8051 is in suspend, asserting this pin starts up the oscillator and interrupts the 8051 to allow it to exit the suspend mode.<br>Holding WAKEUP asserted inhibits the EZ-USB FX1 chip from suspending.<br>This pin has programmable polarity (WAKEUP.4).                                                                                                                                   |

| 36          | 29          | 15        | SCL      | OD      | Z       | <b>Clock</b> for the $I^2C$ interface. Connect to VCC with a 2.2K resistor, even if no $I^2C$ peripheral is attached.                                                                                                                                                                                                                                                                                                 |

| 37          | 30          | 16        | SDA      | OD      | Z       | Data for I <sup>2</sup> C interface. Connect to VCC with a 2.2K resistor, even if no I <sup>2</sup> C peripheral is attached.                                                                                                                                                                                                                                                                                         |

|             |             |           |          |         |         |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2           | 1           | 55        | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

| 26          | 20          | 11        | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

| 43          | 33          | 17        | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

| 48          | 38          |           | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

| 64          | 49          | 27        | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

| 68          | 53          |           | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

| 81          | 66          | 32        | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

| 100         | 78          | 43        | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

| 107         | 85          |           | VCC      | Power   | N/A     | VCC. Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                                                    |

# 6.0 Register Summary

FX1 register bit definitions are described in the EZ-USB TRM in greater detail.

### Table 6-1. FX1 Register Summary

| E400 1                                                   |                                 |                                        |                                                                                                                      |                                   |                           |                           |                      |                      |                              |                     |                     | -                                |             |

|----------------------------------------------------------|---------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------|---------------------------|----------------------|----------------------|------------------------------|---------------------|---------------------|----------------------------------|-------------|

|                                                          | Size                            | Name<br>GPIF Waveform Merr             | Description                                                                                                          | b7                                | b6                        | b5                        | b4                   | b3                   | b2                           | b1                  | b0                  | Default                          | Access      |

|                                                          | 128                             | GPIF Waveform Men<br>WAVEDATA          | OPIF Waveform                                                                                                        | D7                                | D6                        | D5                        | D4                   | D3                   | D2                           | D1                  | D0                  | xxxxxxx                          | RW          |

|                                                          |                                 |                                        | Descriptor 0, 1, 2, 3 data                                                                                           | 07                                | 00                        | 05                        | D4                   | 03                   | Dz                           |                     | DU                  | ******                           | R VV        |

| E480 1                                                   | 128                             | reserved<br>GENERAL CONFIGU            |                                                                                                                      |                                   |                           |                           |                      |                      |                              |                     |                     |                                  |             |

| E600 1                                                   | 1                               | GENERAL CONFIGU                        | CPU Control & Status                                                                                                 | 0                                 | 0                         | PORTCSTB                  | CLKSPD1              | CLKSPD0              | CLKINV                       | CLKOE               | 8051RES             | 00000010                         | rrbbbbbr    |

| E600 1                                                   | 1                               | IFCONFIG                               | Interface Configuration                                                                                              | IFCLKSRC                          | 0<br>3048MHZ              | IFCLKOE                   | IFCLKPOL             | ASYNC                | GSTATE                       | IFCFG1              | IFCFG0              | 100000000                        |             |

|                                                          |                                 | PINFLAGSAB <sup>[9]</sup>              | (Ports, GPIF, slave FIFOs)<br>Slave FIFO FLAGA and                                                                   |                                   | FLAGB2                    | FLAGB1                    | FLAGB0               |                      | FLAGA2                       |                     |                     |                                  |             |

| E602 1                                                   |                                 |                                        | FLAGB Pin Configuration                                                                                              | FLAGB3                            | -                         |                           |                      | FLAGA3               | -                            | FLAGA1              | FLAGA0              | 00000000                         |             |

| E603 1                                                   | 1                               | PINFLAGSCD <sup>[9]</sup>              | Slave FIFO FLAGC and<br>FLAGD Pin Configuration                                                                      | FLAGD3                            | FLAGD2                    | FLAGD1                    | FLAGD0               | FLAGC3               | FLAGC2                       | FLAGC1              | FLAGC0              | 00000000                         | RW          |

| E604 1                                                   | 1                               | FIFORESET <sup>[9]</sup>               | Restore FIFOS to default state                                                                                       | NAKALL                            | 0                         | 0                         | 0                    | EP3                  | EP2                          | EP1                 | EP0                 | XXXXXXXX                         | W           |

| E605 1                                                   | 1                               | BREAKPT                                | Breakpoint Control                                                                                                   | 0                                 | 0                         | 0                         | 0                    | BREAK                | BPPULSE                      | BPEN                | 0                   | 00000000                         | rrrrbbbr    |

| E606 1                                                   | 1                               | BPADDRH                                | Breakpoint Address H                                                                                                 | A15                               | A14                       | A13                       | A12                  | A11                  | A10                          | A9                  | A8                  | XXXXXXXX                         | RW          |

| E607 1                                                   | 1                               | BPADDRL                                | Breakpoint Address L                                                                                                 | A7                                | A6                        | A5                        | A4                   | A3                   | A2                           | A1                  | A0                  | XXXXXXXX                         | RW          |

| E608 1                                                   | 1                               | UART230                                | 230 Kbaud internally<br>generated ref. clock                                                                         | 0                                 | 0                         | 0                         | 0                    | 0                    | 0                            | 230UART1            | 230UART0            | 00000000                         | rrrrrbb     |

| E609 1                                                   | 1                               | FIFOPINPOLAR <sup>[9]</sup>            | Slave FIFO Interface pins                                                                                            | 0                                 | 0                         | PKTEND                    | SLOE                 | SLRD                 | SLWR                         | EF                  | FF                  | 00000000                         | rrbbbbbb    |

| E60A 1                                                   | 1                               | REVID                                  | Chip Revision                                                                                                        | rv7                               | rv6                       | rv5                       | rv4                  | rv3                  | rv2                          | rv1                 | rv0                 | RevA<br>00000001                 | R           |

| E60B 1                                                   | 1                               | REVCTL <sup>[9]</sup>                  | Chip Revision Control                                                                                                | 0                                 | 0                         | 0                         | 0                    | 0                    | 0                            | dyn_out             | enh_pkt             | 00000000                         | rrrrrbb     |

| -000                                                     |                                 | UDMA                                   | Chip Revision Control                                                                                                | 0                                 | 0                         | 0                         | 0                    | 0                    | 0                            | uyn_out             | епп_ркс             | 00000000                         |             |

| E60C 1                                                   | 1                               | GPIFHOLDAMOUNT                         | MSTB Hold Time                                                                                                       | 0                                 | 0                         | 0                         | 0                    | 0                    | 0                            | HOLDTIMF1           | HOLDTIME0           | 00000000                         | rrrrrbb     |

|                                                          | 3                               | reserved                               | (for UDMA)                                                                                                           | -                                 | -                         | -                         | -                    | -                    | -                            |                     |                     |                                  |             |

|                                                          | 5                               | 10301700                               | I                                                                                                                    |                                   |                           |                           |                      |                      |                              |                     |                     |                                  |             |

|                                                          |                                 | ENDPOINT CONFIG                        | URATION                                                                                                              |                                   |                           |                           |                      |                      |                              |                     |                     |                                  |             |

| E610 1                                                   | 1                               | EP1OUTCFG                              | Endpoint 1-OUT<br>Configuration                                                                                      | VALID                             | 0                         | TYPE1                     | TYPE0                | 0                    | 0                            | 0                   | 0                   | 10100000                         | brbbrrrr    |

| E611 1                                                   | 1                               | EP1INCFG                               | Endpoint 1-IN<br>Configuration                                                                                       | VALID                             | 0                         | TYPE1                     | TYPE0                | 0                    | 0                            | 0                   | 0                   | 10100000                         | brbbrrrr    |

| E612 1                                                   | 1                               | EP2CFG                                 | Endpoint 2 Configuration                                                                                             | VALID                             | DIR                       | TYPE1                     | TYPE0                | SIZE                 | 0                            | BUF1                | BUF0                | 10100010                         | bbbbbrbb    |

| E613 1                                                   | 1                               | EP4CFG                                 | Endpoint 4 Configuration                                                                                             | VALID                             | DIR                       | TYPE1                     | TYPE0                | 0                    | 0                            | 0                   | 0                   | 10100000                         | bbbbrrrr    |

| E614 1                                                   | 1                               | EP6CFG                                 | Endpoint 6 Configuration                                                                                             | VALID                             | DIR                       | TYPE1                     | TYPE0                | SIZE                 | 0                            | BUF1                | BUF0                | 11100010                         | bbbbbrbb    |

| E615 1                                                   | 1                               | EP8CFG                                 | Endpoint 8 Configuration                                                                                             | VALID                             | DIR                       | TYPE1                     | TYPE0                | 0                    | 0                            | 0                   | 0                   | 11100000                         | bbbbrrrr    |

| 2                                                        | 2                               | reserved                               |                                                                                                                      |                                   |                           |                           |                      |                      |                              |                     |                     |                                  |             |

| E618 1                                                   | 1                               | EP2FIFOCFG <sup>[9]</sup>              | Endpoint 2 / slave FIFO<br>configuration                                                                             | 0                                 | INFM1                     | OEP1                      | AUTOOUT              | AUTOIN               | ZEROLENIN                    | 0                   | WORDWIDE            | 00000101                         | rbbbbbrb    |

| E619 1                                                   | 1                               | EP4FIFOCFG <sup>[9]</sup>              | Endpoint 4 / slave FIFO configuration                                                                                | 0                                 | INFM1                     | OEP1                      | AUTOOUT              | AUTOIN               | ZEROLENIN                    | 0                   | WORDWIDE            | 00000101                         | rbbbbbrb    |

| E61A 1                                                   | 1                               | EP6FIFOCFG <sup>[9]</sup>              | Endpoint 6 / slave FIFO configuration                                                                                | 0                                 | INFM1                     | OEP1                      | AUTOOUT              | AUTOIN               | ZEROLENIN                    | 0                   | WORDWIDE            | 00000101                         | rbbbbbrb    |

| E61B 1                                                   | 1                               | EP8FIFOCFG <sup>[9]</sup>              | Endpoint 8 / slave FIFO<br>configuration                                                                             | 0                                 | INFM1                     | OEP1                      | AUTOOUT              | AUTOIN               | ZEROLENIN                    | 0                   | WORDWIDE            | 00000101                         | rbbbbbrb    |

| E61C 4                                                   | 4                               | reserved                               | configuration                                                                                                        |                                   |                           |                           |                      |                      |                              |                     |                     |                                  |             |

| E620 1                                                   | 1                               | EP2AUTOINLENH <sup>[9]</sup>           | Endpoint 2 AUTOIN<br>Packet Length H                                                                                 | 0                                 | 0                         | 0                         | 0                    | 0                    | PL10                         | PL9                 | PL8                 | 00000010                         | rrrrbbb     |

| E621 1                                                   | 1                               | EP2AUTOINLENL <sup>[9]</sup>           | Endpoint 2 AUTOIN                                                                                                    | PL7                               | PL6                       | PL5                       | PL4                  | PL3                  | PL2                          | PL1                 | PL0                 | 00000000                         | RW          |

| E622 1                                                   | 1                               | EP4AUTOINLENH <sup>[9]</sup>           | Packet Length L<br>Endpoint 4 AUTOIN                                                                                 | 0                                 | 0                         | 0                         | 0                    | 0                    | 0                            | PL9                 | PL8                 | 00000010                         | rrrrrbb     |

| E623 1                                                   | 1                               | EP4AUTOINLENL <sup>[9]</sup>           | Packet Length H<br>Endpoint 4 AUTOIN                                                                                 | PL7                               | PL6                       | PL5                       | PL4                  | PL3                  | PL2                          | PL1                 | PL0                 | 00000000                         | RW          |

| E624 1                                                   |                                 | EP6AUTOINLENH <sup>[9]</sup>           | Packet Length L<br>Endpoint 6 AUTOIN                                                                                 | 0                                 | 0                         | 0                         | 0                    | 0                    | PL10                         | PL9                 | PL8                 | 00000010                         |             |

|                                                          |                                 | EP6AUTOINLENL <sup>[9]</sup>           | Packet Length H<br>Endpoint 6 AUTOIN                                                                                 | PL7                               | PL6                       | PL5                       | PL4                  | PL3                  | PL2                          | PL1                 |                     | 000000000                        |             |

| -625                                                     |                                 |                                        | Packet Length L                                                                                                      |                                   |                           |                           |                      |                      |                              |                     |                     |                                  |             |

| E625 1                                                   |                                 | EP8AUTOINLENH <sup>[9]</sup>           | Endpoint 8 AUTOIN                                                                                                    | 0                                 | 0                         | 0                         | 0                    | 0                    | 0                            | PL9                 | PL8                 | 00000010                         |             |

| E626 1                                                   |                                 |                                        | Packet Length H                                                                                                      |                                   |                           | PL5                       | PL4                  | PL3                  | PL2                          | PL1                 | PL0                 | 00000000                         | RW          |

|                                                          | 1                               | EP8AUTOINLENL <sup>[9]</sup>           | Endpoint 8 AUTOIN<br>Packet Length L                                                                                 | PL7                               | PL6                       | . 20                      |                      |                      |                              |                     |                     |                                  |             |

| E626 1                                                   | 1                               | EP8AUTOINLENL <sup>[9]</sup><br>ECCCFG | Endpoint 8 AUTOIN                                                                                                    | PL7<br>0                          | PL6<br>0                  | 0                         | 0                    | 0                    | 0                            | 0                   | ECCM                | 00000000                         | rrrrrb      |

| E626 1<br>E627 1                                         | 1                               |                                        | Endpoint 8 AUTOIN<br>Packet Length L                                                                                 |                                   |                           |                           | 0<br>x               | х                    | 0<br>x                       | 0<br>x              | ECCM<br>x           | 00000000<br>00000000             |             |

| E626 1<br>E627 1<br>E628 1                               | 1<br>1<br>1<br>1                | ECCCFG<br>ECCRESET<br>ECC1B0           | Endpoint 8 AUTOIN<br>Packet Length L<br>ECC Configuration<br>ECC Reset<br>ECC1 Byte 0 Address                        | 0<br>x<br>LINE15                  |                           | 0<br>x<br>LINE13          | x<br>LINE12          | x<br>LINE11          | x<br>LINE10                  | x<br>LINE9          | ECCM<br>x<br>LINE8  |                                  |             |

| E626 1<br>E627 1<br>E628 1<br>E629 1                     | 1<br>1<br>1<br>1<br>1           | ECCCFG<br>ECCRESET<br>ECC1B0<br>ECC1B1 | Endpoint 8 AUTOIN<br>Packet Length L<br>ECC Configuration<br>ECC Reset<br>ECC1 Byte 0 Address<br>ECC1 Byte 1 Address | 0<br>x                            | 0<br>x                    | 0<br>x<br>LINE13<br>LINE5 | x<br>LINE12<br>LINE4 | x<br>LINE11<br>LINE3 | x<br>LINE10<br>LINE2         | х                   | x                   | 0000000                          | W           |

| E626 1<br>E627 1<br>E628 1<br>E629 1<br>E62A 1           | 1<br>1<br>1<br>1<br>1           | ECCCFG<br>ECCRESET<br>ECC1B0           | Endpoint 8 AUTOIN<br>Packet Length L<br>ECC Configuration<br>ECC Reset<br>ECC1 Byte 0 Address                        | 0<br>x<br>LINE15<br>LINE7<br>COL5 | 0<br>x<br>LINE14          | 0<br>x<br>LINE13          | x<br>LINE12          | x<br>LINE11          | x<br>LINE10<br>LINE2<br>COL0 | x<br>LINE9          | x<br>LINE8          | 00000000<br>11111111             | W<br>R      |

| E626 1<br>E627 1<br>E628 1<br>E629 1<br>E62A 1<br>E62B 1 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | ECCCFG<br>ECCRESET<br>ECC1B0<br>ECC1B1 | Endpoint 8 AUTOIN<br>Packet Length L<br>ECC Configuration<br>ECC Reset<br>ECC1 Byte 0 Address<br>ECC1 Byte 1 Address | 0<br>x<br>LINE15<br>LINE7         | 0<br>x<br>LINE14<br>LINE6 | 0<br>x<br>LINE13<br>LINE5 | x<br>LINE12<br>LINE4 | x<br>LINE11<br>LINE3 | x<br>LINE10<br>LINE2         | x<br>LINE9<br>LINE1 | x<br>LINE8<br>LINE0 | 00000000<br>11111111<br>11111111 | W<br>R<br>R |

9. Read and writes to these register may require synchronization delay, see Technical Reference Manual for "Synchronization Delay."

## Table 6-1. FX1 Register Summary (continued)