# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12X                                                                  |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI               |

| Peripherals                | LCD, Motor control PWM, POR, PWM, WDT                                   |

| Number of I/O              | 76                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 8K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912xhy128f0vll |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 1 Device Overview MC9S12XHY-Family

# 1.1 Introduction

The MC9S12XHY family is an optimized, automotive, 16-bit microcontroller product line that is specifically designed for entry level instrument clusters. This family also services generic automotive applications requiring CAN, LCD, Motor driver control or LIN/SAE J2602. Typical examples of these applications include instrument clusters for automobiles and 2 or 3 wheelers, HVAC displays, general purpose motor control and body controllers.

The MC9S12XHY family uses many of the same features found on the MC9S12XS family and MC9S12HY/HA family, including error correction code (ECC) on flash memory, a separate data-flash module for diagnostic or data storage, a fast analog-to-digital converter (ATD) and a frequency modulated phase locked loop (IPLL) that improves the EMC performance. The MC9S12XHY family features a 40x4 liquid crystal display (LCD) controller/driver and a motor pulse width modulator (MC) consisting of up to 16 high current outputs. The device is capable of stepper motor stall detection (SSD) via hardware or software, please contact Freescale sales office for detailed information on software SSD.

The MC9S12XHY family deliver all the advantages and efficiencies of a 16-bit MCU while retaining the low cost, power consumption, EMC, and code-size efficiency advantages currently enjoyed by users of Freescale's existing 8-bit and 16-bit MCU families. Like the MC9S12HY/HA family, the MC9S12XHY family run 16-bit wide accesses without wait states for all peripherals and memories. The MC9S12XHY family is available in 112-pin LQFP and 100-pin LQFP package options. In addition to the I/O ports available in each module, further I/O ports are available with interrupt capability allowing wake-up from stop or wait modes.

# 1.2 Features

This section describes the key features of the MC9S12XHY family.

- 16-bit free-running counter with 8-bit precision prescaler

- 1 x 16-bit pulse accumulator

# 1.3.10 Liquid crystal display driver (LCD)

- Configurable for up to 40 frontplanes and 4 backplanes or general-purpose input or output

- 5 modes of operation allow for different display sizes to meet application requirements

- Unused frontplane and backplane pins can be used as general-purpose I/O

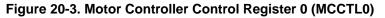

# 1.3.11 Motor Controller (MC)

- PWM motor controller (MC) with up to 16 high current drivers

- Each PWM channel switchable between two drivers in an H-bridge configuration

- Left, right and center aligned outputs

- Support for sine and cosine drive

- Dithering

- Output slew rate control

## 1.3.12 Pulse Width Modulation Module (PWM)

- 8channel x 8-bit or 4channel x 16-bit pulse width modulator

- Programmable period and duty cycle per channel

- Center-aligned or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

## 1.3.13 Inter-IC bus Module (IIC)

- 1 Inter-IC (IIC) bus module which has following feature

- Multi-master operation

- Soft programming for one of 256 different serial clock frequencies

- General Call(Broadcast) mode support

- 10-bit address support

## 1.3.14 Controller Area Network Module (MSCAN)

- 1 Mbit per second, CAN 2.0 A, B software compatible

- Standard and extended data frames

- 0–8 bytes data length

- Programmable bit rate up to 1 Mbps

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization

- Flexible identifier acceptance filter programmable as:

| Table 2-6. DDRA Register F | ield Descriptions |

|----------------------------|-------------------|

|----------------------------|-------------------|

| Field         | Description                                                                                                                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4,2<br>DDRA | Port A Data Direction—<br>This bit determines whether the associated pin is an input or output.<br>If corresponding LCD segment is enabled, it will be forced as input/output disable                                                                |

|               | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                  |

| 3<br>DDRA     | Port A Data Direction—<br>This bit determines whether the associated pin is an input or output.<br>If corresponding LCD segment is enabled, it will be forced as input/output disabled<br>Else if API_EXTCLK is enabled, it will be forced as output |

|               | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                  |

| 1<br>DDRA     | Port A Data Direction—<br>This bit determines whether the associated pin is an input or output.<br>If corresponding LCD segment is enabled, it will be forced as input/output disabled<br>Else if XIRQ is enabled, it will be forced as input        |

|               | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                  |

| 0<br>DDRA     | Port A Data Direction—<br>This bit determines whether the associated pin is an input or output.<br>If corresponding LCD segment is enabled, it will be forced as input/output disabled<br>Else if /IRQ is enabled, it will be forced as input        |

|               | 1 Associated pin is configured as output<br>0 Associated pin is configured as input                                                                                                                                                                  |

#### 2.3.6 Port B Data Direction Register (DDRB)

Address 0x0003 (PRR) Access: User read/write<sup>1</sup> 7 6 5 4 3 2 1 0 R DDRB7 DDRB6 DDRB5 DDRB4 DDRB3 DDRB2 DDRB1 DDRB0 W 0 0 0 0 0 0 0 0 Reset

Figure 2-4. Port B Data Direction Register (DDRB)

<sup>1</sup> Read: Anytime

Write: Anytime

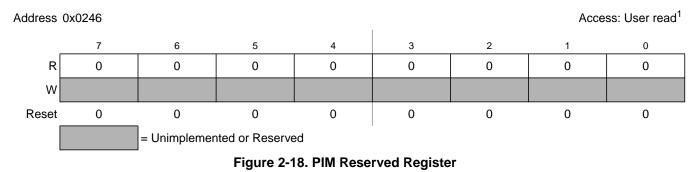

# 2.3.20 PIM Reserved Register

<sup>1</sup> Read: Always reads 0x00 Write: Unimplemented

# 2.3.21 Port T Routing Register (PTTRR)

Access: User read<sup>1</sup> Address 0x0247 7 6 5 4 3 2 1 0 R PTTRR7 PTTRR6 PTTRR5 PTTRR4 PTTRR3 PTTRR2 PTTRR1 PTTRR0 W Routing IOC0\_7 IOC0\_5 IOC0\_4 IOC0\_6 IOC1\_7 IOC1\_6 Option Reset 0 0 0 0 0 0 0 0 = Unimplemented or Reserved Figure 2-19. Port T Routing Register (PTTRR)

<sup>1</sup> Read: Anytime Write: Anytime

This register configures the re-routing of TIM0/1 channels on alternative pins on Port R/T.

| Table 2-16. | Port T | Routing | Register   | Field  | Descriptions |

|-------------|--------|---------|------------|--------|--------------|

|             |        | noung   | i togiotoi | 1 1010 | Docomptionio |

| Field          | Description                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------|

| [7:6]<br>PTTRR | Port T data direction—<br>This register controls the routing of IOC0_7.                                            |

|                | 00 IOC0_7 routed to PT7<br>01 IOC0_7 routed to PR1<br>10 IOC0_7 routed to PV6<br>11 IOC0_7 routed to PT7(reserved) |

| 5<br>PTTRR     | Port T data direction—<br>This register controls the routing of IOC0_5.                                            |

|                | 0 IOC0_5 routed to PT5<br>1 IOC0_5 routed to PV2                                                                   |

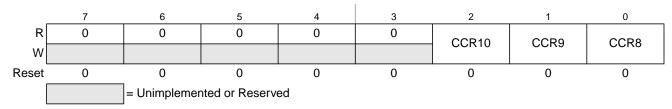

# 5.3.2.2 BDM CCR LOW Holding Register (BDMCCRL)

Register Global Address 0x7FFF06

| _                        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------------------------|------|------|------|------|------|------|------|------|

| R<br>W                   | CCR7 | CCR6 | CCR5 | CCR4 | CCR3 | CCR2 | CCR1 | CCR0 |

| Reset                    |      |      |      |      |      |      |      |      |

| Special Single-Chip Mode | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0    |

| All Other Modes          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Figure 5-4. BDM CCR LOW Holding Register (BDMCCRL)

Read: All modes through BDM operation when not secured

Write: All modes through BDM operation when not secured

#### NOTE

When BDM is made active, the CPU stores the content of its  $CCR_L$  register in the BDMCCRL register. However, out of special single-chip reset, the BDMCCRL is set to 0xD8 and not 0xD0 which is the reset value of the  $CCR_L$  register in this CPU mode. Out of reset in all other modes the BDMCCRL register is read zero.

When entering background debug mode, the BDM CCR LOW holding register is used to save the low byte of the condition code register of the user's program. It is also used for temporary storage in the standard BDM firmware mode. The BDM CCR LOW holding register can be written to modify the CCR value.

## 5.3.2.3 BDM CCR HIGH Holding Register (BDMCCRH)

Register Global Address 0x7FFF07

#### Figure 5-5. BDM CCR HIGH Holding Register (BDMCCRH)

Read: All modes through BDM operation when not secured

Write: All modes through BDM operation when not secured

When entering background debug mode, the BDM CCR HIGH holding register is used to save the high byte of the condition code register of the user's program. The BDM CCR HIGH holding register can be written to modify the CCR value.

#### S12X Debug (S12XDBGV3) Module

Comparators B and D consist of four register bytes (three address bus compare registers and a control register).

Each set of comparator registers is accessible in the same 8-byte window of the register address map and can be accessed using the COMRV bits in the DBGC1 register. If the Comparators B or D are accessed through the 8-byte window, then only the address and control bytes are visible, the 4 bytes associated with data bus and data bus masking read as zero and cannot be written. Furthermore the control registers for comparators B and D differ from those of comparators A and C.

| 0x0028 | CONTROL              | Read/Write | Comparators A,B,C,D     |

|--------|----------------------|------------|-------------------------|

| 0x0029 | ADDRESS HIGH         | Read/Write | Comparators A,B,C,D     |

| 0x002A | ADDRESS MEDIUM       | Read/Write | Comparators A,B,C,D     |

| 0x002B | ADDRESS LOW          | Read/Write | Comparators A,B,C,D     |

| 0x002C | DATA HIGH COMPARATOR | Read/Write | Comparator A and C only |

| 0x002D | DATA LOW COMPARATOR  | Read/Write | Comparator A and C only |

| 0x002E | DATA HIGH MASK       | Read/Write | Comparator A and C only |

| 0x002F | DATA LOW MASK        | Read/Write | Comparator A and C only |

#### Table 6-25. Comparator Register Layout

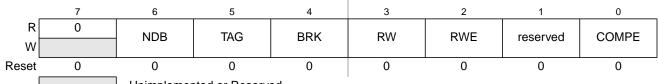

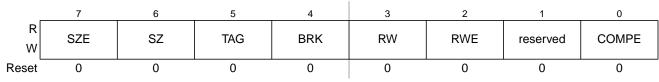

#### 6.3.2.8.1 Debug Comparator Control Register (DBGXCTL)

The contents of this register bits 7 and 6 differ depending upon which comparator registers are visible in the 8-byte window of the DBG module register address map.

Address: 0x0028

= Unimplemented or Reserved

Address: 0x0028

Figure 6-14. Debug Comparator Control Register (Comparators B and D)

Read: Anytime. See Table 6-26 for visible register encoding.

Write: If DBG not armed. See Table 6-26 for visible register encoding.

#### WARNING

DBGXCTL[1] is reserved. Setting this bit maps the corresponding comparator to an

MC9S12XHY-Family Reference Manual, Rev. 1.01

### NOTE

Using this configuration, a byte access of ADDR[n] can cause a comparator match if the databus low byte by chance contains the same value as ADDR[n+1] because the databus comparator does not feature access size comparison and uses the mask as a "don't care" function. Thus masked bits do not prevent a match.

Comparators A and C feature an NDB control bit to determine if a match occurs when the data bus differs to comparator register contents or when the data bus is equivalent to the comparator register contents.

# 6.4.2.2 Exact Address Comparator Match (Comparators B and D)

Comparators B and D feature SZ and SZE control bits. If SZE is clear, then the comparator address match qualification functions the same as for comparators A and C.

If the SZE bit is set the access size (word or byte) is compared with the SZ bit value such that only the specified type of access causes a match. Thus if configured for a byte access of a particular address, a word access covering the same address does not lead to match.

| Comparator             | Address | SZE | SZ8 | Condition For Valid Match                                                                        |

|------------------------|---------|-----|-----|--------------------------------------------------------------------------------------------------|

| Comparators<br>A and C | ADDR[n] | _   |     | Word and byte accesses of ADDR[n] <sup>(1)</sup><br>MOVB #\$BYTE ADDR[n]<br>MOVW #\$WORD ADDR[n] |

| Comparators<br>B and D | ADDR[n] | 0   | Х   | Word and byte accesses of ADDR[n] <sup>1</sup><br>MOVB #\$BYTE ADDR[n]<br>MOVW #\$WORD ADDR[n]   |

| Comparators<br>B and D | ADDR[n] | 1   | 0   | Word accesses of ADDR[n] <sup>1</sup><br>MOVW #\$WORD ADDR[n]                                    |

| Comparators<br>B and D | ADDR[n] | 1   | 1   | Byte accesses of ADDR[n]<br>MOVB #\$BYTE ADDR[n]                                                 |

Table 6-37. Comparator Access Size Considerations

1. A word access of ADDR[n-1] also accesses ADDR[n] but does not generate a match.

The comparator address register must contain the exact address used in the code.

# 6.4.2.3 Data Bus Comparison NDB Dependency

Comparators A and C each feature an NDB control bit, which allows data bus comparators to be configured to either trigger on equivalence or trigger on difference. This allows monitoring of a difference in the contents of an address location from an expected value.

When matching on an equivalence (NDB=0), each individual data bus bit position can be masked out by clearing the corresponding mask bit (DBGxDHM/DBGxDLM), so that it is ignored in the comparison. A match occurs when all data bus bits with corresponding mask bits set are equivalent. If all mask register bits are clear, then a match is based on the address bus only, the data bus is ignored.

When matching on a difference, mask bits can be cleared to ignore bit positions. A match occurs when any data bus bit with corresponding mask bit set is different. Clearing all mask bits, causes all bits to be ignored and prevents a match because no difference can be detected. In this case address bus equivalence does not cause a match.

- External pin reset

- Real-Time Interrupt (RTI)

# 7.1.2 Modes of Operation

This subsection lists and briefly describes all operating modes supported by the S12XECRG.

• Run Mode

All functional parts of the S12XECRG are running during normal Run Mode. If RTI or COP functionality is required the individual bits of the associated rate select registers (COPCTL, RTICTL) have to be set to a non zero value.

• Wait Mode

In this mode the IPLL can be disabled automatically depending on the PLLWAI bit.

• Stop Mode

Depending on the setting of the PSTP bit Stop Mode can be differentiated between Full Stop Mode (PSTP = 0) and Pseudo Stop Mode (PSTP = 1).

— Full Stop Mode

The oscillator is disabled and thus all system and core clocks are stopped. The COP and the RTI remain frozen.

— Pseudo Stop Mode

The oscillator continues to run and most of the system and core clocks are stopped. If the respective enable bits are set the COP and RTI will continue to run, else they remain frozen.

• Self Clock Mode

Self Clock Mode will be entered if the Clock Monitor Enable Bit (CME) and the Self Clock Mode Enable Bit (SCME) are both asserted and the clock monitor in the oscillator block detects a loss of clock. As soon as Self Clock Mode is entered the S12XECRG starts to perform a clock quality check. Self Clock Mode remains active until the clock quality check indicates that the required quality of the incoming clock signal is met (frequency and amplitude). Self Clock Mode should be used for safety purposes only. It provides reduced functionality to the MCU in case a loss of clock is causing severe system conditions.

# 7.1.3 Block Diagram

Figure 7-1 shows a block diagram of the S12XECRG.

| TSEG22 | TSEG21 | TSEG20 | Time Segment 2                  |

|--------|--------|--------|---------------------------------|

| 0      | 0      | 0      | 1 Tq clock cycle <sup>(1)</sup> |

| 0      | 0      | 1      | 2 Tq clock cycles               |

| :      | :      | :      | :                               |

| 1      | 1      | 0      | 7 Tq clock cycles               |

| 1      | 1      | 1      | 8 Tq clock cycles               |

Table 11-9. Time Segment 2 Values

1. This setting is not valid. Please refer to Table 11-37 for valid settings.

Table 11-10. Time Segment 1 Values

| TSEG13 | TSEG12 | TSEG11 | TSEG10 | Time segment 1                  |

|--------|--------|--------|--------|---------------------------------|

| 0      | 0      | 0      | 0      | 1 Tq clock cycle <sup>(1)</sup> |

| 0      | 0      | 0      | 1      | 2 Tq clock cycles <sup>1</sup>  |

| 0      | 0      | 1      | 0      | 3 Tq clock cycles <sup>1</sup>  |

| 0      | 0      | 1      | 1      | 4 Tq clock cycles               |

| :      | :      | :      | :      | :                               |

| 1      | 1      | 1      | 0      | 15 Tq clock cycles              |

| 1      | 1      | 1      | 1      | 16 Tq clock cycles              |

1. This setting is not valid. Please refer to Table 11-37 for valid settings.

The bit time is determined by the oscillator frequency, the baud rate prescaler, and the number of time quanta (Tq) clock cycles per bit (as shown in Table 11-9 and Table 11-10).

Eqn. 11-1

# Bit Time= $\frac{(Prescaler value)}{f_{CANCLK}} \bullet (1 + TimeSegment1 + TimeSegment2)$

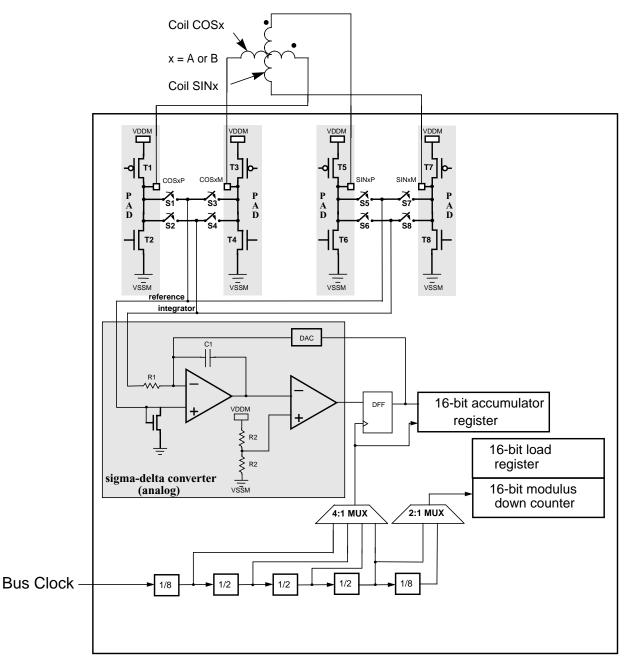

## 11.3.2.5 MSCAN Receiver Flag Register (CANRFLG)

A flag can be cleared only by software (writing a 1 to the corresponding bit position) when the condition which caused the setting is no longer valid. Every flag has an associated interrupt enable bit in the CANRIER register.

Access: User read/write<sup>(1)</sup> Module Base + 0x0004 7 6 5 3 2 1 0 4 RSTAT1 RSTAT0 TSTAT1 TSTAT0 R WUPIF CSCIF **OVRIF** RXF W 0 0 0 0 0 0 0 0 Reset: = Unimplemented Figure 11-8. MSCAN Receiver Flag Register (CANRFLG)

MC9S12XHY-Family Reference Manual Rev. 1.01

# 11.4.3.1 Protocol Violation Protection

The MSCAN protects the user from accidentally violating the CAN protocol through programming errors. The protection logic implements the following features:

- The receive and transmit error counters cannot be written or otherwise manipulated.

- All registers which control the configuration of the MSCAN cannot be modified while the MSCAN is on-line. The MSCAN has to be in Initialization Mode. The corresponding INITRQ/INITAK handshake bits in the CANCTL0/CANCTL1 registers (see Section 11.3.2.1, "MSCAN Control Register 0 (CANCTL0)") serve as a lock to protect the following registers:

- MSCAN control 1 register (CANCTL1)

- MSCAN bus timing registers 0 and 1 (CANBTR0, CANBTR1)

- MSCAN identifier acceptance control register (CANIDAC)

- MSCAN identifier acceptance registers (CANIDAR0–CANIDAR7)

- MSCAN identifier mask registers (CANIDMR0–CANIDMR7)

- The TXCAN is immediately forced to a recessive state when the MSCAN goes into the power down mode or initialization mode (see Section 11.4.5.6, "MSCAN Power Down Mode," and Section 11.4.4.5, "MSCAN Initialization Mode").

- The MSCAN enable bit (CANE) is writable only once in normal system operation modes, which provides further protection against inadvertently disabling the MSCAN.

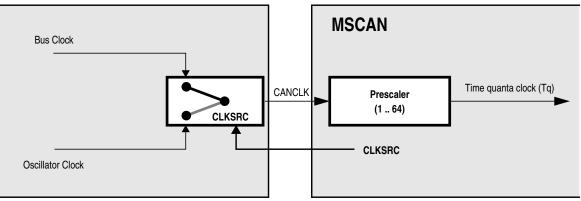

## 11.4.3.2 Clock System

Figure 11-43 shows the structure of the MSCAN clock generation circuitry.

Figure 11-43. MSCAN Clocking Scheme

The clock source bit (CLKSRC) in the CANCTL1 register (11.3.2.2/11-349) defines whether the internal CANCLK is connected to the output of a crystal oscillator (oscillator clock) or to the bus clock.

The clock source has to be chosen such that the tight oscillator tolerance requirements (up to 0.4%) of the CAN protocol are met. Additionally, for high CAN bus rates (1 Mbps), a 45% to 55% duty cycle of the clock is required.

If the bus clock is generated from a PLL, it is recommended to select the oscillator clock rather than the bus clock due to jitter considerations, especially at the faster CAN bus rates.

Pulse-Width Modulator (S12PWM8B8CV1)

## 13.3.2.7 Reserved Register (PWMTST)

This register is reserved for factory testing of the PWM module and is not available in normal modes.

Module Base + 0x0006

Figure 13-9. Reserved Register (PWMTST)

Read: Always read \$00 in normal modes

Write: Unimplemented in normal modes

#### NOTE

Writing to this register when in special modes can alter the PWM functionality.

## 13.3.2.8 Reserved Register (PWMPRSC)

This register is reserved for factory testing of the PWM module and is not available in normal modes.

Module Base + 0x0007

Figure 13-10. Reserved Register (PWMPRSC)

Read: Always read \$00 in normal modes

Write: Unimplemented in normal modes

#### NOTE

Writing to this register when in special modes can alter the PWM functionality.

## 13.3.2.9 PWM Scale A Register (PWMSCLA)

PWMSCLA is the programmable scale value used in scaling clock A to generate clock SA. Clock SA is generated by taking clock A, dividing it by the value in the PWMSCLA register and dividing that by two.

Clock SA = Clock A / (2 \* PWMSCLA)

MC9S12XHY-Family Reference Manual, Rev. 1.01

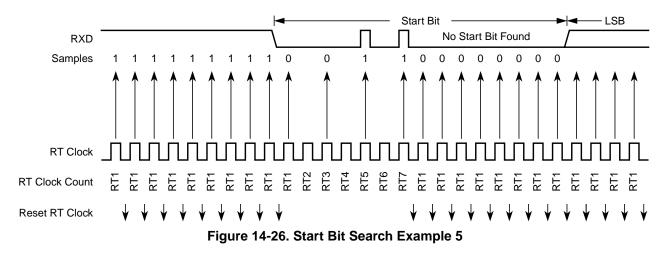

Figure 14-26 shows a burst of noise near the beginning of the start bit that resets the RT clock. The sample after the reset is low but is not preceded by three high samples that would qualify as a falling edge. Depending on the timing of the start bit search and on the data, the frame may be missed entirely or it may set the framing error flag.

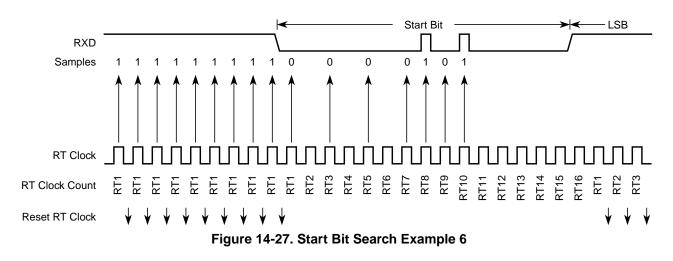

In Figure 14-27, a noise burst makes the majority of data samples RT8, RT9, and RT10 high. This sets the noise flag but does not reset the RT clock. In start bits only, the RT8, RT9, and RT10 data samples are ignored.

#### 14.4.6.4 Framing Errors

If the data recovery logic does not detect a logic 1 where the stop bit should be in an incoming frame, it sets the framing error flag, FE, in SCI status register 1 (SCISR1). A break character also sets the FE flag because a break character has no stop bit. The FE flag is set at the same time that the RDRF flag is set.

MC9S12XHY-Family Reference Manual, Rev. 1.01

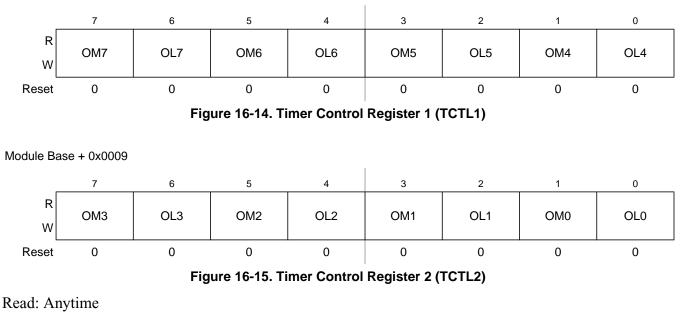

## 16.3.2.8 Timer Control Register 1/Timer Control Register 2 (TCTL1/TCTL2)

Write: Anytime

Module Base + 0x0008

#### Table 16-8. TCTL1/TCTL2 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OMx | <ul> <li>Output Mode — These eight pairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx.</li> <li>Note: To enable output action by OMx bits on timer port, the corresponding bit in OC7M should be cleared. For an output line to be driven by an OCx the OCPDx must be cleared.</li> </ul>  |

| 7:0<br>OLx | <ul> <li>Output Level — These eight pairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx.</li> <li>Note: To enable output action by OLx bits on timer port, the corresponding bit in OC7M should be cleared. For an output line to be driven by an OCx the OCPDx must be cleared.</li> </ul> |

#### Table 16-9. Compare Result Output Action

| ОМх | OLx | Action                                                 |

|-----|-----|--------------------------------------------------------|

| 0   | 0   | No output compare<br>action on the timer output signal |

| 0   | 1   | Toggle OCx output line                                 |

| 1   | 0   | Clear OCx output line to zero                          |

| 1   | 1   | Set OCx output line to one                             |

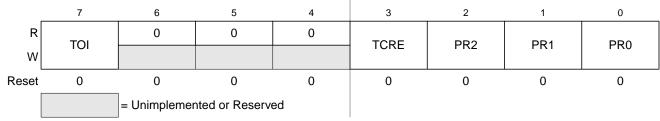

# 16.3.2.11 Timer System Control Register 2 (TSCR2)

Module Base + 0x000D

#### Figure 16-19. Timer System Control Register 2 (TSCR2)

Read: Anytime

Write: Anytime.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7<br>TOI     | Timer Overflow Interrupt Enable         0 Interrupt inhibited.         1 Hardware interrupt requested when TOF flag set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 3<br>TCRE    | <ul> <li>Timer Counter Reset Enable — This bit allows the timer counter to be reset by a successful output compare 7 event. This mode of operation is similar to an up-counting modulus counter.</li> <li>Counter reset inhibited and counter free runs.</li> <li>Counter reset by a successful output compare 7.</li> <li>Note: If TC7 = 0x0000 and TCRE = 1, TCNT will stay at 0x0000 continuously. If TC7 = 0xFFFF and TCRE = 1, TOF will never be set when TCNT is reset from 0xFFFF to 0x0000.</li> <li>Note: TCRE=1 and TC7!=0, the TCNT cycle period will be TC7 x "prescaler counter width" + "1 Bus Clock", for a more detail explanation please refer to Section 16.4.3, "Output Compare</li> </ul> |  |  |  |

| 2<br>PR[2:0] | <b>Timer Prescaler Select</b> — These three bits select the frequency of the timer prescaler clock derived from the Bus Clock as shown in Table 16-15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

#### Table 16-14. TSCR2 Field Descriptions

| PR2 | PR1 | PR0 | Timer Clock     |  |  |

|-----|-----|-----|-----------------|--|--|

| 0   | 0   | 0   | Bus Clock / 1   |  |  |

| 0   | 0   | 1   | Bus Clock / 2   |  |  |

| 0   | 1   | 0   | Bus Clock / 4   |  |  |

| 0   | 1   | 1   | Bus Clock / 8   |  |  |

| 1   | 0   | 0   | Bus Clock / 16  |  |  |

| 1   | 0   | 1   | Bus Clock / 32  |  |  |

| 1   | 1   | 0   | Bus Clock / 64  |  |  |

| 1   | 1   | 1   | Bus Clock / 128 |  |  |

| FPLS[1:0] | Global Address Range Protected Siz |          |

|-----------|------------------------------------|----------|

| 00        | 0x7F_8000-0x7F_83FF                | 1 Kbyte  |

| 01        | 0x7F_8000-0x7F_87FF                | 2 Kbytes |

| 10        | 0x7F_8000-0x7F_8FFF                | 4 Kbytes |

| 11        | 0x7F_8000-0x7F_9FFF                | 8 Kbytes |

Table 18-18. P-Flash Protection Lower Address Range

All possible P-Flash protection scenarios are shown in Figure 18-13. Although the protection scheme is loaded from the Flash memory at global address 0x7F\_FF0C during the reset sequence, it can be changed by the user. The P-Flash protection scheme can be used by applications requiring reprogramming in single chip mode while providing as much protection as possible if reprogramming is not required.

128 KByte Flash Module (S12XFTMR128K1V1)

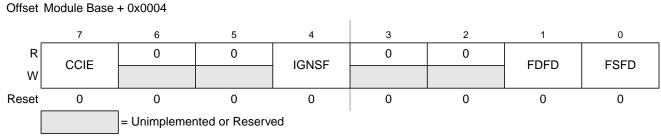

## 19.2.1.5 Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash command complete interrupt and forces ECC faults on Flash array read access from the CPU or XGATE.

#### Figure 19-6. Flash Configuration Register (FCNFG)

CCIE, IGNSF, FDFD, and FSFD bits are readable and writable while remaining bits read 0 and are not writable.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIE  | Command Complete Interrupt Enable — The CCIE bit controls interrupt generation when a Flash command has completed.         0 Command complete interrupt disabled         1 An interrupt will be requested whenever the CCIF flag in the FSTAT register is set (see Section 19.2.1.7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4<br>IGNSF | Ignore Single Bit Fault — The IGNSF controls single bit fault reporting in the FERSTAT register (see Section 19.2.1.8).         0 All single bit faults detected during array reads are reported         1 Single bit faults detected during array reads are not reported and the single bit fault interrupt will not be generated                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1<br>FDFD  | <ul> <li>Force Double Bit Fault Detect — The FDFD bit allows the user to simulate a double bit fault during Flash array read operations and check the associated interrupt routine. The FDFD bit is cleared by writing a 0 to FDFD. The FECCR registers will not be updated during the Flash array read operation with FDFD set unless an actual double bit fault is detected.</li> <li>0 Flash array read operations will set the DFDIF flag in the FERSTAT register only if a double bit fault is detected 1 Any Flash array read operation will force the DFDIF flag in the FERSTAT register to be set (see Section 19.2.1.7) and an interrupt will be generated as long as the DFDIE interrupt enable in the FERCNFG register is set (see Section 19.2.1.6)</li> </ul> |

| 0<br>FSFD  | <ul> <li>Force Single Bit Fault Detect — The FSFD bit allows the user to simulate a single bit fault during Flash array read operations and check the associated interrupt routine. The FSFD bit is cleared by writing a 0 to FSFD. The FECCR registers will not be updated during the Flash array read operation with FSFD set unless an actual single bit fault is detected.</li> <li>0 Flash array read operations will set the SFDIF flag in the FERSTAT register only if a single bit fault is detected 1 Flash array read operation will force the SFDIF flag in the FERSTAT register to be set (see Section 19.2.1.7) and an interrupt will be generated as long as the SFDIE interrupt enable in the FERCNFG register is set (see Section 19.2.1.6)</li> </ul>     |

#### Table 19-10. FCNFG Field Descriptions

## 19.2.1.6 Flash Error Configuration Register (FERCNFG)

The FERCNFG register enables the Flash error interrupts for the FERSTAT flags.

MC9S12XHY-Family Reference Manual, Rev. 1.01

#### 128 KByte Flash Module (S12XFTMR128K1V1)

any Flash program or erase command loaded during a command write sequence will not execute and the ACCERR bit in the FSTAT register will set.

#### 19.3.1.2 Command Write Sequence

The Memory Controller will launch all valid Flash commands entered using a command write sequence.

Before launching a command, the ACCERR and FPVIOL bits in the FSTAT register must be clear (see Section 19.2.1.7) and the CCIF flag should be tested to determine the status of the current command write sequence. If CCIF is 0, the previous command write sequence is still active, a new command write sequence cannot be started, and all writes to the FCCOB register are ignored.

#### CAUTION

Writes to any Flash register must be avoided while a Flash command is active (CCIF=0) to prevent corruption of Flash register contents and Memory Controller behavior.

#### 19.3.1.2.1 Define FCCOB Contents

The FCCOB parameter fields must be loaded with all required parameters for the Flash command being executed. Access to the FCCOB parameter fields is controlled via the CCOBIX bits in the FCCOBIX register (see Section 19.2.1.3).

The contents of the FCCOB parameter fields are transferred to the Memory Controller when the user clears the CCIF command completion flag in the FSTAT register (writing 1 clears the CCIF to 0). The CCIF flag will remain clear until the Flash command has completed. Upon completion, the Memory Controller will return CCIF to 1 and the FCCOB register will be used to communicate any results. The flow for a generic command write sequence is shown in Figure 19-23.

| Offset | Register | Access |

|--------|----------|--------|

| 0x003E | Reserved | —      |

| 0x003F | Reserved | —      |

| 1      |          |        |

#### Figure 20-2. MC10B8C Memory Map (continued)

<sup>1</sup> Write accesses to "Reserved" addresses have no effect. Read accesses to "Reserved" addresses provide **invalid** data (0x0000).

### 20.3.2 Register Descriptions

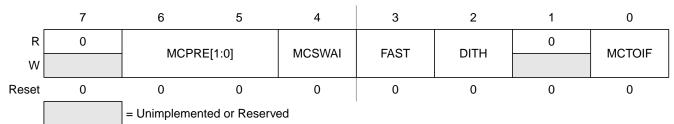

#### 20.3.2.1 Motor Controller Control Register 0

This register controls the operating mode of the motor controller module.

Offset Module Base + 0x0000

#### Table 20-3. MCCTL0 Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:5<br>MCPRE[1:0] | <b>Motor Controller Prescaler Select</b> — MCPRE1 and MCPRE0 determine the prescaler value that sets the motor controller timer counter clock frequency ( $f_{TC}$ ). The clock source for the prescaler is the peripheral bus clock ( $f_{BUS}$ ) as shown in Figure 20-22. Writes to MCPRE1 or MCPRE0 will not affect the timer counter clock frequency $f_{TC}$ until the start of the next PWM period. Table 20-4 shows the prescaler values that result from the possible combinations of MCPRE1 and MCPRE0 |

| 4<br>MCSWAI       | <ul> <li>Motor Controller Module Stop in Wait Mode</li> <li>0 Entering wait mode has no effect on the motor controller module and the associated port pins maintain the functionality they had prior to entering wait mode both during wait mode and after exiting wait mode.</li> <li>1 Entering wait mode will stop the clock of the module and debias the analog circuitry. The module will release the pins.</li> </ul>                                                                                      |

| 3<br>FAST         | Motor Controller PWM Resolution Mode0PWM operates in 11-bit resolution mode, duty cycle registers of all channels are switched to word mode.1PWM operates in 7-bit resolution (fast) mode, duty cycle registers of all channels are switched to byte mode.                                                                                                                                                                                                                                                       |

| 2<br>DITH         | <ul> <li>Motor Control/Driver Dither Feature Enable (refer to Section 20.4.1.3.5, "Dither Bit (DITH)")</li> <li>0 Dither feature is disabled.</li> <li>1 Dither feature is enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| 0<br>MCTOIF       | <ul> <li>Motor Controller Timer Counter Overflow Interrupt Flag — This bit is set when a motor controller timer counter overflow occurs. The bit is cleared by writing a 1 to the bit.</li> <li>0 A motor controller timer counter overflow has not occurred since the last reset or since the bit was cleared.</li> <li>1 A motor controller timer counter overflow has occurred.</li> </ul>                                                                                                                    |

# 21.1.3 Block Diagram

Figure 21-1. SSD Block Diagram

| Model          | Description                                     | Symbol | Value  | Unit |

|----------------|-------------------------------------------------|--------|--------|------|

| Human Body     | Series resistance                               | R1     | 1500   | Ohm  |

|                | Storage capacitance                             | С      | 100    | pF   |

|                | Number of pulse per pin<br>Positive<br>Negative |        | 1<br>1 |      |

| Charged Device | Number of pulse per pin<br>Positive<br>Negative | _      | 3<br>3 |      |

| Latch-up       | Minimum input voltage limit                     | _      | -2.5   | V    |

|                | Maximum input voltage limit                     | _      | 7.5    | V    |

#### Table A-2. ESD and Latch-up Test Conditions

Table A-3. ESD and Latch-Up Protection Characteristics

| Num | С | Rating                                                                       | Symbol           | Min          | Max | Unit |

|-----|---|------------------------------------------------------------------------------|------------------|--------------|-----|------|

| 1   | С | Human Body Model (HBM)                                                       | V <sub>HBM</sub> | 2000         | _   | V    |

| 2   | С | Charge Device Model (CDM) corner pins<br>Charge Device Model (CDM) edge pins | V <sub>CDM</sub> | 750<br>500   |     | V    |

| 3   | С | Latch-up current at T <sub>A</sub> = 125°C<br>Positive<br>Negative           | I <sub>LAT</sub> | +100<br>-100 | _   | mA   |

| 4   | С | Latch-up current at T <sub>A</sub> = 27°C<br>Positive<br>Negative            | I <sub>LAT</sub> | +200<br>-200 |     | mA   |

## A.1.7 Operating Conditions

This section describes the operating conditions of the device. Unless otherwise noted those conditions apply to all the following data.

#### NOTE

Please refer to the temperature rating of the device (C, V, M) with regards to the ambient temperature  $T_A$  and the junction temperature  $T_J$ . For power dissipation calculations refer to Section A.1.8, "Power Dissipation and Thermal Characteristics".

| Table A-4. | Operating | Conditions |

|------------|-----------|------------|

|------------|-----------|------------|

| Rating                                                 | Symbol            | Min               | Тур          | Мах     | Unit |

|--------------------------------------------------------|-------------------|-------------------|--------------|---------|------|

| I/O, regulator and analog supply voltage               | V <sub>DD35</sub> | 3.13 <sup>1</sup> | 5            | 5.5     | V    |

| NVM logic supply voltage <sup>2</sup>                  | V <sub>DDF</sub>  | 2.7               | 2.8          | 2.9     | V    |

| Voltage difference $V_{DDX}$ to $V_{DDA}$ to $V_{DDM}$ | $\Delta_{VDDX}$   |                   | refer to Tab | le A-12 |      |