#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | DMA, POR, PWM, WDT                                                    |

| Number of I/O              | 26                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | ·                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                           |

| Data Converters            | A/D 12x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f030k6t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   | 3.15   | Serial pe | eripheral interface (SPI) 22                           |

|---|--------|-----------|--------------------------------------------------------|

|   | 3.16   | Serial w  | ire debug port (SW-DP) 23                              |

| 4 | Pinou  | ts and p  | oin descriptions                                       |

| 5 | Memo   | ory map   | ping                                                   |

| 6 | Electr | ical cha  | aracteristics                                          |

|   | 6.1    | Parame    | ter conditions                                         |

|   |        | 6.1.1     | Minimum and maximum values                             |

|   |        | 6.1.2     | Typical values                                         |

|   |        | 6.1.3     | Typical curves                                         |

|   |        | 6.1.4     | Loading capacitor                                      |

|   |        | 6.1.5     | Pin input voltage                                      |

|   |        | 6.1.6     | Power supply scheme                                    |

|   |        | 6.1.7     | Current consumption measurement                        |

|   | 6.2    | Absolute  | e maximum ratings 42                                   |

|   | 6.3    | Operatir  | ng conditions                                          |

|   |        | 6.3.1     | General operating conditions                           |

|   |        | 6.3.2     | Operating conditions at power-up / power-down          |

|   |        | 6.3.3     | Embedded reset and power control block characteristics |

|   |        | 6.3.4     | Embedded reference voltage                             |

|   |        | 6.3.5     | Supply current characteristics                         |

|   |        | 6.3.6     | Wakeup time from low-power mode                        |

|   |        | 6.3.7     | External clock source characteristics                  |

|   |        | 6.3.8     | Internal clock source characteristics                  |

|   |        | 6.3.9     | PLL characteristics                                    |

|   |        | 6.3.10    | Memory characteristics                                 |

|   |        | 6.3.11    | EMC characteristics                                    |

|   |        | 6.3.12    | Electrical sensitivity characteristics                 |

|   |        | 6.3.13    | I/O current injection characteristics                  |

|   |        | 6.3.14    | I/O port characteristics                               |

|   |        | 6.3.15    | NRST pin characteristics                               |

|   |        | 6.3.16    | 12-bit ADC characteristics                             |

|   |        | 6.3.17    | Temperature sensor characteristics                     |

|   |        | 6.3.18    | Timer characteristics                                  |

|   |        | 6.3.19    | Communication interfaces                               |

| 7 | Packa | age info  | rmation                | 75 |

|---|-------|-----------|------------------------|----|

|   | 7.1   | LQFP64    | package information    | 75 |

|   | 7.2   | LQFP48    | package information    | 78 |

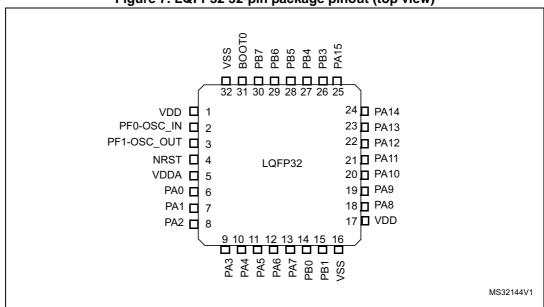

|   | 7.3   | LQFP32    | package information    | 81 |

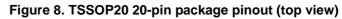

|   | 7.4   | TSSOP     | 20 package information | 84 |

|   | 7.5   | Therma    | characteristics        | 87 |

|   |       | 7.5.1     | Reference document     | 87 |

| 8 | Order | ring info | rmation                | 88 |

| 9 | Revis | ion hist  | ory                    | 89 |

# 2 Description

The STM32F030x4/x6/x8/xC microcontrollers incorporate the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0 32-bit RISC core operating at a 48 MHz frequency, high-speed embedded memories (up to 256 Kbytes of Flash memory and up to 32 Kbytes of SRAM), and an extensive range of enhanced peripherals and I/Os. All devices offer standard communication interfaces (up to two I<sup>2</sup>Cs, up to two SPIs and up to six USARTs), one 12-bit ADC, seven general-purpose 16-bit timers and an advanced-control PWM timer.

The STM32F030x4/x6/x8/xC microcontrollers operate in the -40 to +85 °C temperature range from a 2.4 to 3.6V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

The STM32F030x4/x6/x8/xC microcontrollers include devices in four different packages ranging from 20 pins to 64 pins. Depending on the device chosen, different sets of peripherals are included. The description below provides an overview of the complete range of STM32F030x4/x6/x8/xC peripherals proposed.

These features make the STM32F030x4/x6/x8/xC microcontrollers suitable for a wide range of applications such as application control and user interfaces, handheld equipment, A/V receivers and digital TV, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms, and HVACs.

# 3.11 Timers and watchdogs

The STM32F030x4/x6/x8/xC devices include up to five general-purpose timers, two basic timers and one advanced control timer.

*Table 5* compares the features of the different timers.

| Timer<br>type       | Timer                                       | Counter resolution | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |

|---------------------|---------------------------------------------|--------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|

| Advanced<br>control | TIM1                                        | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | 3                        |

|                     | TIM3                                        | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | -                        |

| General             | TIM14                                       | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | No                     | 1                           | -                        |

| purpose             | TIM15 <sup>(1)</sup>                        | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 2                           | -                        |

|                     | TIM16,<br>TIM17                             | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 1                           | 1                        |

| Basic               | TIM6, <sup>(1)</sup><br>TIM7 <sup>(2)</sup> | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | -                        |

1. Available on STM32F030x8 and STM32F030xC devices only.

2. Available on STM32F030xC devices only

## 3.11.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes)

- One-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard timers which have the same architecture. The advanced control timer can therefore work together with the other timers via the Timer Link feature for synchronization or event chaining.

## 3.11.2 General-purpose timers (TIM3, TIM14..17)

There are four or five synchronizable general-purpose timers embedded in the STM32F030x4/x6/x8/xC devices (see *Table 5* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

## TIM3

STM32F030x4/x6/x8/xC devices feature one synchronizable 4-channel general-purpose timer. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM3 general-purpose timer can work with the TIM1 advanced-control timer via the Timer Link feature for synchronization or event chaining.

TIM3 has an independent DMA request generation.

This timer is capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

The counter can be frozen in debug mode.

#### TIM14

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

### TIM15, TIM16 and TIM17

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

## 3.11.3 Basic timers TIM6 and TIM7

These timers can be used as a generic 16-bit time base.

### 3.11.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It

DocID024849 Rev 3

## Figure 7. LQFP32 32-pin package pinout (top view)

| F      | Pin nu | nber   |         |                                       |          | đ             | _     | Pin functions                                                                                                      |                                |

|--------|--------|--------|---------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------|--------------------------------|

| LQFP64 | LQFP48 | LQFP32 | TSSOP20 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                | Additional functions           |

| 22     | 16     | 12     | 12      | PA6                                   | I/O      | ТТа           | -     | SPI1_MISO,<br>TIM3_CH1,<br>TIM1_BKIN,<br>TIM16_CH1,<br>EVENTOUT<br>USART3_CTS <sup>(5)</sup>                       | ADC_IN6                        |

| 23     | 17     | 13     | 13      | PA7                                   | I/O      | ТТа           | -     | SPI1_MOSI,<br>TIM3_CH2,<br>TIM14_CH1,<br>TIM1_CH1N,<br>TIM17_CH1,<br>EVENTOUT                                      | ADC_IN7                        |

| 24     | -      | -      | -       | PC4                                   | I/O      | TTa           | -     | EVENTOUT,<br>USART3_TX <sup>(5)</sup>                                                                              | ADC_IN14                       |

| 25     | -      | -      | -       | PC5                                   | I/O      | TTa           | -     | USART3_RX <sup>(5)</sup>                                                                                           | ADC_IN15, WKPU5 <sup>(5)</sup> |

| 26     | 18     | 14     | -       | PB0                                   | I/O      | ТТа           | -     | TIM3_CH3,<br>TIM1_CH2N,<br>EVENTOUT,<br>USART3_CK <sup>(5)</sup>                                                   | ADC_IN8                        |

| 27     | 19     | 15     | 14      | PB1                                   | I/O      | ТТа           | -     | TIM3_CH4,<br>TIM14_CH1,<br>TIM1_CH3N,<br>USART3_RTS <sup>(5)</sup>                                                 | ADC_IN9                        |

| 28     | 20     | -      | -       | PB2                                   | I/O      | FT            | (6)   | -                                                                                                                  | -                              |

| 29     | 21     | -      | -       | PB10                                  | I/O      | FT            | -     | SPI2_SCK <sup>(5)</sup> ,<br>I2C1_SCL <sup>(2)</sup> ,<br>I2C2_SCL <sup>(3)(5)</sup> ,<br>USART3_TX <sup>(5)</sup> | -                              |

| 30     | 22     | -      | -       | PB11                                  | I/O      | FT            | -     | I2C1_SDA <sup>(2)</sup> ,<br>I2C2_SDA <sup>(3)(5)</sup> ,<br>EVENTOUT,<br>USART3_RX <sup>(5)</sup>                 | -                              |

| 31     | 23     | 16     | -       | VSS                                   | S        | -             | -     | Grou                                                                                                               | und                            |

| 32     | 24     | 17     | 16      | VDD                                   | S        | -             | -     | Digital power supply                                                                                               |                                |

| 33     | 25     | -      | -       | PB12                                  | I/O      | FT            | -     | SPI1_NSS <sup>(2)</sup> ,<br>SPI2_NSS <sup>(3)(5)</sup> ,<br>TIM1_BKIN,<br>EVENTOUT,<br>USART3_CK <sup>(5)</sup>   | -                              |

Table 11. STM32F030x4/6/8/C pin definitions (continued)

| Pin name     | AF0                         | AF1                                  | AF2       | AF3                          | AF4                        | AF5                     |  |

|--------------|-----------------------------|--------------------------------------|-----------|------------------------------|----------------------------|-------------------------|--|

| PB8          | -                           | I2C1_SCL                             | TIM16_CH1 | -                            | -                          | -                       |  |

| PB9          | IR_OUT                      | I2C1_SDA                             | TIM17_CH1 | EVENTOUT                     | -                          | SPI2_NSS <sup>(1)</sup> |  |

| <b>DD</b> 40 |                             | I2C1_SCL <sup>(2)</sup>              |           |                              | USART3_TX <sup>(1)</sup>   | SPI2_SCK <sup>(1)</sup> |  |

| PB10         | -                           | I2C2_SCL <sup>(1)(3)</sup>           | -         | -                            | USART3_RX <sup>(1)</sup>   | -                       |  |

| PB11         | EVENTOUT                    | I2C1_SDA <sup>(2)</sup>              |           | -                            |                            |                         |  |

|              |                             | I2C2_SDA <sup>(1)(3)</sup>           | -         |                              | USART3_RX <sup>(1)</sup>   | -                       |  |

| PB12 -       | SPI1_NSS <sup>(2)</sup>     |                                      |           |                              |                            | TIM15 <sup>(1)</sup>    |  |

|              | SPI2_NSS <sup>(1)(3)</sup>  | EVENTOUT                             | TIM1_BKIN | -                            | USART3_RTS <sup>(1)</sup>  | TIM15 <sup>(*)</sup>    |  |

| DD40         | SPI1_SCK <sup>(2)</sup>     |                                      |           |                              |                            |                         |  |

| PB13         | SPI2_SCK <sup>(1)(3)</sup>  | -                                    | TIM1_CH1N | -                            | USART3_CTS( <sup>(1)</sup> | I2C2_SCL <sup>(1)</sup> |  |

|              | SPI1_MISO <sup>(2)</sup>    | PI1_MISO <sup>(2)</sup>              |           |                              | (1)                        |                         |  |

| PB14         | SPI2_MISO <sup>(1)(3)</sup> | TIM15_CH1 <sup>(1)(3)</sup>          | TIM1_CH2N | -                            | USART3_RTS <sup>(1)</sup>  | I2C2_SDA <sup>(1)</sup> |  |

|              | SPI1_MOSI <sup>(2)</sup>    | TIM15_CH2 <sup>(1)(3)</sup>          |           |                              |                            |                         |  |

| PB15 -       | SPI2_MOSI <sup>(1)(3)</sup> | TIM15_CH2 <sup>(1)(3)</sup> TIM1_CH3 |           | TIM15_CH1N <sup>(1)(3)</sup> | -                          | -                       |  |

1. This feature is available on STM32F030xC devices.

2. This feature is available on STM32F030x4 and STM32F030x6 devices.

3. This feature is available on STM32F030x8 devices.

**N**

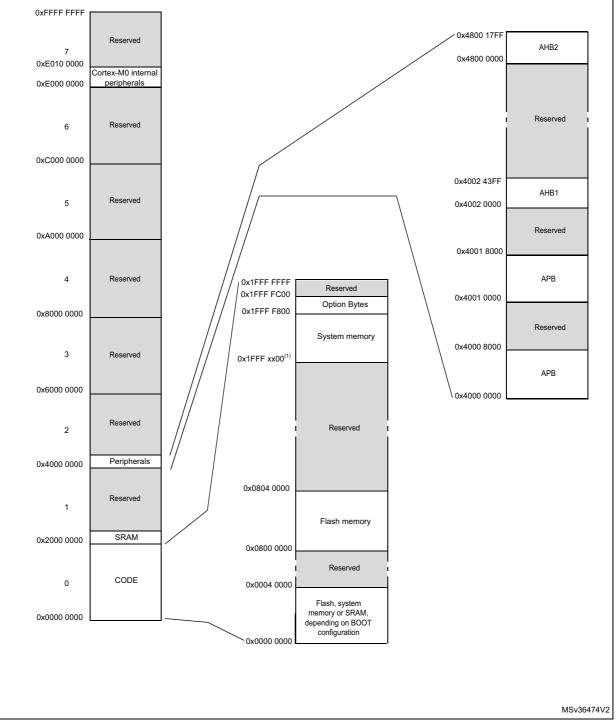

# 5 Memory mapping

Figure 9. STM32F030x4/x6/x8/xC memory map

1. The start address of the system memory is 0x1FFF EC00 for STM32F030x4, STM32F030x6 and STM32F030x8 devices, and 0x1FFF D800 for STM32F030xC devices.

DocID024849 Rev 3

| Bus | Boundary address          | Size  | Peripheral            |

|-----|---------------------------|-------|-----------------------|

| -   | 0x4000 8000 - 0x4000 FFFF | 32 KB | Reserved              |

|     | 0x4000 7400 - 0x4000 7FFF | 3 KB  | Reserved              |

|     | 0x4000 7000 - 0x4000 73FF | 1 KB  | PWR                   |

|     | 0x4000 5C00 - 0x4000 6FFF | 5 KB  | Reserved              |

|     | 0x4000 5800 - 0x4000 5BFF | 1 KB  | I2C2 <sup>(1)</sup>   |

|     | 0x4000 5400 - 0x4000 57FF | 1 KB  | I2C1                  |

|     | 0x4000 5000 - 0x4000 53FF | 1 KB  | USART5 <sup>(2)</sup> |

|     | 0x4000 4C00 - 0x4000 4FFF | 1 KB  | USART4 <sup>(2)</sup> |

|     | 0x4000 4800 - 0x4000 4BFF | 1 KB  | USART3 <sup>(2)</sup> |

|     | 0x4000 4400 - 0x4000 47FF | 1 KB  | USART2 <sup>(1)</sup> |

|     | 0x4000 3C00 - 0x4000 43FF | 2 KB  | Reserved              |

|     | 0x4000 3800 - 0x4000 3BFF | 1 KB  | SPI2 <sup>(1)</sup>   |

| APB | 0x4000 3400 - 0x4000 37FF | 1 KB  | Reserved              |

|     | 0x4000 3000 - 0x4000 33FF | 1 KB  | IWDG                  |

|     | 0x4000 2C00 - 0x4000 2FFF | 1 KB  | WWDG                  |

|     | 0x4000 2800 - 0x4000 2BFF | 1 KB  | RTC                   |

|     | 0x4000 2400 - 0x4000 27FF | 1 KB  | Reserved              |

|     | 0x4000 2000 - 0x4000 23FF | 1 KB  | TIM14                 |

|     | 0x4000 1800 - 0x4000 1FFF | 2 KB  | Reserved              |

|     | 0x4000 1400 - 0x4000 17FF | 1 KB  | TIM7 <sup>(2)</sup>   |

|     | 0x4000 1000 - 0x4000 13FF | 1 KB  | TIM6 <sup>(1)</sup>   |

|     | 0x4000 0800 - 0x4000 0FFF | 2 KB  | Reserved              |

|     | 0x4000 0400 - 0x4000 07FF | 1 KB  | ТІМЗ                  |

|     | 0x4000 0000 - 0x4000 03FF | 1 KB  | Reserved              |

#### Table 17. STM32F030x4/x6/x8/xC peripheral register boundary addresses (continued)

1. This feature is available on STM32F030x8 and STM32F030xC devices only. For STM32F030x6 and STM32F060x4, the area is Reserved.

2. This feature is available on STM32F030xC devices only. This area is reserved for STM32F030x4/6/8 devices.

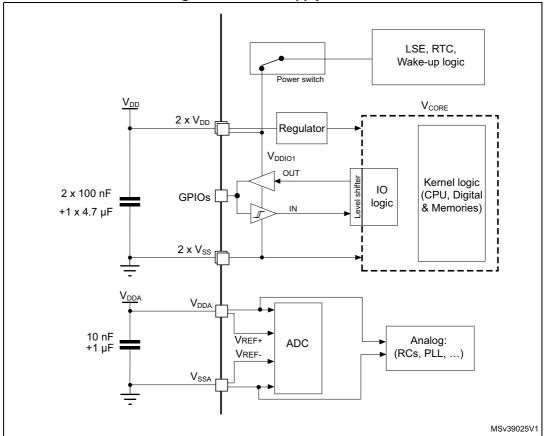

## 6.1.6 Power supply scheme

Figure 12. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

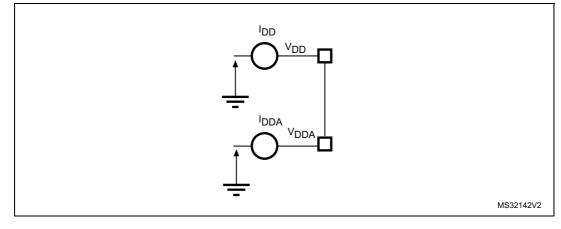

## 6.1.7 Current consumption measurement

## Figure 13. Current consumption measurement scheme

## Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 25* to *Table 27* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

# Table 25. Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD}$ = 3.6 V<sup>(1)</sup>

|                 |                                     |                           |                   | All peripher | als enabled                         |      |

|-----------------|-------------------------------------|---------------------------|-------------------|--------------|-------------------------------------|------|

| Symbol          | Parameter                           | Conditions                | f <sub>HCLK</sub> |              | Max @ T <sub>A</sub> <sup>(2)</sup> | Unit |

| Sy              |                                     |                           |                   | Тур          | 85 °C                               |      |

|                 |                                     |                           | 48 MHz            | 22.0         | 22.8                                |      |

|                 |                                     | HSI or HSE clock, PLL on  | 48 MHz            | 26.8         | 30.2                                |      |

|                 | Supply current in<br>Run mode, code |                           | 24 MHz            | 12.2         | 13.2                                | mA   |

| I <sub>DD</sub> | executing from Flash                |                           | 24 MHz            | 14.1         | 16.2                                | ma   |

|                 |                                     | HSI or HSE clock, PLL off | 8 MHz             | 4.4          | 5.2                                 |      |

|                 |                                     |                           | 8 MHz             | 4.9          | 5.6                                 |      |

|                 |                                     | HSI or HSE clock, PLL on  | 48 MHz            | 22.2         | 23.2                                | mA   |

|                 | Supply current in Run mode, code    |                           | 48 MHz            | 26.1         | 29.3                                |      |

| 1               |                                     |                           | 24 MHz            | 11.2         | 12.2                                |      |

| I <sub>DD</sub> | executing from RAM                  |                           | 24 MHz            | 13.3         | 15.7                                |      |

|                 |                                     | HSI or HSE clock, PLL off | 8 MHz             | 4.0          | 4.5                                 |      |

|                 |                                     |                           | 8 MHz             | 4.6          | 5.2                                 |      |

|                 |                                     |                           | 48 MHz            | 14           | 15.3                                |      |

|                 | Supply current in                   | HSI or HSE clock, PLL on  | 48 MHz            | 17.0         | 19.0                                |      |

| 1               | Sleep mode, code                    | TIGE OF THE CIUCK, FLE OF | 24 MHz            | 7.3          | 7.8                                 | mA   |

| I <sub>DD</sub> | executing from Flash<br>or RAM      |                           | 24 MHz            | 8.7          | 10.1                                |      |

|                 |                                     | HSI or HSE clock, PLL off | 8 MHz             | 2.6          | 2.9                                 |      |

|                 |                                     | TIGE OF THE CIUCK, FLE UI | 8 MHz             | 3.0          | 3.5                                 |      |

1. The gray shading is used to distinguish the values for STM32F030xC devices.

2. Data based on characterization results, not tested in production unless otherwise specified.

| Symbol                 | Parameter                         | Cor                                                | Typ @V <sub>DD</sub><br>(V <sub>DD</sub> = V <sub>DDA</sub> )  | Max <sup>(1)</sup>   | Unit                   |     |

|------------------------|-----------------------------------|----------------------------------------------------|----------------------------------------------------------------|----------------------|------------------------|-----|

|                        |                                   |                                                    |                                                                | 3.6 V                | T <sub>A</sub> = 85 °C |     |

| I <sub>DD</sub> Stop r | Supply current in                 | Regulator in run mode                              | , all oscillators OFF                                          | 19                   | 48                     |     |

|                        | Stop mode                         | Regulator in low-powe                              | 5                                                              | 32                   |                        |     |

|                        | Supply current in<br>Standby mode | LSI ON and IWDG ON                                 |                                                                | 2                    | -                      |     |

|                        | Supply current in Stop mode       |                                                    | Regulator in run or low-<br>power mode, all<br>oscillators OFF | 2.9                  | 3.5                    | μA  |

|                        | Supply current in Standby mode    | V <sub>DDA</sub> monitoring ON<br>upply current in | LSI ON and IWDG ON                                             | 3.3                  | -                      |     |

|                        |                                   |                                                    |                                                                | LSI OFF and IWDG OFF | 2.8                    | 3.5 |

| I <sub>DDA</sub>       | Supply current in Stop mode       |                                                    | Regulator in run or low-<br>power mode, all<br>oscillators OFF | 1.7                  | -                      |     |

|                        | Supply current in                 |                                                    | LSI ON and IWDG ON                                             | 2.3                  | -                      |     |

|                        | Standby mode                      |                                                    | LSI OFF and IWDG OFF                                           | 1.4                  | -                      |     |

Table 27. Typical and maximum consumption in Stop and Standby modes

1. Data based on characterization results, not tested in production unless otherwise specified.

## Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins are in analog input configuration

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol               | Parameter  | Conditions                                                                             | Monitored        | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |  |  |  |

|----------------------|------------|----------------------------------------------------------------------------------------|------------------|------------------------------------------------|------|--|--|--|

|                      | Farameter  |                                                                                        | frequency band   | 8/48 MHz                                       | Onit |  |  |  |

|                      | Decklosed  | $V_{DD} = 3.6 V$ , $T_A = 25 °C$ ,<br>LQFP100 package<br>compliant with<br>IEC 61967-2 | 0.1 to 30 MHz    | -3                                             |      |  |  |  |

| 6                    |            |                                                                                        | 30 to 130 MHz    | 23                                             | dBµV |  |  |  |

| S <sub>EMI</sub> Pea | Peak level |                                                                                        | 130 MHz to 1 GHz | 17                                             |      |  |  |  |

|                      |            |                                                                                        | EMI Level        | 4                                              | -    |  |  |  |

#### Table 42. EMI characteristics

## 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### **Electrostatic discharge (ESD)**

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                               | Conditions                                                  | Packages | Class                                  | Maximum<br>value <sup>(1)</sup>          | Unit |  |  |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------------|----------|----------------------------------------|------------------------------------------|------|--|--|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \text{ °C}$ , conforming<br>to JESD22-A114       | All      | 2                                      | 2000                                     | V    |  |  |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C}$ , conforming<br>to ANSI/ESD STM5.3.1 | All      | C4 <sup>(2)</sup><br>C3 <sup>(3)</sup> | 500 <sup>(2)</sup><br>250 <sup>(3)</sup> | V    |  |  |

Table 43. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

2. Applicable to STM32F030xC

3. Applicable to STM32F030x4, STM32F030x6, and STM32F030x8

## Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 44. Electrical sensitivities

| Symbol Parameter |                       | Conditions                                    | Class      |  |

|------------------|-----------------------|-----------------------------------------------|------------|--|

| LU               | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |  |

## 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DDIOx}$  (for standard, 3.3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of the -5  $\mu$ A/+0  $\mu$ A range) or other functional failure (for example reset occurrence or oscillator frequency deviation).

The characterization results are given in Table 45.

Negative induced leakage current is caused by negative injection and positive induced leakage current is caused by positive injection.

| Symbol           | Deparintian                                                                                                          |                    | Functional susceptibility |      |  |

|------------------|----------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------|------|--|

| Symbol           | Description                                                                                                          | Negative injection | Positive injection        | Unit |  |

|                  | Injected current on BOOT0 and PF1 pins                                                                               | -0                 | NA                        |      |  |

|                  | Injected current on PA9, PB3, PB13, PF11 pins with induced leakage current on adjacent pins less than 50 $\mu \rm A$ | -5                 | NA                        |      |  |

| I <sub>INJ</sub> | Injected current on PA11 and PA12 pins with induced leakage current on adjacent pins less than -1 mA                 | -5                 | NA                        | mA   |  |

| ·IINJ            | Injected current on all other FT and FTf pins                                                                        | -5                 | NA                        |      |  |

|                  | Injected current on PB0 and PB1 pins                                                                                 | -5                 | NA                        |      |  |

|                  | Injected current on PC0 pin                                                                                          | -0                 | +5                        |      |  |

|                  | Injected current on all other TTa, TC and RST pins                                                                   | -5                 | +5                        |      |  |

| Table 45. I/O currer | nt injection | susceptibility |

|----------------------|--------------|----------------|

|----------------------|--------------|----------------|

## 6.3.14 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under the conditions summarized in *Table 21: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol           | Parameter                     | Conditions                   | Min                                            | Тур                    | Max                                          | Unit |

|------------------|-------------------------------|------------------------------|------------------------------------------------|------------------------|----------------------------------------------|------|

|                  |                               | TC and TTa I/O               | -                                              | -                      | 0.3 V <sub>DDIOx</sub> +0.07 <sup>(1)</sup>  |      |

|                  |                               | FT and FTf I/O               | -                                              | -                      | 0.475 V <sub>DDIOx</sub> -0.2 <sup>(1)</sup> |      |

| V <sub>IL</sub>  | Low level input<br>voltage    | BOOT0                        | -                                              | -                      | 0.3 V <sub>DDIOx</sub> -0.3 <sup>(1)</sup>   | V    |

|                  |                               | All I/Os except<br>BOOT0 pin | -                                              | -                      | 0.3 V <sub>DDIOx</sub>                       |      |

|                  |                               | TC and TTa I/O               | 0.445 V <sub>DDIOx</sub> +0.398 <sup>(1)</sup> | -                      | -                                            |      |

|                  | High level input              | FT and FTf I/O               | 0.5 V <sub>DDIOx</sub> +0.2 <sup>(1)</sup>     | -                      | -                                            |      |

| V <sub>IH</sub>  | voltage                       | BOOT0                        | 0.2 V <sub>DDIOx</sub> +0.95 <sup>(1)</sup>    | -                      | -                                            | V    |

|                  |                               | All I/Os except<br>BOOT0 pin | 0.7 V <sub>DDIOx</sub>                         | -                      | -                                            |      |

|                  |                               | TC and TTa I/O               | -                                              | - 200 <sup>(1)</sup> - |                                              |      |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis | FT and FTf I/O               | -                                              | 100 <sup>(1)</sup>     | -                                            | mV   |

|                  | , - · - · - · -               | BOOT0                        | -                                              | 300 <sup>(1)</sup>     | -                                            |      |

| Table 46. I/O static | characteristics |

|----------------------|-----------------|

|----------------------|-----------------|

## **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 18: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 18: Voltage characteristics*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                                  | Min                     | Max | Unit   |

|-----------------------------------|------------------------------------------------------------|-------------------------------------------------------------|-------------------------|-----|--------|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 8 mA                                    | -                       | 0.4 | v<br>v |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥2.7 V                                   | V <sub>DDIOx</sub> -0.4 | -   |        |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 20 mA                                   | -                       | 1.3 |        |

| V <sub>OH</sub> <sup>(2)</sup>    | Output high level voltage for an I/O pin                   | $V_{DDIOx} \ge 2.7 V$                                       | V <sub>DDIOx</sub> -1.3 | -   |        |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                    | ll   _ 6 m 4                                                | -                       | 0.4 | V      |

| V <sub>OH</sub> <sup>(2)</sup>    | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 6 mA                                    | V <sub>DDIOx</sub> -0.4 | -   | V      |

| V <sub>OLFm+</sub> <sup>(2)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | $ I_{IO}  = 20 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$ | -                       | 0.4 | V      |

|                                   |                                                            | I <sub>IO</sub>   = 10 mA                                   | -                       | 0.4 | V      |

### Table 47. Output voltage characteristics<sup>(1)</sup>

1. The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in *Table 18: Voltage characteristics*, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings  $\Sigma I_{IO}$ .

2. Data based on characterization results. Not tested in production.

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 20* and *Table 48*, respectively.

Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                                          | Min | Max  | Unit |

|----------------------------------------|-------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|-----|------|------|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                      | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥2.4 V                   | -   | 2    | MHz  |

| x0                                     | t <sub>f(IO)out</sub>   | Output fall time                                                      |                                                                     | -   | 125  | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                                                      | ]                                                                   |     | 125  | 115  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                      |                                                                     | -   | 10   | MHz  |

| 01                                     | t <sub>f(IO)out</sub>   | Output fall time                                                      | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.4 \text{ V}$                  | -   | 25   | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                                                      |                                                                     | -   | 25   |      |

|                                        |                         |                                                                       | $C_L = 30 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                  | -   | - 50 |      |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                      | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                  | -   | 30   | MHz  |

|                                        |                         |                                                                       | $C_L = 50 \text{ pF}, 2.4 \text{ V} \leq V_{DDIOx} < 2.7 \text{ V}$ | -   | 20   |      |

|                                        | t <sub>f(IO)out</sub>   | Output fall time<br>Output rise time                                  | $C_L = 30 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                  | -   | 5    | ns   |

| 11                                     |                         |                                                                       | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                  | -   | 8    |      |

|                                        |                         |                                                                       | $C_L$ = 50 pF, 2.4 V $\leq$ V <sub>DDIOx</sub> < 2.7 V              | -   | 12   |      |

|                                        |                         |                                                                       | $C_L = 30 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                  | -   | 5    |      |

|                                        | t <sub>r(IO)out</sub>   |                                                                       | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                  | -   | 8    |      |

|                                        |                         |                                                                       | $C_L = 50 \text{ pF}, 2.4 \text{ V} \leq V_{DDIOx} < 2.7 \text{ V}$ | -   | 12   |      |

| Fm+                                    | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                      |                                                                     |     | 2    | MHz  |

| configuration                          | t <sub>f(IO)out</sub>   | Output fall time                                                      | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.4 \text{ V}$                  | -   | 12   |      |

| (4)                                    | t <sub>r(IO)out</sub>   | Output rise time                                                      | 1                                                                   |     | 34   | ns   |

| -                                      | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller | -                                                                   | 10  | -    | ns   |

Table 48. I/O AC characteristics<sup>(1)(2)</sup>

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the STM32F0xxxx RM0360 reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design, not tested in production.

3. The maximum frequency is defined in *Figure 20*.

When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the STM32F0xxxx reference manual RM0360 for a detailed description of Fm+ I/O configuration.

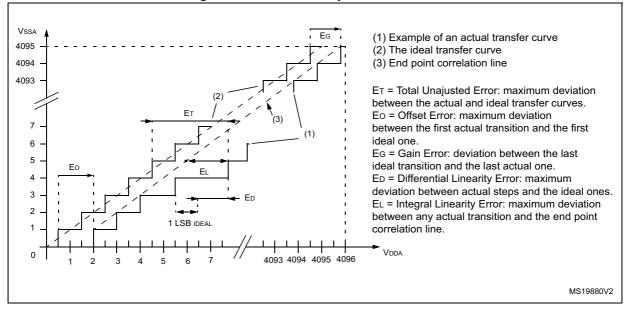

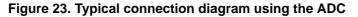

#### Figure 22. ADC accuracy characteristics

1. Refer to Table 50: ADC characteristics for the values of  $R_{AIN}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 12: Power supply scheme*. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$