Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 55                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                             |

| Data Converters            | A/D 18x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f030r8t6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

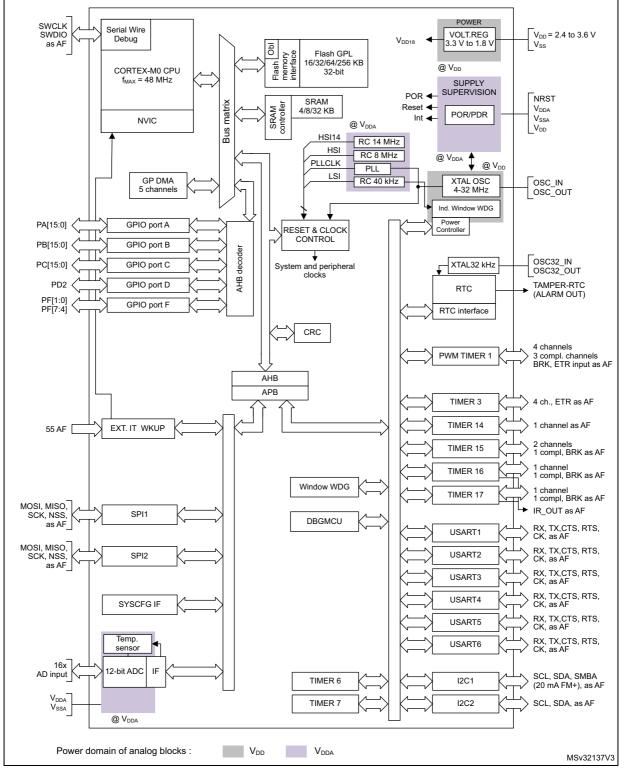

| Figure 1.  | Block diagram                                                        | 11 |

|------------|----------------------------------------------------------------------|----|

| Figure 2.  | Clock tree 1                                                         |    |

| Figure 3.  | LQFP64 64-pin package pinout (top view), for STM32F030x4/6/8 devices | 24 |

| Figure 4.  | LQFP64 64-pin package pinout (top view), for STM32F030RC devices     | 24 |

| Figure 5.  | LQFP48 48-pin package pinout (top view), for STM32F030x4/6/8 devices | 25 |

| Figure 6.  | LQFP48 48-pin package pinout (top view), for STM32F030CC devices     | 25 |

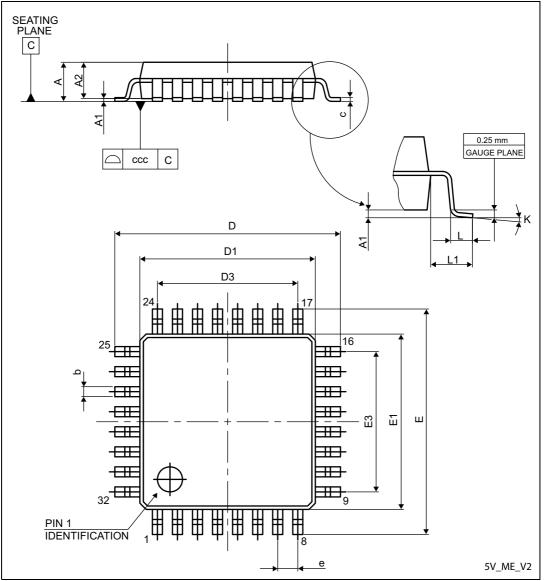

| Figure 7.  | LQFP32 32-pin package pinout (top view)                              |    |

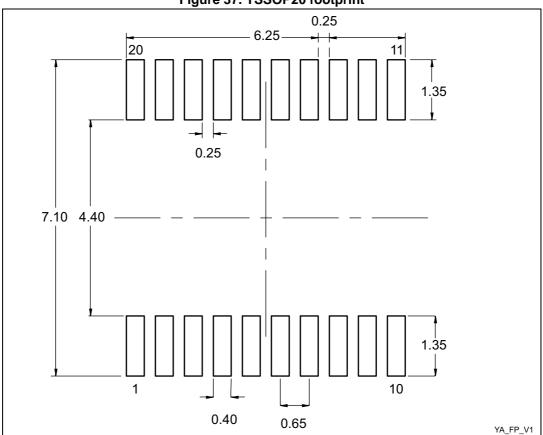

| Figure 8.  | TSSOP20 20-pin package pinout (top view)2                            | 26 |

| Figure 9.  | STM32F030x4/x6/x8/xC memory map                                      | 37 |

| Figure 10. | Pin loading conditions.                                              | 40 |

| Figure 11. | Pin input voltage                                                    | 40 |

| Figure 12. | Power supply scheme                                                  | 11 |

| Figure 13. | Current consumption measurement scheme                               | 41 |

| Figure 14. | High-speed external clock source AC timing diagram                   | 51 |

| Figure 15. | Low-speed external clock source AC timing diagram                    | 52 |

| Figure 16. | Typical application with an 8 MHz crystal                            | 53 |

| Figure 17. | Typical application with a 32.768 kHz crystal                        | 54 |

| Figure 18. | TC and TTa I/O input characteristics6                                |    |

| Figure 19. | Five volt tolerant (FT and FTf) I/O input characteristics            | 32 |

| Figure 20. | I/O AC characteristics definition                                    | 35 |

| Figure 21. | Recommended NRST pin protection                                      | 36 |

| Figure 22. | ADC accuracy characteristics                                         |    |

| Figure 23. | Typical connection diagram using the ADC                             |    |

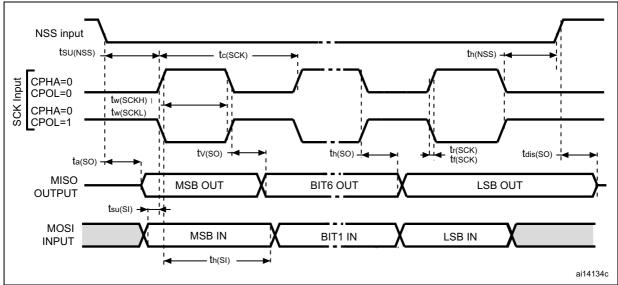

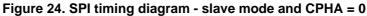

| Figure 24. | SPI timing diagram - slave mode and CPHA = 0                         |    |

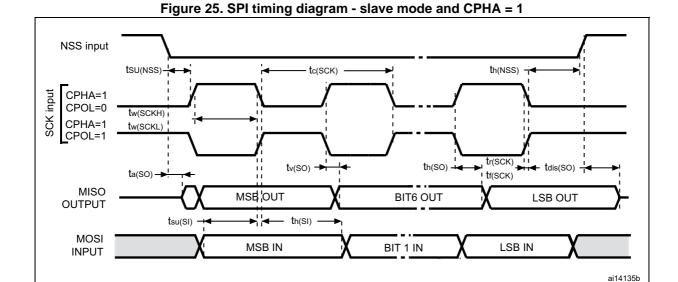

| Figure 25. | SPI timing diagram - slave mode and CPHA = 1                         | 73 |

| Figure 26. | SPI timing diagram - master mode                                     | 74 |

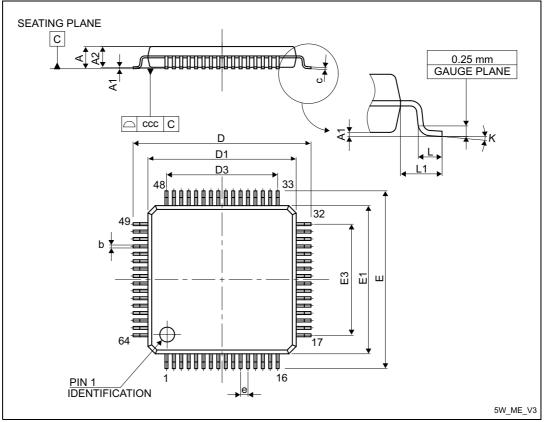

| Figure 27. | LQFP64 outline                                                       | 75 |

| Figure 28. | LQFP64 recommended footprint                                         |    |

| Figure 29. | LQFP64 marking example (package top view)7                           | 77 |

| Figure 30. | LQFP48 outline                                                       |    |

| Figure 31. | LQFP48 recommended footprint                                         |    |

| Figure 32. | LQFP48 marking example (package top view)                            | 30 |

| Figure 33. | LQFP32 outline                                                       |    |

| Figure 34. | LQFP32 recommended footprint                                         |    |

| Figure 35. | LQFP32 marking example (package top view)                            | 33 |

| Figure 36. | TSSOP20 outline                                                      |    |

| Figure 37. | TSSOP20 footprint                                                    |    |

| Figure 38. | TSSOP20 marking example (package top view)                           | 36 |

- 1. TIMER6, TIMER15, SPI, USART2 and I2C2 are available on STM32F030x8/C devices only.

- 2. USART3, USART4, USART5, USART6 and TIMER7 are available on STM32F030xC devices only.

# 3.5.4 Low-power modes

The STM32F030x4/x6/x8/xC microcontrollers support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines and RTC.

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the RTC domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pins, or an RTC event occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

# 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

# 3.8 Direct memory access controller (DMA)

The 5-channel general-purpose DMA manages memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I2C, USART, all TIMx timers (except TIM14) and ADC.

# 3.9 Interrupts and events

# 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of  $Cortex^{\mbox{\tiny B}}$ -M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

# 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 55 GPIOs can be connected to the 16 external interrupt lines.

# 3.13 Inter-integrated circuit interfaces (I<sup>2</sup>C)

Up to two I2C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s) or Fast mode (up to 400 kbit/s). I2C1 also supports Fast Mode Plus (up to 1 Mbit/s), with 20 mA output drive.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

| -                                   | Analog filter                                         | Digital filter                                                                                       |  |  |  |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |  |  |  |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |  |  |  |

| Drawbacks                           | Variations depending on temperature, voltage, process | -                                                                                                    |  |  |  |

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management

The I2C interfaces can be served by the DMA controller.

Refer to Table 7 for the differences between I2C1 and I2C2.

| I2C features                                                 | I2C1 | I2C2 <sup>(2)</sup> |

|--------------------------------------------------------------|------|---------------------|

| 7-bit addressing mode                                        | Х    | Х                   |

| 10-bit addressing mode                                       | Х    | Х                   |

| Standard mode (up to 100 kbit/s)                             | Х    | Х                   |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х                   |

| Fast Mode Plus (up to 1 Mbit/s), with 20mA output drive I/Os | Х    | -                   |

| Independent clock                                            | Х    | -                   |

| SMBus                                                        | Х    | -                   |

| Wakeup from STOP                                             | -    | -                   |

| Table 7. STM32F030x4/x6/x8/xC I <sup>2</sup> C implementation <sup>(1)</sup> |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

1. X = supported.

2. Only available on STM32F030x8/C devices.

# 3.14 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds up to six universal synchronous/asynchronous receivers/transmitters that communicate at speeds of up to 6 Mbit/s.

DocID024849 Rev 3

| Na                                                              | me                   | Abbreviation Definition                                                                                                               |                                                             |  |  |

|-----------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| Pin r                                                           | name                 | Unless otherwise specified in brackets below the pin name, the pin function during and after reset is the same as the actual pin name |                                                             |  |  |

|                                                                 |                      | S                                                                                                                                     | Supply pin                                                  |  |  |

| Pin                                                             | type                 | I                                                                                                                                     | Input only pin                                              |  |  |

|                                                                 |                      | I/O                                                                                                                                   | Input / output pin                                          |  |  |

|                                                                 |                      | FT                                                                                                                                    | 5 V tolerant I/O                                            |  |  |

|                                                                 |                      | FTf                                                                                                                                   | 5 V tolerant I/O, FM+ capable                               |  |  |

| I/O atr                                                         | ucture               | TTa                                                                                                                                   | TTa 3.3 V tolerant I/O directly connected to ADC            |  |  |

| i/O str                                                         | ucture               | TC                                                                                                                                    | Standard 3.3 V I/O                                          |  |  |

|                                                                 |                      | В                                                                                                                                     | Dedicated BOOT0 pin                                         |  |  |

|                                                                 |                      | RST                                                                                                                                   | Bidirectional reset pin with embedded weak pull-up resistor |  |  |

| Notes                                                           |                      | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset.                                     |                                                             |  |  |

| Pin Alternate<br>functions selected through GPIOx_AFR registers |                      |                                                                                                                                       | d through GPIOx_AFR registers                               |  |  |

| functions                                                       | Additional functions | Functions directly selected/enabled through peripheral registers                                                                      |                                                             |  |  |

# Table 11. STM32F030x4/6/8/C pin definitions

| F      | Pin nui | mber   |         |                                       |          | ø     |                     | Pin functions                                              |                                            |  |

|--------|---------|--------|---------|---------------------------------------|----------|-------|---------------------|------------------------------------------------------------|--------------------------------------------|--|

| LQFP64 | LQFP48  | LQFP32 | TSSOP20 | Pin name<br>(function after<br>reset) | Pin type | Notes | Alternate functions | Additional functions                                       |                                            |  |

| 1      | 1       | -      | -       | VDD                                   | S        | -     | -                   | Complementary                                              | power supply                               |  |

| 2      | 2       | -      | -       | PC13                                  | I/O      | тс    | (1)                 | -                                                          | RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT,<br>WKUP2 |  |

| 3      | 3       | -      | -       | PC14-OSC32_IN<br>(PC14)               | I/O      | тс    | (1)                 | -                                                          | OSC32_IN                                   |  |

| 4      | 4       | -      | -       | PC15-OSC32_OUT<br>(PC15)              | I/O      | тс    | (1)                 | -                                                          | OSC32_OUT                                  |  |

| 5      | 5       | 2      | 2       | PF0-OSC_IN<br>(PF0)                   | I/O      | FT    | -                   | I2C1_SDA <sup>(5)</sup>                                    | OSC_IN                                     |  |

| 6      | 6       | 3      | 3       | PF1-OSC_OUT<br>(PF1)                  | I/O      | FT    | -                   | I2C1_SCL <sup>(5)</sup>                                    | OSC_OUT                                    |  |

| 7      | 7       | 4      | 4       | NRST                                  | I/O      | RST   | -                   | Device reset input / internal reset output<br>(active low) |                                            |  |

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 18: Voltage characteristics*, *Table 19: Current characteristics* and *Table 20: Thermal characteristics* may cause permanent damage to the device. These are stress *ratings* only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                                                                        | Ratings                                           | Min                  | Мах                                     | Unit |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------|-----------------------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                                                                                              | External main supply voltage                      | -0.3                 | 4.0                                     | V    |

| V <sub>DDA</sub> -V <sub>SS</sub>                                                                                             | External analog supply voltage                    | -0.3                 | 4.0                                     | V    |

| V <sub>DD</sub> -V <sub>DDA</sub>                                                                                             | Allowed voltage difference for $V_{DD} > V_{DDA}$ | -                    | 0.4                                     | V    |

|                                                                                                                               | Input voltage on FT and FTf pins                  | V <sub>SS</sub> -0.3 | V <sub>DDIOx</sub> + 4.0 <sup>(3)</sup> | V    |

| V <sub>IN</sub> <sup>(2)</sup>                                                                                                | Input voltage on TTa pins                         | V <sub>SS</sub> –0.3 | 4.0                                     | V    |

| VIN'                                                                                                                          | BOOT0                                             | 0                    | V <sub>DDIOx</sub> + 4.0 <sup>(3)</sup> | V    |

|                                                                                                                               | Input voltage on any other pin                    | V <sub>SS</sub> –0.3 | 4.0                                     | V    |

| $ \Delta V_{DDx} $                                                                                                            | Variations between different $V_{DD}$ power pins  | -                    | 50                                      | mV   |

| V <sub>SSx</sub> -V <sub>SS</sub>                                                                                             | Variations between all the different ground pins  | -                    | 50                                      | mV   |

| VESD(HBM)Electrostatic discharge voltage<br>(human body model)see Section 6.3.12: Electrostatic<br>sensitivity characteristic |                                                   |                      | -                                       |      |

| Table 18. Voltage c | haracteristics <sup>(1)</sup> |

|---------------------|-------------------------------|

|---------------------|-------------------------------|

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 19: Current characteristics* for the maximum allowed injected current values.

3.  $V_{DDIOx}$  is internally connected with VDD pin.

| Symbol Parameter                     |                     | Conditions | Min  | Тур  | Max  | Unit |

|--------------------------------------|---------------------|------------|------|------|------|------|

| V <sub>PDRhyst</sub>                 | PDR hysteresis      | -          | -    | 40   | -    | mV   |

| t <sub>RSTTEMPO</sub> <sup>(4)</sup> | Reset temporization | -          | 1.50 | 2.50 | 4.50 | ms   |

#### Table 23. Embedded reset and power control block characteristics (continued)

1. The PDR detector monitors  $V_{DD}$  and also  $V_{DDA}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{DD}.$

2. The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR/PDR}}$  value.

3. Data based on characterization results, not tested in production.

4. Guaranteed by design, not tested in production.

## 6.3.4 Embedded reference voltage

The parameters given in *Table 24* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Table 24. Embedded memai reference voltage |                                                                    |                                |                     |      |                    |        |  |  |

|--------------------------------------------|--------------------------------------------------------------------|--------------------------------|---------------------|------|--------------------|--------|--|--|

| Symbol                                     | Parameter                                                          | Conditions                     | Min                 | Тур  | Max                | Unit   |  |  |

| V <sub>REFINT</sub>                        | Internal reference<br>voltage                                      | -40°C < T <sub>A</sub> < +85°C | 1.2                 | 1.23 | 1.25               | V      |  |  |

| t <sub>START</sub>                         | ADC_IN17 buffer startup time                                       | -                              | -                   | -    | 10 <sup>(1)</sup>  | μs     |  |  |

| t <sub>S_vrefint</sub>                     | ADC sampling time when reading the internal reference voltage      | -                              | 4 <sup>(1)</sup>    | -    | -                  | μs     |  |  |

| $\Delta V_{REFINT}$                        | Internal reference<br>voltage spread over the<br>temperature range | V <sub>DDA</sub> = 3 V         | -                   | -    | 10 <sup>(1)</sup>  | mV     |  |  |

| T <sub>Coeff</sub>                         | Temperature coefficient                                            | -                              | -100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |  |  |

Table 24. Embedded internal reference voltage

1. Guaranteed by design, not tested in production.

# 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

| Symbol          | Parameter                                                           | Conditions                      |                                                                | Typ @V <sub>DD</sub><br>(V <sub>DD</sub> = V <sub>DDA</sub> ) | Max <sup>(1)</sup>     | Unit |    |

|-----------------|---------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------|---------------------------------------------------------------|------------------------|------|----|

|                 |                                                                     |                                 |                                                                | 3.6 V                                                         | T <sub>A</sub> = 85 °C |      |    |

|                 | Supply current in                                                   | Regulator in run mode           | , all oscillators OFF                                          | 19                                                            | 48                     |      |    |

| I <sub>DD</sub> | Stop mode                                                           | Regulator in low-powe           | r mode, all oscillators OFF                                    | 5                                                             | 32                     |      |    |

|                 | Supply current in<br>Standby mode                                   | LSI ON and IWDG ON              |                                                                | 2                                                             | -                      |      |    |

|                 | Supply current in Stop mode                                         |                                 | Regulator in run or low-<br>power mode, all<br>oscillators OFF | 2.9                                                           | 3.5                    |      |    |

|                 | Supply current in Standby mode                                      |                                 | V <sub>DDA</sub> monitoring ON                                 | LSI ON and IWDG ON                                            | 3.3                    | -    | μA |

|                 |                                                                     |                                 | LSI OFF and IWDG OFF                                           | 2.8                                                           | 3.5                    |      |    |

| IDDA            | Supply current in Stop mode                                         |                                 | Regulator in run or low-<br>power mode, all<br>oscillators OFF | 1.7                                                           | -                      |      |    |

|                 | V <sub>DDA</sub> monitoring OF<br>Supply current in<br>Standby mode | V <sub>DDA</sub> monitoring OFF | LSI ON and IWDG ON                                             | 2.3                                                           | -                      |      |    |

|                 |                                                                     |                                 | LSI OFF and IWDG OFF                                           | 1.4                                                           | -                      |      |    |

Table 27. Typical and maximum consumption in Stop and Standby modes

1. Data based on characterization results, not tested in production unless otherwise specified.

# Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins are in analog input configuration

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

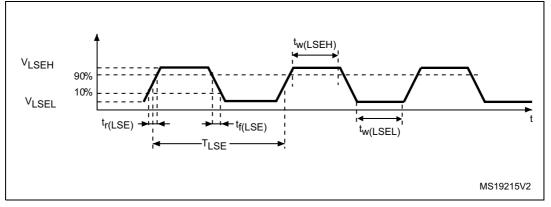

## Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in *Figure 15*.

| Symbol                                       | Parameter <sup>(1)</sup>              | Min                    | Тур    | Мах                    | Unit |

|----------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | $0.7 V_{\text{DDIOx}}$ | -      | V <sub>DDIOx</sub>     | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage  | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | -                      | -      | 50                     | 115  |

Table 32. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### Figure 15. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 33*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol              | Parameter            | Conditions <sup>(1)</sup> | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |  |  |  |

|---------------------|----------------------|---------------------------|--------------------|-----|--------------------|------|--|--|--|

| f <sub>OSC_IN</sub> | Oscillator frequency | -                         | 4                  | 8   | 32                 | MHz  |  |  |  |

| R <sub>F</sub>      | Feedback resistor    | -                         | -                  | 200 | -                  | kΩ   |  |  |  |

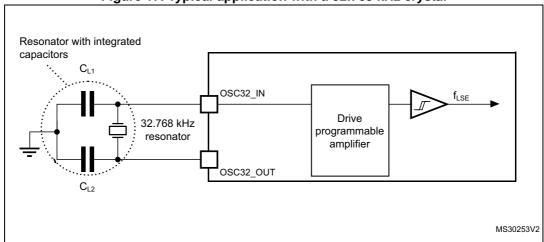

obtained with typical external components specified in *Table 34*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                      | Conditions <sup>(1)</sup>        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|--------------------------------|----------------------------------|--------------------|-----|--------------------|------|

|                                     |                                | low drive capability             | -                  | 0.5 | 0.9                |      |

|                                     | LSE current                    | medium-low drive capability      | -                  | -   | 1                  |      |

| I <sub>DD</sub>                     | consumption                    | medium-high drive capability     | -                  | -   | 1.3                | μA   |

|                                     |                                | high drive capability            | -                  | -   | 1.6                |      |

| g <sub>m</sub>                      | Oscillator<br>transconductance | low drive capability             | 5                  | -   | -                  |      |

|                                     |                                | medium-low drive capability      | 8                  | -   | -                  |      |

|                                     |                                | medium-high drive capability     | 15                 | -   | -                  | μΑ/V |

|                                     |                                | high drive capability            | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                   | V <sub>DDIOx</sub> is stabilized | -                  | 2   | -                  | S    |

Table 34. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

#### Figure 17. Typical application with a 32.768 kHz crystal

Note: An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

Table 37. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | -   | μΑ   |

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 85 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

# 6.3.9 PLL characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Symbol                | Parameter                      |                   | Unit |                    |      |

|-----------------------|--------------------------------|-------------------|------|--------------------|------|

| Symbol                |                                | Min               | Тур  | Max                | Unit |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0  | 24 <sup>(2)</sup>  | MHz  |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %    |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 48                 | MHz  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs   |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps   |

#### Table 38. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

# 6.3.10 Memory characteristics

#### Flash memory

The characteristics are given at  $T_A = -40$  to 85 °C unless otherwise specified.

| Symbol             | Parameter                      | Conditions                     | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|--------------------------------|--------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time        | $T_{A} = -40$ to +85 °C        | -   | 53.5 | -                  | μs   |

| t <sub>ERASE</sub> | Page erase time <sup>(2)</sup> | T <sub>A</sub> = -40 to +85 °C | -   | 30   | -                  | ms   |

| t <sub>ME</sub>    | Mass erase time                | $T_A = -40$ to +85 °C          | -   | 30   | -                  | ms   |

|                    | I <sub>DD</sub> Supply current | Write mode                     | -   | -    | 10                 | mA   |

| DD                 |                                | Erase mode                     | -   | -    | 12                 | mA   |

| V <sub>prog</sub>  | Programming voltage            | -                              | 2.4 | -    | 3.6                | V    |

| Table 39. Flash memory | y characteristics |

|------------------------|-------------------|

|------------------------|-------------------|

1. Guaranteed by design, not tested in production.

2. Page size is 1KB for STM32F030x4/6/8 devices and 2KB for STM32F030xC devices

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol Paran       | Parameter                   | Conditions                                                                                         | Monitored        | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |  |  |  |  |

|--------------------|-----------------------------|----------------------------------------------------------------------------------------------------|------------------|------------------------------------------------|------|--|--|--|--|

|                    | rarameter                   | Conditions                                                                                         | frequency band   | 8/48 MHz                                       | Onit |  |  |  |  |

|                    | S <sub>EMI</sub> Peak level | $V_{DD} = 3.6 \text{ V}, T_A = 25 \text{ °C},$<br>LQFP100 package<br>compliant with<br>IEC 61967-2 | 0.1 to 30 MHz    | -3                                             |      |  |  |  |  |

| 6                  |                             |                                                                                                    | 30 to 130 MHz    | 23                                             | dBµV |  |  |  |  |

| S <sub>EMI</sub> F |                             |                                                                                                    | 130 MHz to 1 GHz | 17                                             |      |  |  |  |  |

|                    |                             |                                                                                                    | EMI Level        | 4                                              | -    |  |  |  |  |

#### Table 42. EMI characteristics

## 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### **Electrostatic discharge (ESD)**

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 18: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 18: Voltage characteristics*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                                  | Min                     | Max | Unit |

|-----------------------------------|------------------------------------------------------------|-------------------------------------------------------------|-------------------------|-----|------|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 8 mA                                    | -                       | 0.4 | V    |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥2.7 V                                   | V <sub>DDIOx</sub> -0.4 | -   | v    |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 20 mA                                   | -                       | 1.3 | V    |

| V <sub>OH</sub> <sup>(2)</sup>    | Output high level voltage for an I/O pin                   | $V_{DDIOx} \ge 2.7 V$                                       | V <sub>DDIOx</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                    | ll   _ 6 m 4                                                | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(2)</sup>    | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 6 mA                                    | V <sub>DDIOx</sub> -0.4 | -   | v    |

| V <sub>OLFm+</sub> <sup>(2)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | $ I_{IO}  = 20 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$ | -                       | 0.4 | V    |

|                                   |                                                            | I <sub>IO</sub>   = 10 mA                                   | -                       | 0.4 | V    |

#### Table 47. Output voltage characteristics<sup>(1)</sup>

1. The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in *Table 18: Voltage characteristics*, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings  $\Sigma I_{IO}$ .

2. Data based on characterization results. Not tested in production.

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 20* and *Table 48*, respectively.

Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |  |  |

|-------------------|--------------|--------------------------------|--------------------------------|------|--|--|

| /4                | 0            | 0.1                            | 409.6                          |      |  |  |

| /8                | 1            | 0.2                            | 819.2                          |      |  |  |

| /16               | 2            | 0.4                            | 1638.4                         |      |  |  |

| /32               | 3            | 0.8                            | 3276.8                         | ms   |  |  |

| /64               | 4            | 1.6                            | 6553.6                         |      |  |  |

| /128              | 5            | 3.2                            | 13107.2                        |      |  |  |

| /256              | 6 or 7       | 6.4                            | 26214.4                        |      |  |  |

Table 55. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

1. These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value | Max timeout value | Unit |

|-----------|-------|-------------------|-------------------|------|

| 1         | 0     | 0.0853            | 5.4613            |      |

| 2         | 1     | 0.1706            | 10.9226           | me   |

| 4         | 2     | 0.3413            | 21.8453           | ms   |

| 8         | 3     | 0.6826            | 43.6906           |      |

Table 56. WWDG min/max timeout value at 48 MHz (PCLK)

# 6.3.19 Communication interfaces

## I<sup>2</sup>C interface characteristics

The I2C interface meets the timings requirements of the  $I^2$ C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I2C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I2C I/Os characteristics.

All I2C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 7.1 LQFP64 package information

LQFP64 is 64-pin, 10 x 10 mm low-profile quad flat package.

1. Drawing is not to scale.

Table 59. LQFP64 mechanical data

| Symbol |       |       | inches <sup>(1)</sup> |        |        |        |

|--------|-------|-------|-----------------------|--------|--------|--------|

| Symbol | Min   | Тур   | Max                   | Min    | Тур    | Max    |

| A      | -     | -     | 1.600                 | -      | -      | 0.0630 |

| A1     | 0.050 | -     | 0.150                 | 0.0020 | -      | 0.0059 |

| A2     | 1.350 | 1.400 | 1.450                 | 0.0531 | 0.0551 | 0.0571 |

# 7.3 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package

Figure 33. LQFP32 outline

1. Drawing is not to scale.

| Table 61. LQFP32 m | nechanical data |

|--------------------|-----------------|

|--------------------|-----------------|

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

|        | Table 02. 10001 20 mechanical data (continued) |      |       |                       |      |        |

|--------|------------------------------------------------|------|-------|-----------------------|------|--------|

| Symbol | millimeters                                    |      |       | inches <sup>(1)</sup> |      |        |

| Symbol | Min.                                           | Тур. | Max.  | Min.                  | Тур. | Max.   |

| k      | 0°                                             | -    | 8°    | 0°                    | -    | 8°     |

| aaa    | -                                              | -    | 0.100 | -                     | -    | 0.0039 |

Table 62. TSSOP20 mechanical data (continued)

1. Values in inches are converted from mm and rounded to four decimal digits.

# Figure 37. TSSOP20 footprint

1. Dimensions are expressed in millimeters.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04-Jul-2013 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15-Jan-2015 | 2        | <ul> <li>Extended the applicability to STM32F030xC.</li> <li>Updated: <ul> <li>Features and Table Device summary,</li> <li>Section: Description,</li> <li>Table: STM32F030x4/6/8/C family device features and peripheral counts,</li> <li>Figure: Block diagram,</li> <li>Section: Memories,</li> <li>Section: General-purpose inputs/outputs (GPIOs),</li> <li>Section: Universal synchronous/asynchronous receiver transmitters (USART),</li> <li>Table: STM32F030x4/6/8/C pin definitions,</li> <li>Table: Alternate functions selected through GPIOA_AFR registers for port A,</li> <li>Table: Alternate functions selected through GPIOB_AFR registers for port B</li> <li>Table: Alternate functions selected through GPIOD_AFR registers for port C</li> <li>Table: Alternate functions selected through GPIOD_AFR registers for port C,</li> <li>Table: Alternate functions selected through GPIOD_AFR registers for port C,</li> <li>Table: Alternate functions selected through GPIOD_AFR registers for port D,</li> <li>Table: Alternate functions selected through GPIOD_AFR registers for port D,</li> <li>Table: Alternate functions selected through GPIOD_AFR registers for port D,</li> <li>Table: Alternate functions selected through GPIOF_AFR registers for port F,</li> <li>Section: EMC characteristics,</li> <li>Section: EMC characteristics,</li> <li>Section: Part numbering.</li> <li>Added device marking example (package top view),</li> <li>Figure: LQFP48 marking example (package top view),</li> <li>Figure: TSSOP20 marking example (package top view),</li> </ul> </li> </ul> |

| 23-Jan-2017 | 3        | <ul> <li>Updated:</li> <li>Table 2: STM32F030x4/x6/x8/xC family device features and peripheral counts</li> <li>Figure 1: Block diagram and figure footnotes</li> <li>Figure 2: Clock tree and figure footnotes</li> <li>Section 3.11: Timers and watchdogs - number of timers, counts of complementary outputs in the table and the footnotes</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Table 65. Document revision history