Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 24MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                 |

| Data Converters            | A/D 4x14b; D/A 4x9b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 8-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c27143-24pxi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article "How to Design with PSoC<sup>®</sup> 1, PowerPSoC<sup>®</sup>, and PLC – KBA88292". Following is an abbreviated list for PSoC 1:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP

- In addition, PSoC Designer includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 1 are:

- □ Getting Started with PSoC<sup>®</sup> 1 AN75320

- □ PSoC<sup>®</sup> 1 Getting Started with GPIO AN2094

- □ PSoC<sup>®</sup> 1 Analog Structure and Configuration AN74170

- □ PSoC<sup>®</sup> 1 Switched Capacitor Analog Blocks AN2041

- Selecting Analog Ground and Reference AN2219

**Note:** For CY8C27X43 devices related Application note please click here.

- Development Kits:

- CY3210-PSoCEval1 supports all PSoC 1 Mixed-Signal Array families, including automotive, except CY8C25/26xxx devices. The kit includes an LCD module, potentiometer, LEDs, and breadboarding space.

- CY3214-PSoCEvalUSB features a development board for the CY8C24x94 PSoC device. Special features of the board include USB and CapSense development and debugging support.

**Note:** For CY8C27X43 devices related Development Kits please click here.

The MiniProg1 and MiniProg3 devices provide interfaces for flash programming and debug.

## **PSoC Designer**

PSoC Designer is a free Windows-based Integrated Design Environment (IDE). Develop your applications using a library of pre-characterized analog and digital peripherals in a drag-and-drop design environment. Then, customize your design leveraging the dynamically generated API libraries of code. Figure 1 shows PSoC Designer windows. **Note:** This is not the default view.

- 1. Global Resources all device hardware settings.

- 2. **Parameters –** the parameters of the currently selected User Modules.

- 3. Pinout information related to device pins.

- 4. Chip-Level Editor a diagram of the resources available on the selected chip.

- 5. Datasheet the datasheet for the currently selected UM

- 6. User Modules all available User Modules for the selected device.

- 7. **Device Resource Meter –** device resource usage for the current project configuration.

- 8. Workspace a tree level diagram of files associated with the project.

- 9. Output output from project build and debug operations.

**Note:** For detailed information on PSoC Designer, go to PSoC<sup>®</sup> Designer > Help > Documentation > Designer Specific Documents > IDE User Guide.

### Figure 1. PSoC Designer Layout

## **PSoC Functional Overview**

The PSoC family consists of many programmable system-on-chip controller devices. These devices are designed to replace multiple traditional microcontroller unit (MCU)-based components with low-cost system one, single-chip programmable device. PSoC devices include configurable blocks of analog and digital logic, as well as programmable interconnects. This architecture lets you to create customized peripheral configurations that match the requirements of each individual application. Additionally, a fast central processing unit (CPU), flash program memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts and packages.

The PSoC architecture, as illustrated in Logic Block Diagram on page 1, consists of four main areas: PSoC core, digital system, analog system, and system resources. Configurable global busing allows all the device resources to be combined into a complete custom system. The PSoC CY8C27x43 family can have up to five I/O ports that connect to the global digital and analog interconnects, providing access to eight digital blocks and 12 analog blocks.

### **PSoC Core**

The PSoC core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable GPIO.

The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a four MIPS 8-bit Harvard architecture microprocessor. The CPU uses an interrupt controller with 17 vectors, to simplify programming of real time embedded events. Program execution is timed and protected using the included sleep and watchdog timers (WDT).

Memory encompasses 16 KB of flash for program storage, 256 bytes of SRAM for data storage, and up to 2 K of EEPROM emulated using the flash. Program flash uses four protection levels on blocks of 64 bytes, allowing customized software IP protection.

The PSoC device incorporates flexible internal clock generators, including a 24-MHz internal main oscillator (IMO) accurate to 2.5% over temperature and voltage. The 24-MHz IMO can also be doubled to 48 MHz for use by the digital system. A low power 32-kHz internal low speed oscillator (ILO) is provided for the sleep timer and WDT. If crystal accuracy is desired, the 32.768-kHz external crystal oscillator (ECO) is available for use as a Real Time Clock (RTC) and can optionally generate a crystal-accurate 24-MHz system clock using a PLL. The clocks, together with programmable clock dividers (as a system resource), provide the flexibility to integrate almost any timing requirement into the PSoC device.

PSoC GPIOs provide connection to the CPU, digital and analog resources of the device. Each pin's drive mode may be selected from eight options, allowing great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

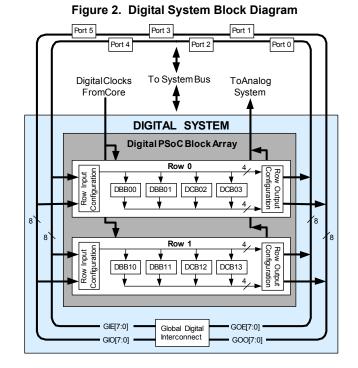

### **Digital System**

The digital system is composed of eight digital PSoC blocks. Each block is an 8-bit resource that can be used alone or combined with other blocks to form 8-, 16-, 24-, and 32-bit peripherals, which are called user modules.

Digital peripheral configurations include:

- PWMs (8- and 16-bit)

- PWMs with dead band (8- and 16-bit)

- Counters (8- to 32-bit)

- Timers (8- to 32-bit) [1, 2]

- UART 8-bit with selectable parity (up to two)

- SPI slave and master (up to two) [3]

- I<sup>2</sup>C slave and multi-master (one available as a system resource)

- CRC/generator (8- to 32-bit)

- IrDA (up to two)

- Pseudo random sequence (PRS) generators (8- to 32-bit)

#### Notes

- 1. Errata: When operated between 4.75 V to 5.25 V, the input capture signal cannot be sourced from Row Output signals or the Broadcast clock signals. This problem has been fixed in silicon Rev B. For more information, see "Errata" on page 61.

- Errata: When operated between 3.0V to 4.75V, the input capture signal can only be sourced from Row input signal that has been re-synchronized. This problem has been fixed in silicon Rev B. For more information, see "Errata" on page 61.

Errata: Development of the problem has been fixed in silicon Rev B. For more information, see "Errata" on page 61.

Errata: In PSoC, when one output of one SPI Slave block is connected to the input of other SPI slave block, data is shifted correctly but last bit is read incorrectly. For the workaround and more information related to this problem, see "Errata" on page 61.

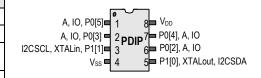

# **Pinouts**

The CY8C27x43 PSoC device is available in a variety of packages which are listed and illustrated in the following tables. Every port pin (labeled with a "P") is capable of Digital I/O. However, Vss,  $V_{DD}$ , SMP, and XRES are not capable of Digital I/O.

### 8-pin Part Pinout

#### Table 2. Pin Definitions – 8-pin PDIP

| Pin   | Ту      | ре            | Pin             | Description                                                                             |

|-------|---------|---------------|-----------------|-----------------------------------------------------------------------------------------|

| No.   | Digital | Analog        | Name            | Description                                                                             |

| 1     | I/O     | I/O           | P0[5]           | Analog column mux input and column output                                               |

| 2     | I/O I/O |               | P0[3]           | Analog column mux input and column output                                               |

| 3     | I/O     |               | P1[1]           | Crystal Input (XTALin), I <sup>2</sup> C serial clock (SCL), ISSP-SCLK <sup>[6]</sup>   |

| 4     | Power   |               | Vss             | Ground connection.                                                                      |

| 5     | I/O     |               | P1[0]           | Crystal output (XTALout), I <sup>2</sup> C serial data (SDA), ISSP-SDATA <sup>[6]</sup> |

| 6     | I/O     | I/O I/O P     |                 | Analog column mux input and column output                                               |

| 7     | I/O     | I/O I/O P0[4] |                 | Analog column mux input and column output                                               |

| 8     | Power V |               | V <sub>DD</sub> | Supply voltage                                                                          |

| I FGF |         | nalog I = I   | nnut and        | $\Omega = \Omega utput$                                                                 |

Figure 4. CY8C27143 8-pin PSoC Device

**END**: A = Analog, I = Input, and O = Output.

### 20-pin Part Pinout

### Table 3. Pin Definitions – 20-pin SSOP, SOIC

| Pin | Ту      | pe           | Pin             | Description                                                               |       |                                    |

|-----|---------|--------------|-----------------|---------------------------------------------------------------------------|-------|------------------------------------|

| No. | Digital | Analog       | Name            | Description                                                               |       |                                    |

| 1   | I/O     | I            | P0[7]           | Analog column mux input                                                   |       |                                    |

| 2   | I/O     | I/O          | P0[5]           | Analog column mux input and column output                                 |       |                                    |

| 3   | I/O I/O |              | P0[3]           | Analog column mux input and column output                                 |       |                                    |

| 4   | I/O     | I            | P0[1]           | Analog column mux input                                                   |       |                                    |

| 5   | Po      | wer          | SMP             | Switch Mode Pump (SMP) connection to external<br>components required      |       |                                    |

| 6   | I/O     |              | P1[7]           | I <sup>2</sup> C Serial Clock (SCL)                                       |       |                                    |

| 7   | I/O     |              | I/O             |                                                                           | P1[5] | I <sup>2</sup> C Serial Data (SDA) |

| 8   | I/O     |              | P1[3]           |                                                                           |       |                                    |

| 9   | I/O     |              | P1[1]           | Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[6]</sup>    |       |                                    |

| 10  | Power   |              | Vss             | Ground connection.                                                        |       |                                    |

| 11  | I/O     |              | P1[0]           | Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[6]</sup> |       |                                    |

| 12  | I/O     |              | P1[2]           |                                                                           |       |                                    |

| 13  | I/O     |              | P1[4]           | Optional external clock input (EXTCLK)                                    |       |                                    |

| 14  | I/O     |              | P1[6]           |                                                                           |       |                                    |

| 15  | Input   |              | XRES            | Active high external reset with internal pull down                        |       |                                    |

| 16  | I/O I   |              | P0[0]           | Analog column mux input                                                   |       |                                    |

| 17  | I/O     | I/O I/O P0[2 |                 | Analog column mux input and column output                                 |       |                                    |

| 18  | I/O     | I/O          | P0[4]           | Analog column mux input and column output                                 |       |                                    |

| 19  | I/O     | I            | P0[6]           | Analog column mux input                                                   |       |                                    |

| 20  | Po      | wer          | V <sub>DD</sub> | Supply voltage                                                            |       |                                    |

Figure 5. CY8C27243 20-pin PSoC Device

LEGEND: A = Analog, I = Input, and O = Output.

#### Note

6. These are the ISSP pins, which are not High Z at POR (Power On Reset). See the PSoC Programmable System-on-Chip Technical Reference Manual for details.

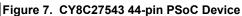

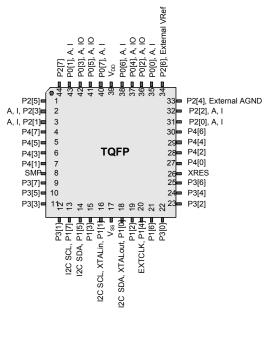

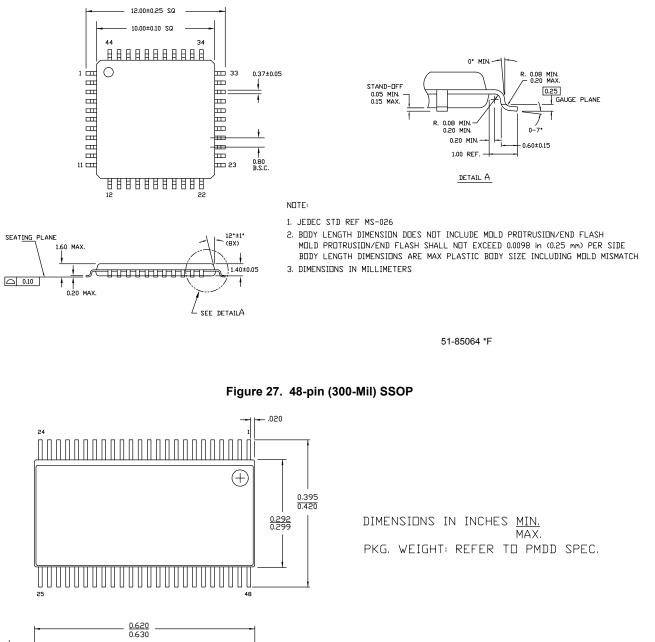

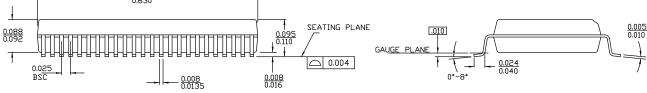

### 44-pin Part Pinout

### Table 5. Pin Definitions – 44-pin TQFP

| No.         Digital         Analog           1         I/O         P2[5]           2         I/O         I         P2[1]           3         I/O         I         P2[1]           4         I/O         P4[7]           5         I/O         P4[3]           6         I/O         P4[3]           7         I/O         P4[1]           8         Power         SMP           9         I/O         P3[7]           10         I/O         P3[3]           11         I/O         P3[3]           12         I/O         P3[1]           13         I/O         P1[7]           14         I/O         P3[3]           15         I/O         P1[7]           16         I/O         P1[3]           16         I/O         P1[1]           17         Power         Vss           18         I/O         P1[2]           20         I/O         P1[4]           0ptional external clock input (EXTCLK)           21         I/O         P1[6]           22         I/O         P3[2]           23 </th <th>Pin</th> <th>Ту</th> <th>ре</th> <th>Pin Name</th> <th>Description</th>                                                                                                                                                                                                   | Pin | Ту      | ре     | Pin Name        | Description                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|--------|-----------------|------------------------------------------------------------------------------|

| 2         I/O         I         P2[3]         Direct switched capacitor block input           3         I/O         I         P2[1]         Direct switched capacitor block input           4         I/O         P4[7]         Direct switched capacitor block input           5         I/O         P4[5]         End           6         I/O         P4[1]         Patas           7         I/O         P4[1]         Patas           8         Power         SMP         SMP connection to external components require           9         I/O         P3[5]         Patas         Patas           11         I/O         P3[3]         Patas         Patas           12         I/O         P3[1]         I/C SCL         Patas           13         I/O         P1[7]         I/C SCL         Patas           14         I/O         P1[5]         I/C SDA         Patas           15         I/O         P1[3]         I/C SCL, ISSP-SCLK <sup>[8]</sup> 16         I/O         P1[1]         Crystal output (XTALout), I/C SDA, ISSP-SDATa <sup>[8]</sup> 18         I/O         P1[2]         Patas         Patas           20         I/O         P1[4] <t< th=""><th>No.</th><th>Digital</th><th>Analog</th><th>Pin Name</th><th>Description</th></t<>                       | No. | Digital | Analog | Pin Name        | Description                                                                  |

| 3         I/O         I         P2[1]         Direct switched capacitor block input           4         I/O         P4[7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1   | I/O     |        | P2[5]           |                                                                              |

| 4         I/O         P4[7]           5         I/O         P4[5]           6         I/O         P4[5]           6         I/O         P4[1]           7         I/O         P4[1]           8         Power         SMP           9         I/O         P3[7]           10         I/O         P3[5]           11         I/O         P3[3]           12         I/O         P3[1]           13         I/O         P1[5]           14         I/O         P1[5]           15         I/O         P1[5]           16         I/O         P1[1]           17         Power         Vss           18         I/O         P1[2]           20         I/O         P1[2]           20         I/O         P1[4]           19         I/O         P1[2]           20         I/O         P1[4]           21         I/O         P1[4]           23         I/O         P3[2]           24         I/O         P3[4]           25         I/O         P3[6]           26         Input                                                                                                                                                                                                                                                                                                        | 2   | I/O     | I      | P2[3]           | Direct switched capacitor block input                                        |

| 5         I/O         P4[5]           6         I/O         P4[3]           7         I/O         P4[1]           8         Power         SMP           9         I/O         P3[5]           11         I/O         P3[5]           11         I/O         P3[5]           11         I/O         P3[3]           12         I/O         P3[1]           13         I/O         P1[7]           14         I/O         P1[5]           15         I/O         P1[1]           16         I/O         P1[1]           17         Power         Vss           18         I/O         P1[2]           20         I/O         P1[2]           20         I/O         P1[4]           21         I/O         P1[6]           22         I/O         P3[4]           23         I/O         P3[4]           24         I/O         P3[4]           25         I/O         P3[6]           26         Input         XRES           Active high external reset with internal pull dow           27         I/O                                                                                                                                                                                                                                                                                  | 3   | I/O     | I      | P2[1]           | Direct switched capacitor block input                                        |

| 6         I/O         P4[3]           7         I/O         P4[1]           8         Power         SMP         SMP connection to external components require           9         I/O         P3[7]         Interval         SMP connection to external components require           10         I/O         P3[5]         Interval         Interval         Interval           11         I/O         P3[3]         Interval         Interval         Interval           12         I/O         P3[1]         Interval         Interval         Interval         Interval           13         I/O         P1[5]         I²C SCL         Interval         Interval         Interval           14         I/O         P1[6]         Crystal input (XTALin), I²C SCL, ISSP-SCLK <sup>[8]</sup> Interval         Interval         Interval           16         I/O         P1[1]         Crystal output (XTALin), I²C SDA, ISSP-SDAR         ISSP-SDATA <sup>[8]</sup> Interval           | 4   | I/O     |        |                 |                                                                              |

| 7         I/O         P4[1]           8         Power         SMP         SMP connection to external components require           9         I/O         P3[7]         10           10         I/O         P3[7]         11           11         I/O         P3[3]         12           12         I/O         P3[1]         11           13         I/O         P1[7]         I <sup>2</sup> C SCL           14         I/O         P1[5]         I <sup>2</sup> C SCL           14         I/O         P1[3]         16           16         I/O         P1[1]         Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 17         Power         Vss         Ground connection.           18         I/O         P1[0]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]         20         I/O           20         I/O         P1[4]         Optional external clock input (EXTCLK)           21         I/O         P3[6]         23           23         I/O         P3[6]         24           24         I/O         P3[6]         25           25         I/O         P4[4]         30 </td <td>5</td> <td>I/O</td> <td></td> <td>P4[5]</td> <td></td>                                        | 5   | I/O     |        | P4[5]           |                                                                              |

| 8         Power         SMP         SMP connection to external components require           9         I/O         P3[7]         10         I/O         P3[5]           11         I/O         P3[3]         12         I/O         P3[1]           13         I/O         P1[7]         I <sup>2</sup> C SCL         14         I/O         P1[5]         I <sup>2</sup> C SDA           15         I/O         P1[3]         16         I/O         P1[1]         Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 16         I/O         P1[1]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 18         I/O         P1[2]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]         Optional external clock input (EXTCLK)           21         I/O         P1[6]         22           23         I/O         P3[2]         24           24         I/O         P3[6]         26           25         I/O         P3[6]         26           26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]         28         I/O         P4[2]           29                                   | 6   | I/O     |        | P4[3]           |                                                                              |

| 9         I/O         P3[7]           10         I/O         P3[5]           11         I/O         P3[3]           12         I/O         P3[1]           13         I/O         P1[7]         I <sup>2</sup> C SCL           14         I/O         P1[5]         I <sup>2</sup> C SDA           15         I/O         P1[3]           16         I/O         P1[1]         Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 17         Power         Vss         Ground connection.           18         I/O         P1[2]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]         Optional external clock input (EXTCLK)           21         I/O         P1[6]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 22         I/O         P1[2]         Optional external clock input (EXTCLK)           23         I/O         P3[6]         Category           24         I/O         P3[6]         Category           25         I/O         P3[6]         Category           26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[6]                                                 | 7   | I/O     |        | P4[1]           |                                                                              |

| 10         I/O         P3[5]           11         I/O         P3[3]           12         I/O         P3[1]           13         I/O         P1[7]         I <sup>2</sup> C SCL           14         I/O         P1[5]         I <sup>2</sup> C SDA           15         I/O         P1[3]           16         I/O         P1[1]         Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 17         Power         Vss         Ground connection.           18         I/O         P1[0]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]         Optional external clock input (EXTCLK)           21         I/O         P1[6]         Crystal output (XTALin), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 22         I/O         P1[6]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 23         I/O         P1[4]         Optional external clock input (EXTCLK)           24         I/O         P3[6]         Categet P3[6]           25         I/O         P3[6]         Categet P3[6]           26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]         Categet P3[6] | 8   | Pov     | wer    | SMP             | SMP connection to external components required                               |

| 11         I/O         P3[3]           12         I/O         P3[1]           13         I/O         P1[7]         I <sup>2</sup> C SCL           14         I/O         P1[5]         I <sup>2</sup> C SDA           15         I/O         P1[3]           16         I/O         P1[1]         Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 17         Power         Vss         Ground connection.           18         I/O         P1[0]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]            20         I/O         P1[4]         Optional external clock input (EXTCLK)           21         I/O         P1[6]            22         I/O         P3[0]            23         I/O         P3[2]            24         I/O         P3[4]            25         I/O         P3[6]            26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]            28         I/O         P4[2]            29         I/O                                                                                                                                                                                         | 9   | I/O     |        | P3[7]           |                                                                              |

| 12I/OP3[1]13I/OP1[7]I²C SCL14I/OP1[5]I²C SDA15I/OP1[3]16I/OP1[1]Crystal input (XTALin), I²C SCL, ISSP-SCLK <sup>[8]</sup> 17PowerVssGround connection.18I/OP1[0]Crystal output (XTALout), I²C SDA,19I/OP1[2]20I/OP1[4]20I/OP1[6]22I/OP3[0]23I/OP3[2]24I/OP3[4]25I/OP3[6]26InputXRESActive high external reset with internal pull dow27I/OP4[0]28I/OP4[6]31I/OP4[6]31I/OP2[2]24I/OP4[6]31I/OP4[6]33I/OP4[6]33I/OP2[6]External Analog Ground (AGND)34I/OP2[6]35I/OI36I/OI38I/OI38I/OI90[6]Analog column mux input and column output38I/OI90[6]Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10  | I/O     |        | P3[5]           |                                                                              |

| 13I/O $P1[7]$ $I^2C$ SCL14I/O $P1[5]$ $I^2C$ SDA15I/O $P1[3]$ 16I/O $P1[1]$ Crystal input (XTALin), $I^2C$ SCL, ISSP-SCLK <sup>[8]</sup> 17PowerVssGround connection.18I/O $P1[0]$ Crystal output (XTALout), $I^2C$ SDA,<br>ISSP-SDATA <sup>[8]</sup> 19I/O $P1[2]$ 20I/O $P1[4]$ 20I/O $P1[6]$ 22I/O $P3[0]$ 23I/O $P3[2]$ 24I/O $P3[4]$ 25I/O $P3[6]$ 26InputXRESXRESActive high external reset with internal pull dow27I/O $P4[6]$ 30I/O $P4[4]$ 30I/O $P4[6]$ 31I/O $P2[2]$ Direct switched capacitor block input33I/O $P2[4]$ 34I/O $P2[6]$ 35I/OI36I/OI37I/OI38I/OI38I/OI90[6]Analog column mux input38I/OI90[6]Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | I/O     |        |                 |                                                                              |

| 14I/OP1[5]I²C SDA15I/OP1[3]16I/OP1[1]Crystal input (XTALin), I²C SCL, ISSP-SCLK <sup>[8]</sup> 17PowerVssGround connection.18I/OP1[0]Crystal output (XTALout), I²C SDA,<br>ISSP-SDATA <sup>[8]</sup> 19I/OP1[2]20I/OP1[4]21I/OP1[6]22I/OP3[0]23I/OP3[2]24I/OP3[4]25I/OP3[6]26InputXRESActive high external reset with internal pull dow27I/OP4[0]28I/OP4[4]30I/OP4[6]31I/OI32I/OP2[2]Direct switched capacitor block input33I/OP2[6]External Analog Ground (AGND)34I/O35I/OI36I/OP0[2]Analog column mux input36I/O17P0[6]38I/O18P0[6]31I/O33I/O34I/O35I/O36I/O17P0[0]38I/O18P0[6]31I/O33I/O34I/O35I/O36I/O36I/O37I/O38I/O36I/O <td>12</td> <td>I/O</td> <td></td> <td>P3[1]</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12  | I/O     |        | P3[1]           |                                                                              |

| 15         I/O         P1[3]           16         I/O         P1[1]         Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 17         Power         Vss         Ground connection.           18         I/O         P1[0]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]           20         I/O         P1[4]         Optional external clock input (EXTCLK)           21         I/O         P1[6]         22           22         I/O         P3[0]         23           23         I/O         P3[2]         24           24         I/O         P3[6]         26           26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]         28           28         I/O         P4[2]         29           29         I/O         P4[6]         31           31         I/O         I         P2[2]         Direct switched capacitor block input           32         I/O         I         P2[2]         Direct switched capacitor block input           33         I/O         P2[4]         External Analog Ground (AGND)                                                                                        | 13  | I/O     |        | P1[7]           | I <sup>2</sup> C SCL                                                         |

| 16         I/O         P1[1]         Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 17         Power         Vss         Ground connection.           18         I/O         P1[0]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]           20         I/O         P1[4]         Optional external clock input (EXTCLK)           21         I/O         P1[6]         22           22         I/O         P3[0]         23           23         I/O         P3[2]         24           24         I/O         P3[6]         25           26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]         28           28         I/O         P4[2]         29           29         I/O         P4[6]           31         I/O         P2[2]         Direct switched capacitor block input           33         I/O         P2[4]         External Analog Ground (AGND)           34         I/O         P2[6]         External Voltage Reference (VRef)           35         I/O         I         P0[0]         Analog column mux input                                                                                 | 14  | I/O     |        | P1[5]           | I <sup>2</sup> C SDA                                                         |

| 17         Power         Vss         Ground connection.           18         I/O         P1[0]         Crystal output (XTALout), I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]           20         I/O         P1[4]         Optional external clock input (EXTCLK)           21         I/O         P1[6]         22           22         I/O         P3[0]         23           23         I/O         P3[4]         25           24         I/O         P3[6]         26           26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]         28         I/O         P4[2]           29         I/O         P4[4]         30         I/O         P4[6]           31         I/O         P 2[0]         Direct switched capacitor block input           32         I/O         I         P2[0]         Direct switched capacitor block input           33         I/O         P2[4]         External Analog Ground (AGND)         34           34         I/O         P2[6]         External Voltage Reference (VRef)           35         I/O         I         P0[0]         Analog co                                                                                   | 15  | I/O     |        | P1[3]           |                                                                              |

| 18         I/O         P1[0]         Crystal output (XTALout), I <sup>2</sup> C SDA,<br>ISSP-SDATA <sup>[8]</sup> 19         I/O         P1[2]           20         I/O         P1[4]         Optional external clock input (EXTCLK)           21         I/O         P1[6]            22         I/O         P3[0]            23         I/O         P3[2]            24         I/O         P3[4]            25         I/O         P3[6]            26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]            28         I/O         P4[2]            29         I/O         P4[6]            31         I/O         P2[2]         Direct switched capacitor block input           32         I/O         I         P2[2]         Direct switched capacitor block input           33         I/O         P2[4]         External Analog Ground (AGND)           34         I/O         P2[6]         External Voltage Reference (VRef)           35         I/O         I         P0[0]         Analog column mux input                                                                                                                                                                                | 16  | I/O     |        | P1[1]           | Crystal input (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup>       |

| 19         I/O         P1[2]           20         I/O         P1[4]         Optional external clock input (EXTCLK)           21         I/O         P1[6]         P3[0]           23         I/O         P3[2]         P3[2]           24         I/O         P3[6]         P3[6]           26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]         P4[0]           28         I/O         P4[6]         P4[2]           29         I/O         P4[6]         P4[6]           30         I/O         P4[6]         P2[2]           29         I/O         P4[6]         P3[3]           31         I/O         I         P2[0]         Direct switched capacitor block input           32         I/O         I         P2[2]         Direct switched capacitor block input           33         I/O         P2[4]         External Analog Ground (AGND)           34         I/O         P2[6]         External Voltage Reference (VRef)           35         I/O         I         P0[0]         Analog column mux input           36         I/O         I/O         P0[4]                                                                                                                             | 17  | Po      | wer    | Vss             |                                                                              |

| 20         I/O         P1[4]         Optional external clock input (EXTCLK)           21         I/O         P1[6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18  | I/O     |        | P1[0]           | Crystal output (XTALout), I <sup>2</sup> C SDA,<br>ISSP-SDATA <sup>[8]</sup> |

| 21         I/O         P1[6]           22         I/O         P3[0]           23         I/O         P3[2]           24         I/O         P3[6]           25         I/O         P3[6]           26         Input         XRES           27         I/O         P4[0]           28         I/O         P4[2]           29         I/O         P4[4]           30         I/O         P4[6]           31         I/O         P2[2]           29         I/O         P4[6]           31         I/O         P2[2]           33         I/O         P2[2]           33         I/O         P2[4]           34         I/O         P2[6]           External Analog Ground (AGND)         34           34         I/O         P2[6]           External Voltage Reference (VRef)         35           35         I/O         I           36         I/O         I/O           37         I/O         I/O           38         I/O         I           90[6]         Analog column mux input                                                                                                                                                                                                                                                                                                  | 19  | I/O     |        | P1[2]           |                                                                              |

| 22         I/O         P3[0]           23         I/O         P3[2]           24         I/O         P3[4]           25         I/O         P3[6]           26         Input         XRES           27         I/O         P4[0]           28         I/O         P4[2]           29         I/O         P4[4]           30         I/O         P4[6]           31         I/O         I           32         I/O         I           33         I/O         P2[4]           33         I/O         P2[4]           33         I/O         P2[6]           34         I/O         P2[6]           35         I/O         I           36         I/O         P0[0]           36         I/O         I/O           37         I/O         I/O           38         I/O         I           90[6]         Analog column mux input           38         I/O         I                                                                                                                                                                                                                                                                                                                                                                                                                        | 20  | I/O     |        |                 | Optional external clock input (EXTCLK)                                       |

| 23         I/O         P3[2]           24         I/O         P3[4]           25         I/O         P3[6]           26         Input         XRES           27         I/O         P4[0]           28         I/O         P4[2]           29         I/O         P4[6]           30         I/O         P4[6]           31         I/O         I           32         I/O         I           33         I/O         P2[4]           33         I/O         P2[6]           34         I/O         P2[6]           35         I/O         I           36         I/O         P0[0]           36         I/O         I           37         I/O         P0[2]           38         I/O         I           38         I/O         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21  | I/O     |        |                 |                                                                              |

| 24         I/O         P3[4]           25         I/O         P3[6]           26         Input         XRES         Active high external reset with internal pull dow           27         I/O         P4[0]            28         I/O         P4[2]            29         I/O         P4[4]            30         I/O         P4[6]            31         I/O         I         P2[0]         Direct switched capacitor block input           32         I/O         I         P2[2]         Direct switched capacitor block input           33         I/O         P2[4]         External Analog Ground (AGND)           34         I/O         P2[6]         External Voltage Reference (VRef)           35         I/O         I         P0[0]         Analog column mux input           36         I/O         I/O         P0[2]         Analog column mux input and column output           37         I/O         I/O         P0[6]         Analog column mux input                                                                                                                                                                                                                                                                                                               | 22  | I/O     |        | P3[0]           |                                                                              |

| 25I/OP3[6]26InputXRESActive high external reset with internal pull dow27I/OP4[0]28I/OP4[2]29I/OP4[4]30I/OP4[6]31I/OI22I/OI33I/OP2[4]34I/OP2[6]55I/OI92[6]External Analog Ground (AGND)34I/OP2[6]35I/OI90[0]Analog column mux input36I/OI/O90[2]Analog column mux input and column output38I/OI90[6]Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23  | I/O     |        | P3[2]           |                                                                              |

| 26InputXRESActive high external reset with internal pull dow27I/OP4[0]28I/OP4[2]29I/OP4[4]30I/OP4[6]31I/OI22I/OI33I/OP2[4]34I/OP2[6]55I/OI92[6]External Voltage Reference (VRef)35I/OI36I/OI/O90[0]Analog column mux input37I/OI/O38I/OI90[6]Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24  | I/O     |        | P3[4]           |                                                                              |

| 27I/OP4[0]28I/OP4[2]29I/OP4[4]30I/OP4[6]31I/OI32I/OI33I/OP2[2]Direct switched capacitor block input33I/O94P2[4]External Analog Ground (AGND)34I/O92[6]External Voltage Reference (VRef)35I/O1/OP0[0]Analog column mux input36I/O1/OP0[4]Analog column mux input and column output37I/O1/OI90[6]Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25  |         |        | P3[6]           |                                                                              |

| 28       I/O       P4[2]         29       I/O       P4[4]         30       I/O       P4[6]         31       I/O       I       P2[0]       Direct switched capacitor block input         32       I/O       I       P2[2]       Direct switched capacitor block input         33       I/O       P2[4]       External Analog Ground (AGND)         34       I/O       P2[6]       External Voltage Reference (VRef)         35       I/O       I       P0[0]       Analog column mux input         36       I/O       I/O       P0[2]       Analog column mux input and column output         37       I/O       I/O       P0[4]       Analog column mux input         38       I/O       I       P0[6]       Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26  | Inp     | but    |                 | Active high external reset with internal pull down                           |

| 29I/OP4[4]30I/OP4[6]31I/OI32I/OI33I/OP2[2]Direct switched capacitor block input33I/O92[4]External Analog Ground (AGND)34I/O92[6]External Voltage Reference (VRef)35I/O10P0[0]Analog column mux input36I/O1/OP0[2]Analog column mux input and column output37I/O10I90[6]Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27  | I/O     |        | P4[0]           |                                                                              |

| 30       I/O       P4[6]         31       I/O       I       P2[0]       Direct switched capacitor block input         32       I/O       I       P2[2]       Direct switched capacitor block input         33       I/O       P2[4]       External Analog Ground (AGND)         34       I/O       P2[6]       External Voltage Reference (VRef)         35       I/O       I       P0[0]       Analog column mux input         36       I/O       I/O       P0[2]       Analog column mux input and column output         37       I/O       I/O       P0[4]       Analog column mux input         38       I/O       I       P0[6]       Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28  | I/O     |        |                 |                                                                              |

| 31       I/O       I       P2[0]       Direct switched capacitor block input         32       I/O       I       P2[2]       Direct switched capacitor block input         33       I/O       P2[4]       External Analog Ground (AGND)         34       I/O       P2[6]       External Voltage Reference (VRef)         35       I/O       I       P0[0]       Analog column mux input         36       I/O       I/O       P0[2]       Analog column mux input and column output         37       I/O       I/O       P0[4]       Analog column mux input and column output         38       I/O       I       P0[6]       Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29  | I/O     |        | P4[4]           |                                                                              |

| 32     I/O     I     P2[2]     Direct switched capacitor block input       33     I/O     P2[4]     External Analog Ground (AGND)       34     I/O     P2[6]     External Voltage Reference (VRef)       35     I/O     I     P0[0]     Analog column mux input       36     I/O     I/O     P0[2]     Analog column mux input and column output       37     I/O     I/O     P0[4]     Analog column mux input and column output       38     I/O     I     P0[6]     Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30  | I/O     |        | P4[6]           |                                                                              |

| 33     I/O     P2[4]     External Analog Ground (AGND)       34     I/O     P2[6]     External Voltage Reference (VRef)       35     I/O     I     P0[0]     Analog column mux input       36     I/O     I/O     P0[2]     Analog column mux input and column output       37     I/O     I/O     P0[4]     Analog column mux input and column output       38     I/O     I     P0[6]     Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31  | I/O     | I      | P2[0]           | Direct switched capacitor block input                                        |

| 34         I/O         P2[6]         External Voltage Reference (VRef)           35         I/O         I         P0[0]         Analog column mux input           36         I/O         I/O         P0[2]         Analog column mux input and column output           37         I/O         I/O         P0[4]         Analog column mux input and column output           38         I/O         I         P0[6]         Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32  | I/O     | I      |                 | Direct switched capacitor block input                                        |

| 35         I/O         I         P0[0]         Analog column mux input           36         I/O         I/O         P0[2]         Analog column mux input and column output           37         I/O         I/O         P0[4]         Analog column mux input and column output           38         I/O         I         P0[6]         Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | I/O     |        |                 |                                                                              |

| 36         I/O         I/O         P0[2]         Analog column mux input and column output           37         I/O         I/O         P0[4]         Analog column mux input and column output           38         I/O         I         P0[6]         Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |         |        |                 | External Voltage Reference (VRef)                                            |

| 37         I/O         I/O         P0[4]         Analog column mux input and column output           38         I/O         I         P0[6]         Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35  | I/O     | I      | P0[0]           |                                                                              |

| 38 I/O I P0[6] Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36  | I/O     | I/O    |                 | Analog column mux input and column output                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |         | I/O    |                 |                                                                              |

| 39 Power V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38  | I/O     | I      |                 | Analog column mux input                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |         | wer    | V <sub>DD</sub> | Supply voltage                                                               |

| 40 I/O I P0[7] Analog column mux input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -   | -       |        | P0[7]           | - ·                                                                          |

| 41 I/O I/O P0[5] Analog column mux input and column output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41  | I/O     | I/O    |                 | Analog column mux input and column output                                    |

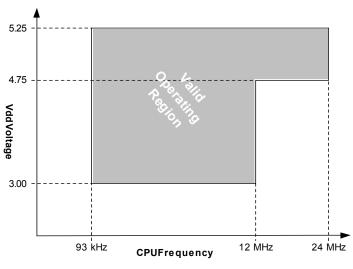

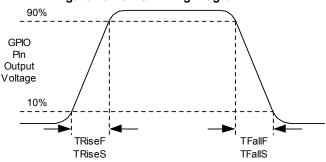

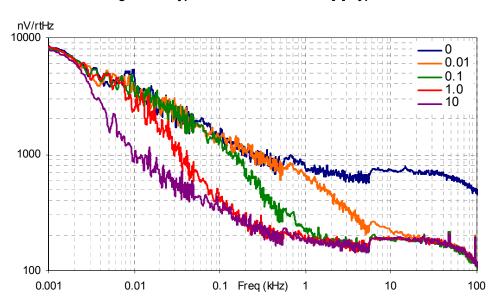

| 42 I/O I/O P0[3] Analog column mux input and column output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42  | -       | I/O    | P0[3]           | Analog column mux input and column output                                    |