#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | M8C                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 24MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                   |

| Data Converters            | A/D 4x14b; D/A 4x9b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c27243-24pvxit |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Designing with PSoC Designer**

The development process for the PSoC device differs from that of a traditional fixed function microprocessor. The configurable analog and digital hardware blocks give the PSoC architecture a unique flexibility that pays dividends in managing specification change during development and by lowering inventory costs. These configurable resources, called PSoC Blocks, have the ability to implement a wide variety of user-selectable functions. The PSoC development process is summarized in four steps:

- 1. Select User Modules.

- 2. Configure user modules.

- 3. Organize and connect.

- 4. Generate, verify, and debug.

#### Select User Modules

PSoC Designer provides a library of prebuilt, pretested hardware peripheral components called "user modules." User modules make selecting and implementing peripheral devices, both analog and digital, simple.

#### **Configure User Modules**

Each user module that you select establishes the basic register settings that implement the selected function. They also provide parameters and properties that allow you to tailor their precise configuration to your particular application. For example, a pulse width modulator (PWM) User Module configures one or more digital PSoC blocks, one for each 8 bits of resolution. The user module parameters permit you to establish the pulse width and duty cycle. Configure the parameters and properties to correspond to your chosen application. Enter values directly or by selecting values from drop-down menus. All the user modules are documented in datasheets that may be viewed directly in PSoC Designer or on the Cypress website. These user module datasheets explain the internal operation of the user module and provide performance specifications. Each datasheet describes the use of each user module parameter, and other information you may need to successfully implement your design.

#### **Organize and Connect**

You build signal chains at the chip level by interconnecting user modules to each other and the I/O pins. You perform the selection, configuration, and routing so that you have complete control over all on-chip resources.

#### Generate, Verify, and Debug

When you are ready to test the hardware configuration or move on to developing code for the project, you perform the "Generate Configuration Files" step. This causes PSoC Designer to generate source code that automatically configures the device to your specification and provides the software for the system. The generated code provides application programming interfaces (APIs) with high-level functions to control and respond to hardware events at run time and interrupt service routines that you can adapt as needed.

A complete code development environment lets you to develop and customize your applications in either C, assembly language, or both.

The last step in the development process takes place inside PSoC Designer's debugger (access by clicking the Connect icon). PSoC Designer downloads the HEX image to the ICE where it runs at full speed. PSoC Designer debugging capabilities rival those of systems costing many times more. In addition to traditional single-step, run-to-breakpoint and watch-variable features, the debug interface provides a large trace buffer and lets you to define complex breakpoint events that include monitoring address and data bus values, memory locations and external signals.

# 48-pin Part Pinout

# Table 6. Pin Definitions – 48-pin Part Pinout (SSOP)

|            | -<br>-  | no.    |                 | · · · · · · · · · · · · · · · · ·                                             |

|------------|---------|--------|-----------------|-------------------------------------------------------------------------------|

| Pin<br>No. |         | pe     | Pin<br>Name     | Description                                                                   |

|            | Digital | Analog |                 |                                                                               |

| 1          | 1/0     |        | P0[7]           | Analog column mux input                                                       |

| 2          | 1/0     | I/O    | P0[5]           | Analog column mux input and column output                                     |

| 3          | 1/0     | I/O    | P0[3]           | Analog column mux input and column output                                     |

| 4          | 1/0     | I      | P0[1]           | Analog column mux input                                                       |

| 5          | 1/0     |        | P2[7]           |                                                                               |

| 6          | 1/0     |        | P2[5]           |                                                                               |

| 7          | 1/0     | 1      | P2[3]           | Direct switched capacitor block input                                         |

| 8          | 1/0     | I      | P2[1]           | Direct switched capacitor block input                                         |

| 9          | 1/0     |        | P4[7]           |                                                                               |

| 10         | I/O     |        | P4[5]           |                                                                               |

| 11         | 1/0     |        | P4[3]           |                                                                               |

| 12         | 1/0     |        | P4[1]           |                                                                               |

| 13         | Po      | wer    | SMP             | SMP connection to external components<br>required                             |

| 14         | I/O     |        | P3[7]           |                                                                               |

| 15         | I/O     |        | P3[5]           |                                                                               |

| 16         | I/O     |        | P3[3]           |                                                                               |

| 17         | I/O     |        | P3[1]           |                                                                               |

| 18         | I/O     |        | P5[3]           |                                                                               |

| 19         | I/O     |        | P5[1]           |                                                                               |

| 20         | I/O     |        | P1[7]           | I <sup>2</sup> C SCL                                                          |

| 21         | I/O     |        | P1[5]           | I <sup>2</sup> C SDA                                                          |

| 22         | I/O     |        | P1[3]           |                                                                               |

| 23         | I/O     |        | P1[1]           | Crystal Input (XTALin), I <sup>2</sup> C SCL,<br>ISSP-SCLK <sup>[9]</sup>     |

| 24         | Po      | wer    | Vss             | Ground connection                                                             |

| 25         | I/O     |        | P1[0]           | Crystal output (XTALout), I <sup>2</sup> C SDA,<br>ISSP-SDATA. <sup>[9]</sup> |

| 26         | I/O     |        | P1[2]           |                                                                               |

| 27         | I/O     |        | P1[4]           | Optional external clock input (EXTCLK)                                        |

| 28         | I/O     |        | P1[6]           |                                                                               |

| 29         | I/O     |        | P5[0]           |                                                                               |

| 30         | I/O     |        | P5[2]           |                                                                               |

| 31         | I/O     |        | P3[0]           |                                                                               |

| 32         | I/O     |        | P3[2]           |                                                                               |

| 33         | I/O     |        | P3[4]           |                                                                               |

| 34         | I/O     |        | P3[6]           |                                                                               |

| 35         | In      | put    | XRES            | Active high external reset with internal pull down                            |

| 36         | I/O     |        | P4[0]           |                                                                               |

| 37         | I/O     |        | P4[2]           |                                                                               |

| 38         | I/O     |        | P4[4]           |                                                                               |

| 39         | I/O     |        | P4[6]           |                                                                               |

| 40         | I/O     | 1      | P2[0]           | Direct switched capacitor block input                                         |

| 41         | I/O     | Ι      | P2[2]           | Direct switched capacitor block input                                         |

| 42         | I/O     |        | P2[4]           | External analog ground (AGND)                                                 |

| 43         | I/O     |        | P2[6]           | External voltage reference (VRef)                                             |

| 44         | I/O     | I      | P0[0]           | Analog column mux input                                                       |

| 45         | I/O     | I/O    | P0[2]           | Analog column mux input and column output                                     |

| 46         | I/O     | I/O    | P0[4]           | Analog column mux input and column output                                     |

| 47         | 1/O     |        | P0[6]           | Analog column mux input                                                       |

| 48         |         | wer    | V <sub>DD</sub> | Supply voltage                                                                |

| +0         |         |        | • 00            |                                                                               |

### Figure 8. CY8C27643 48-pin PSoC Device

|                      | _        |          |      |                         |

|----------------------|----------|----------|------|-------------------------|

| A, I, P0[7]          | <b>1</b> | $\smile$ | 48   | V <sub>DD</sub>         |

| A, IO, P0[5]         | 2        |          | 47   | P0[6], A, I             |

| A, IO, P0[3]         | 3        |          | 46   | P0[4], A, IO            |

| A, I, P0[1] <b>=</b> | 4        |          | 45   | P0[2], A, IO            |

| P2[7] 🗖              | 5        |          | 44   | P0[0], A, I             |

| P2[5] 🗖              | 6        |          | 43   | P2[6], External VRef    |

| A, I, P2[3] <b>=</b> | 7        |          | 42   | P2[4], External AGND    |

| A, I, P2[1] <b>=</b> | 8        |          | 41   | P2[2], A, I             |

| P4[7] 🗖              | 9        |          | 40   | P2[0], A, I             |

| P4[5] 🗖              | 10       |          | 39   | P4[6]                   |

| P4[3] 🗖              | 11       |          | 38   | P4[4]                   |

| P4[1] 🗖              | 12       | SSOP     | 37   | P4[2]                   |

| SMP                  | 13       | 0001     | 36   | P4[0]                   |

| P3[7] 🗖              | 14       |          | 35   | XRES                    |

| P3[5] 🗖              | 15       |          | 34 🗖 | P3[6]                   |

| P3[3] 🖛              | 16       |          | 33   | P3[4]                   |

| P3[1] 🗖              | 17       |          | 32   | P3[2]                   |

| P5[3] 🗖              | 18       |          | 31   | P3[0]                   |

| P5[1] <b>=</b>       |          |          | 30   | P5[2]                   |

| I2C SCL, P1[7]       |          |          | 29   | P5[0]                   |

| I2C SDA, P1[5]       | 21       |          | 28   | P1[6]                   |

| P1[3] 🗖              |          |          | 27   | P1[4], EXTCLK           |

| SCL, XTALin, P1[1]   |          |          | 26   | P1[2]                   |

| V <sub>SS</sub> 🗖    | 24       |          | 25   | P1[0], XTALout, I2C SDA |

| L                    |          |          |      |                         |

**LEGEND**: A = Analog, I = Input, and O = Output.

#### Note

9. These are the ISSP pins, which are not High Z at POR (Power On Reset). See the PSoC Programmable System-on-Chip Technical Reference Manual for details.

I2C

# **Register Reference**

This section lists the registers of the CY8C27x43 PSoC device. For detailed register information, see the PSoC Programmable System-on-Chip Technical Reference Manual.

### **Register Conventions**

The register conventions specific to this section are listed in the following table.

#### Table 9. Register Conventions

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

#### Table 10. Register Map Bank 0 Table: User Space

#### **Register Mapping Tables**

The PSoC device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks. The XOI bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XOI bit is set, the user is in Bank 1.

**Note** In the following register mapping tables, blank fields are reserved and must not be accessed.

| Name     | Addr<br>(0,Hex) | Access | Name    | Addr<br>(0,Hex) | Access | Name     | Addr<br>(0,Hex) | Access | Name       | Addr<br>(0,Hex) | Access |

|----------|-----------------|--------|---------|-----------------|--------|----------|-----------------|--------|------------|-----------------|--------|

| PRT0DR   | 00              | RW     |         | 40              |        | ASC10CR0 | 80              | RW     |            | C0              |        |

| PRTOIE   | 01              | RW     |         | 41              |        | ASC10CR1 | 81              | RW     |            | C1              |        |

| PRT0GS   | 02              | RW     |         | 42              |        | ASC10CR2 | 82              | RW     |            | C2              |        |

| PRT0DM2  | 03              | RW     |         | 43              |        | ASC10CR3 | 83              | RW     |            | C3              |        |

| PRT1DR   | 04              | RW     |         | 44              |        | ASD11CR0 | 84              | RW     |            | C4              |        |

| PRT1IE   | 05              | RW     |         | 45              |        | ASD11CR1 | 85              | RW     |            | C5              |        |

| PRT1GS   | 06              | RW     |         | 46              |        | ASD11CR2 | 86              | RW     |            | C6              |        |

| PRT1DM2  | 07              | RW     |         | 47              |        | ASD11CR3 | 87              | RW     |            | C7              |        |

| PRT2DR   | 08              | RW     |         | 48              |        | ASC12CR0 | 88              | RW     |            | C8              |        |

| PRT2IE   | 09              | RW     |         | 49              |        | ASC12CR1 | 89              | RW     |            | C9              |        |

| PRT2GS   | 0A              | RW     |         | 4A              |        | ASC12CR2 | 8A              | RW     |            | CA              |        |

| PRT2DM2  | 0B              | RW     |         | 4B              |        | ASC12CR3 | 8B              | RW     |            | СВ              |        |

| PRT3DR   | 0C              | RW     |         | 4C              |        | ASD13CR0 | 8C              | RW     |            | CC              | -      |

| PRT3IE   | 0D              | RW     |         | 4D              |        | ASD13CR1 | 8D              | RW     |            | CD              | -      |

| PRT3GS   | 0E              | RW     |         | 4E              |        | ASD13CR2 | 8E              | RW     |            | CE              | -      |

| PRT3DM2  | 0F              | RW     |         | 4F              |        | ASD13CR3 | 8F              | RW     |            | CF              | 1      |

| PRT4DR   | 10              | RW     |         | 50              |        | ASD20CR0 | 90              | RW     |            | D0              | 1      |

| PRT4IE   | 11              | RW     |         | 51              |        | ASD20CR1 | 91              | RW     |            | D1              | 1      |

| PRT4GS   | 12              | RW     |         | 52              |        | ASD20CR2 | 92              | RW     |            | D2              | 1      |

| PRT4DM2  | 13              | RW     |         | 53              |        | ASD20CR3 | 93              | RW     |            | D3              | 1      |

| PRT5DR   | 14              | RW     |         | 54              |        | ASC21CR0 | 94              | RW     |            | D4              | 1      |

| PRT5IE   | 15              | RW     |         | 55              |        | ASC21CR1 | 95              | RW     |            | D5              | -      |

| PRT5GS   | 16              | RW     |         | 56              |        | ASC21CR2 | 96              | RW     | I2C_CFG    | D6              | RW     |

| PRT5DM2  | 17              | RW     |         | 57              |        | ASC21CR3 | 97              | RW     | I2C_SCR    | D7              | #      |

|          | 18              |        |         | 58              |        | ASD22CR0 | 98              | RW     | <br>I2C_DR | D8              | RW     |

|          | 19              |        |         | 59              |        | ASD22CR1 | 99              | RW     | I2C_MSCR   | D9              | #      |

|          | 1A              |        |         | 5A              |        | ASD22CR2 | 9A              | RW     | INT CLR0   | DA              | RW     |

|          | 1B              |        |         | 5B              |        | ASD22CR3 | 9B              | RW     | INT_CLR1   | DB              | RW     |

|          | 1C              |        |         | 5C              |        | ASC23CR0 | 9C              | RW     |            | DC              | 1      |

|          | 1D              |        |         | 5D              |        | ASC23CR1 | 9D              | RW     | INT CLR3   | DD              | RW     |

|          | 1E              |        |         | 5E              |        | ASC23CR2 | 9E              | RW     | INT_MSK3   | DE              | RW     |

|          | 1F              |        |         | 5F              |        | ASC23CR3 | 9F              | RW     |            | DF              | -      |

| DBB00DR0 | 20              | #      | AMX_IN  | 60              | RW     | 1        | A0              | 1      | INT_MSK0   | E0              | RW     |

| DBB00DR1 | 21              | W      |         | 61              |        | 1        | A1              | 1      | INT_MSK1   | E1              | RW     |

| DBB00DR2 | 22              | RW     | 1       | 62              | 1      | 1        | A2              | 1      | INT_VC     | E2              | RC     |

| DBB00CR0 | 23              | #      | ARF CR  | 63              | RW     | 1        | A3              | 1      | RES WDT    | E3              | W      |

| DBB01DR0 | 24              | #      | CMP CR0 | 64              | #      | 1        | A4              | 1      | DEC_DH     | E4              | RC     |

| DBB01DR1 | 25              | W      | ASY CR  | 65              | #      |          | A5              |        | DEC_DL     | E5              | RC     |

| DBB01DR2 | 26              | RW     | CMP_CR1 | 66              | RW     | -        | A6              | +      | DEC_CR0    | E6              | RW     |

Blank fields are Reserved and must not be accessed.

# Access is bit specific.

### Table 10. Register Map Bank 0 Table: User Space (continued)

| Name     | Addr<br>(0,Hex) | Access | Name     | Addr<br>(0,Hex) | Access | Name    | Addr<br>(0,Hex) | Access | Name     | Addr<br>(0,Hex) | Access |

|----------|-----------------|--------|----------|-----------------|--------|---------|-----------------|--------|----------|-----------------|--------|

| DBB01CR0 | 27              | #      |          | 67              |        |         | A7              |        | DEC_CR1  | E7              | RW     |

| DCB02DR0 | 28              | #      |          | 68              |        |         | A8              |        | MUL_X    | E8              | W      |

| DCB02DR1 | 29              | W      |          | 69              |        |         | A9              |        | MUL_Y    | E9              | W      |

| DCB02DR2 | 2A              | RW     |          | 6A              |        |         | AA              |        | MUL_DH   | EA              | R      |

| DCB02CR0 | 2B              | #      |          | 6B              |        |         | AB              |        | MUL_DL   | EB              | R      |

| DCB03DR0 | 2C              | #      |          | 6C              |        |         | AC              |        | ACC_DR1  | EC              | RW     |

| DCB03DR1 | 2D              | W      |          | 6D              |        |         | AD              |        | ACC_DR0  | ED              | RW     |

| DCB03DR2 | 2E              | RW     |          | 6E              |        |         | AE              |        | ACC_DR3  | EE              | RW     |

| DCB03CR0 | 2F              | #      |          | 6F              |        |         | AF              |        | ACC_DR2  | EF              | RW     |

| DBB10DR0 | 30              | #      | ACB00CR3 | 70              | RW     | RDIORI  | B0              | RW     |          | F0              |        |

| DBB10DR1 | 31              | W      | ACB00CR0 | 71              | RW     | RDI0SYN | B1              | RW     |          | F1              |        |

| DBB10DR2 | 32              | RW     | ACB00CR1 | 72              | RW     | RDI0IS  | B2              | RW     |          | F2              |        |

| DBB10CR0 | 33              | #      | ACB00CR2 | 73              | RW     | RDI0LT0 | B3              | RW     |          | F3              |        |

| DBB11DR0 | 34              | #      | ACB01CR3 | 74              | RW     | RDI0LT1 | B4              | RW     |          | F4              |        |

| DBB11DR1 | 35              | W      | ACB01CR0 | 75              | RW     | RDI0RO0 | B5              | RW     |          | F5              |        |

| DBB11DR2 | 36              | RW     | ACB01CR1 | 76              | RW     | RDI0RO1 | B6              | RW     |          | F6              |        |

| DBB11CR0 | 37              | #      | ACB01CR2 | 77              | RW     |         | B7              |        | CPU_F    | F7              | RL     |

| DCB12DR0 | 38              | #      | ACB02CR3 | 78              | RW     | RDI1RI  | B8              | RW     |          | F8              |        |

| DCB12DR1 | 39              | W      | ACB02CR0 | 79              | RW     | RDI1SYN | B9              | RW     |          | F9              |        |

| DCB12DR2 | 3A              | RW     | ACB02CR1 | 7A              | RW     | RDI1IS  | BA              | RW     |          | FA              |        |

| DCB12CR0 | 3B              | #      | ACB02CR2 | 7B              | RW     | RDI1LT0 | BB              | RW     |          | FB              | 1      |

| DCB13DR0 | 3C              | #      | ACB03CR3 | 7C              | RW     | RDI1LT1 | BC              | RW     |          | FC              | 1      |

| DCB13DR1 | 3D              | W      | ACB03CR0 | 7D              | RW     | RDI1RO0 | BD              | RW     | 1        | FD              | 1      |

| DCB13DR2 | 3E              | RW     | ACB03CR1 | 7E              | RW     | RDI1RO1 | BE              | RW     | CPU_SCR1 | FE              | #      |

| DCB13CR0 | 3F              | #      | ACB03CR2 | 7F              | RW     |         | BF              |        | CPU_SCR0 | FF              | #      |

Blank fields are Reserved and must not be accessed.

# Access is bit specific.

Table 11. Register Map Bank 1 Table: Configuration Space

| Name    | Addr<br>(1,Hex) | Access | Name | Addr<br>(1,Hex) | Access | Name     | Addr<br>(1,Hex) | Access | Name     | Addr<br>(1,Hex) | Access |

|---------|-----------------|--------|------|-----------------|--------|----------|-----------------|--------|----------|-----------------|--------|

| PRT0DM0 | 00              | RW     |      | 40              |        | ASC10CR0 | 80              | RW     |          | C0              |        |

| PRT0DM1 | 01              | RW     |      | 41              |        | ASC10CR1 | 81              | RW     |          | C1              |        |

| PRT0IC0 | 02              | RW     |      | 42              |        | ASC10CR2 | 82              | RW     |          | C2              |        |

| PRT0IC1 | 03              | RW     |      | 43              |        | ASC10CR3 | 83              | RW     |          | C3              |        |

| PRT1DM0 | 04              | RW     |      | 44              |        | ASD11CR0 | 84              | RW     |          | C4              |        |

| PRT1DM1 | 05              | RW     |      | 45              |        | ASD11CR1 | 85              | RW     |          | C5              |        |

| PRT1IC0 | 06              | RW     |      | 46              |        | ASD11CR2 | 86              | RW     |          | C6              |        |

| PRT1IC1 | 07              | RW     |      | 47              |        | ASD11CR3 | 87              | RW     |          | C7              |        |

| PRT2DM0 | 08              | RW     |      | 48              |        | ASC12CR0 | 88              | RW     |          | C8              |        |

| PRT2DM1 | 09              | RW     |      | 49              |        | ASC12CR1 | 89              | RW     |          | C9              |        |

| PRT2IC0 | 0A              | RW     |      | 4A              |        | ASC12CR2 | 8A              | RW     |          | CA              |        |

| PRT2IC1 | 0B              | RW     |      | 4B              |        | ASC12CR3 | 8B              | RW     |          | CB              | 1      |

| PRT3DM0 | 0C              | RW     |      | 4C              |        | ASD13CR0 | 8C              | RW     |          | CC              | 1      |

| PRT3DM1 | 0D              | RW     |      | 4D              |        | ASD13CR1 | 8D              | RW     |          | CD              | 1      |

| PRT3IC0 | 0E              | RW     |      | 4E              |        | ASD13CR2 | 8E              | RW     |          | CE              | 1      |

| PRT3IC1 | 0F              | RW     |      | 4F              |        | ASD13CR3 | 8F              | RW     |          | CF              | 1      |

| PRT4DM0 | 10              | RW     |      | 50              |        | ASD20CR0 | 90              | RW     | GDI_O_IN | D0              | RW     |

| PRT4DM1 | 11              | RW     |      | 51              |        | ASD20CR1 | 91              | RW     | GDI_E_IN | D1              | RW     |

| PRT4IC0 | 12              | RW     |      | 52              |        | ASD20CR2 | 92              | RW     | GDI_O_OU | D2              | RW     |

| PRT4IC1 | 13              | RW     |      | 53              |        | ASD20CR3 | 93              | RW     | GDI_E_OU | D3              | RW     |

| PRT5DM0 | 14              | RW     |      | 54              |        | ASC21CR0 | 94              | RW     |          | D4              | -      |

| PRT5DM1 | 15              | RW     |      | 55              |        | ASC21CR1 | 95              | RW     |          | D5              | -      |

| PRT5IC0 | 16              | RW     |      | 56              |        | ASC21CR2 | 96              | RW     |          | D6              | -      |

| PRT5IC1 | 17              | RW     |      | 57              |        | ASC21CR3 | 97              | RW     |          | D7              | -      |

|         | 18              |        |      | 58              |        | ASD22CR0 | 98              | RW     |          | D8              |        |

|         | 19              |        |      | 59              |        | ASD22CR1 | 99              | RW     | 1        | D9              |        |

|         | 1A              |        |      | 5A              |        | ASD22CR2 | 9A              | RW     |          | DA              | 1      |

|         | 1B              |        |      | 5B              |        | ASD22CR3 | 9B              | RW     |          | DB              | +      |

|         | 1C              |        |      | 5C              |        | ASC23CR0 | 9C              | RW     | 1        | DC              | +      |

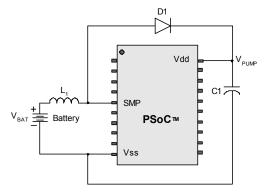

# DC Switch Mode Pump Specifications

Table 21 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 21. DC Switch Mode Pump (SMP) Specifications

| Symbol                   | Description                                                                                                                       | Min  | Тур  | Max  | Unit            | Notes                                                                                                                                                                           |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PUMP</sub> 5 V    | 5 V output voltage                                                                                                                | 4.75 | 5.0  | 5.25 | V               | Configured as in Note 15. Average,<br>neglecting ripple. SMP trip voltage is<br>set to 5.0 V.                                                                                   |

| V <sub>PUMP</sub> 3 V    | 3 V output voltage                                                                                                                | 3.00 | 3.25 | 3.60 | V               | Configured as in Note 15. Average,<br>neglecting ripple. SMP trip voltage is<br>set to 3.25 V.                                                                                  |

| I <sub>PUMP</sub>        | Available output current $V_{BAT} = 1.5 \text{ V}, V_{PUMP} = 3.25 \text{ V}$ $V_{BAT} = 1.8 \text{ V}, V_{PUMP} = 5.0 \text{ V}$ |      |      |      | mA<br>mA        | Configured as in Note 15. SMP trip<br>voltage is set to 3.25 V.<br>SMP trip voltage is set to 5.0 V.                                                                            |

| V <sub>BAT</sub> 5 V     | Input voltage range from battery                                                                                                  | 1.8  | -    | 5.0  | V               | Configured as in Note 15. SMP trip voltage is set to 5.0 V.                                                                                                                     |

| V <sub>BAT</sub> 3 V     | Input voltage range from battery                                                                                                  | 1.0  | -    | 3.3  | V               | Configured as in Note 15. SMP trip voltage is set to 3.25 V.                                                                                                                    |

| VBATSTART                | Minimum input voltage from battery to start pump                                                                                  | 1.1  | -    | -    | V               | Configured as in Note 15.                                                                                                                                                       |

| $\Delta V_{PUMP}_{Line}$ | Line regulation (over V <sub>BAT</sub> range)                                                                                     | -    | 5    | _    | %V <sub>O</sub> | Configured as in Note 15. $V_{O}$ is the " $V_{DD}$ Value for PUMP Trip" specified by the VM[2:0] setting in the DC POR and LVD Specification, Table 25 on page 33.             |

| $\Delta V_{PUMP\_Load}$  | Load regulation                                                                                                                   | _    | 5    | _    | %V <sub>O</sub> | Configured as in Note 15. $V_{O}$ is the<br>" $V_{DD}$ Value for PUMP Trip" specified<br>by the VM[2:0] setting in the DC POR<br>and LVD Specification, Table 25 on<br>page 33. |

| $\Delta V_{PUMP}$ Ripple | Output voltage ripple (depends on capacitor/load)                                                                                 | -    | 100  | -    | mVpp            | Configured as in Note 15. Load is 5 mA.                                                                                                                                         |

| E <sub>3</sub>           | Efficiency                                                                                                                        | 35   | 50   | -    | %               | Configured as in Note 15. Load is 5 mA. SMP trip voltage is set to 3.25 V.                                                                                                      |

| F <sub>PUMP</sub>        | Switching frequency                                                                                                               | -    | 1.3  | -    | MHz             |                                                                                                                                                                                 |

| DC <sub>PUMP</sub>       | Switching duty cycle                                                                                                              | _    | 50   | -    | %               |                                                                                                                                                                                 |

#### Figure 12. Basic Switch Mode Pump Circuit

# DC Analog Reference Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85°C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

The guaranteed specifications are measured through the Analog Continuous Time PSoC blocks. The power levels for AGND refer to the power of the analog continuous time PSoC block. The power levels for RefHi and RefLo refer to the Analog Reference Control register. The limits stated for AGND include the offset error of the AGND buffer local to the Analog Continuous Time PSoC block. Reference control power is high.

**Note** Avoid using P2[4] for digital signaling when using an analog resource that depends on the Analog Reference. Some coupling of the digital signal may appear on the AGND.

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings | Symbol             | Reference | Description                  | Min                        | Тур                        | Max                        | Unit |

|------------------------------|-----------------------------|--------------------|-----------|------------------------------|----------------------------|----------------------------|----------------------------|------|

|                              | RefPower = high             | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap | V <sub>DD</sub> /2 + 1.228 | V <sub>DD</sub> /2 + 1.290 | V <sub>DD</sub> /2 + 1.352 | V    |

|                              | Opamp bias = high           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2           | V <sub>DD</sub> /2-0.078   | $V_{DD}/2 - 0.007$         | V <sub>DD</sub> /2 + 0.063 | V    |

|                              |                             | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap | V <sub>DD</sub> /2 – 1.336 | V <sub>DD</sub> /2 – 1.295 | V <sub>DD</sub> /2 - 1.250 | V    |

|                              | RefPower = high             | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap | V <sub>DD</sub> /2 + 1.224 | V <sub>DD</sub> /2 + 1.293 | V <sub>DD</sub> /2 + 1.356 | V    |

|                              | Opamp bias = low            | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2           | V <sub>DD</sub> /2 – 0.056 | $V_{DD}/2 - 0.005$         | V <sub>DD</sub> /2 + 0.043 | V    |

| 0b000                        |                             | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap | V <sub>DD</sub> /2 – 1.338 | V <sub>DD</sub> /2 – 1.298 | V <sub>DD</sub> /2 – 1.255 | V    |

| 00000                        | RefPower = medium           | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap | V <sub>DD</sub> /2 + 1.226 | V <sub>DD</sub> /2 + 1.293 | V <sub>DD</sub> /2 + 1.356 | V    |

|                              | Opamp bias = high           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2           | V <sub>DD</sub> /2 – 0.057 | $V_{DD}/2 - 0.006$         | V <sub>DD</sub> /2 + 0.044 | V    |

|                              |                             | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap | V <sub>DD</sub> /2 – 1.337 | V <sub>DD</sub> /2 - 1.298 | V <sub>DD</sub> /2 – 1.256 | V    |

|                              | RefPower = medium           | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap | V <sub>DD</sub> /2 + 1.226 | V <sub>DD</sub> /2 + 1.294 | V <sub>DD</sub> /2 + 1.359 | V    |

|                              | Opamp bias = low            | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2           | V <sub>DD</sub> /2-0.047   | $V_{DD}/2 - 0.004$         | V <sub>DD</sub> /2 + 0.035 | V    |

|                              |                             | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap | V <sub>DD</sub> /2 – 1.338 | V <sub>DD</sub> /2 - 1.299 | V <sub>DD</sub> /2 – 1.258 | V    |

### Table 22. 5-V DC Analog Reference Specifications

# Table 22. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                     | Min             | Тур                     | Max                     | Unit |

|------------------------------|----------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|------|

|                              | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.222   | P2[4] + 1.290           | P2[4] + 1.343           | V    |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.331   | P2[4] – 1.295           | P2[4] – 1.254           | V    |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.226   | P2[4] + 1.293           | P2[4] + 1.347           | V    |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -    |

| 0b101                        |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.331   | P2[4] – 1.298           | P2[4] – 1.259           | V    |

| 00101                        | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.227   | P2[4] + 1.294           | P2[4] + 1.347           | V    |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.331   | P2[4] – 1.298           | P2[4] – 1.259           | V    |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.228   | P2[4] + 1.295           | P2[4] + 1.349           | V    |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.332   | P2[4] – 1.299           | P2[4] – 1.260           | V    |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.535           | 2.598                   | 2.644                   | V    |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.227           | 1.305                   | 1.398                   | V    |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.009 | V <sub>SS</sub> + 0.038 | V    |

|                              |                                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.530           | 2.598                   | 2.643                   | V    |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.244           | 1.303                   | 1.370                   | V    |

| 0b110                        |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.005 | V <sub>SS</sub> + 0.024 | V    |

| 00110                        | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.532           | 2.598                   | 2.644                   | V    |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.239           | 1.304                   | 1.380                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.026 | V    |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.528           | 2.598                   | 2.645                   | V    |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.249           | 1.302                   | 1.362                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.018 | V    |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.041           | 4.155                   | 4.234                   | V    |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 1.998           | 2.083                   | 2.183                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.010 | V <sub>SS</sub> + 0.038 | V    |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.047           | 4.153                   | 4.236                   | V    |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.012           | 2.082                   | 2.157                   | V    |

| 0b111                        |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.024 | V    |

| 00111                        | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.049           | 4.154                   | 4.238                   | V    |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.008           | 2.083                   | 2.165                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.026 | V    |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.047           | 4.154                   | 4.238                   | V    |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.016           | 2.081                   | 2.150                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.018 | V    |

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                  | Symbol             | Reference | Description | Min   | Тур         | Max         | Unit |

|------------------------------|----------------------------------------------|--------------------|-----------|-------------|-------|-------------|-------------|------|

|                              |                                              | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap | 2.507 | 2.598       | 2.698       | V    |

|                              | RefPower = high<br>Opamp bias = high         | V <sub>AGND</sub>  | AGND      | Bandgap     | 1.203 | 1.307       | 1.424       | V    |

|                              |                                              | $V_{REFLO}$        | Ref Low   | Vss         | Vss   | Vss + 0.012 | Vss + 0.067 | V    |

|                              | RefPower = high<br>Opamp bias = low          | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap | 2.516 | 2.598       | 2.683       | V    |

|                              |                                              | V <sub>AGND</sub>  | AGND      | Bandgap     | 1.241 | 1.303       | 1.376       | V    |

| 0b110                        |                                              | $V_{REFLO}$        | Ref Low   | Vss         | Vss   | Vss + 0.007 | Vss + 0.040 | V    |

| 00110                        |                                              | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap | 2.510 | 2.599       | 2.693       | V    |

|                              | RefPower = medium<br>Opamp bias = high       | V <sub>AGND</sub>  | AGND      | Bandgap     | 1.240 | 1.305       | 1.374       | V    |

|                              |                                              | $V_{REFLO}$        | Ref Low   | Vss         | Vss   | Vss + 0.008 | Vss + 0.048 | V    |

|                              |                                              | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap | 2.515 | 2.598       | 2.683       | V    |

|                              | RefPower = medium<br>Opamp bias = low        | V <sub>AGND</sub>  | AGND      | Bandgap     | 1.258 | 1.302       | 1.355       | V    |

|                              | • •                                          | $V_{REFLO}$        | Ref Low   | Vss         | Vss   | Vss + 0.005 | Vss + 0.03  | V    |

| 0b111                        | All power settings.<br>Not allowed for 3.3 V | -                  | -         | _           | -     | -           | _           | -    |

### Table 23. 3.3-V DC Analog Reference Specifications

### DC Analog PSoC Block Specifications

Table 24 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 24. DC Analog PSoC Block Specifications

| Symbol          | Description                           | Min | Тур  | Max | Unit |

|-----------------|---------------------------------------|-----|------|-----|------|

| R <sub>CT</sub> | Resistor unit value (continuous time) | _   | 12.2 | -   | kΩ   |

| C <sub>SC</sub> | Capacitor unit value (switch cap)     | _   | 80   |     | fF   |

# DC Programming Specifications

Table 26 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 26. DC Programming Specifications

| Symbol                | Description                                                                          | Min                    | Тур | Max             | Unit   | Notes                                                                                            |

|-----------------------|--------------------------------------------------------------------------------------|------------------------|-----|-----------------|--------|--------------------------------------------------------------------------------------------------|

| V <sub>DDP</sub>      | V <sub>DD</sub> for programming and erase                                            | 4.5                    | 5   | 5.5             | V      | This specification applies<br>to the functional<br>requirements of external<br>programmer tools. |

| V <sub>DDLV</sub>     | Low V <sub>DD</sub> for verify                                                       | 3                      | 3.1 | 3.2             | V      | This specification applies<br>to the functional<br>requirements of external<br>programmer tools. |

| V <sub>DDHV</sub>     | High V <sub>DD</sub> for verify                                                      | 5.1                    | 5.2 | 5.3             | V      | This specification applies<br>to the functional<br>requirements of external<br>programmer tools. |

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operation                                             | 3                      |     | 5.25            | V      | This specification applies<br>to this device when it is<br>executing internal flash<br>writes.   |

| I <sub>DDP</sub>      | Supply current during programming or verify                                          | -                      | 5   | 25              | mA     |                                                                                                  |

| V <sub>ILP</sub>      | Input low voltage during programming or verify                                       | -                      | -   | 0.8             | V      |                                                                                                  |

| V <sub>IHP</sub>      | Input high voltage during programming or verify                                      | 2.2                    | -   | -               | V      |                                                                                                  |

| I <sub>ILP</sub>      | Input current when applying $V_{ILP}$ to P1[0] or P1[1] during programming or verify | -                      | -   | 0.2             | mA     | Driving internal pull-down resistor.                                                             |

| I <sub>IHP</sub>      | Input current when applying $V_{IHP}$ to P1[0] or P1[1] during programming or verify | -                      | -   | 1.5             | mA     | Driving internal pull-down resistor.                                                             |

| V <sub>OLV</sub>      | Output low voltage during programming or verify                                      | -                      | _   | Vss + 0.75      | V      |                                                                                                  |

| V <sub>OHV</sub>      | Output high voltage during programming or verify                                     | V <sub>DD</sub> – 1.0  | _   | V <sub>DD</sub> | V      |                                                                                                  |

| Flash <sub>ENPB</sub> | Flash endurance (per block)                                                          | 50,000 <sup>[19]</sup> | -   | -               | Cycles | Erase/write cycles per block.                                                                    |

| Flash <sub>ENT</sub>  | Flash endurance (total) <sup>[20]</sup>                                              | 1,800,000              | -   | -               | Cycles | Erase/write cycles.                                                                              |

| Flash <sub>DR</sub>   | Flash data retention                                                                 | 10                     | 1   | -               | Years  |                                                                                                  |

# DC I<sup>2</sup>C Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

# Table 27. DC I<sup>2</sup>C Specifications

| Parameter                          | Description      | Min                 | Тур | Max                    | Units | Notes                            |

|------------------------------------|------------------|---------------------|-----|------------------------|-------|----------------------------------|

| V <sub>ILI2C</sub> <sup>[21]</sup> | Input low level  | -                   | -   | 0.3 × V <sub>DD</sub>  | V     | $3.0~V \leq V_{DD} \leq 3.6~V$   |

|                                    |                  | -                   | -   | 0.25 × V <sub>DD</sub> | V     | $4.75~V \leq V_{DD} \leq 5.25~V$ |

| V <sub>IHI2C</sub> <sup>[21]</sup> | Input high level | $0.7 \times V_{DD}$ | -   | -                      | V     | $3.0~V \leq V_{DD} \leq 5.25~V$  |

Notes

<sup>19.</sup> The 50,000 cycle flash endurance per block is only guaranteed if the flash is operating within one voltage range. Voltage ranges are 3.0 V to 3.6 V and 4.75 V to 5.25 V. 19: The 50,000 cycle hash endurance per block is only guaranteed in the hash is operating within one voltage range. Voltage ranges are 3.0 v to 3.6 v and 4.7 v to 5.25 v.

20: A maximum of 36 x 50,000 block endurance cycles is allowed. This may be balanced between operations on 36x1 blocks of 50,000 maximum cycles each, 36 x 2 blocks of 25,000 maximum cycles each, or 36 x 4 blocks of 12,500 maximum cycles each (to limit the total number of cycles to 36 x 50,000 and that no single block ever sees more than 50,000 cycles).

For the full industrial range, you must employ a temperature sensor user module (FlashTemp) and feed the result to the temperature argument before writing. Refer to the Flash APIs application note Design Aids – Reading and Writing PSoC<sup>®</sup> Flash – AN2015 for more information.

21. All GPIOs meet the DC GPIO V<sub>IL</sub> and V<sub>IH</sub> specifications found in the DC GPIO specifications sections. The I<sup>2</sup>C GPIO pins also meet the above specs.

# **AC Electrical Characteristics**

#### AC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 28. AC Chip-Level Specifications

| Symbol                   | Description                                             | Min    | Тур    | Мах                      | Unit | Notes                                                                                                                                                                                                                                                                                                  |

|--------------------------|---------------------------------------------------------|--------|--------|--------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO</sub>         | Internal main oscillator (IMO) frequency                | 23.4   | 24     | 24.6 <sup>[22]</sup>     | MHz  | Trimmed. Utilizing factory trim values.                                                                                                                                                                                                                                                                |

| F <sub>CPU1</sub>        | CPU frequency (5 V nominal)                             | 0.0914 | 24     | 24.6 <sup>[22]</sup>     | MHz  | Trimmed. Utilizing factory trim values. SLIMO mode = 0.                                                                                                                                                                                                                                                |

| F <sub>CPU2</sub>        | CPU frequency (3.3 V nominal)                           | 0.0914 | 12     | 12.3 <sup>[23]</sup>     | MHz  | Trimmed. Utilizing factory trim values. SLIMO mode = 0.                                                                                                                                                                                                                                                |

| F <sub>48M</sub>         | Digital PSoC block frequency                            | 0      | 48     | 49.2 <sup>[22, 24]</sup> | MHz  | Refer to AC Digital Block<br>Specifications on page 40.                                                                                                                                                                                                                                                |

| F <sub>24M</sub>         | Digital PSoC block frequency                            | 0      | 24     | 24.6 <sup>[24]</sup>     | MHz  |                                                                                                                                                                                                                                                                                                        |

| F <sub>32K1</sub>        | Internal low speed oscillator (ILO) frequency           | 15     | 32     | 64                       | kHz  |                                                                                                                                                                                                                                                                                                        |

| F <sub>32K2</sub>        | External crystal oscillator                             | -      | 32.768 | _                        | kHz  | Accuracy is capacitor and crystal dependent. 50% duty cycle.                                                                                                                                                                                                                                           |

| F <sub>32K_U</sub>       | ILO untrimmed frequency                                 | 5      | -      | 100                      | kHz  | After a reset and before the m8c<br>starts to run, the ILO is not<br>trimmed. See the System Resets<br>section of the PSoC Technical<br>Reference Manual for details on<br>timing this                                                                                                                 |

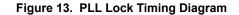

| F <sub>PLL</sub>         | PLL frequency                                           | -      | 23.986 | _                        | MHz  | Multiple (x732) of crystal frequency.                                                                                                                                                                                                                                                                  |

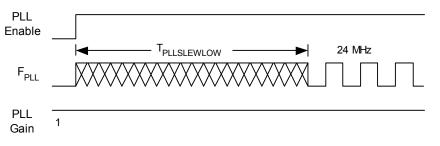

| t <sub>PLLSLEW</sub>     | PLL lock time                                           | 0.5    | -      | 10                       | ms   |                                                                                                                                                                                                                                                                                                        |

| t <sub>PLLSLEWSLOW</sub> | PLL lock time for low gain setting                      | 0.5    | -      | 50                       | ms   |                                                                                                                                                                                                                                                                                                        |

| t <sub>OS</sub>          | External crystal oscillator startup to 1%               | -      | 1700   | 2620                     | ms   |                                                                                                                                                                                                                                                                                                        |

| tosacc                   | External crystal oscillator startup to 100 ppm          | _      | 2800   | 3800                     | ms   | The crystal oscillator frequency is within 100 ppm of its final value by the end of the T <sub>osacc</sub> period. Correct operation assumes a properly loaded 1 $\mu$ W maximum drive level 32.768 kHz crystal. 3.0 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C. |

| t <sub>XRST</sub>        | External reset pulse width                              | 10     | -      | _                        | μs   |                                                                                                                                                                                                                                                                                                        |

| DC <sub>24M</sub>        | 24 MHz duty cycle                                       | 40     | 50     | 60                       | %    |                                                                                                                                                                                                                                                                                                        |

| DC <sub>ILO</sub>        | ILO duty cycle                                          | 20     | 50     | 80                       | %    |                                                                                                                                                                                                                                                                                                        |

| Step <sub>24M</sub>      | 24 MHz trim step size                                   | -      | 50     | -                        | kHz  |                                                                                                                                                                                                                                                                                                        |

| t <sub>POWERUP</sub>     | Time from end of POR to CPU executing code              | -      | 16     | 100                      | ms   | wer-up from 0 V. See the System<br>Resets section of the PSoC<br>Technical Reference Manual.                                                                                                                                                                                                           |

| Fout <sub>48M</sub>      | 48 MHz output frequency                                 | 46.8   | 48.0   | 49.2 <sup>[22, 23]</sup> | MHz  | Trimmed. Utilizing factory trim values.                                                                                                                                                                                                                                                                |

| F <sub>MAX</sub>         | Maximum frequency of signal on row input or row output. | -      | -      | 12.3                     | MHz  |                                                                                                                                                                                                                                                                                                        |

| SR <sub>POWER_UP</sub>   | Power supply slew rate                                  | _      | -      | 250                      | V/ms | V <sub>DD</sub> slew rate during power-up.                                                                                                                                                                                                                                                             |

Notes

22.4.75 V <  $V_{DD}$  < 5.25 V. 23.3.0 V <  $V_{DD}$  < 3.6 V. See application note Adjusting PSoC<sup>®</sup> Trims for 3.3 V and 2.7 V Operation – AN2012 for information on trimming for operation at 3.3 V. 24. See the individual user module datasheets for information on maximum frequencies for user modules.

# Table 28. AC Chip-Level Specifications (continued)

| Symbol                   | Description                                        | Min | Тур | Max  | Unit | Notes  |

|--------------------------|----------------------------------------------------|-----|-----|------|------|--------|

| tjit_IMO <sup>[25]</sup> | 24 MHz IMO cycle-to-cycle jitter (RMS)             | -   | 200 | 700  | ps   | N = 32 |

|                          | 24 MHz IMO long term N cycle-to-cycle jitter (RMS) | -   | 300 | 900  |      |        |

|                          | 24 MHz IMO period jitter (RMS)                     | -   | 100 | 400  |      |        |

| tjit_PLL <sup>[25]</sup> | 24 MHz IMO cycle-to-cycle jitter (RMS)             | -   | 200 | 800  | ps   | N = 32 |

|                          | 24 MHz IMO long term N cycle-to-cycle jitter (RMS) | -   | 300 | 1200 |      |        |

|                          | 24 MHz IMO period jitter (RMS)                     | -   | 100 | 700  | 1    |        |

Figure 14. PLL Lock for Low Gain Setting Timing Diagram

Figure 15. External Crystal Oscillator Startup Timing Diagram

Note

25. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

# AC Analog Output Buffer Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 34. 5-V AC Analog Output Buffer Specifications

| Symbol            | Description                                                                                       | Min          | Тур | Max        | Unit         |

|-------------------|---------------------------------------------------------------------------------------------------|--------------|-----|------------|--------------|

| t <sub>ROB</sub>  | Rising settling time to 0.1%, 1 V Step, 100 pF load<br>Power = low<br>Power = high                |              |     | 2.5<br>2.5 | μs<br>μs     |

| t <sub>SOB</sub>  | Falling settling time to 0.1%, 1 V Step, 100 pF load<br>Power = low<br>Power = high               |              |     | 2.2<br>2.2 | μs<br>μs     |

| SR <sub>ROB</sub> | Rising slew rate (20% to 80%), 1 V Step, 100 pF load<br>Power = low<br>Power = high               | 0.65<br>0.65 |     | _<br>_     | V/μs<br>V/μs |

| SR <sub>FOB</sub> | Falling slew rate (80% to 20%), 1 V Step, 100 pF load<br>Power = low<br>Power = high              | 0.65<br>0.65 |     |            | V/μs<br>V/μs |

| BW <sub>OB</sub>  | Small signal bandwidth, 20 mV <sub>pp</sub> , 3 dB BW, 100 pF load<br>Power = low<br>Power = high | 0.8<br>0.8   |     | _<br>_     | MHz<br>MHz   |

| BW <sub>OB</sub>  | Large signal bandwidth, 1 V <sub>pp</sub> , 3 dB BW, 100 pF load<br>Power = low<br>Power = high   | 300<br>300   |     | _<br>_     | kHz<br>kHz   |

### Table 35. 3.3-V AC Analog Output Buffer Specifications

| Symbol            | Description                                                                                       | Min        | Тур | Max        | Unit         |

|-------------------|---------------------------------------------------------------------------------------------------|------------|-----|------------|--------------|

| t <sub>ROB</sub>  | Rising settling time to 0.1%, 1 V Step, 100 pF load<br>Power = low<br>Power = high                |            | -   | 3.8<br>3.8 | μs<br>μs     |

| t <sub>SOB</sub>  | Falling settling time to 0.1%, 1 V Step, 100 pF load<br>Power = low<br>Power = high               |            | -   | 2.6<br>2.6 | μs<br>μs     |

| SR <sub>ROB</sub> | Rising slew rate (20% to 80%), 1 V Step, 100 pF load<br>Power = low<br>Power = high               | 0.5<br>0.5 | -   |            | V/μs<br>V/μs |

| SR <sub>FOB</sub> | Falling slew rate (80% to 20%), 1 V Step, 100 pF load<br>Power = low<br>Power = high              | 0.5<br>0.5 |     |            | V/μs<br>V/μs |

| BW <sub>OB</sub>  | Small signal bandwidth, 20m V <sub>pp</sub> , 3 dB BW, 100 pF load<br>Power = low<br>Power = high | 0.7<br>0.7 |     |            | MHz<br>MHz   |

| BW <sub>OB</sub>  | Large signal bandwidth, 1 V <sub>pp</sub> , 3 dB BW, 100 pF load<br>Power = low<br>Power = high   | 200<br>200 |     | _<br>_     | kHz<br>kHz   |

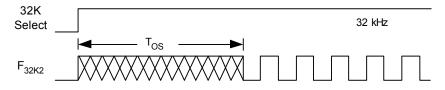

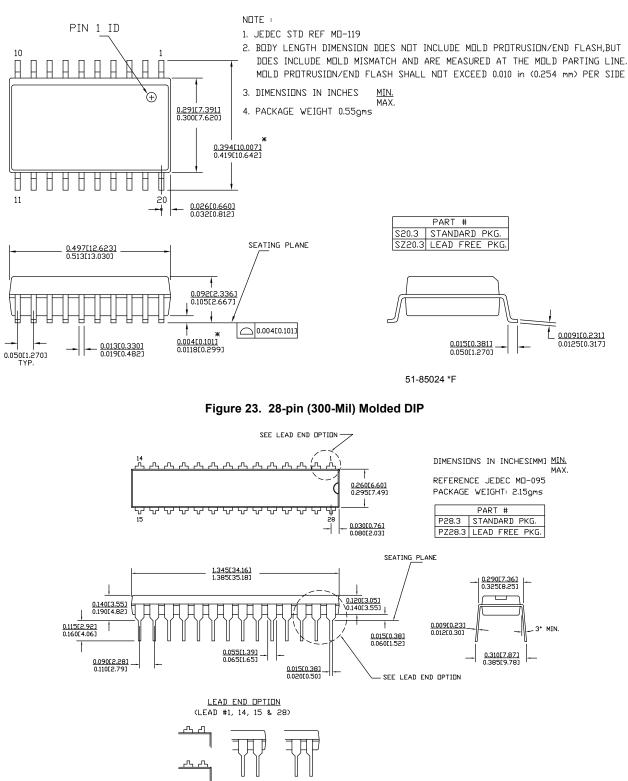

### Figure 22. 20-pin SOIC (0.513 × 0.300 × 0.0932 Inches) Package Outline, 51-85024

51-85014 \*G

# **Development Tool Selection**